Design of Voltage–Current Reference Source in CMOS Technology

Abstract

1. Introduction

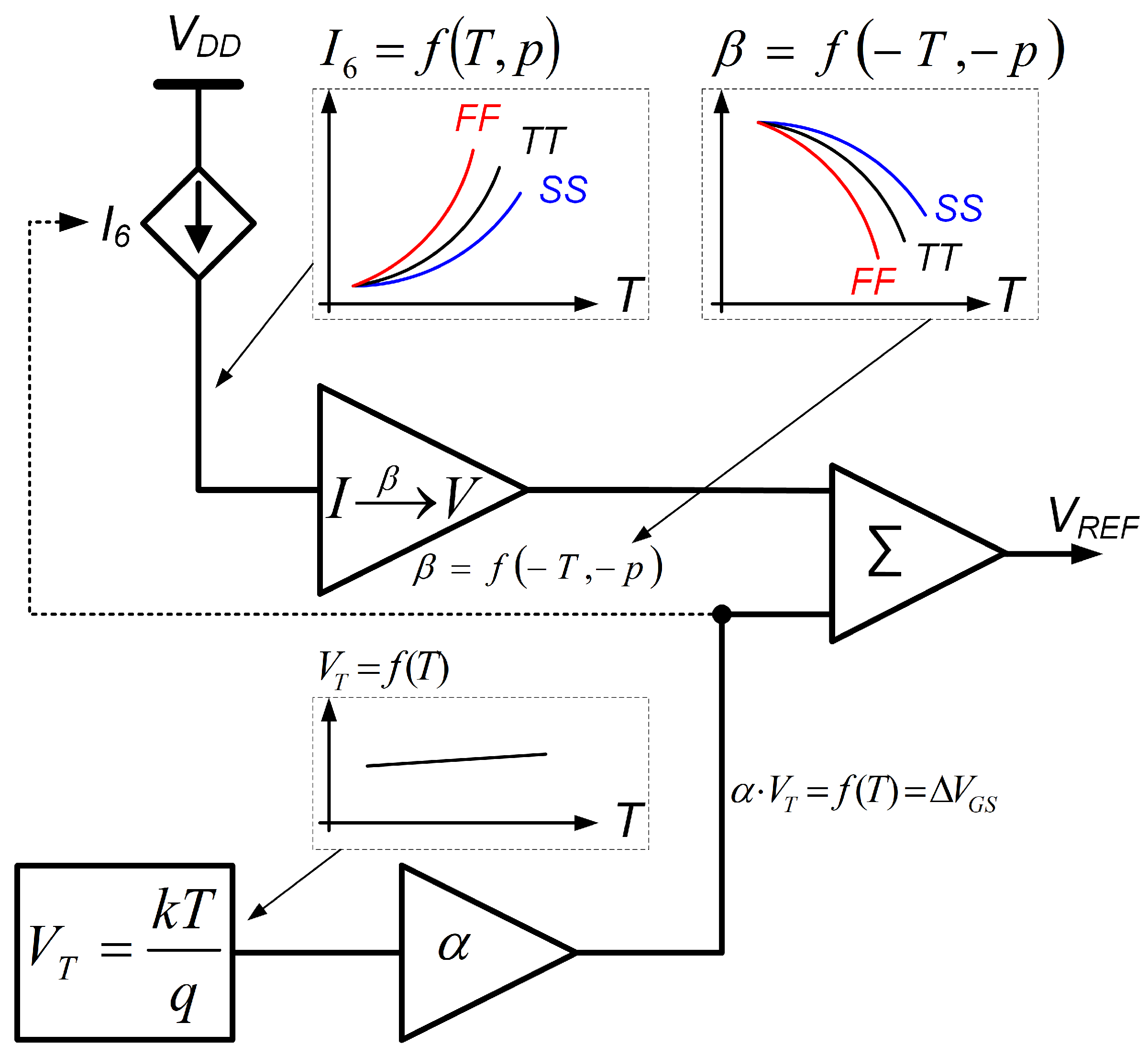

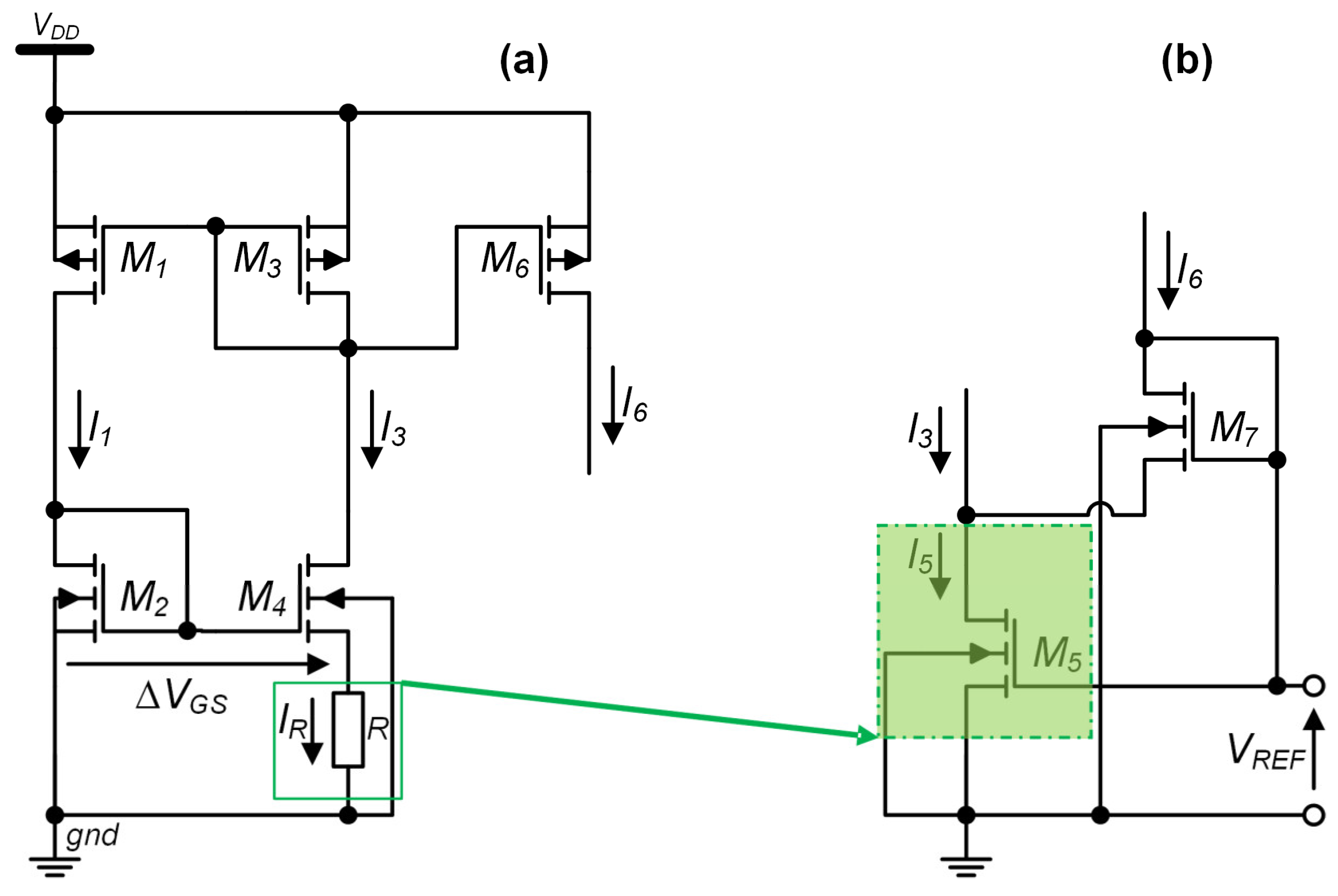

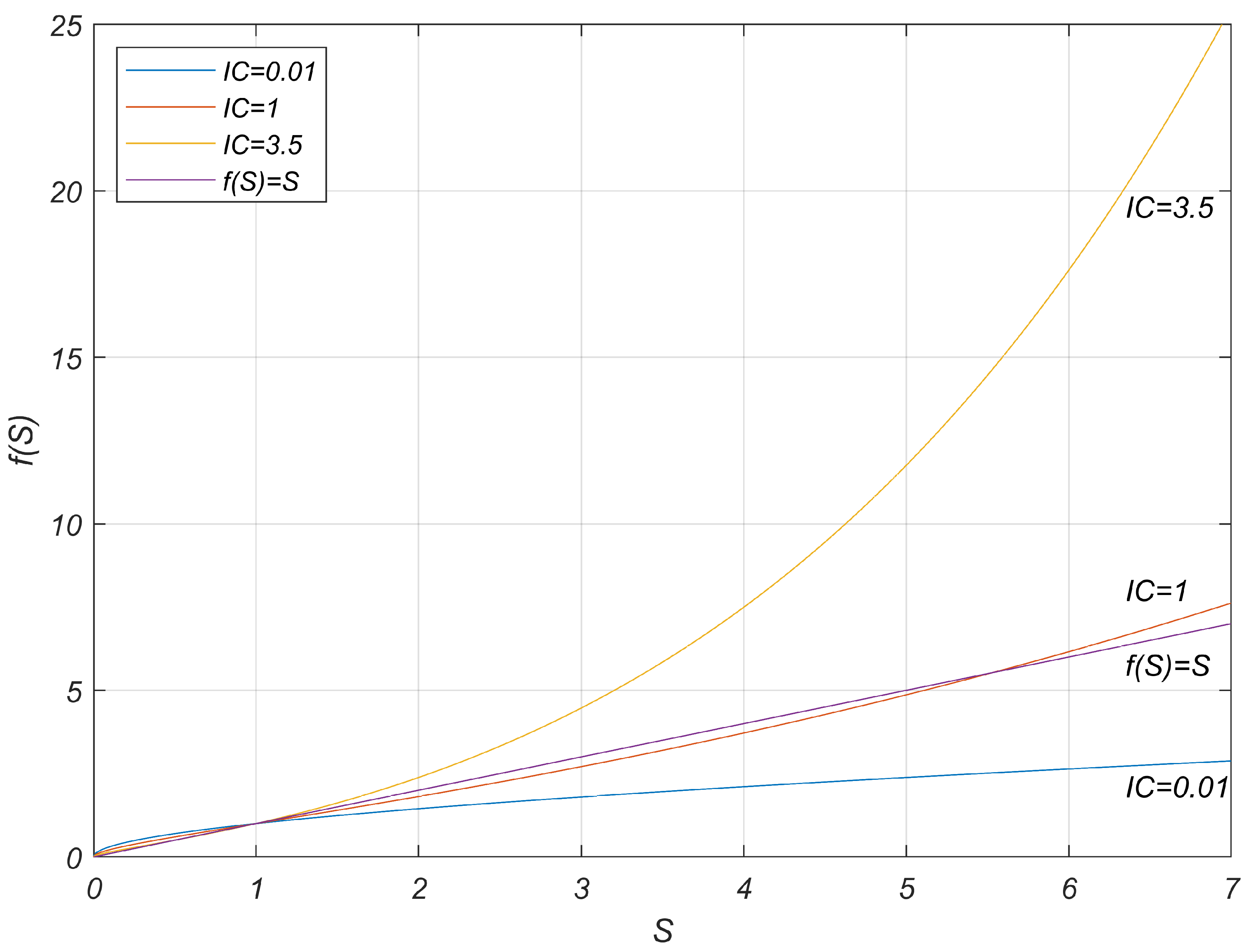

2. Known Reference Source Circuits

3. Novel Voltage–Current Reference Source Design and Principle of Operation

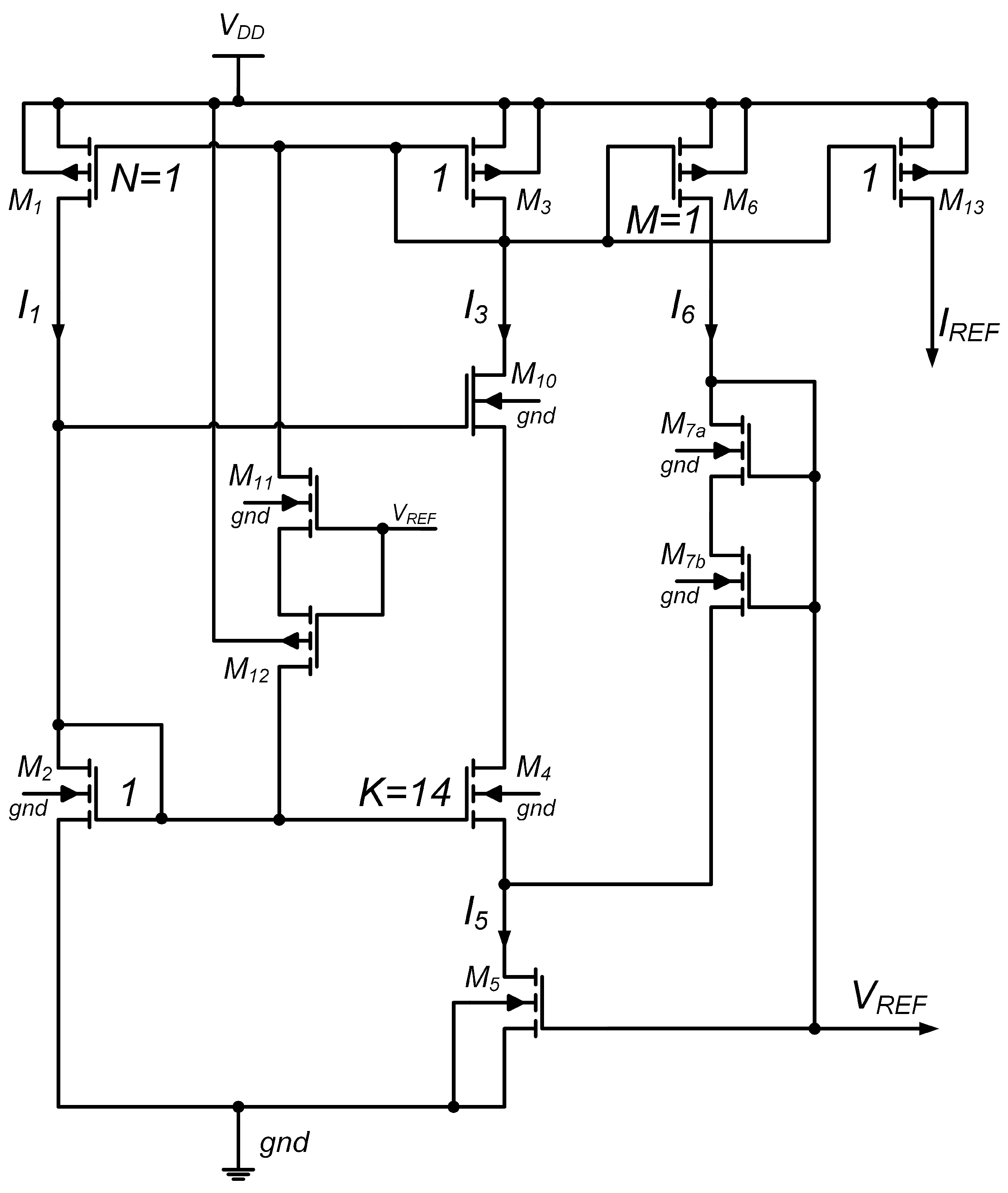

4. Example Implementation of a Novel Voltage–Current Reference Source

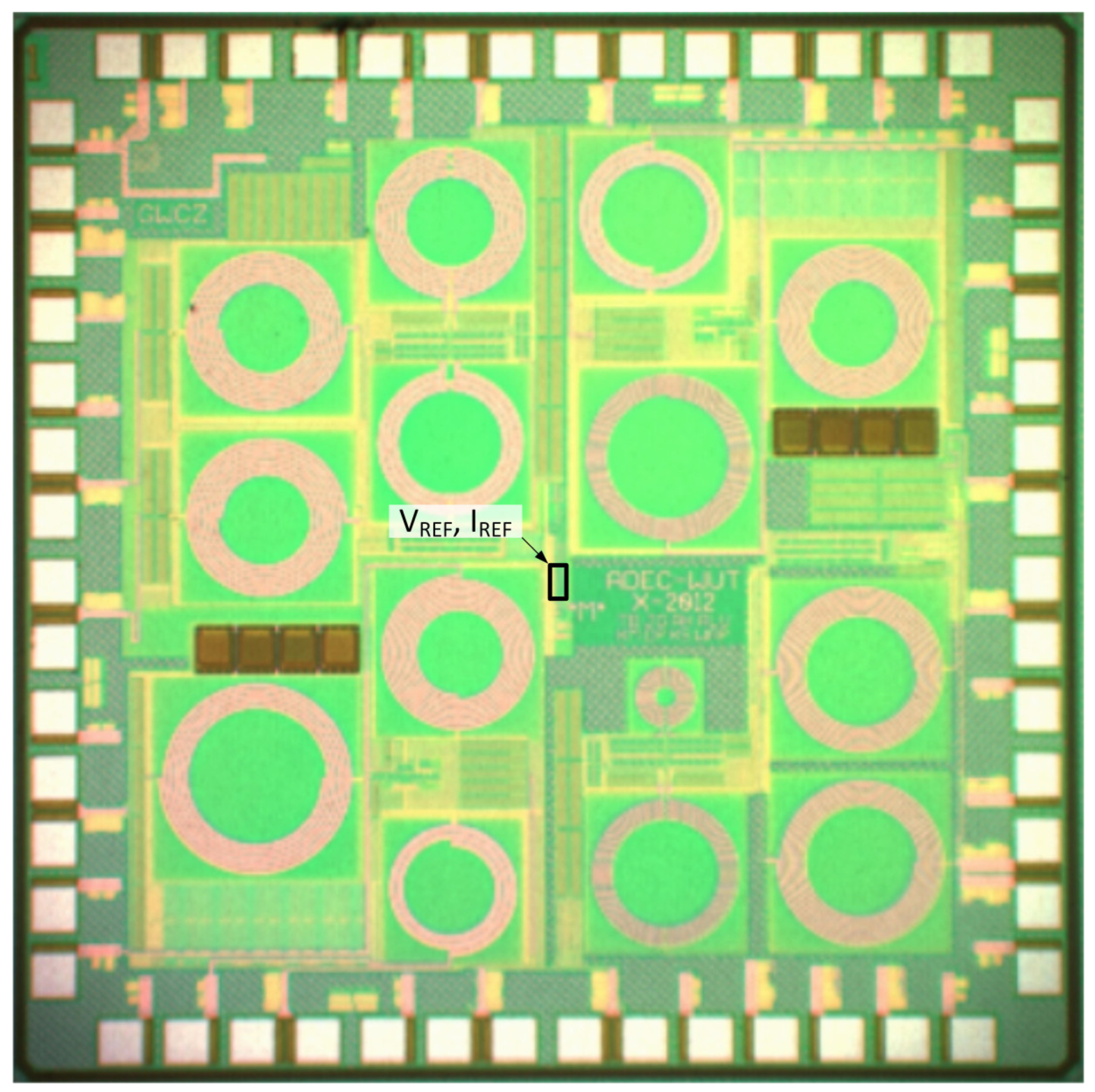

4.1. Schematic, Layout and Simulation Results of the New Voltage–Current Source

4.2. Measurement Results of the Example Implementation of a Novel Current–Voltage Source

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Widlar, R. New developments in IC voltage regulators. IEEE J. Solid-state Circuits 1971, 6, 2–7. [Google Scholar] [CrossRef]

- Pease, R. The design of band-gap reference circuits: Trials and tribulations. In Proceedings of the Bipolar Circuits and Technology Meeting, Minneapolis, MN, USA, 17–18 September 1990. [Google Scholar] [CrossRef]

- Song, B.-S.; Gray, P. A precision curvature-compensated CMOS bandgap reference. In Proceedings of the 1983 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, New York, NY, USA, 23–25 February 1983; pp. 240–241. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P. A sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE J. Solid-state Circuits 2002, 37, 526–530. [Google Scholar] [CrossRef]

- Banba, H.; Shiga, H.; Umezawa, A.; Miyaba, T.; Tanzawa, T.; Atsumi, S.; Sakui, K. A CMOS bandgap reference circuit with sub-1-V operation. IEEE J. Solid-state Circuits 1999, 34, 670–674. [Google Scholar] [CrossRef]

- Chen, Z.; Wang, Q.; Li, X.; Song, S.; Chen, H.; Song, Z. A High-Precision Current-Mode Bandgap Reference with Nonlinear Temperature Compensation. Micromachines 2023, 14, 1420. [Google Scholar] [CrossRef] [PubMed]

- Barteselli, E.; Sant, L.; Gaggl, R.; Baschirotto, A. Design Techniques for Low-Power and Low-Voltage Bandgaps. Electricity 2021, 2, 271–284. [Google Scholar] [CrossRef]

- Nagulapalli, R.; Yassine, N.; Tammam, A.A.; Barker, S.; Hayatleh, K. A 10.5 ppm/°C Modified Sub-1 V Bandgap in 28 nm CMOS Technology with Only Two Operating Points. Electronics 2024, 13, 1011. [Google Scholar] [CrossRef]

- Leung, K.N.; Mok, P. A CMOS Voltage Reference Based on Weighted ΔV/sub GS/ for CMOS Low-Dropout Linear Regulators. IEEE J. Solid-State Circuits 2003, 38, 146–150. [Google Scholar] [CrossRef]

- di Naro, G.; Lombardo, G.; Paolino, C.; Lullo, G. A Low-Power Fully-Mosfet Voltage Reference Generator for 90 nm CMOS Technology. In Proceedings of the 2006 IEEE International Conference on IC Design and Technology, Padua, Italy, 1–4 May 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Vittoz, E.; Fellrath, J. CMOS analog integrated circuits based on weak inversion operations. IEEE J. Solid-state Circuits 1977, 12, 224–231. [Google Scholar] [CrossRef]

- Lin, H.; Chang, D.-K. A Low-Voltage Process Corner Insensitive Subthreshold CMOS Voltage Reference Circuit. In Proceedings of the 2006 IEEE International Conference on IC Design and Technology, Padua, Italy, 1–4 May 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Miller, S.; MacEachern, L. A nanowatt bandgap voltage reference for ultra-low power applications. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems, Kos, Greece, 21–24 May 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Navidi, M.M.; Graham, D.W. A Low-Power Voltage Reference Cell with a 1.5 V Output. J. Low Power Electron. Appl. 2018, 8, 19. [Google Scholar] [CrossRef]

- Borejko, T.; Pleskacz, W.A. A Resistorless Voltage Reference Source for 90 nm CMOS Technology with Low Sensitivity to Process and Temperature Variations. In Proceedings of the 2008 11th IEEE International Workshop on Design and Diagnostics of Electronic Circuits and Systems (DDECS 2008), Bratislava, Slovakia, 16–18 April 2008; pp. 38–43. [Google Scholar] [CrossRef]

- Enz, C.C.; Krummenacher, F.; Vittoz, E.A. An Analytical MOS Transistor Model Valid in All Regions of Operation and Dedicated to Low-Voltage and Low-Current Applications. In Low-Voltage Low-Power Analog Integrated Circuits; Serdijn, W., Ed.; The Springer International Series in Engineering and Computer Science; Springer: Boston, MA, USA, 1995; Volume 328, pp. 83–114. [Google Scholar] [CrossRef]

- Łukaszewicz, M.; Borejko, T.; Pleskacz, W.A. A Resistorless Current Reference Source for 65 nm CMOS Technology with Low Sensitivity to Process, Supply Voltage and Temperature Variations. In Proceedings of the 2011 IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems—IEEE DDECS 2011, Cottbus, Germany, 13–15 April 2011; pp. 75–79. [Google Scholar] [CrossRef]

- Samir, A.; Girardeau, L.; Bert, Y.; Kussener, E.; Rahajandraibe, W.; Barthelemy, H. 173nA-7.5ppm/°C-771mV-0.03mm2 CMOS Resistorless Voltage Reference. In Proceedings of the 2011 Faible Tension Faible Consommation (FTFC), Marrakech, Morocco, 30 May–1 June 2011; pp. 71–74. [Google Scholar] [CrossRef]

- Vilella, E.; Diéguez, A. Design of a Bandgap Reference Circuit with Trimming for Operation at Multiple Voltages and Tolerant to Radiation in 90 nm CMOS Technology. In Proceedings of the 2010 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Lixouri, Greece, 5–7 July 2010; pp. 269–272. [Google Scholar] [CrossRef]

- Cabrini, A.; De Sandre, G.; Gobbi, L.; Malcovati, P.; Pasotti, M.; Poles, M.; Rigoni, F.; Torelli, G. A 1 V, 26 μW Extended Temperature Range Band gap Reference in 130-nm CMOS Technology. In Proceedings of the 31st IEEE European Solid-State Circuits Conference—ESSCIRC 2005, Grenoble, France, 12–16 September 2005; pp. 503–506. [Google Scholar] [CrossRef]

- Zhu, W.-r.; Yang, H.-g.; Gao, T.-q. A Novel Low Voltage Subtracting Band Gap Reference with Temperature Coefficient of 2.2 ppm/°C. In Proceedings of the 2011 IEEE International Symposium on Circuits and Systems—ISCAS 2011, Rio de Janeiro, Brazil, 15–18 May 2011; pp. 2281–2284. [Google Scholar] [CrossRef]

- Lee, J.; Cho, S.H. A 210 nW 29.3 ppm/°C 0.7 V voltage reference with a temperature range of −50 to 130 °C in 0.13 µm CMOS. In Proceedings of the 2011 Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, 15–17 June 2011; pp. 278–279. [Google Scholar]

- Han, D.-O.; Kim, J.-H.; Kim, N.-H. Design of Bandgap Reference and Current Reference Generator with Low Supply Voltage. In Proceedings of the 2008 International Conference on Solid-State and Integrated-Circuit Technology—ICSICT 2008, Beijing, China, 20–23 October 2008; pp. 1733–1736. [Google Scholar] [CrossRef]

- Tang, S.; Narendra, S.; De, V. Temperature and process invariant MOS based reference current generation circuits for sub-1 V operation. In Proceedings of the 2003 International Symposium on Low Power Electronics and Design—ISLPED ‘03, Seoul, Republic of Korea, 27 August 2003; pp. 199–204. [Google Scholar] [CrossRef]

- Bendali, A.; Audet, Y. A 1-V CMOS Current Reference With Temperature and Process Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 1424–1429. [Google Scholar] [CrossRef]

- Kelleci, B.; Karsilayan, A.I. Low-Voltage Temperature-Independent Current Reference with no External Components. In Proceedings of the IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 3836–3839. [Google Scholar] [CrossRef]

- Lee, E.K.F. Low Voltage CMOS Bandgap References with Temperature Compensated Reference Current Output. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems—ISCAS 2010, Paris, France, 30 May–2 June 2010; pp. 1643–1646. [Google Scholar] [CrossRef]

- Krishnamoorthy, H.P. Methods and Apparatuses for a CMOS-Based Process Insensitive Current Reference Circuit. U.S. Patent 9,977,454 B1, 22 May 2018. Available online: https://image-ppubs.uspto.gov/dirsearch-public/print/downloadPdf/9977454 (accessed on 18 October 2024).

| Device | M1 | M2 | M3 | M4 | M5 | M6 | M7 | M10 | M11 | M12 | M13 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Wtot [ µm] | 2 × 40 | 2 × 9 | 2 × 40 | 28 × 9 | 1.42 | 2 × 40 | 1.42 | 2 | 10 | 72 | 2 × 40 |

| L [µm] | 1 | 0.5 | 1 | 0.5 | 0.88 | 1 | 2 × 0.88 | 10 | 0.12 | 0.12 | 1 |

| IDS [µA] | 5.0 | 5.0 | 5.0 | 5.0 | 10.0 | 5.0 | 5.0 | 5.0 | 0 | 0 | 5.0 |

| Parameter | Unit | Value |

|---|---|---|

| Technology feature size | um | 130 |

| Supply current (output IREF not included) | µA | 15.0 |

| Supply voltage range | V | 0.9–2.0 |

| Temperature range | °C | −40–125 |

| Reference output current (IREF) | µA | 5.00 |

| Temperature coefficient (TCI) of IREF | ppm/°C | 280 |

| Line sensitivity of IREF (in VDD range) | % | ±4.0 |

| Process corners sensitivity of IREF | % | ±7.4 |

| IREF MC 3σ × 1000 runs Process only | µA | M = 4.99; σ = 0.06 |

| IREF MC 3σ × 1000 runs Mismatch only | µA | M = 5.01; σ = 0.26 |

| IREF MC 3σ × 1000 runs Process and Mismatch | µA | M = 5.00; σ = 0.27 |

| Noise density | ||

| @ 100 Hz | pA/√Hz | 81 |

| @ 100 kHz | pA/√Hz | 4.8 |

| 1 Hz–10 MHz | nARMS | 9.1 |

| PSRR | ||

| @ 100 Hz | dB | 128 |

| @ 10 MHz | dB | 100 |

| @ 1 GHz | dB | 66 |

| Reference output voltage (VREF) | mV | 800 |

| Temperature coefficient (TCV) of VREF | ppm/°C | 118 |

| Line sensitivity of VREF (in VDD range) | % | ±0.9 |

| Process corners sensitivity of VREF | % | ±5.2 |

| VREF MC 3σ × 1000 runs Process only | mV | M = 800; σ = 11 |

| VREF MC 3σ × 1000 runs Mismatch only | mV | M = 800; σ = 9 |

| VREF MC 3σ × 1000 runs Process and Mismatch | mV | M = 800; σ = 14 |

| Noise density | ||

| @ 100 Hz | µV/√Hz | 3.9 |

| @ 100 kHz | µV/√Hz | 0.23 |

| 1 Hz–10 MHz | µVRMS | 293 |

| PSRR | ||

| @ 100 Hz | dB | 40 |

| @ 10 MHz | dB | 10 |

| @ 1 GHz | dB | 3.5 |

| Settling time | µs | 4.7 |

| Chip area | µm2 | 1200 |

| Process Corner | IREF [µA] | TCI [ppm/°C] | VREF [mV] | TCV [ppm/°C] | IDD [µA] |

|---|---|---|---|---|---|

| SS | 4.59 | 509 | 841 | 186 | 19.1 |

| SF | 4.67 | 888 | 816 | 340 | 19.5 |

| TT | 5.00 | 280 | 800 | 118 | 20.8 |

| FS | 5.25 | 545 | 782 | 72.8 | 21.9 |

| FF | 5.33 | 390 | 758 | 54.5 | 22.2 |

| No. | Technology | VREF [V] IREF [A] | IDD [A] | VDD [V] | TC [ppm/°C] | Process Sens. [%] | Line Sens. [%] | Settling [s] | Area [µm2] |

|---|---|---|---|---|---|---|---|---|---|

| 1 | ATMEL 0.5 µm * | 1.105 V | 351 n | 1.4–7.0 | 22.0 | ±9.0 | ±2.7 | – | – |

| 2 | IBM 180 nm RF | 1.25 V | 3.21 µ | 1.4–2.0 | 52.3 | ±3.8 | ±1.2 | 2.2 µ | 14,900 |

| 3 | IBM 180 nm HV | 1.248 V | 13.1 µ | 1.4–2.0 | 213 | ±2.9 | ±1.8 | 2.0 µ | 30,700 |

| 4 | SMIC 180 nm ** | 1.244 V | 31.6 µ | 1.4–3.63 | 210 | ±1.0 | ±1.5 | 16.6 µ | 1900 |

| 5 | LFoundry 150 nm ** | 1.137 V | 24.5 µ | 1.8–3.63 | 104 | ±0.69 | ±0.6 | 6.9 µ | 13,300 |

| 6 | UMC 130 nm (1) | 784 V | 13.2 µ | 0.9–2.0 | 40.7 | ±5.2 | ±0.8 | 513 n | 1000 |

| 7 | UMC 130 nm (2) ** | 829 mV 4.82 µA | 14.46 µ | 0.9–2.0 | 118 280 | ±5.2 ±7.4 | ±0.9 ±4.0 | 4.7 µ | 1200 |

| 8 | UMC 90 nm (1) ** | 409 mV | 270 n | 0.9–3.3 | 72.4 | ±3.7 | ±3.0 | 16.3 µ | 1100 |

| 9 | UMC 90 nm (2) ** | 337 mV | 9.0 n | 0.7–3.3 | 31.5 | ±5.2 | ±1.5 | 81.9 µ | 1300 |

| 10 | UMC 90 nm (3) ** | 659 mV 845 nA | 5.7 µ | 1.0–2.0 | 53.5 185 | ±7.2 ±15 | ±1.2 ±0.9 | 80 µ | 8200 |

| Source | Process | VREF [V] IREF [A] | IDD [A] | VDD [V] | TC [ppm/°C] | Process Sens. [%] | Line Sens. [%] | Settling [s] | Area [µm2] |

|---|---|---|---|---|---|---|---|---|---|

| This work (5) | 150 nm ** | 1.137 V | 24.5 µ | 1.8–3.63 | 104 | ±0.69 | ±0.6 | 6.9 µ | 13,300 |

| This work (7) | 130 nm ** | 829 mV 4.82 µA | 14.46 µ | 0.9–2.0 | 118 280 | ±5.2 ±7.4 | ±0.9 ±4.0 | 4.7 µ | 1200 |

| This work (9) | 90 nm ** | 337 mV | 9.0 n | 0.7–3.3 | 31.5 | ±5.2 | ±1.5 | 81.9 µ | 1300 |

| [17] | 65 nm | 6.45 µA | 47 µ | 2.6–3.63 | 55 | ±3.0 | - | - | 7000 |

| [10] | 90 nm | 718 mV | 1.3 µ | 1.05–1.35 | 101 | - | ±4.1 | - | - |

| [18] | 90 nm ** | 771 mV | 173 n | 1.6–3.6 | 40 | ±2.6 | ±1.9 | - | 30,000 |

| [19] | 90 nm | 724 mV | 18.7 µ | 1.0–1.2 | 83 | ±3.9 | - | - | 19,910 |

| [13] | 130 nm | 319 mV | 80 n | 0.5 | 2.2 | ±7.8 | - | - | 250 |

| [20] | 130 nm ** | 798 mV | 26 µ | 1.0–2.0 | 6.64 | ±0.8 | ±0.2 | - | 20,000 |

| [21] | 130 nm | 602 mV | 60 µ | 1.2 | 2.2 | ±1.4 | - | - | - |

| [22] | 130 nm ** | 501 mV | 300 n | 0.7–1.8 | 29.3 | ±4.8 | ±0.2 | - | 23,000 |

| [23] | 130 nm ** | 50.2 µA | - | 1.2 | 29 | ±0.3 | - | - | 38,000 |

| [24] | 150 nm ** | 90 µA | - | 1.0 | 257 | ±5.0 | - | - | 38,000 |

| [25] | 180 nm ** | 144 µA | 83 µ | 1.0 | 185 | ±7.0 | - | - | - |

| [26] | 180 nm ** | 54.1 µA | 700 µ | 1.8 | 47.4 | - | - | - | 55,000 |

| [27] | 180 nm | 2.03 µA | 7.1 µ | 1.0 | 45 | ±15 | - | - | - |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Borejko, T.; Pleskacz, W.A. Design of Voltage–Current Reference Source in CMOS Technology. Electronics 2024, 13, 4212. https://doi.org/10.3390/electronics13214212

Borejko T, Pleskacz WA. Design of Voltage–Current Reference Source in CMOS Technology. Electronics. 2024; 13(21):4212. https://doi.org/10.3390/electronics13214212

Chicago/Turabian StyleBorejko, Tomasz, and Witold Adam Pleskacz. 2024. "Design of Voltage–Current Reference Source in CMOS Technology" Electronics 13, no. 21: 4212. https://doi.org/10.3390/electronics13214212

APA StyleBorejko, T., & Pleskacz, W. A. (2024). Design of Voltage–Current Reference Source in CMOS Technology. Electronics, 13(21), 4212. https://doi.org/10.3390/electronics13214212