Ultrathin Antenna-in-Package Based on TMV-Embedded FOWLP for 5G mm-Wave Applications

Abstract

1. Introduction

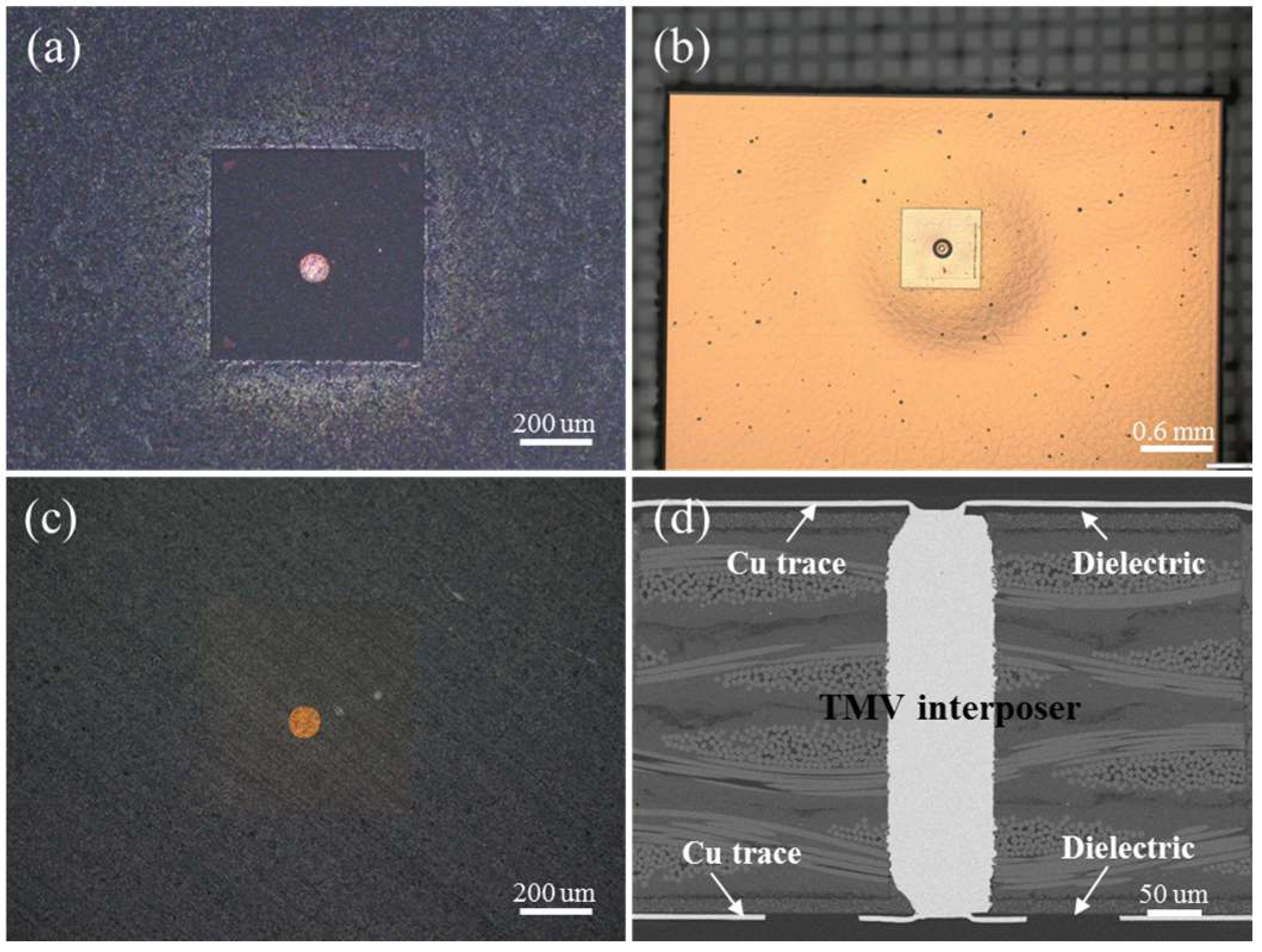

2. Process of TMV-Embedded FOWLP

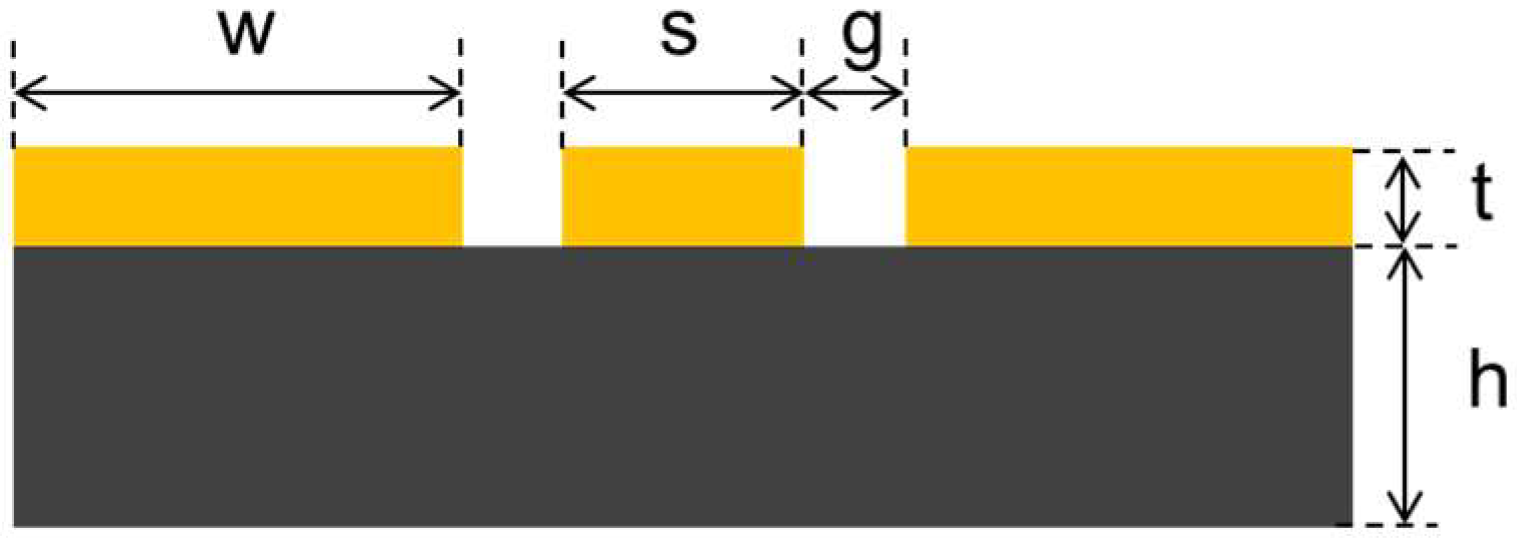

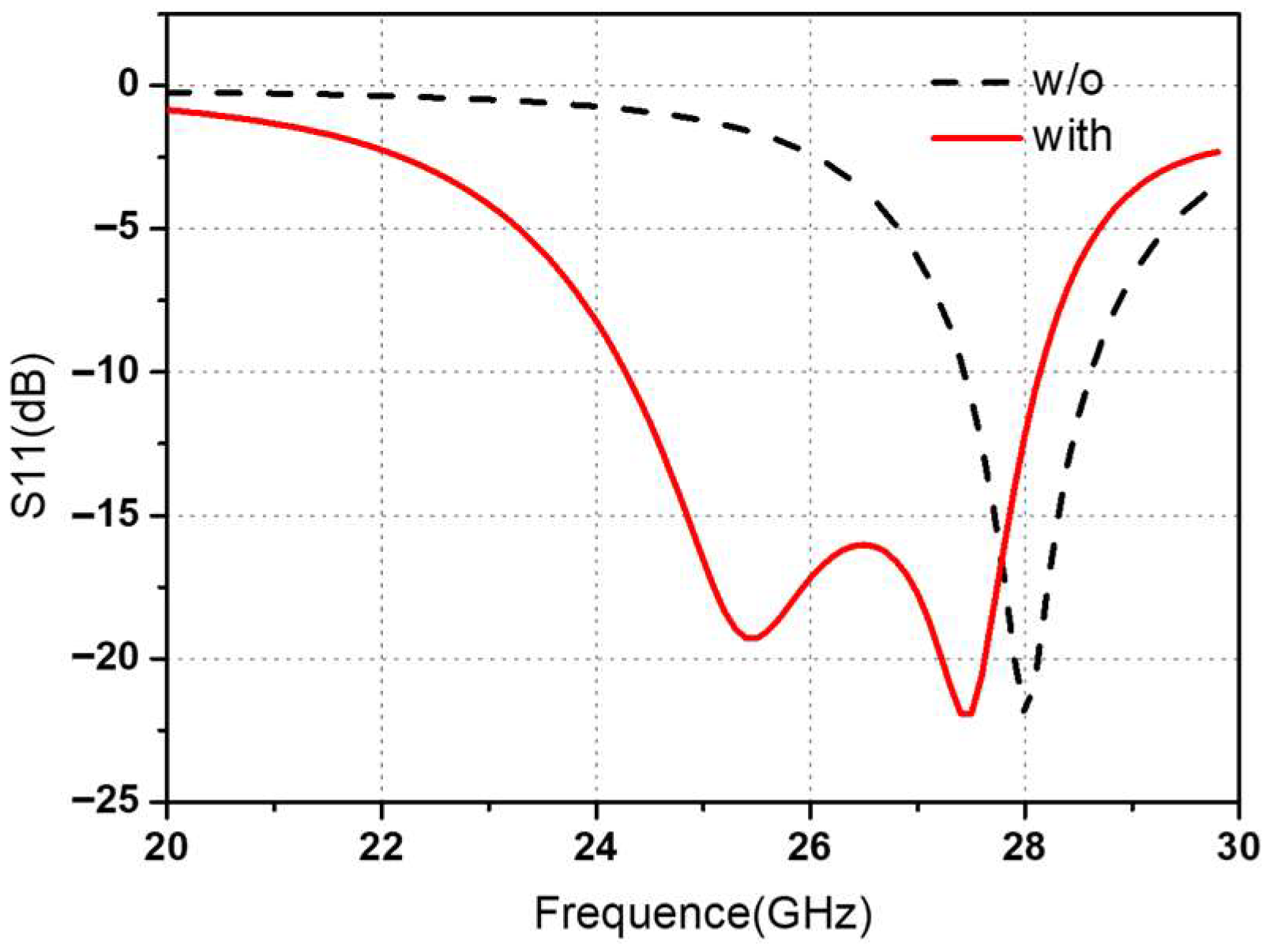

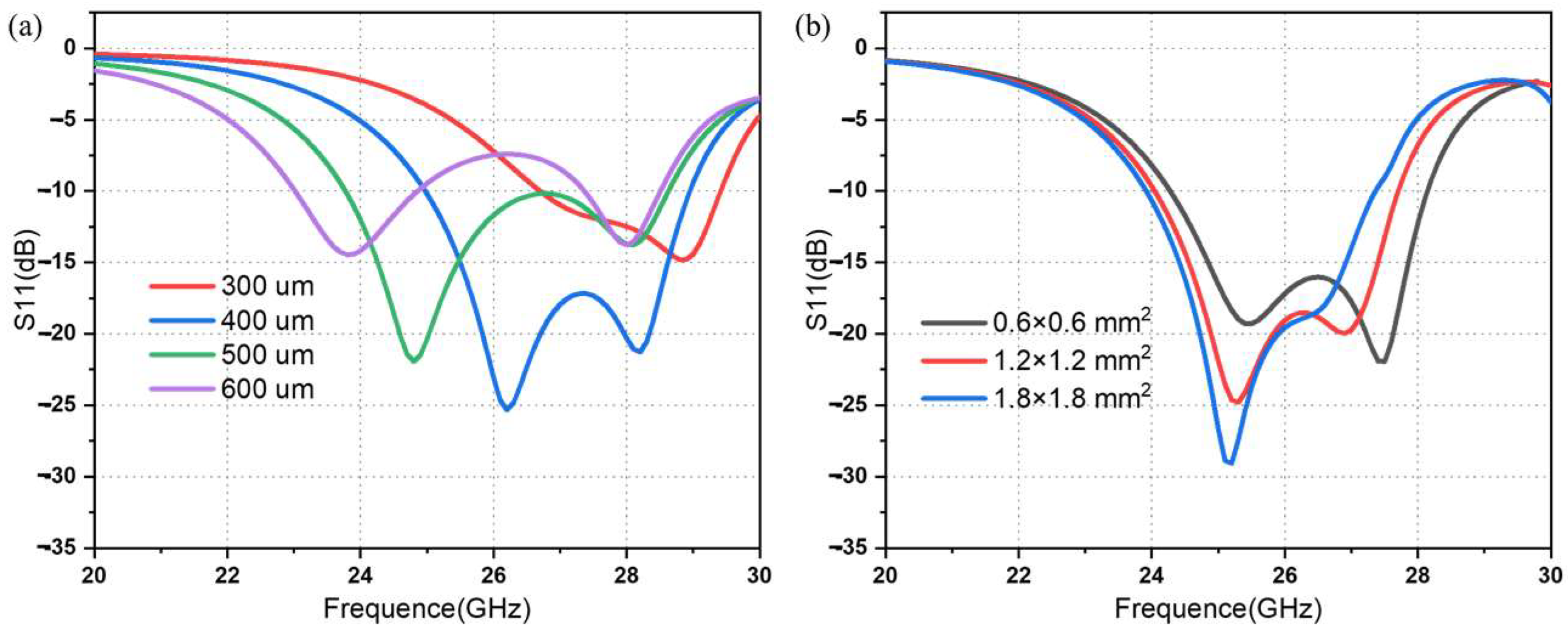

3. Antenna-in-Package Design

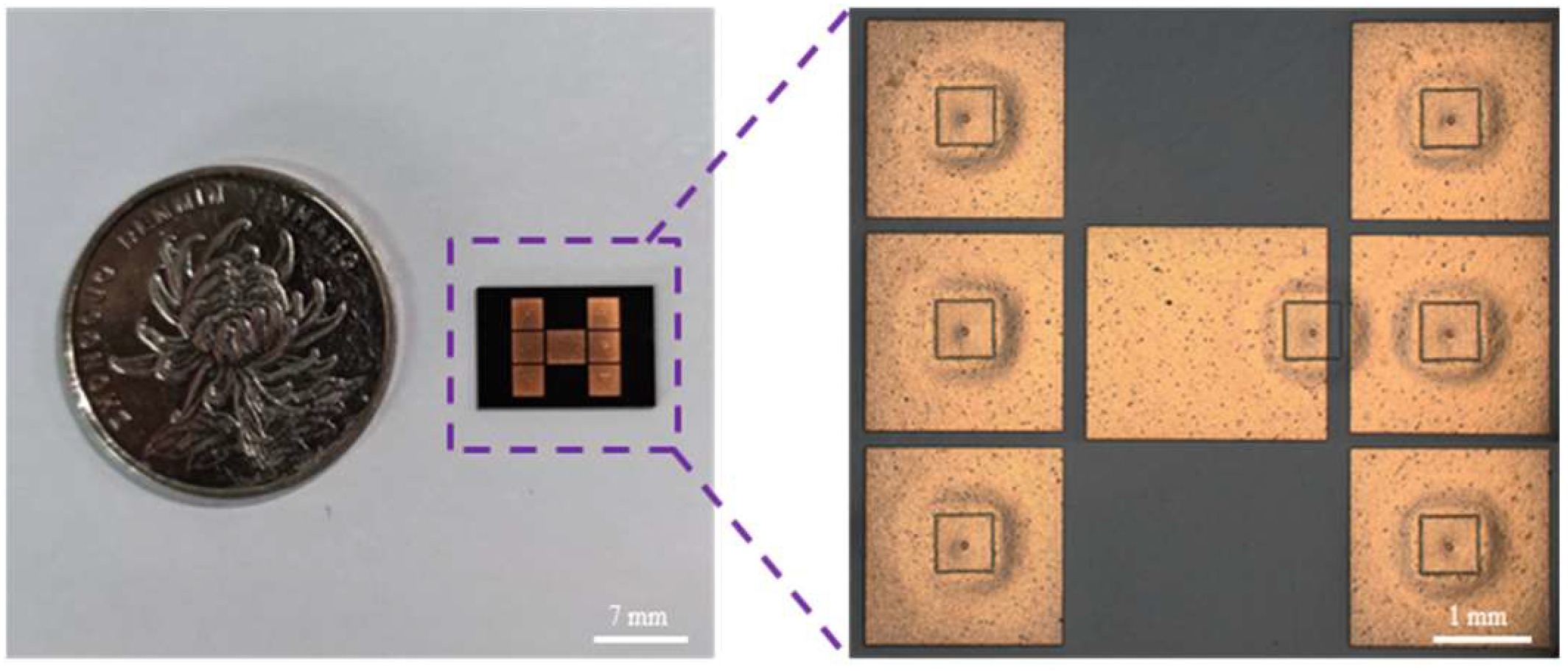

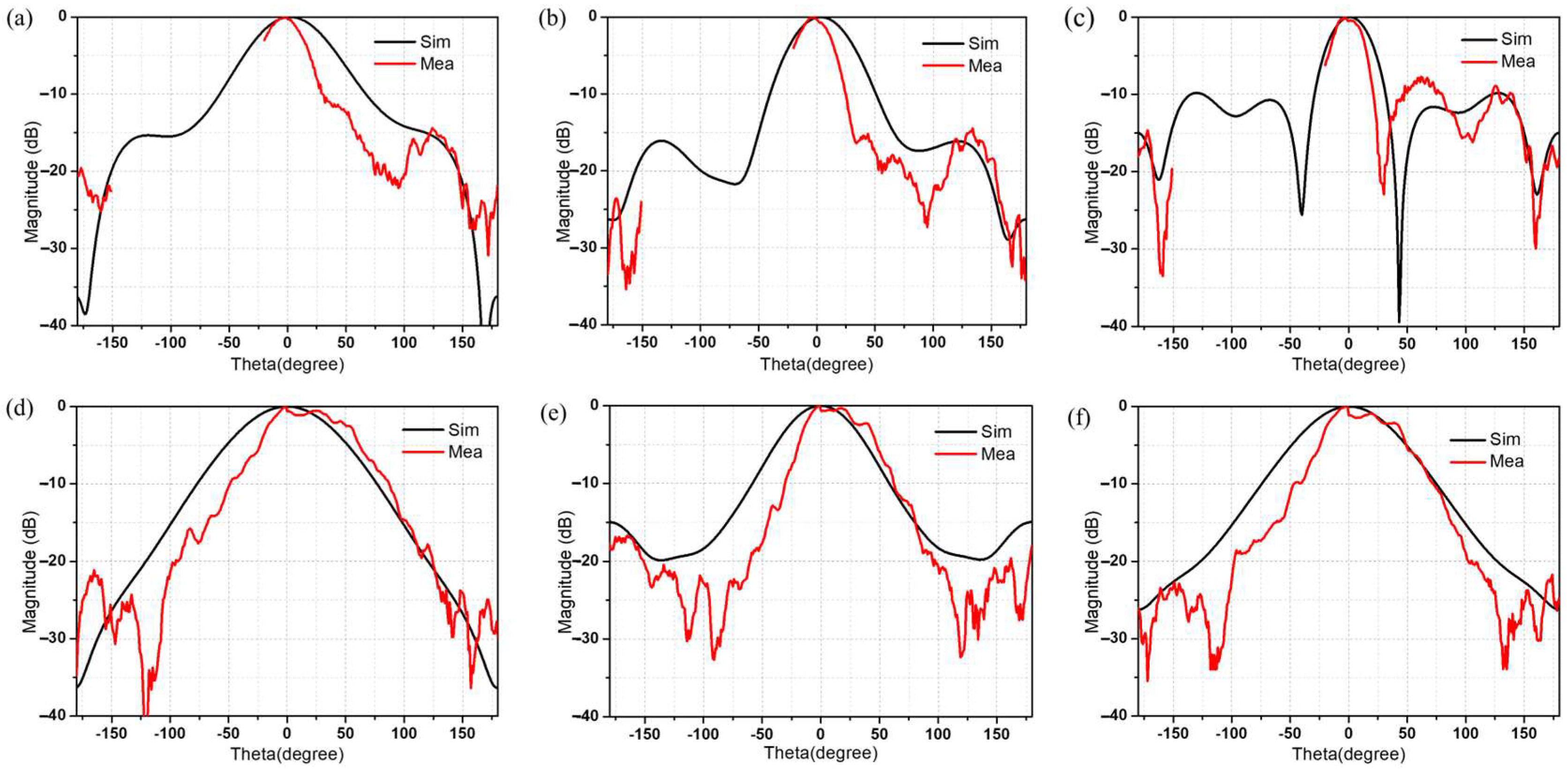

4. Antenna Performance

5. Results

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chowdhury, M.Z.; Shahjalal, M.; Ahmed, S.; Jang, Y.M. 6G wireless communication systems: Applications, requirements, technologies, challenges, and research directions. IEEE Open J. Commun. Soc. 2020, 1, 957–975. [Google Scholar] [CrossRef]

- Boric-Lubecke, O.; Lubecke, V.M.; Jokanovic, B.; Singh, A.; Shahhaidar, E.; Padasdao, B. Microwave and Wearable Technologies for 5G. In Proceedings of the 2015 12th International Conference on Telecommunication in Modern Satellite, Cable and Broadcasting Services (TELSIKS), Nis, Serbia, 14–17 October 2015; pp. 183–188. [Google Scholar]

- Huang, H.C.; Lu, J. Retrospect and Prospect on Integrations of Millimeter-Wave Antennas and Non-Millimeter-Wave Antennas to Mobile Phones. IEEE Access 2022, 10, 48904–48912. [Google Scholar] [CrossRef]

- Lin, T.H.; Kanno, K.; Watanabe, A.O.; Raj, P.M.; Tummala, R.R.; Swaminathan, M.; Tentzeris, M.M. Broadband and miniaturized antenna-in-package (AiP) design for 5G applications. IEEE Antennas Wirel. Propag. Lett. 2020, 19, 1963–1967. [Google Scholar] [CrossRef]

- Cheema, H.M.; Shamim, A. The last barrier: On-chip antennas. IEEE Microw. Mag. 2013, 14, 79–91. [Google Scholar] [CrossRef]

- Watanabe, A.O.; Ali, M.; Tehrani, B.; Hester, J.; Matsuura, H.; Ogawa, T.; Raj, P.M.; Sundaram, V.; Tentzeris, M.M.; Tummala, R.R. First Demonstration of 28 GHz and 39 GHz Transmission Lines and Antennas on Glass Substrates for 5G Modules. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 236–241. [Google Scholar]

- Enayati, A.; Vandenbosch, G.A.E.; De Raedt, W. Millimeter-wave horn-type antenna-in-package solution fabricated in a teflon-based multilayer PCB technology. IEEE Trans. Antennas Propag. 2013, 61, 1581–1590. [Google Scholar] [CrossRef]

- Wu, Y.F.; Cheng, Y.J.; Huang, Z.X. Ka-band near-field-focused 2-D steering antenna array with a focused Rotman lens. IEEE Trans. Antennas Propag. 2018, 66, 5204–5213. [Google Scholar] [CrossRef]

- Wu, Y.F.; You, Q.; Zhang, Y.; Guo, Y.; Cheng, Y.J. Sidelobe Level Reduction for a W-Band SIW Slot Array Antenna by Only Reversing Offset Direction of Partial Slots. IEEE Trans. Antennas Propag. 2023, 71, 8360–8365. [Google Scholar] [CrossRef]

- Li, Y.; Wang, C.; Guo, Y.X. A Ka-band wideband dual-polarized magnetoelectric dipole antenna array on LTCC. IEEE Trans. Antennas Propag. 2019, 68, 4985–4990. [Google Scholar] [CrossRef]

- Kam, D.G.; Liu, D.; Natarajan, A.; Reynolds, S.; Chen, H.C.; Floyd, B.A. LTCC packages with embedded phased-array antennas for 60 GHz communications. IEEE Microw. Wirel. Compon. Lett. 2011, 21, 142–144. [Google Scholar] [CrossRef]

- Gu, X.; Liu, D.; Baks, C.; Tageman, O.; Sadhu, B.; Hallin, J.; Rexberg, L.; Valdes-Garcia, A. A Multilayer Organic Package with 64 Dual-Polarized Antennas for 28GHz 5G Communication. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 1899–1901. [Google Scholar]

- Xia, H.; Zhang, T.; Li, L.; Zheng, F.C. A Low-Cost Dual-Polarized 28 GHz Phased Array Antenna for 5G Communications. In Proceedings of the 2018 International Workshop on Antenna Technology (iWAT), Nanjing, China, 5–7 March 2018; pp. 1–4. [Google Scholar]

- Wang, C.T.; Tang, T.C.; Lin, C.W.; Hsu, C.W.; Hsieh, J.S.; Tsai, C.H.; Wu, K.C.; Pu, H.P.; Yu, D. InFO_AiP Technology for High Performance and Compact 5G Millimeter Wave System Integration. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 202–207. [Google Scholar]

- Hsu, C.W.; Tsai, C.H.; Hsieh, J.S.; Yee, K.C.; Wang, C.T.; Yu, D. High Performance Chip-Partitioned Millimeter Wave Passive Devices on Smooth and Fine Pitch InFO RDL. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 254–259. [Google Scholar]

- Tsai, C.H.; Hsieh, J.S.; Liu, M.; Yeh, E.H.; Chen, H.H.; Hsiao, C.W.; Chen, C.S.; Liu, C.S.; Lii, M.J.; Wang, C.T.; et al. Array Antenna Integrated Fan-Out Wafer Level Packaging (InFO-WLP) for Millimeter Wave System Applications. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 25.1.1–25.1.4. [Google Scholar]

- Rashidian, A.; Jafarlou, S.; Tomkins, A.; Law, K.; Tazlauanu, M.; Hayashi, K. Compact 60 GHz phased-array antennas with enhanced radiation properties in flip-chip BGA packages. IEEE Trans. Antennas Propag. 2018, 67, 1605–1619. [Google Scholar] [CrossRef]

- Zhang, Y.P.; Sun, M.; Lin, W. Novel antenna-in-package design in LTCC for single-chip RF transceivers. IEEE Trans. Antennas Propag. 2008, 56, 2079–2088. [Google Scholar] [CrossRef]

- Watanabe, A.O.; Lin, T.H.; Ali, M.; Wang, Y.; Smet, V.; Raj, P.M.; Tentzeris, M.M.; Tummala, R.R.; Swaminathan, M. Ultrathin antenna-integrated glass-based millimeter-wave package with through-glass vias. IEEE Trans. Microw. Theory Tech. 2020, 68, 5082–5092. [Google Scholar] [CrossRef]

- Zhang, Y.; Mao, J. An overview of the development of antenna-in-package technology for highly integrated wireless devices. Proc. IEEE 2019, 107, 2265–2280. [Google Scholar] [CrossRef]

- Rao, V.S.; Chong, C.T.; Ho, D.; Zhi, D.M.; Choong, C.S.; Sharon, L.P.; Liang, Y.Y. Development of high density fan out wafer level package (HD FOWLP) with multi-layer fine pitch RDL for mobile applications. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 1522–1529. [Google Scholar]

- Hsieh, S.C.; Chu, F.C.; Ho, C.Y.; Wang, C.C. mmWave Antenna Design in Advanced Fan-Out Technology for 5G Application. In Proceedings of the 2019 22nd European Microelectronics and Packaging Conference & Exhibition (EMPC), Pisa, Italy, 16–19 September 2019; pp. 1–4. [Google Scholar]

- Le, T.H.; Kanitkar, A.; Rossi, M.; Ndip, I.; Braun, T.; Mueller, F.; Lang, K.D.; Wieland, M.; Goetze, C.; Halim, S.B.; et al. Dual-Band 5G Antenna Array in Fan-Out Wafer-Level Packaging (FOWLP) Technology. In Proceedings of the 2020 23rd International Microwave and Radar Conference (MIKON), Warsaw, Poland, 5–8 October 2020; pp. 157–161. [Google Scholar]

- Van Huylenbroeck, S.; Stucchi, M.; Li, Y.; Slabbekoorn, J.; Tutunjyan, N.; Sardo, S.; Iourdan, N.; Bogaerts, L.; Beirnaert, F.; Beyer, G.; et al. Small Pitch, High Aspect Ratio Via-Last TSV Module. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 43–49. [Google Scholar]

- Töpper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Nissen, N.; Schröder, H.; Yamamoto, H.; Todt, G.; Reichl, H. 3-D Thin Film Interposer Based on TGV (Through Glass Vias): An Alternative to Si-interposer. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 66–73. [Google Scholar]

- Kim, J.; Lee, K.; Park, D.; Hwang, T.; Kim, K.; Kang, D.; Kim, J.; Lee, C.; Scanlan, C.; Berry, C. Application of through Mold via (TMV) as PoP Base Package. In Proceedings of the 2008 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 1089–1092. [Google Scholar]

- Yu, B.; Qian, Z.; Lin, C.; Lin, J.; Zhang, Y.; Yang, G.; Luo, Y. A Wideband mmWave Antenna in Fan-Out Wafer Level Packaging with Tall Vertical Interconnects for 5G Wireless Communication. IEEE Trans. Antennas Propag. 2021, 69, 6906–6911. [Google Scholar] [CrossRef]

- Shibata, T.; Yoneda, S.; Li, X.; Suzuki, N.; Nonaka, T. Imprint-Through Mold via (i-TMV) with Highly-Effective Electromagnetic Interference Shielding for RF Devices. In Proceedings of the 2020 IEEE 8th Electronics System-Integration Technology Conference (ESTC), Tønsberg, Norway, 15–18 September 2020; pp. 1–4. [Google Scholar]

- Ho, S.W.; Boon, S.S.; Long, L.B.; Hsiang-Yao, H.; Choong, C.S.; Siang, S.L.P.; Chong, C.T. Double Mold Antenna in Package for 77 GHz Automotive Radar. In Proceedings of the 2020 IEEE 22nd Electronics Packaging Technology Conference (EPTC), Singapore, 2–4 December 2020; pp. 257–261. [Google Scholar]

- Long, L.B.; Ho, D.; Guan, L.T.; Yao, H.H.; Siang, L.P.; Jaafar, N. Fabrication Process Flow of Antenna-in-Package Fan-out Wafer Level Packaging. In Proceedings of the 2021 IEEE 23rd Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2021; pp. 226–230. [Google Scholar]

- Cao, Y.; Zhang, Y.; Cai, Y.; Zhang, J.; Qian, Z. Wideband and High Gain Patch Antenna Loaded with Mushroom-Type Metamaterial. In Proceedings of the 2018 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Chengdu, China, 7–11 May 2018. [Google Scholar]

- Cao, Y.; Cai, Y.; Cao, W.; Xi, B.; Qian, Z.; Wu, T.; Zhu, L. Broadband and high-gain microstrip patch antenna loaded with parasitic mushroom-type structure. IEEE Antennas Wirel. Propag. Lett. 2019, 18, 1405–1409. [Google Scholar] [CrossRef]

- Du, J.K.; So, K.; Ra, Y.; Jung, S.Y.; Kim, J.; Kim, S.Y.; Woo, S.; Kim, H.T.; Ho, Y.C.; Paik, W. Dual-Polarized Patch Array Antenna Package for 5G Communication Systems. In Proceedings of the 2017 11th European Conference on Antennas and Propagation (EUCAP), Paris, France, 19–24 March 2017; pp. 3493–3496. [Google Scholar]

- Luo, Y.; Xu, J.; Chen, Y.; Sun, Y.; Xu, B.; Xu, S.; Yang, G. A Zero-Mode Induced mmWave Patch Antenna with low-Profile, Wide-Bandwidth and Large-angle Scanning for 5G Mobile Terminals. IEEE Access 2019, 7, 177607–177615. [Google Scholar] [CrossRef]

- Guo, G.; Wu, L.S.; Zhang, Y.P.; Mao, J.F. Stacked Patch Array in LTCC for 28 GHz Antenna-in-Package Applications. In Proceedings of the 2017 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Haining, China, 14–16 December 2017; pp. 1–3. [Google Scholar]

- Hwang, I.J.; Jo, H.W.; Kim, J.W.; Kim, G.; Yu, J.W.; Lee, W.W. Vertically Stacked Folded Dipole Antenna Using Multi-Layer for mm-Wave Mobile Terminals. In Proceedings of the 2017 IEEE International Symposium on Antennas and Propagation & USNC/URSI National Radio Science Meeting, San Diego, CA, USA, 9–14 July 2017; pp. 2579–2580. [Google Scholar]

- Ahn, K.; Park, J.; Lee, B.; Kang, L.; Kim, J.; Shin, K.; Kim, S.H.; Lee, J.D.; Kim, M.K.; Lee, H.S. Chip-Last FOWLP Based Antenna-in-Package (FO-AiP) for 5G mmWave Application. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; pp. 1384–1389. [Google Scholar]

| Parameter | Value (mm) | Parameter | Value (mm) |

|---|---|---|---|

| L1 | 2.841 | c | 0.272 |

| W1 | 2.519 | h | 0.45 |

| L2 | 1.255 | d | 0.1 |

| a | 2.333 | W | 9.018 |

| b | 0.185 | L | 13.128 |

| Work | Technique | Frequency (GHz) | Number of Layer | Thickness (λ0) | FWB (%) | Gain (dBi) | Antenna Type |

|---|---|---|---|---|---|---|---|

| [33] | HDI | 27.5–29.5 | 8 | 0.072 | 7.01% | 4.0 | Patch |

| [34] | PCB | 23.5–28 | 3 | 0.044 | 17.4% | 6.0 | Patch |

| [27] | FOWLP | 25–43 | 2 | 0.119 | 64.3% | 5.0 | ME dipole |

| [35] | LTCC | 26.3–29.8 | 10 | 0.090 | 12.4% | 3.1 | Patch |

| [36] | PCB | 27.5–29.5 | 10 | 0.076 | 9.3% | 5.7 | Yagi-Uda |

| [37] | FOWLP | 26.5–29.7 | 2 | 0.042 | 12.1% | 5.3 | Patch |

| This work | TMV-embedded FOWLP | 24.2–28.5 | 1 | 0.040 | 17.8% | 7.5 | Patch |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yin, Y.; Xia, C.; Liu, S.; Zhang, Z.; Chen, C.; Wang, G.; Wang, C.; Wu, Y. Ultrathin Antenna-in-Package Based on TMV-Embedded FOWLP for 5G mm-Wave Applications. Electronics 2024, 13, 839. https://doi.org/10.3390/electronics13050839

Yin Y, Xia C, Liu S, Zhang Z, Chen C, Wang G, Wang C, Wu Y. Ultrathin Antenna-in-Package Based on TMV-Embedded FOWLP for 5G mm-Wave Applications. Electronics. 2024; 13(5):839. https://doi.org/10.3390/electronics13050839

Chicago/Turabian StyleYin, Yuhang, Chenhui Xia, Shuli Liu, Zhimo Zhang, Chen Chen, Gang Wang, Chenqian Wang, and Yafei Wu. 2024. "Ultrathin Antenna-in-Package Based on TMV-Embedded FOWLP for 5G mm-Wave Applications" Electronics 13, no. 5: 839. https://doi.org/10.3390/electronics13050839

APA StyleYin, Y., Xia, C., Liu, S., Zhang, Z., Chen, C., Wang, G., Wang, C., & Wu, Y. (2024). Ultrathin Antenna-in-Package Based on TMV-Embedded FOWLP for 5G mm-Wave Applications. Electronics, 13(5), 839. https://doi.org/10.3390/electronics13050839