A Fast Repetitive Control Strategy for a Power Conversion System

Abstract

1. Introduction

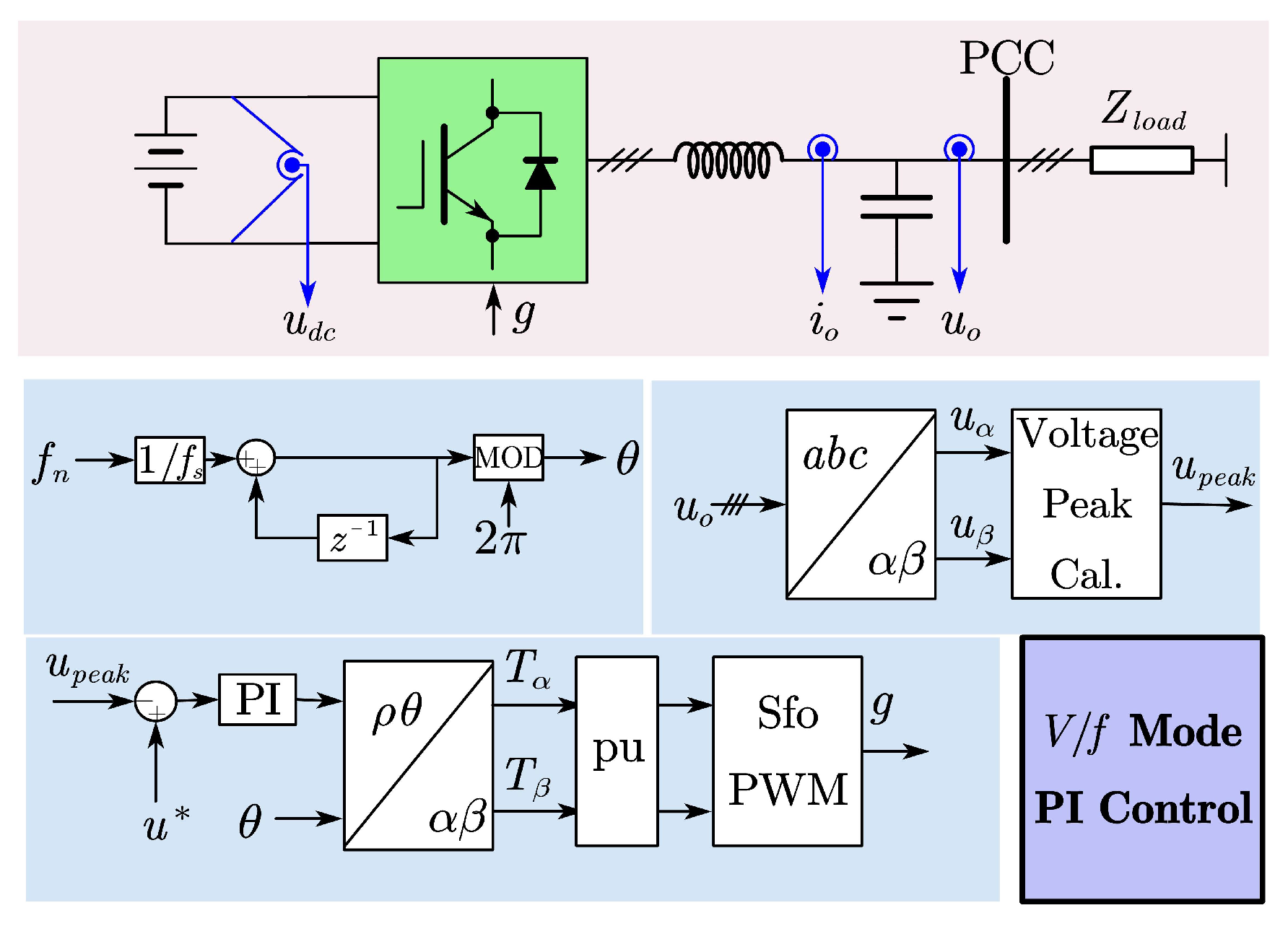

- Proportional–Integral (PI) Control: Using dq coordinate systems, PI control achieves voltage regulation but lacks harmonic suppression and the capability of operating with unbalanced loads. If it is necessary to add harmonic suppression, and in order to cope with three-phase unbalanced loads on top of PI control, an additional VPI controller is required [8,9]. This approach requires the design of additional parameters, greatly increasing the design complexity, which is not conducive to engineering implementation.

- Proportional Resonant (PR)/Quasi-Proportional Resonant (QPR) Control [10]: Based on internal model principles and utilizing abc or coordinate systems, PR/QPR control regulates output voltage without harmonic suppression. Its ability to independently control three-phase voltages allows operation with unbalanced loads.

- Proportional Multiresonant Control (PMR) [11]: As an enhanced version of PR control, PMR control consists of multiple PR controllers in parallel, providing both harmonic suppression and the capability of operating with unbalanced loads. However, its structure is complex, requiring the tuning of multiple control parameters.

- Repetitive control (RC) [12]: Also based on internal model principles, RC control is simple in structure and capable of harmonic suppression and operation with unbalanced loads. However, its dynamic performance may be less favorable. To address the dynamic performance issues of repetitive control, some scholars have proposed odd repetitive control [13], which speeds up the dynamic performance but lacks the suppression of even harmonics.

- Model Predictive Control (MPC) [14,15]: Carrier-based modulated MPC strategies have demonstrated potential for harmonic suppression and operation with unbalanced loads. However, effective MPC controller design requires careful consideration of dynamic system characteristics, constraints, performance metrics, and computational complexity.

- Robust Control [16,17]: Exhibiting strong robustness, robust control requires a good understanding of system uncertainties and the careful selection of weighting functions. Experimental and simulation methods may be necessary to validate and adjust robust control strategies for reliable application.

- Sliding Mode Control (SMC) [18,19]: Leveraging strong robustness and nonlinear characteristics, the SMC exhibits capabilities for harmonic suppression and operation with unbalanced loads. However, in practical applications, precise modeling of system dynamics and careful adjustment of controller parameters are essential. Additionally, SMC may introduce high-frequency oscillations, necessitating appropriate design and tuning to balance system performance and stability.

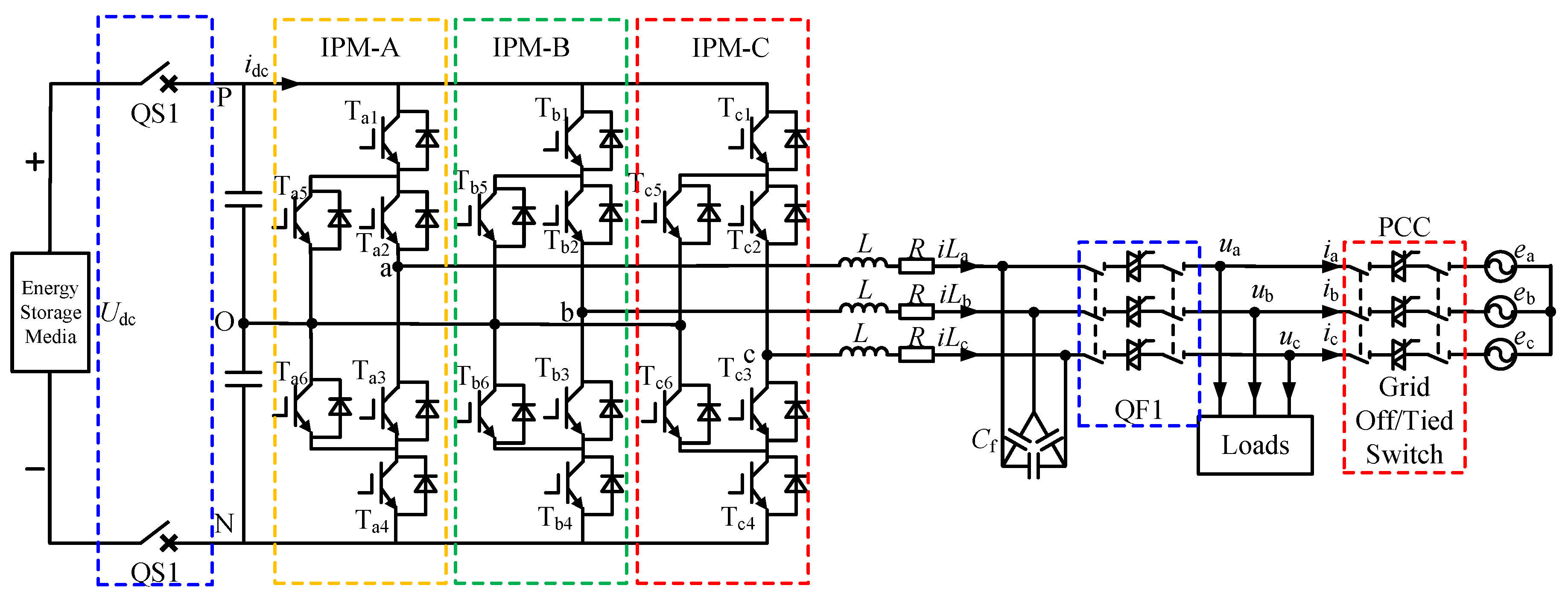

2. ANPC Three-Level PCS Modeling

- Enhanced power quality and increased power density: With higher output levels, the output voltage waveform is closer to sinusoidal, improving the power quality of the output waveform. This design also reduces the size of the filter and increases the power density of the system, especially under the same switching frequency [21].

- Improved efficiency: The three-level structure primarily utilizes the Neutral Point Clamped (NPC) topology, which includes I-type NPC, T-type NPC, and ANPC (Active Neutral Point Clamped) [22].

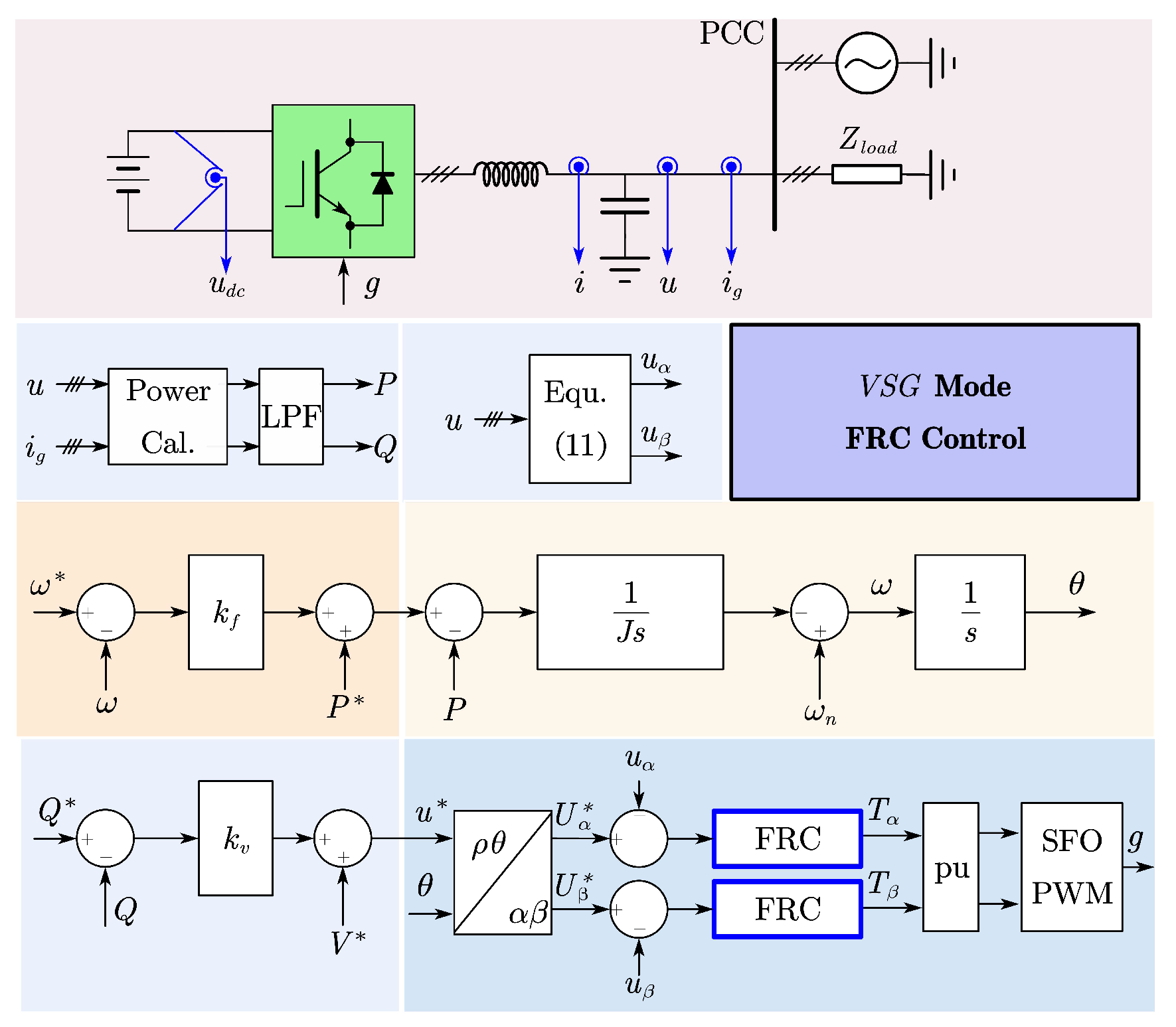

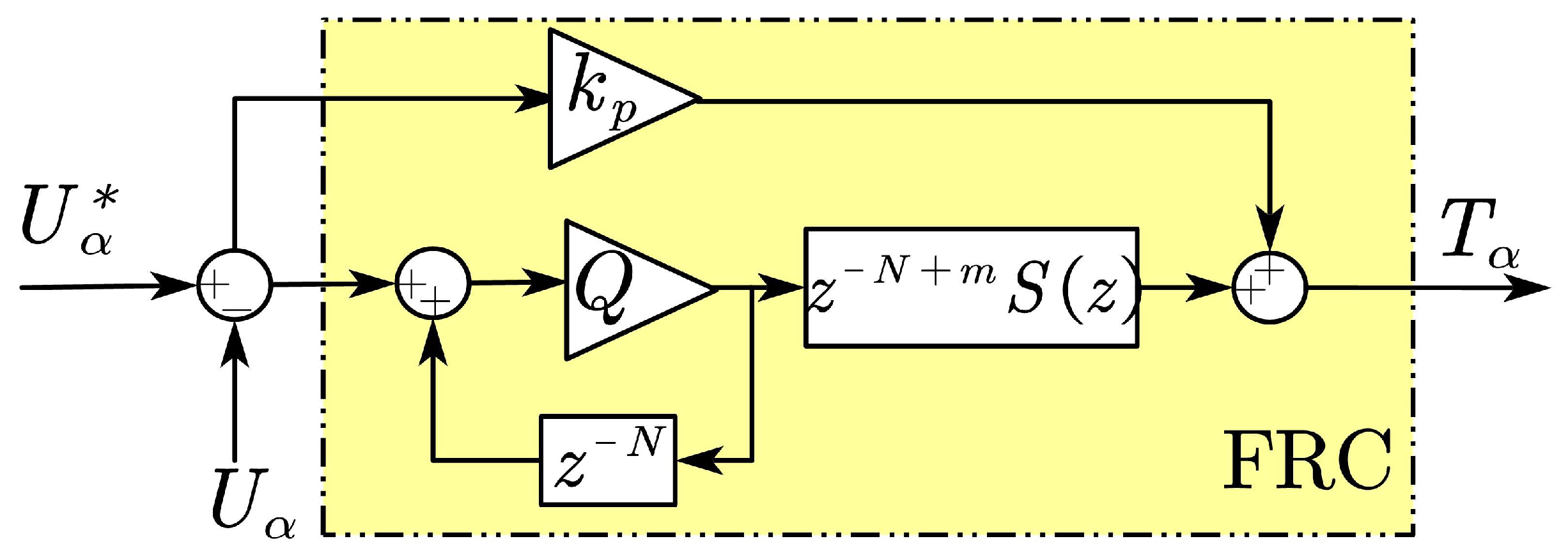

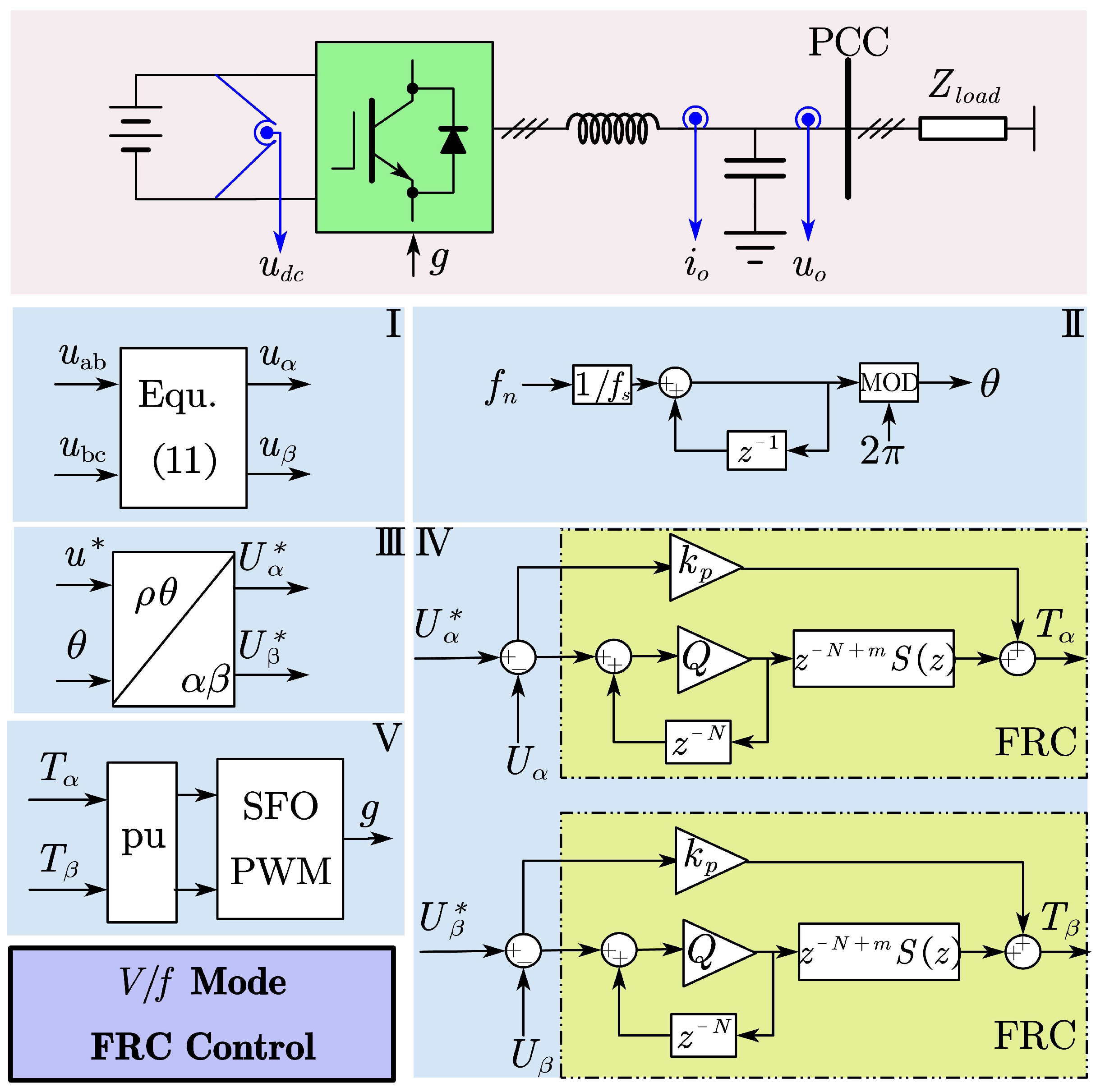

3. The Proposed Scheme

4. Parameter Design and Analysis of the Proposed FRC

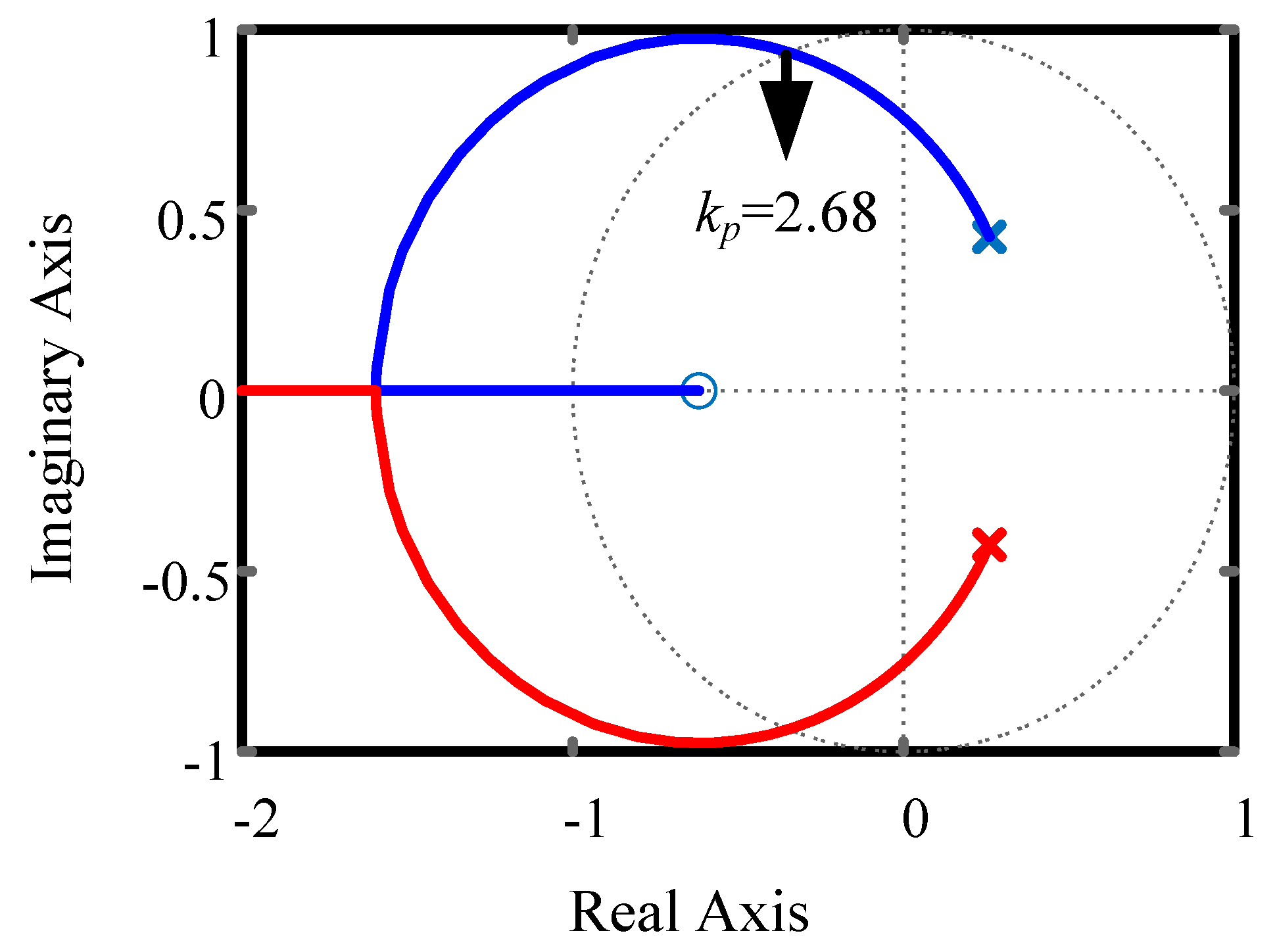

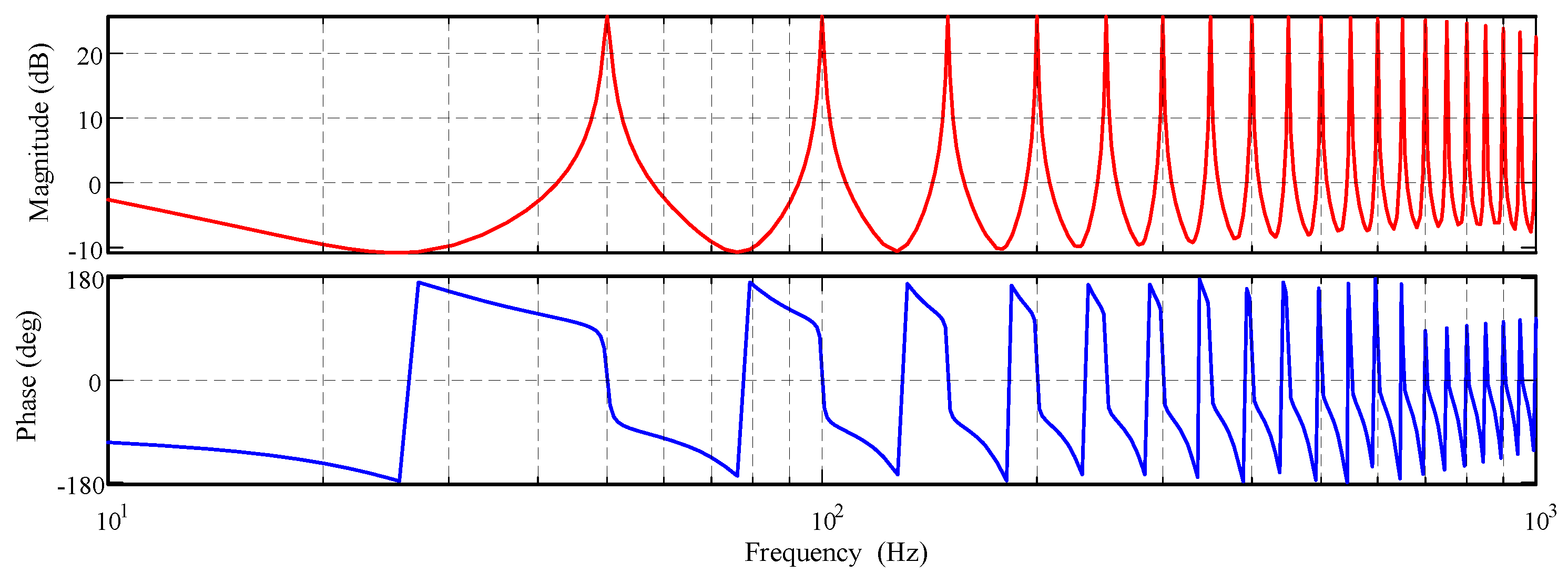

4.1. Stability Analysis

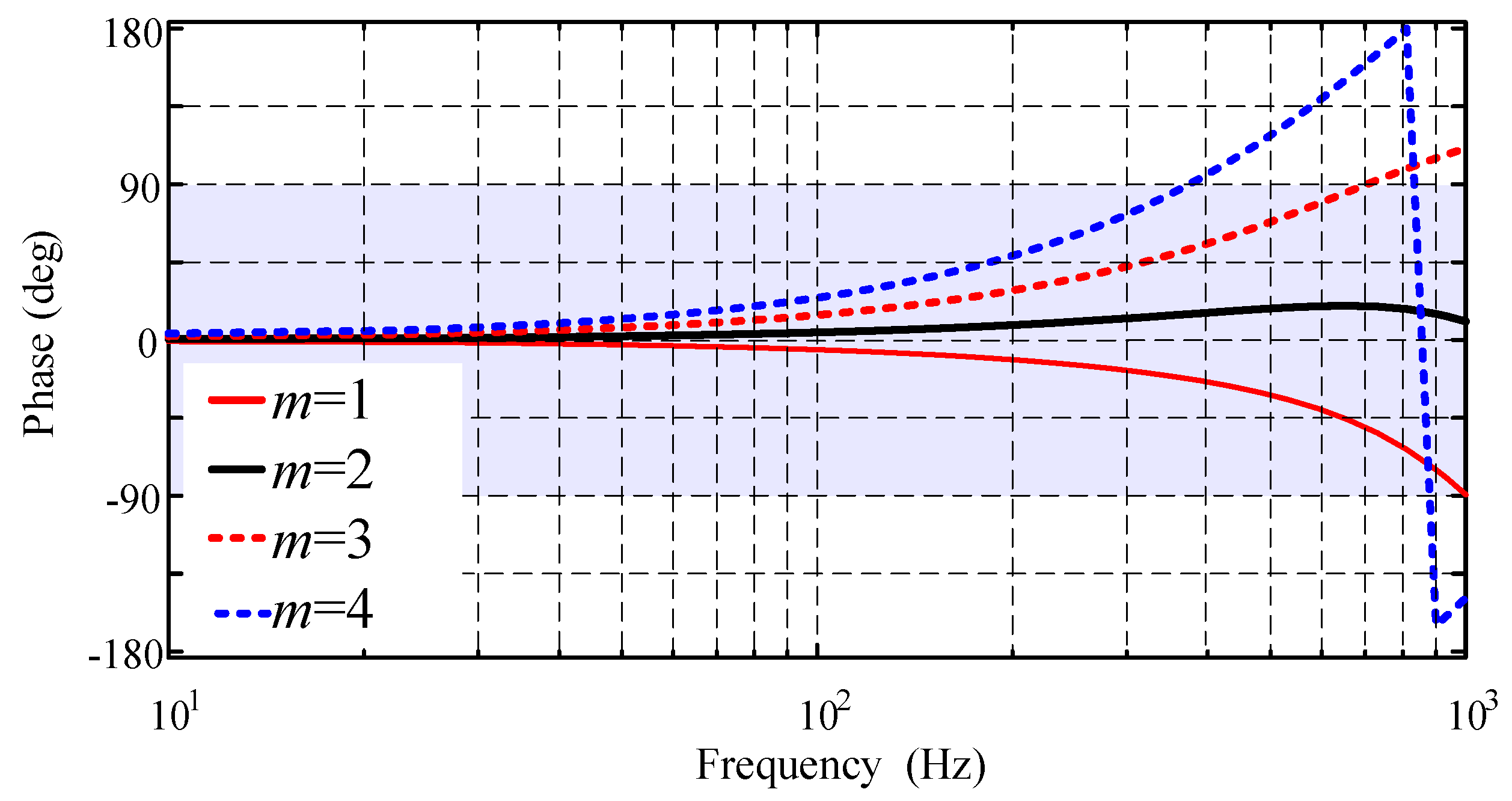

4.2. Parameter Design of an FRC

4.2.1. FRC Gain Coefficient

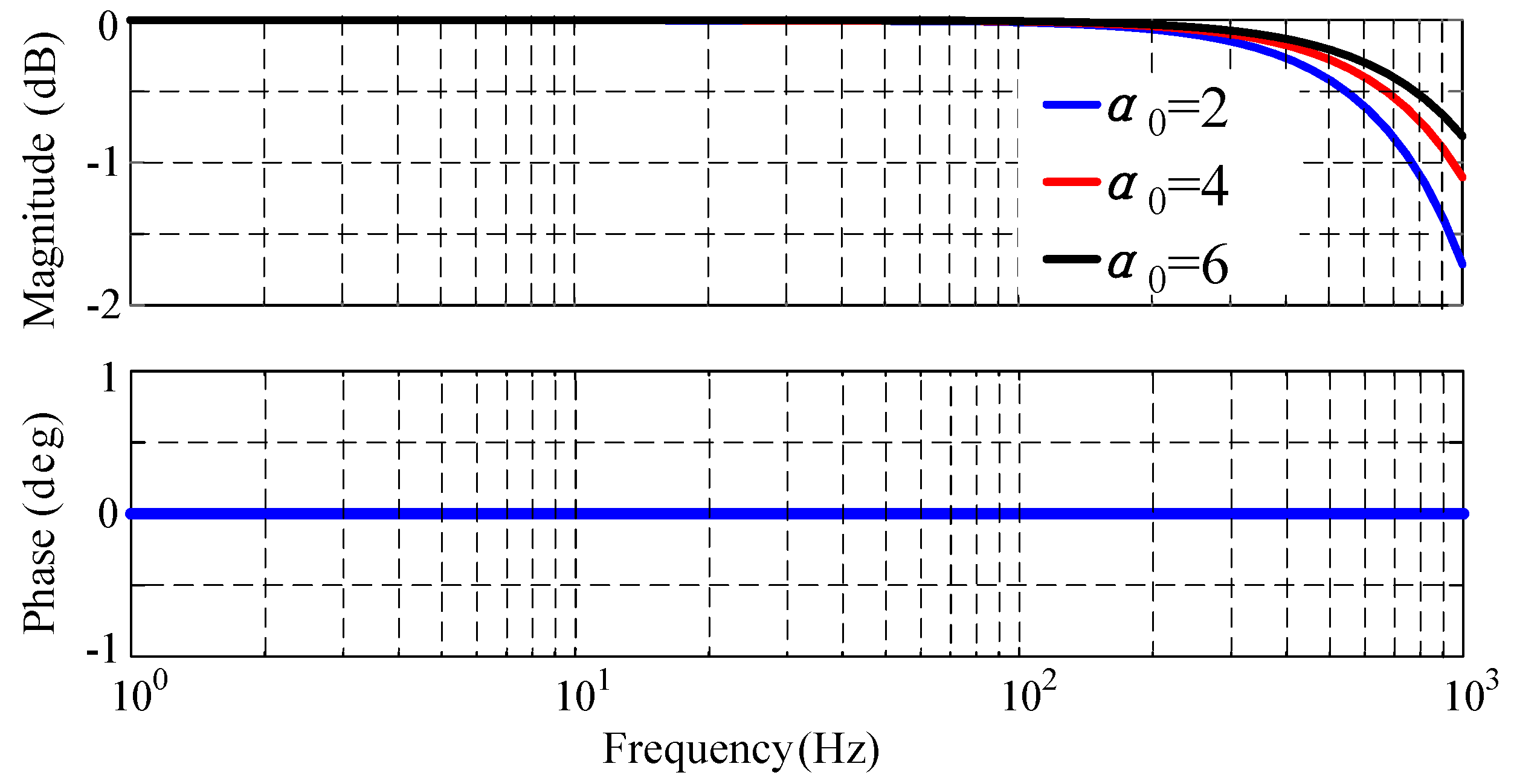

4.2.2. FRC Internal Model Coefficient Q

4.2.3. FRC Compensator

4.2.4. FRC Phase Lead Compensation

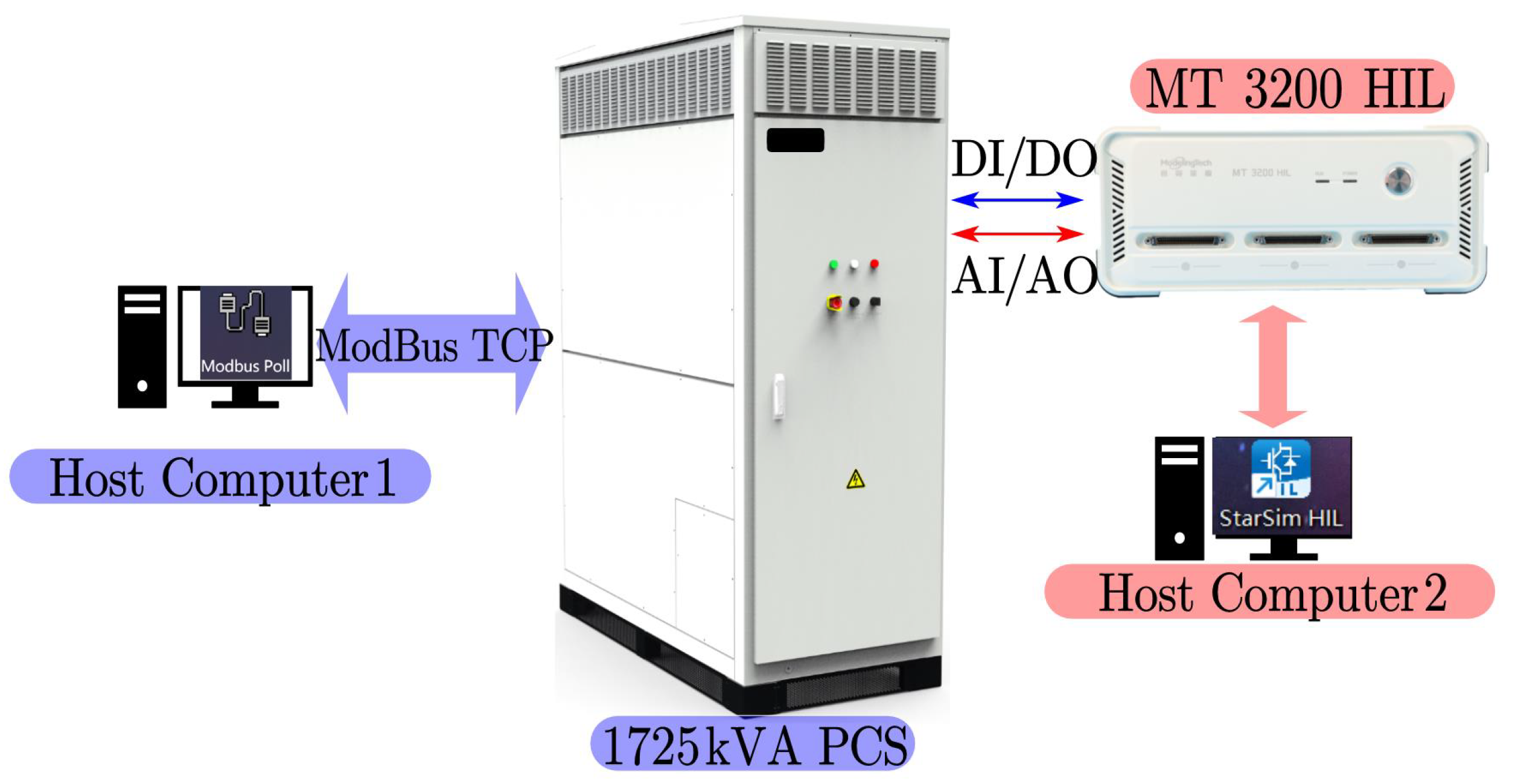

5. Experimental Results

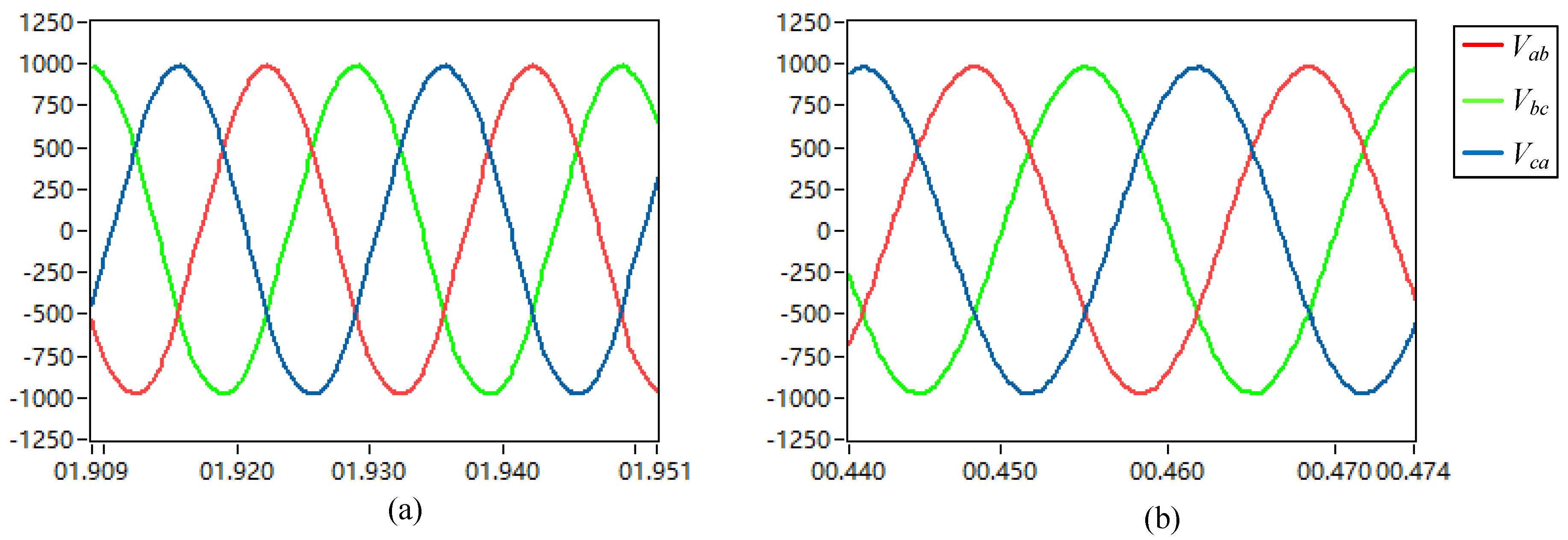

5.1. No-Load Experiment

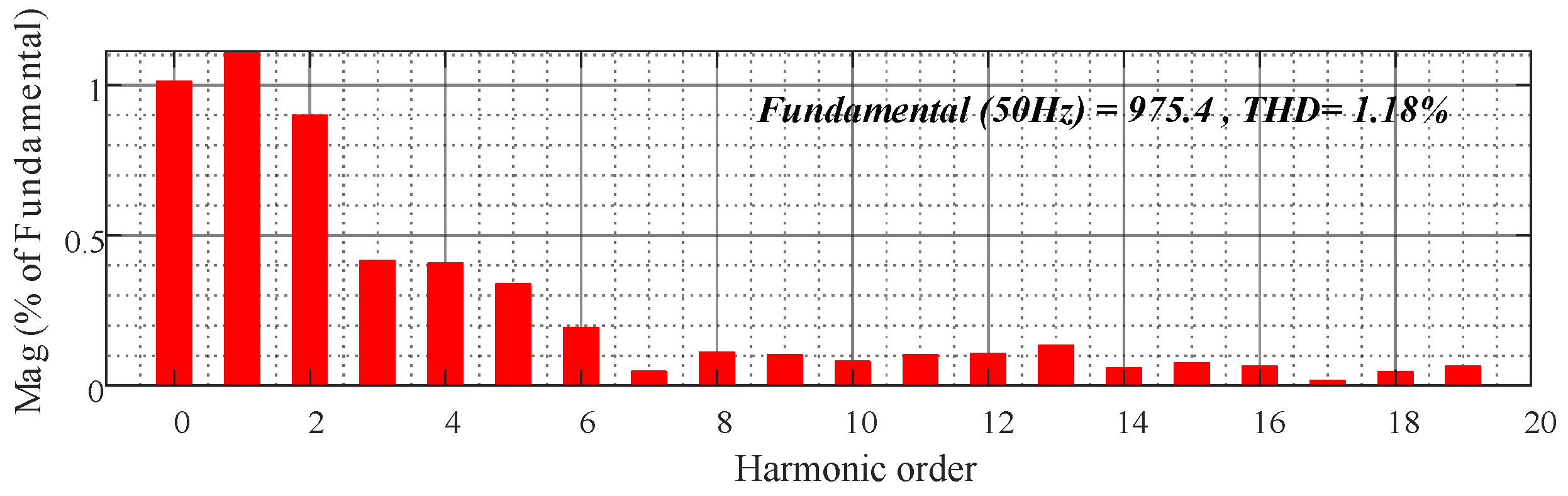

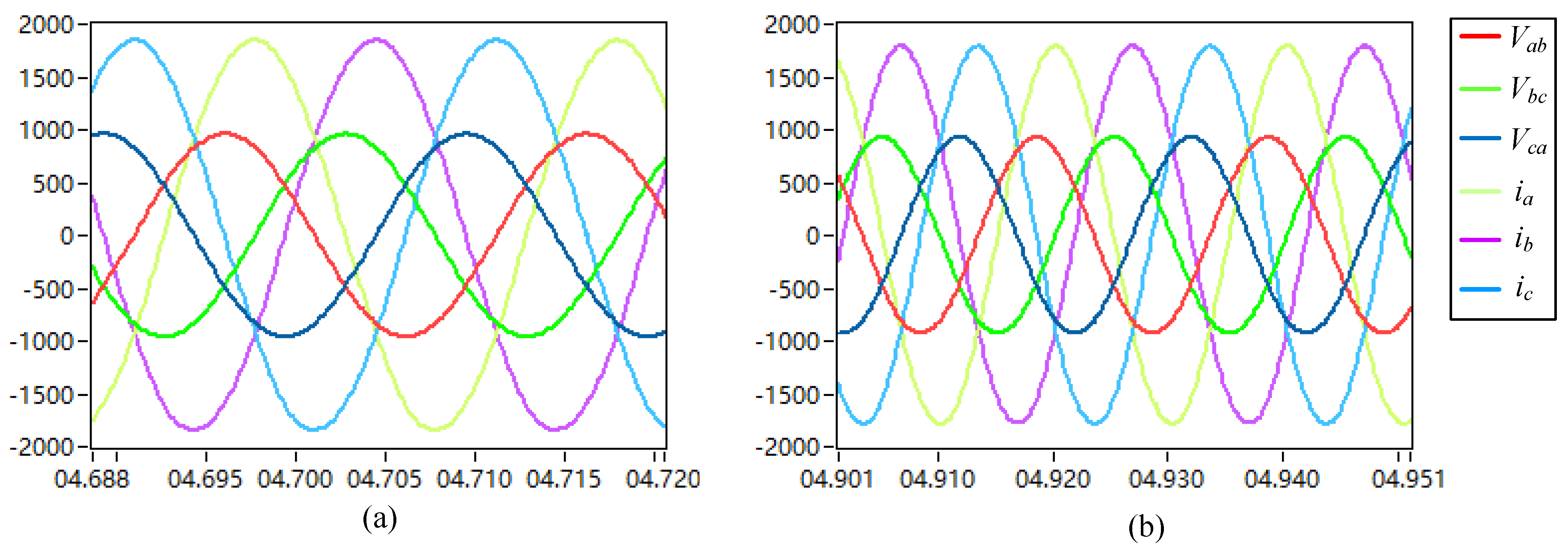

5.2. Full-Load Experiment

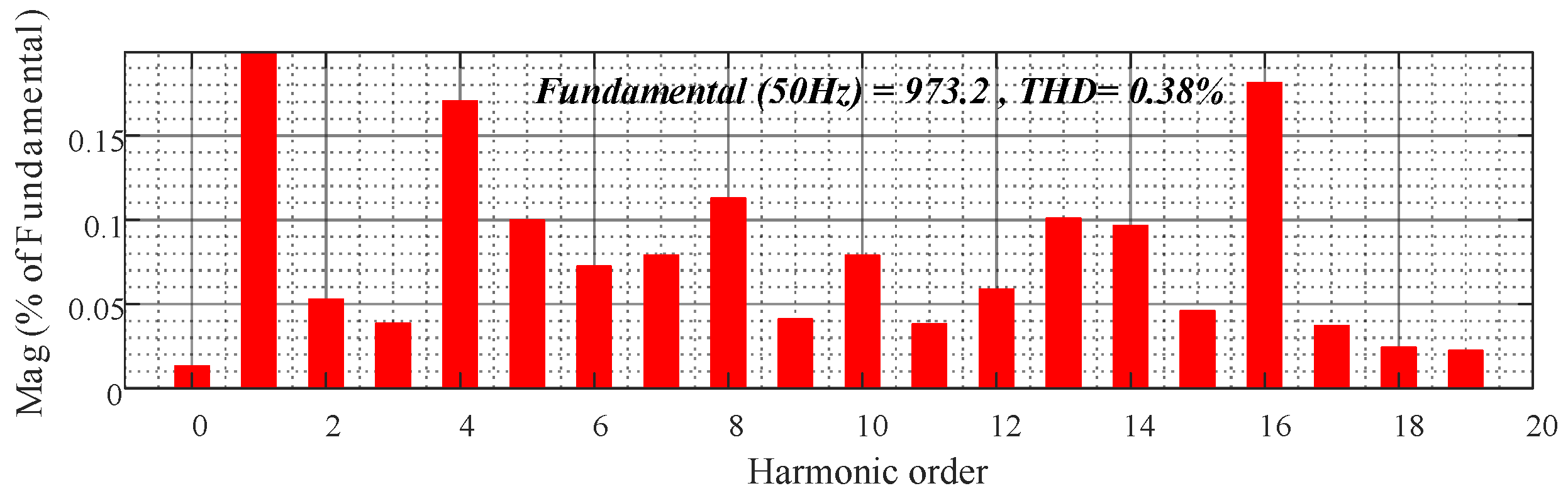

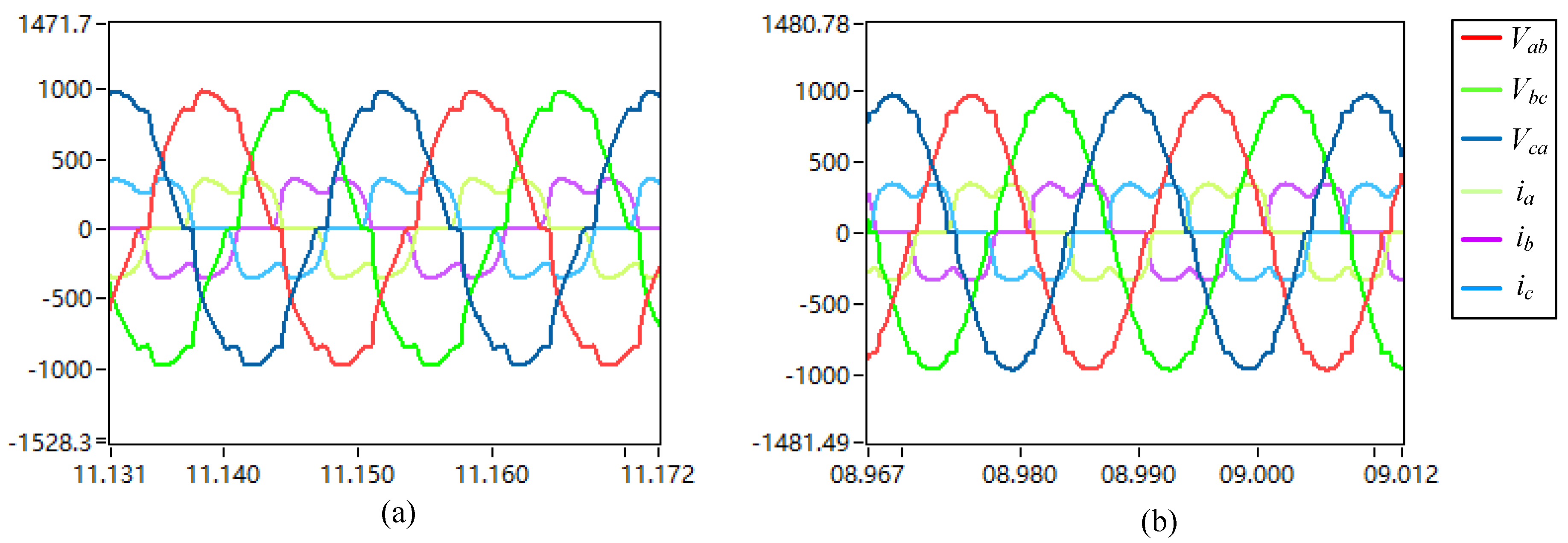

5.3. Nonlinear Load Experiment

5.4. Output-Voltage Harmonics Comparison

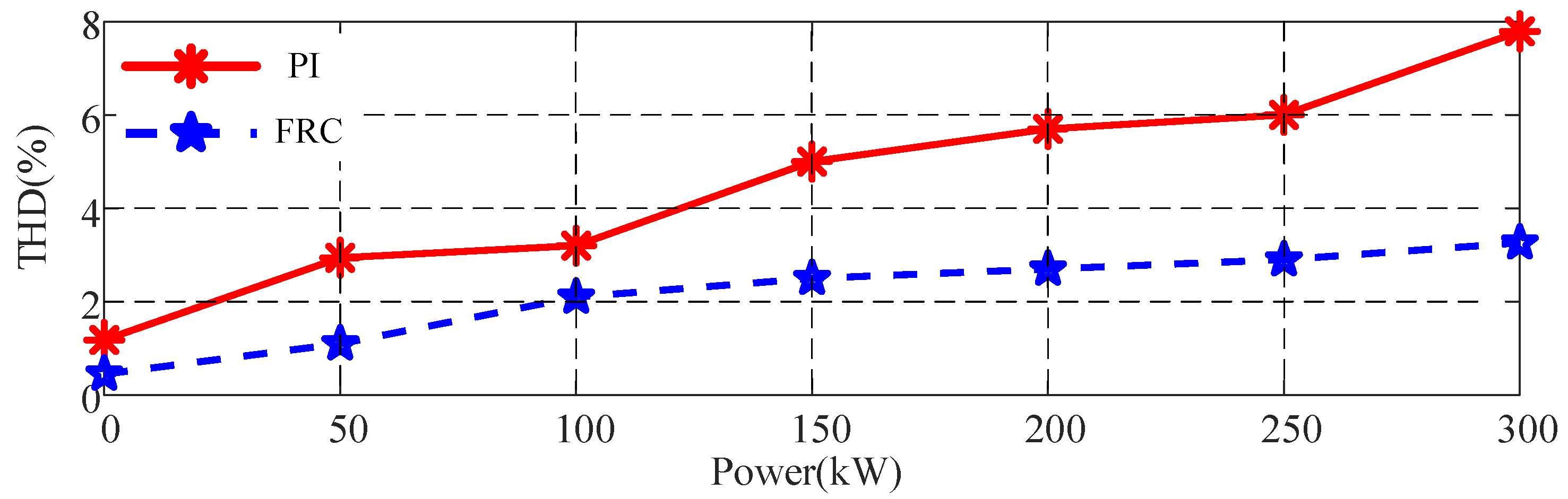

- To visualize the harmonic suppression capability, the output voltage THD (with resistive loads) at different power levels is shown in Figure 20. The red color represents the PI control, and the blue color represents the FRC control. We take the rated power of 0.1 pu as the step point from zero load to full load. No matter what power level, the proposed output voltage THD content of the FRC control is lower than that of the PI. The THD of the FRC control is approximately 0.5%, which is much lower than the international standard requirements (3%).

- To further demonstrate the harmonic rejection capability of the FRC, its output voltage THD (nonlinear load) is shown in Figure 21. With an increasing nonlinear load power (the step unit is 50 kW), the output voltage waveforms of the PI control and FRC control have a certain degree of distortion. The proposed FRC control is capable of suppressing the voltage harmonics to less than 4%, while the PI control is already close to 8%.

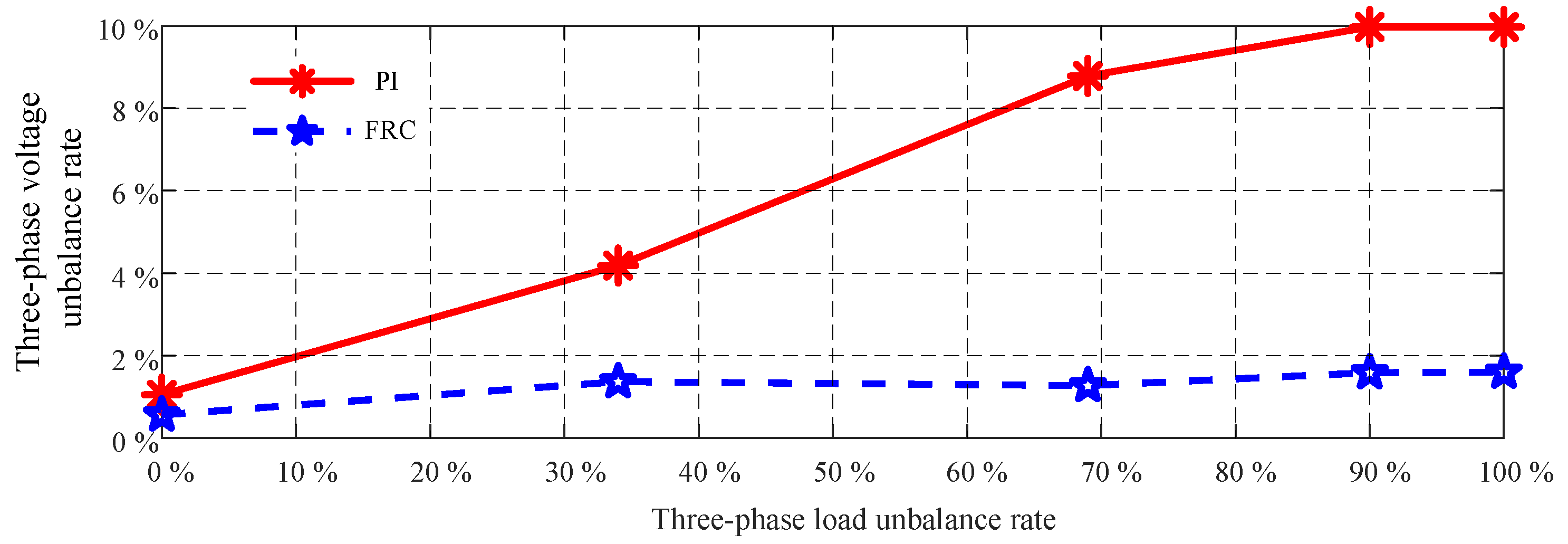

5.5. Three-Phase Unbalanced Load Experiment

6. Discussion

- In this work, both the mode and GFM mode are based on the voltage single loop to design the controller without considering the current inner loop. Although this design is simple and convenient for engineers to design and debug, the disadvantage is also obvious: in the case of overcurrent, due to the lack of a current inner loop, it is not possible to effectively limit the fault current. However, we believe that this is not an obvious disadvantage for GFM control, and it has been confirmed that the stability of GFM with single-voltage closed-loop control is higher than that of GFM with dual closed-loop control under a robust power grid.

- In this work, using the control as an example, it has been clearly demonstrated that the proposed controller has excellent control performance. However, in the GFM mode, more tests are needed. The focus of the test should be on whether the proposed controller has a faster voltage response than the PI control. This response speed directly determines the reactive current of the PCS at LVRT/HVRT.Theoretically, the proposed voltage controller provides real-time control, while the PI control needs to convert to and , and this link usually adds filters to smooth and . Therefore, the proposed FRC controller should have a faster control speed in GFM mode, and the response speed should be faster than the PI control in the LVRT/HVRT test.

- The proposed FRC control can be redesigned into a current controller that can be used for the current control of a PCS (e.g., mode or AC constant current mode), and this control can achieve very low grid-connected harmonic currents.

- If it is desired to add a current inner loop to the FRC control discussed in this work, we strongly do not recommend adding a controller with a similar structure of repetitive control, because it will exacerbate the computational burden of the DSP control chip (for the FRC control, we used 50 kHz; however, we found that the control algorithm could not be calculated in an interrupt cycle in DSP28335, so, we later changed to 40 kHz or adopted an ORC kernel, which solved the problem). PR or QPR control can be used as the current inner loop; however, the stability would need to be re-evaluated.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| PCS | power conversion system |

| ANPC | Active Neutral Point Clamped |

| RC | repetitive control |

| PI | Proportional–Integral |

| FRC | fast repetitive control |

| VSG | Virtual Synchronous Generator |

| IPM | Intelligent Power Module |

| SFO-PWM | Switching Frequency Optimal-PWM |

| THD | Total Harmonic Distortion |

| pu | per unit |

| GFM | Grid Forming |

| LVRT | Low-Voltage Ride Through |

| HVRT | High-Voltage Ride Through |

| ORC | odd repetitive control |

| PR | Proportional Resonant |

| QPR | Quasi-Proportional Resonance |

| DSP | Digital Signal Processing |

| 3P3L | 3 Phase 3 Line |

| LCUR | Line Current Unbalance Ratio |

| PVUR | phase voltage unbalance ratio |

| RMS | Root Mean Square |

| LPF | low-pass filter |

| PCC | point of common coupling |

| HIL | hardware in the loop |

| DI | Digital Input |

| DO | Digital Output |

| AI | Analog Input |

| AO | Analog Output |

| V/f | voltage/frequency |

Appendix A

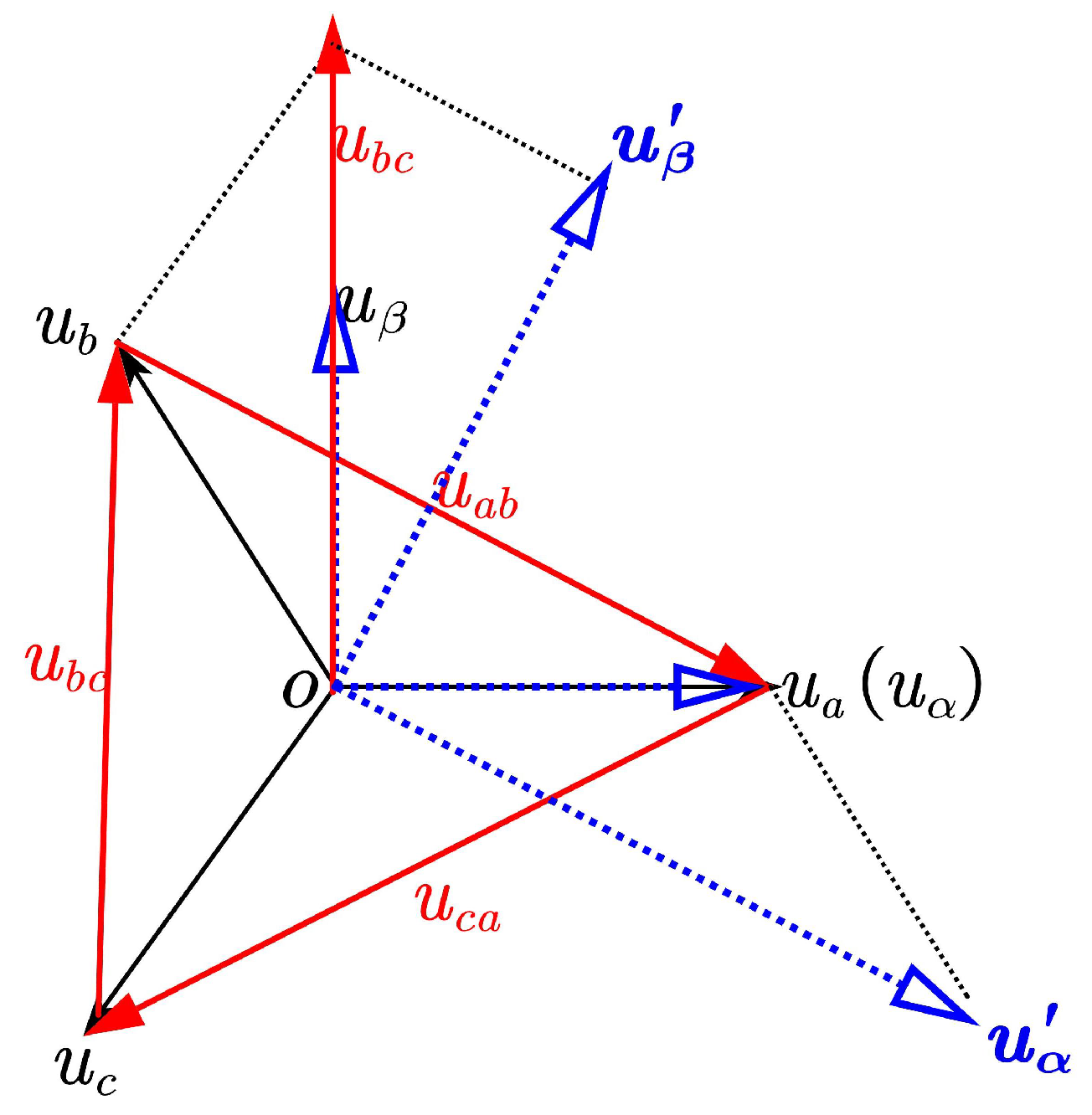

Appendix A.1. 3P3L System with 3/2 Constant Amplitude Transformation Derivation

Appendix A.2. Three-Phase Load Unbalance Rate Calculation Formula

Appendix B

Appendix C

Appendix D

Appendix E

References

- Guo, J.; Ma, S.; Wang, T.; Jing, Y.; Hou, W.; Xu, H. Challenges of developing a power system with a high renewable energy proportion under China’s carbon targets. iEnergy 2022, 1, 12–18. [Google Scholar] [CrossRef]

- Breyer, C.; Khalili, S.; Bogdanov, D.; Ram, M.; Oyewo, A.S.; Aghahosseini, A.; Gulagi, A.; Solomon, A.A.; Keiner, D.; Lopez, G.; et al. On the History and Future of 100% Renewable Energy Systems Research. IEEE Access 2022, 10, 78176–78218. [Google Scholar] [CrossRef]

- Zhang, D.; Du, M.; Zhang, Z.; Li, J.; Li, C.; Liu, H.; Shao, L. Effect of multi-energy storage systems on improving the synergy of integrated energy system. In Proceedings of the 2023 3rd New Energy and Energy Storage System Control Summit Forum (NEESSC), Mianyang, China, 26–28 September 2023; pp. 90–93. [Google Scholar]

- Chen, X.; Chen, Y.; Lin, Z.; Mao, X.; Chen, J.; Zhang, Z. Design of High-Power Energy Storage Bidirectional Power Conversion System. In Proceedings of the 2020 24th International Conference Electronics, Palanga, Lithuania, 15–17 June 2020; pp. 1–6. [Google Scholar]

- Zhai, H.; Yang, F.; Xu, Y.; Liu, J.; Huang, L.; Liu, T.; Hao, X. Performance analysis of VSG controlled PCS in Island mode. In Proceedings of the The 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), Online, 2–3 July 2020; pp. 1042–1045. [Google Scholar]

- Zhong, Q.-C.; Weiss, G. Synchronverters: Inverters That Mimic Synchronous Generators. IEEE Trans. Ind. Electron. 2011, 58, 1259–1267. [Google Scholar] [CrossRef]

- Rosso, R.; Wang, X.; Liserre, M.; Lu, X.; Engelken, S. Grid-Forming Converters: Control Approaches, Grid-Synchronization, and Future Trends—A Review. IEEE Open J. Ind. Appl. 2021, 2, 93–109. [Google Scholar] [CrossRef]

- Zhou, J.; Zhang, R.; Zhang, X.; Wu, J.; Huang, W. A Compound Control Strategy for Inverter Output Voltage in Micro-grid System. In Proceedings of the 2018 IEEE 4th Southern Power Electronics Conference (SPEC), Singapore, 10–13 December 2018; pp. 1–5. [Google Scholar]

- Zhang, Z.; Zhang, D.; Ma, J.; Lu, H.; Zhou, Y.; Xi, Z. Based on Vector Proportional Integral (VPI) Control of Brushless Doubly Fed Induction Generator under Load Imbalance. In Proceedings of the 2022 4th Asia Energy and Electrical Engineering Symposium (AEEES), Chengdu, China, 25–28 March 2022; pp. 64–70. [Google Scholar]

- Fantino, R.A.; Busada, C.A.; Solsona, J.A. Optimum PR Control Applied to LCL Filters with Low Resonance Frequency. IEEE Trans. Power Electron. 2018, 33, 793–801. [Google Scholar] [CrossRef]

- Nazeri, A.A.; Saeidi, M.; Zacharias, P. Design and Performance Analysis of a Modified Proportional Multi-Resonant (PMR) Controller for Three-Phase Voltage-Source Inverters. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications, Hanover, Germany, 5–9 September 2022; pp. 1–12. [Google Scholar]

- Rahman, M.M.; Biswas, S.P.; Islam, M.R.; Muttaqi, K.M.; Muyeen, S.M. Design of a High Performance Resonant Controller for Improved Stability and Robustness of Islanded Three-Phase Microgrids. IEEE Access 2022, 10, 119206–119220. [Google Scholar] [CrossRef]

- Sun, Y.; Zhou, J. Grid-Tied Inverter Fractional-Order Phase Compensation via Odd Repetition Control. In Proceedings of the International Conference on Electrical Engineering and Green Energy (CEEGE), Grimstad, Norway, 6–9 June 2023; Volume 10, pp. 62–68. [Google Scholar]

- Xu, J.; Soeiro, T.B.; Gao, F.; Chen, L.; Tang, H.; Bauer, P.; Dragičević, T. Carrier-Based Modulated Model Predictive Control Strategy for Three-Phase Two-Level VSIs. IEEE Trans. Energy Convers. 2021, 36, 1673–1687. [Google Scholar] [CrossRef]

- Andino, J.; Ayala, P.; Llanos-Proaño, J.; Naunay, D.; Martinez, W.; Arcos-Aviles, D. Constrained Modulated Model Predictive Control for a Three-Phase Three-Level Voltage Source Inverter. IEEE Access 2022, 10, 10673–10687. [Google Scholar] [CrossRef]

- Pardhi, P.K.; Sharma, S. Implementation of Robust Controller for VSI Feeding Stand-alone Loads. In Proceedings of the 2019 IEEE 1st International Conference on Energy, Systems and Information Processing, Chennai, India, 4–6 July 2019; pp. 1–5. [Google Scholar]

- Sun, Y.; Zhao, Q.; Liao, W.; Jiang, K.; Tan, W. Robust Repetitive Controller Design Based on S/SK Problem for Single-phase Grid-connected Inverters. In Proceedings of the International Conference on Robotics and Automation Engineering (ICRAE), Guangzhou, China, 19–22 November 2021; pp. 223–230. [Google Scholar]

- Vieira, R.P.; Martins, L.T.; Massing, J.R.; Stefanello, M. Sliding Mode Controller in a Multiloop Framework for a Grid-Connected VSI With LCL Filter. IEEE Trans. Ind. Electron. 2018, 65, 4714–4723. [Google Scholar] [CrossRef]

- Shen, X.; Wu, C.; Liu, Z.; Wang, Y.; Leon, J.I.; Liu, J.; Franquelo, L.G. Adaptive-Gain Second-Order Sliding-Mode Control of NPC Converters Via Super-Twisting Technique. IEEE Trans. Ind. Electron. 2023, 38, 15406–15418. [Google Scholar] [CrossRef]

- Rodrguez, J.; Lai, J.; Peng, F. Multilevel inverters: A survey of topologies controls and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Barater, D.; Concari, C.; Buticchi, G.; Gurpinar, E.; De, D.; Castellazzi, A. Performance Evaluation of a Three-Level ANPC Photovoltaic Grid-Connected Inverter With 650-V SiC Devices and Optimized PWM. IEEE Trans. Ind. Appl. 2016, 52, 2475–2485. [Google Scholar] [CrossRef]

- Barbosa, P.; Steimer, P.; Meysenc, L.; Winkelnkemper, M.; Steinke, J.; Celanovic, N. Active Neutral-Point-Clamped Multilevel Converters. In Proceedings of the IEEE 36th Power Electronics Specialists Conference, Dresden, Germany, 16 November 2005; pp. 2296–2301. [Google Scholar]

- Taallah, A.; Mekhilef, S. Active neutral point clamped converter for equal loss distribution. IET Power Electron. 2014, 7, 1859–1867. [Google Scholar] [CrossRef]

| DC Characteristics | |

|---|---|

| Maximum DC voltage | 1500 Vdc |

| Minimum DC voltage | 1000 Vdc |

| Full load DC operating voltage range | 1000–1500 Vdc |

| Maximum DC current | 1935 A |

| AC Characteristics (Off-Grid) | |

| Nominal output power | 1725 kVA |

| Maximum output current | 1578 A |

| Nominal AC voltage | 690 Vac |

| AC voltage range | −15%–10% |

| AC voltage harmonics | <3% (Linear loads) |

| DC voltage components | <0.5% × Un |

| Nominal frequency/frequency range | 50 Hz/45∼55 Hz |

| Overload capacity | 120% (20 s) |

| Number of phases at the output | 3 phases/3 lines |

| Parameters | Value |

|---|---|

| Filter inductor DC resistance: R | 0.35 Ω |

| Filter inductors: L | 0.07 mH |

| Filter capacitor: C* | 240 μF |

| Parameters | Value |

|---|---|

| N | 72 |

| Q | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, J.; Sun, Y.; Chen, S.; Lan, T. A Fast Repetitive Control Strategy for a Power Conversion System. Electronics 2024, 13, 1186. https://doi.org/10.3390/electronics13071186

Zhou J, Sun Y, Chen S, Lan T. A Fast Repetitive Control Strategy for a Power Conversion System. Electronics. 2024; 13(7):1186. https://doi.org/10.3390/electronics13071186

Chicago/Turabian StyleZhou, Jinghua, Yifei Sun, Shasha Chen, and Tianfeng Lan. 2024. "A Fast Repetitive Control Strategy for a Power Conversion System" Electronics 13, no. 7: 1186. https://doi.org/10.3390/electronics13071186

APA StyleZhou, J., Sun, Y., Chen, S., & Lan, T. (2024). A Fast Repetitive Control Strategy for a Power Conversion System. Electronics, 13(7), 1186. https://doi.org/10.3390/electronics13071186