A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference

Abstract

1. Introduction

2. Principle of High-Order Temperature Compensation

2.1. Traditional Low-Voltage BGR

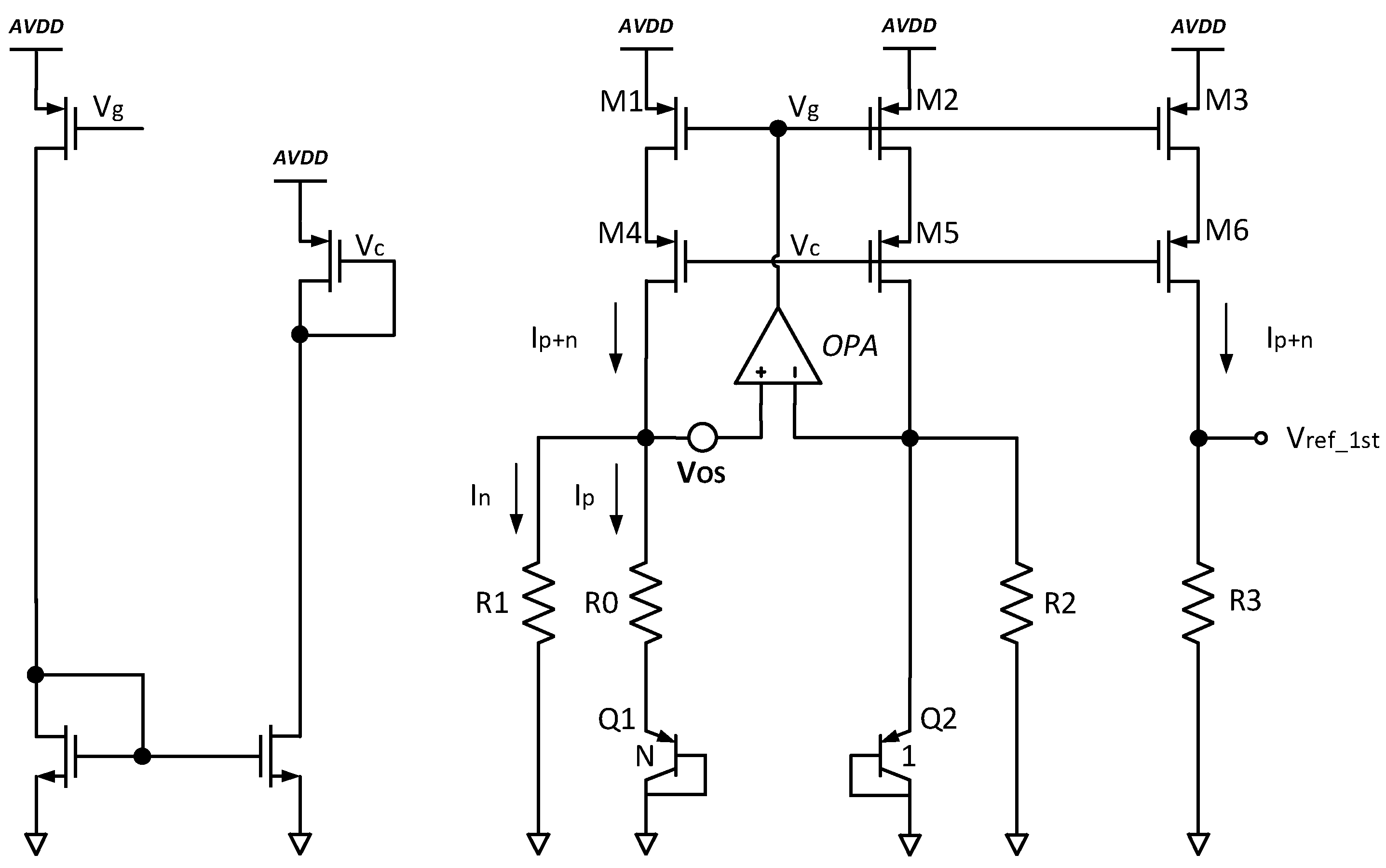

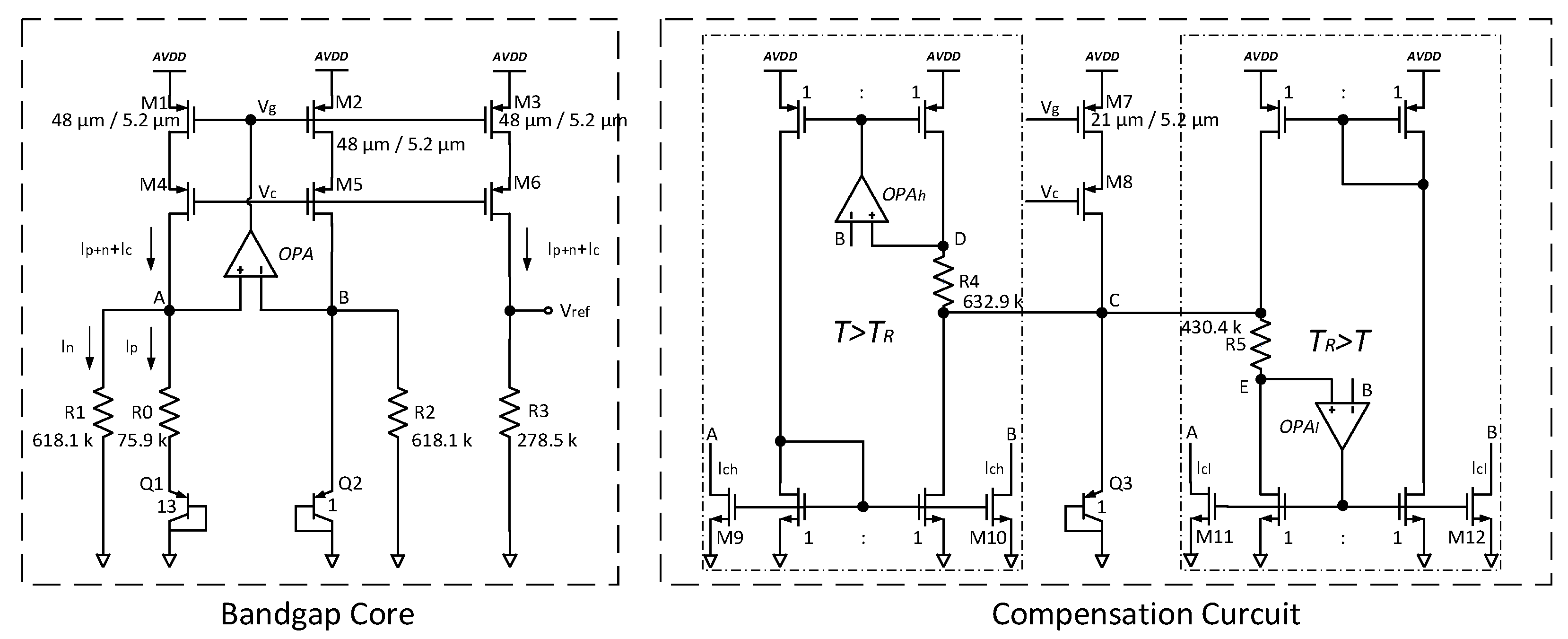

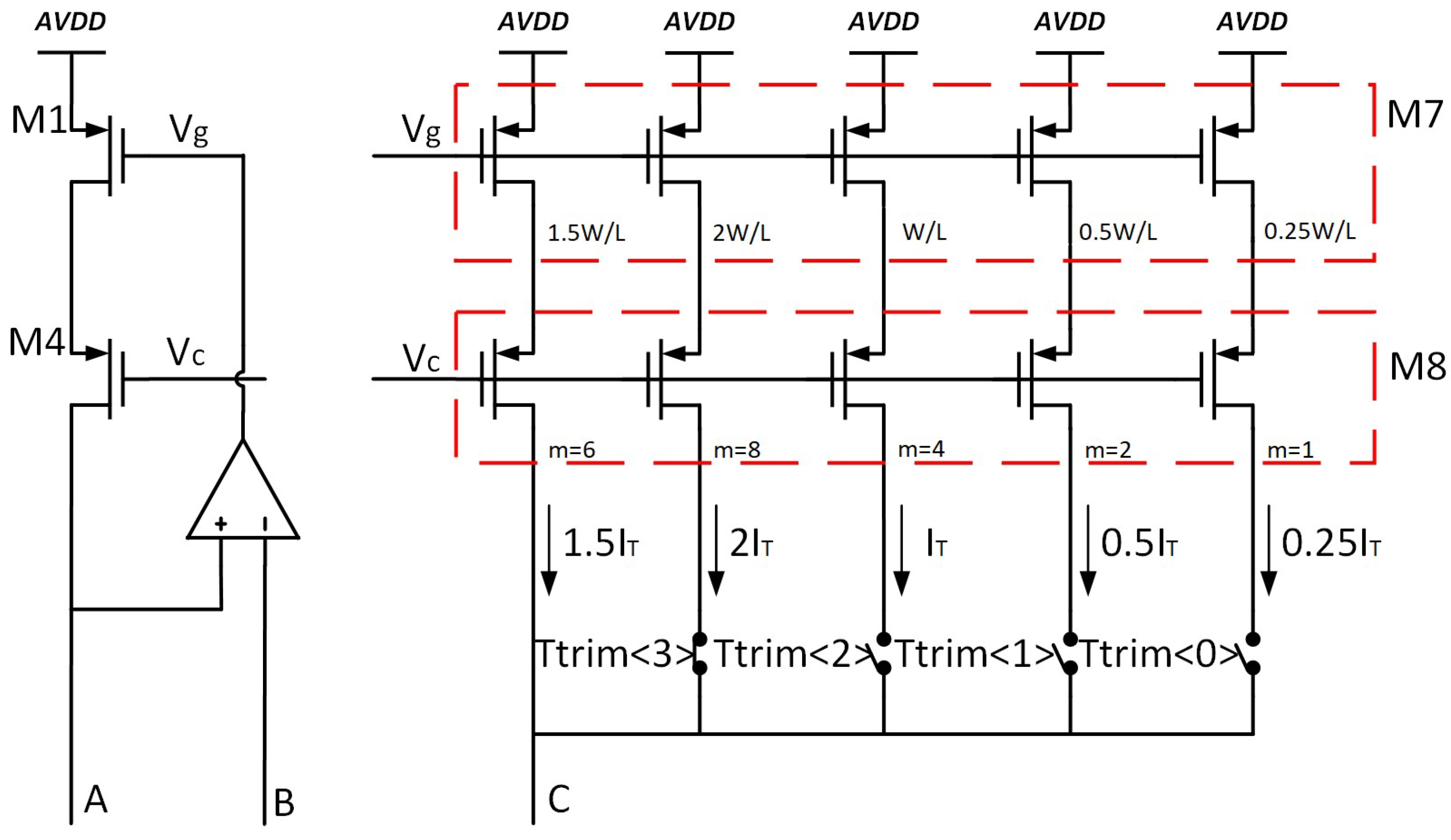

2.2. The Proposed Low-Voltage BGR

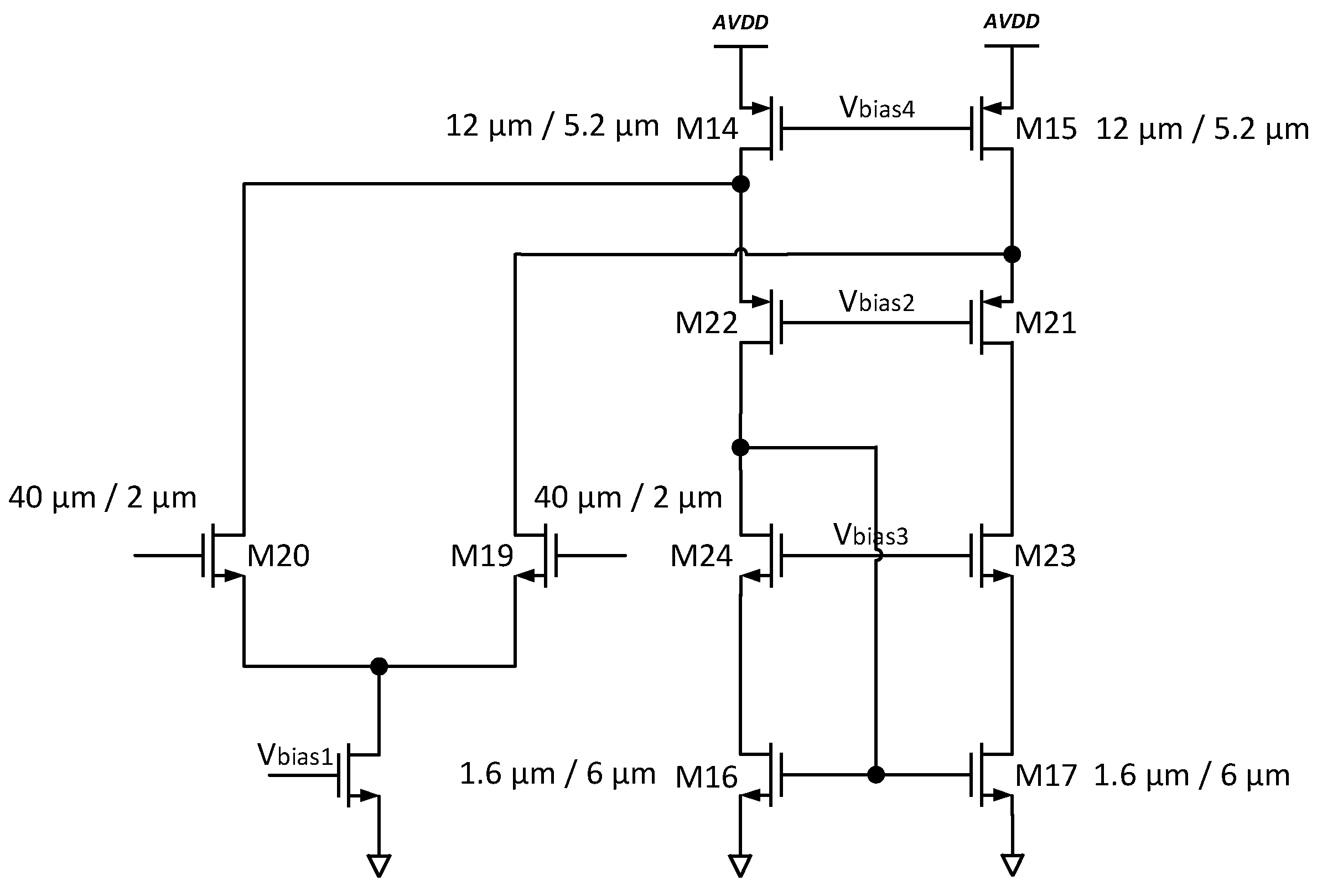

2.3. The Design of OPA

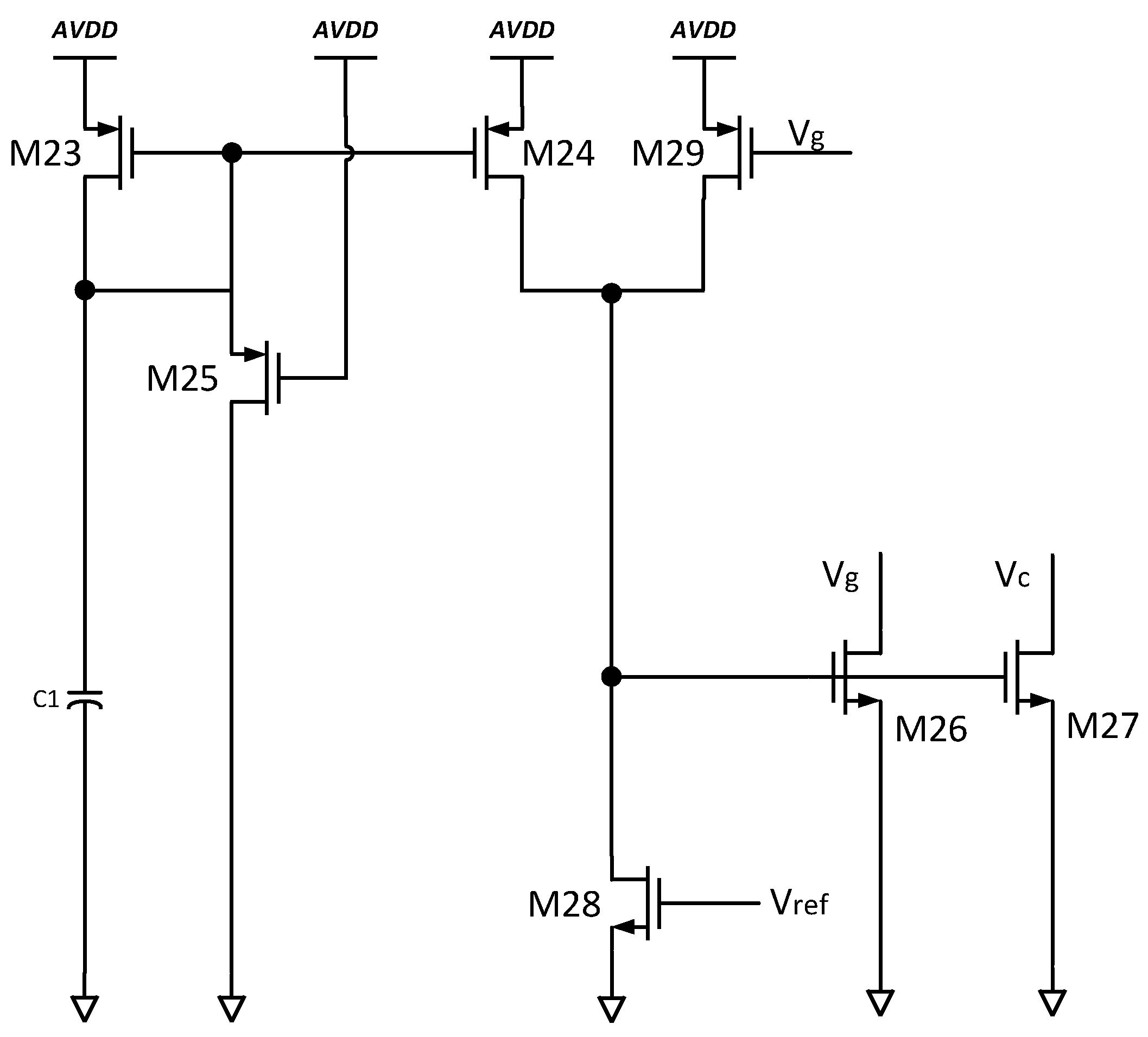

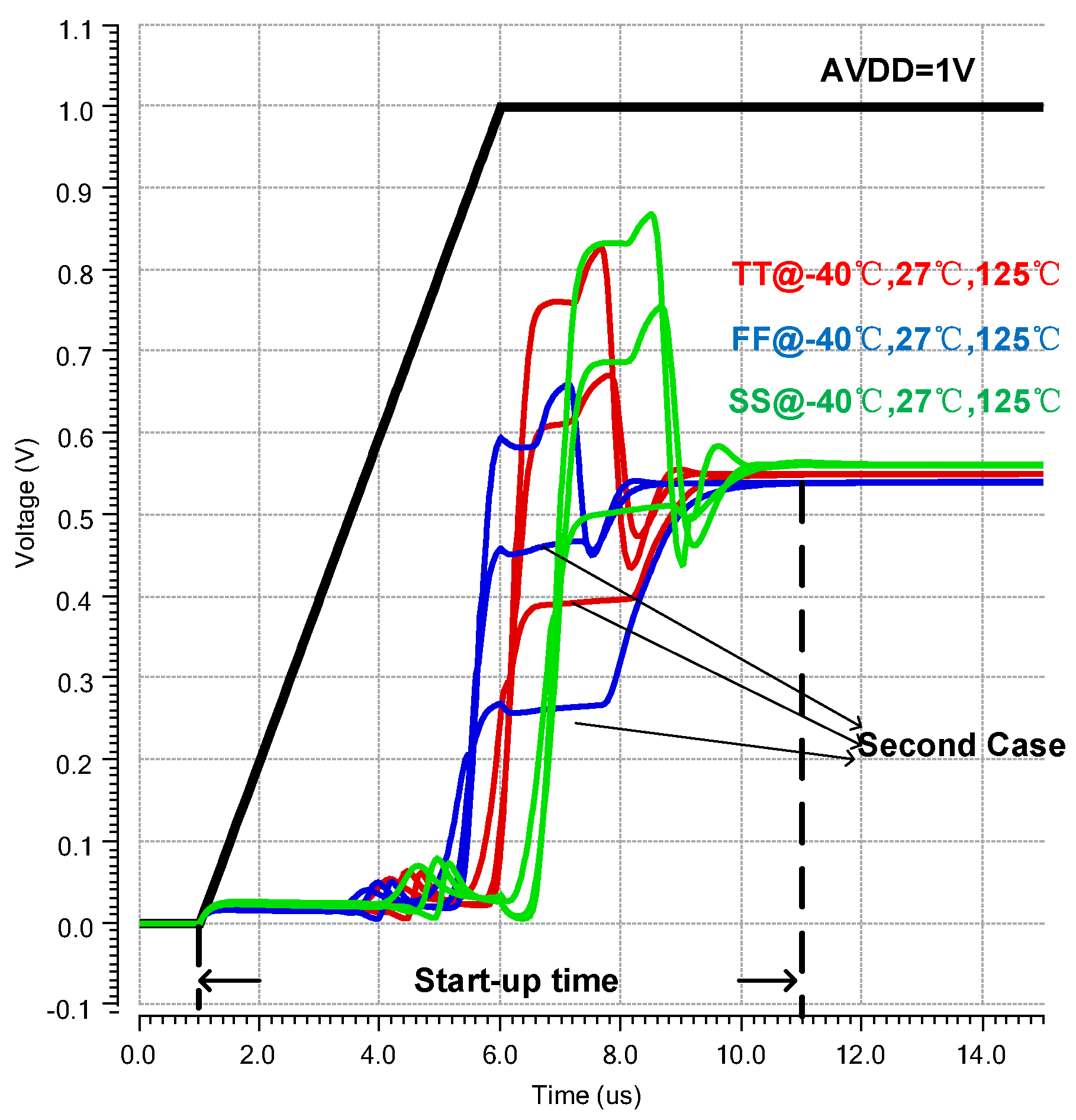

3. Start-Up Circuit

4. Trimming and Simulation Results

4.1. Trimming

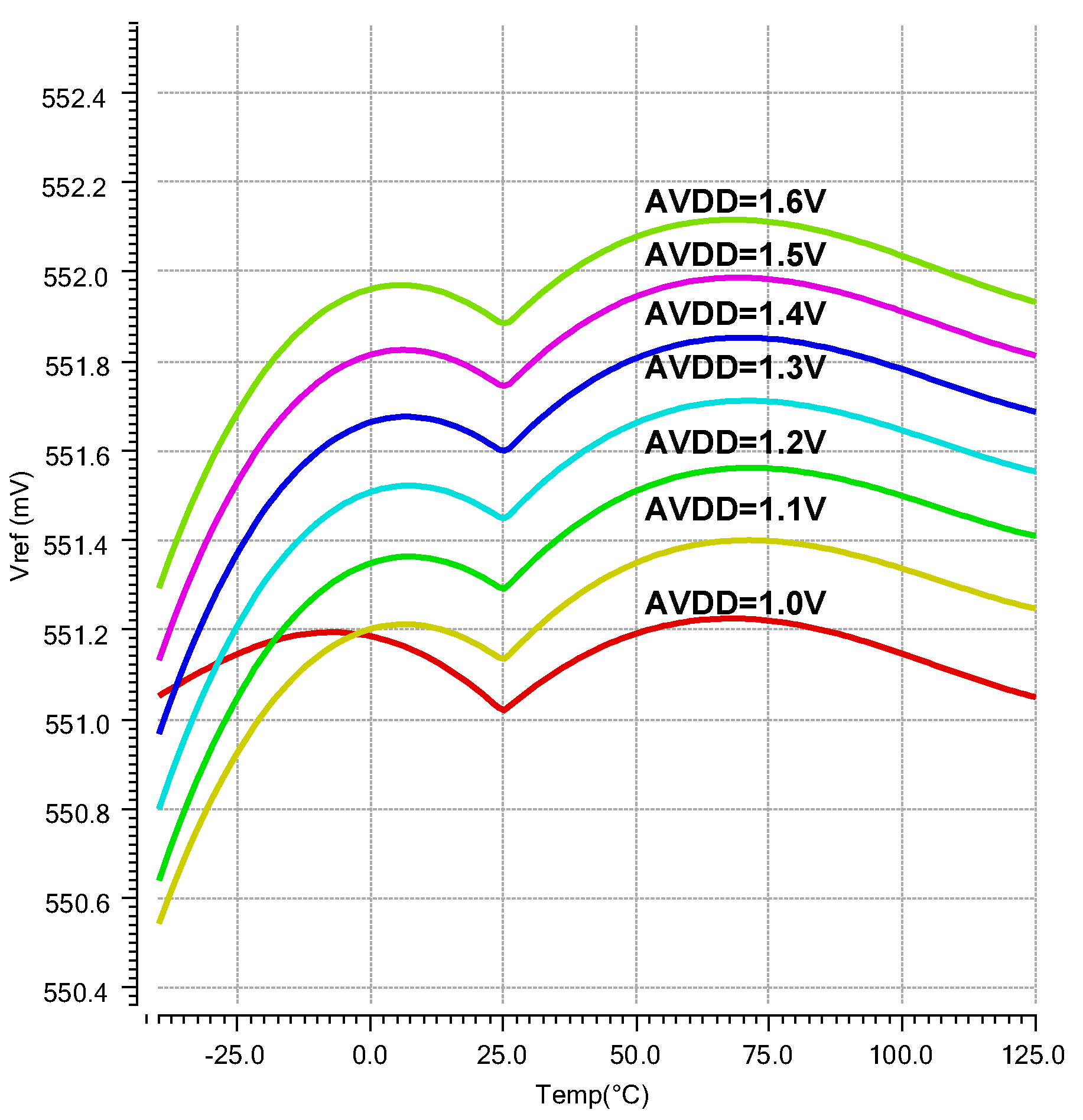

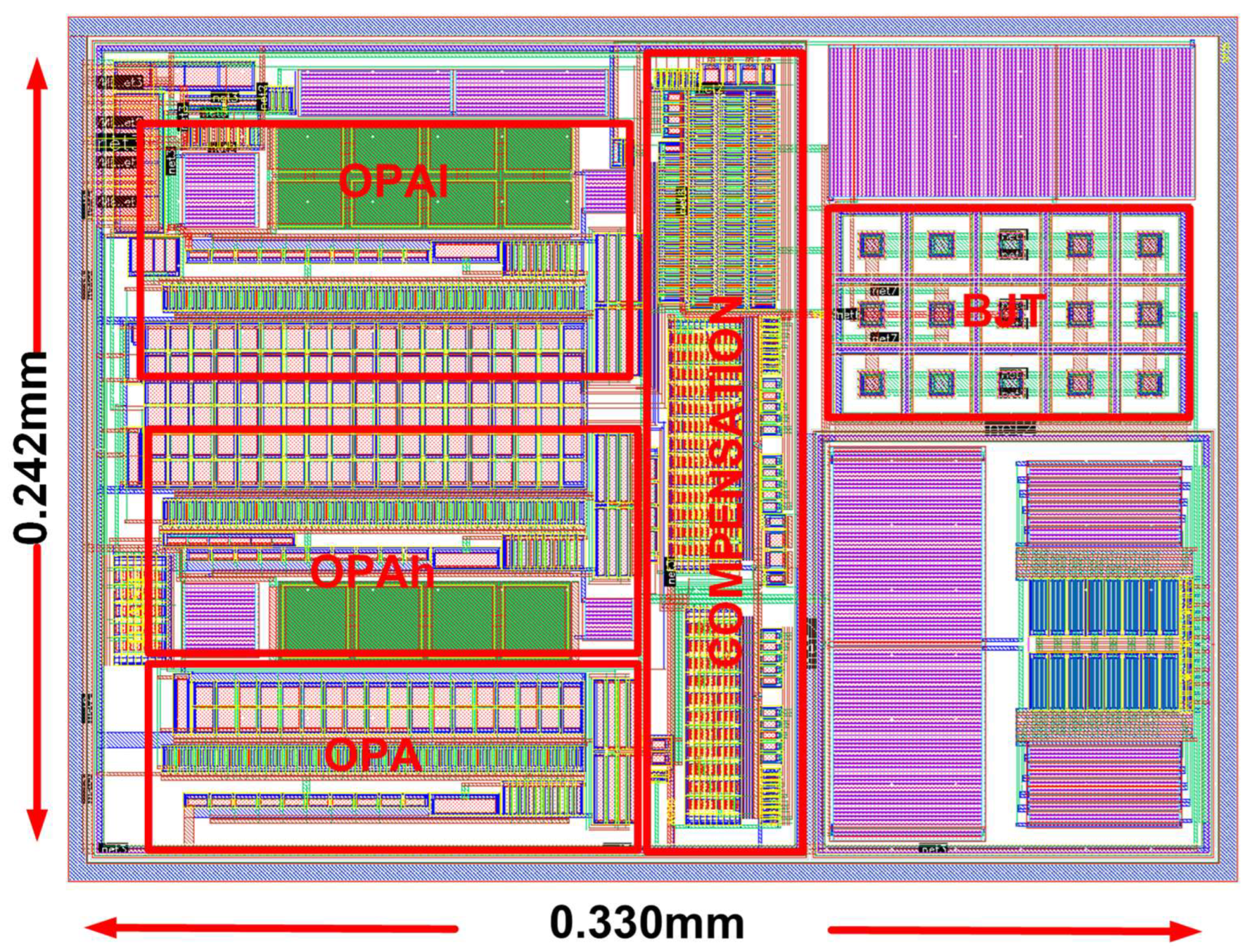

4.2. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Annema, A.J. Low-power bandgap references featuring DTMOSTs. IEEE J. Solid-State Circuits 1999, 34, 949–955. [Google Scholar] [CrossRef]

- Vulligaddala, V.B.; Adusumalli, R.; Singamala, S.; Srinivas, M.B. A Digitally Calibrated Bandgap Reference with 0.06% Error for Low-Side Current Sensing Application. IEEE J. Solid-State Circuits 2018, 53, 2951–2957. [Google Scholar] [CrossRef]

- Liu, L.; Liao, X.; Mu, J. A 3.6~μ Vrms Noise, 3 ppm/°C TC Bandgap Reference with Offset/Noise Suppression and Five-Piece Linear Compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 3786–3796. [Google Scholar] [CrossRef]

- Banba, H.; Shiga, H.; Umezawa, A.; Miyaba, T.; Tanzawa, T.; Atsumi, S.; Sakui, K. A CMOS bandgap reference circuit with sub-1-V operation. IEEE J. Solid-State Circuits 1999, 34, 670–674. [Google Scholar] [CrossRef]

- Ka Nang, L.; Mok, P.K.T. A sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE J. Solid-State Circuits 2002, 37, 526–530. [Google Scholar] [CrossRef]

- Huang, S.; Li, M.; Li, H.; Yin, P.; Shu, Z.; Bermak, A.; Tang, F. A Sub-1 ppm/°C Bandgap Voltage Reference with High-Order Temperature Compensation in 0.18-μm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 1408–1416. [Google Scholar] [CrossRef]

- Ma, B.; Yu, F. A Novel 1.2–V 4.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1026–1035. [Google Scholar] [CrossRef]

- Kamath, U.; Cullen, E.; Yu, T.; Jennings, J.; Wu, S.; Lim, P.; Farley, B.; Staszewski, R.B. A 1-V Bandgap Reference in 7-nm FinFET with a Programmable Temperature Coefficient and Inaccuracy of ±0.2% From −45 °C to 125 °C. IEEE J. Solid-State Circuits 2019, 54, 1830–1840. [Google Scholar] [CrossRef]

- Andreou, C.M.; Koudounas, S.; Georgiou, J. A Novel Wide-Temperature-Range, 3.9 ppm/°C CMOS Bandgap Reference Circuit. IEEE J. Solid-State Circuits 2012, 47, 574–581. [Google Scholar] [CrossRef]

- Yang, Y.; Binkley, D.M.; Li, L.; Gu, C.; Li, C. All-CMOS subbandgap reference circuit operating at low supply voltage. In Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 893–896. [Google Scholar]

- Yang, B.D. 250-mV Supply Subthreshold CMOS Voltage Reference Using a Low-Voltage Comparator and a Charge-Pump Circuit. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 850–854. [Google Scholar] [CrossRef]

- Gagliardi, F.; Catania, A.; Ria, A.; Bruschi, P.; Piotto, M. A Compact All-MOSFETs PVT-compensated Current Reference with Untrimmed 0.88%-(σ/μ). In Proceedings of the 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Valencia, Spain, 18–21 June 2023; pp. 61–64. [Google Scholar]

- Gagliardi, F.; Ria, A.; Piotto, M.; Bruschi, P. A 114 ppm/°C-TC 0.78%-(σ/μ) Current Reference with Minimum-Current-Search Calibration. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 1561–1565. [Google Scholar] [CrossRef]

- Colombo, D.M.; Wirth, G.; Bampi, S. Sub-1 V band-gap based and MOS threshold-voltage based voltage references in 0.13 µm CMOS. Analog. Integr. Circuits Signal Process. 2015, 82, 25–37. [Google Scholar] [CrossRef]

- Ria, A.; Catania, A.; Bruschi, P.; Piotto, M. A Low-Power CMOS Bandgap Voltage Reference for Supply Voltages Down to 0.5 V. Electronics 2021, 10, 1901. [Google Scholar] [CrossRef]

- Gunawan, M.; Meijer, G.C.M.; Fonderie, J.; Huijsing, J.H. A curvature-corrected low-voltage bandgap reference. IEEE J. Solid-State Circuits 1993, 28, 667–670. [Google Scholar] [CrossRef]

- Tsividis, Y.P. Accurate analysis of temperature effects in Ic- VBE characteristics with application to bandgap reference sources. IEEE J. Solid-State Circuits 1980, 15, 1076–1084. [Google Scholar] [CrossRef]

- Tianlin, C.; Yan, H.; Xiaopeng, L.; Hao, L.; Lu, L.; Hao, Z. A 0.9-V high-PSRR bandgap with self-cascode current mirror. In Proceedings of the 2012 IEEE International Conference on Circuits and Systems (ICCAS), Kuala Lumpur, Malaysia, 3–4 October 2012; pp. 267–271. [Google Scholar]

- Ka Nang, L.; Mok, P.K.T.; Chi Yat, L. A 2-V 23-μA 5.3-ppm/°C curvature-compensated CMOS bandgap voltage reference. IEEE J. Solid-State Circuits 2003, 38, 561–564. [Google Scholar] [CrossRef]

- Osaki, Y.; Hirose, T.; Kuroki, N.; Numa, M. 1.2-V Supply, 100-nW, 1.09-V Bandgap and 0.7-V Supply, 52.5-nW, 0.55-V Subbandgap Reference Circuits for Nanowatt CMOS LSIs. IEEE J. Solid-State Circuits 2013, 48, 1530–1538. [Google Scholar] [CrossRef]

- Ji, Y.; Lee, J.; Kim, B.; Park, H.J.; Sim, J.Y. A 192-pW Voltage Reference Generating Bandgap– Vth with Process and Temperature Dependence Compensation. IEEE J. Solid-State Circuits 2019, 54, 3281–3291. [Google Scholar] [CrossRef]

- Malcovati, P.; Maloberti, F.; Fiocchi, C.; Pruzzi, M. Curvature-compensated BiCMOS bandgap with 1-V supply voltage. IEEE J. Solid-State Circuits 2001, 36, 1076–1081. [Google Scholar] [CrossRef]

- Chen, K.; Petruzzi, L.; Hulfachor, R.; Onabajo, M. A 1.16-V 5.8-to-13.5-ppm/°C Curvature-Compensated CMOS Bandgap Reference Circuit with a Shared Offset-Cancellation Method for Internal Amplifiers. IEEE J. Solid-State Circuits 2021, 56, 267–276. [Google Scholar] [CrossRef]

- Lovett, S.J.; Welten, M.; Mathewson, A.; Mason, B. Optimizing MOS transistor mismatch. IEEE J. Solid-State Circuits 1998, 33, 147–150. [Google Scholar] [CrossRef]

- Tan, M.; Liu, F.; Fei, X. A novel sub-1-V bandgap reference in 0.18 µm CMOS technology. In Proceedings of the 2011 IEEE International Conference on Anti-Counterfeiting, Security and Identification, Xiamen, China, 24–26 June 2011; pp. 180–183. [Google Scholar]

| TC_bt (1 V) | TC_at (1 V) | TC_bt (1.3 V) | TC_at (1.3 V) | TC_bt (1.6 V) | TC_at (1.6 V) | |

|---|---|---|---|---|---|---|

| TT | 2.25 ppm/°C | 2.25 ppm/°C | 9.73 ppm/°C | 4.47 ppm/°C | 8.3 ppm/°C | 4.09 ppm/°C |

| FF | 14.3 ppm/°C | 5.61 ppm/°C | 15.87 ppm/°C | 6.69 ppm/°C | 12.96 ppm/°C | 6.21 ppm/°C |

| SS | 17.11 ppm/°C | 5.87 ppm/°C | 28.52 ppm/°C | 11.43 ppm/°C | 26.21 ppm/°C | 11.32 ppm/°C |

| Parameter | This Work * | [7] | [9] | [22] | [23] |

|---|---|---|---|---|---|

| Technology | 0.18 μm | 0.18 μm | 0.35 μm | 0.35 μm | 130 nm |

| Type | Current-mode | Current-mode | Current-mode | N/A | Current-mode |

| Supply Voltage (V) | 1 | 1.2 | 2.5 | 1.0–1.8 | 3.3 |

| Current Consumption (μA) | 36 | 36 | 38 | N/A | 120 |

| Reference Voltage (V) | 550 m | 767 m | 617.7 m | 692.6 m | 1.16 |

| TC (ppm/°C) | 2.25 | 3.4–6.9 | 3.9 | 25 | 5.8–13.5 |

| Temperature Range (°C) | −40–125 | −40–120 | −15–150 | −20–100 | −40–150 |

| Active Area (mm2) | 0.07986 | 0.036 | 0.1019 | 0.0045 | 0.08 |

| PSRR (dB) | −67.5 dB@DC | −84 dB@DC | N/A | −55 dB@100 | −30 dB @100K |

| OUTPUT NOISE (V) | 81.1 μ (0.1–10 HZ) | 5.4 μ@320 Hz | 20 nV (0.1–50 HZ) | 26.8 μ (0.1–10 HZ) | 84.3 μ (0.1–10 HZ) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jia, S.; Ye, T.; Xiao, S. A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference. Electronics 2024, 13, 1499. https://doi.org/10.3390/electronics13081499

Jia S, Ye T, Xiao S. A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference. Electronics. 2024; 13(8):1499. https://doi.org/10.3390/electronics13081499

Chicago/Turabian StyleJia, Shichao, Tianchun Ye, and Shimao Xiao. 2024. "A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference" Electronics 13, no. 8: 1499. https://doi.org/10.3390/electronics13081499

APA StyleJia, S., Ye, T., & Xiao, S. (2024). A 2.25 ppm/°C High-Order Temperature-Segmented Compensation Bandgap Reference. Electronics, 13(8), 1499. https://doi.org/10.3390/electronics13081499