A Large-Scale Neuromodulation System-on-Chip Integrating 128-Channel Neural Recording and 32-Channel Programmable Stimulation for Neuroscientific Applications

Abstract

1. Introduction

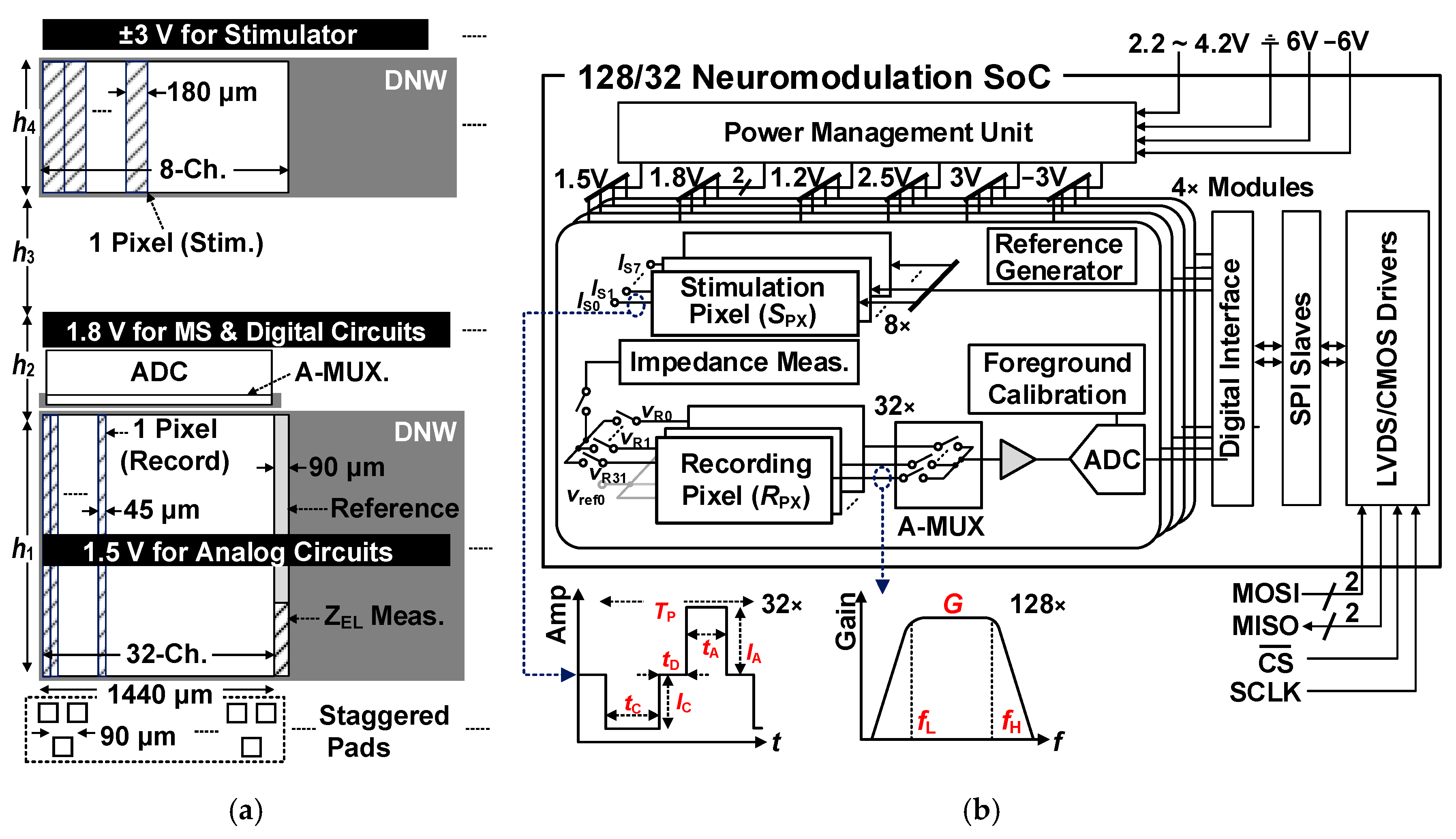

2. System Overview

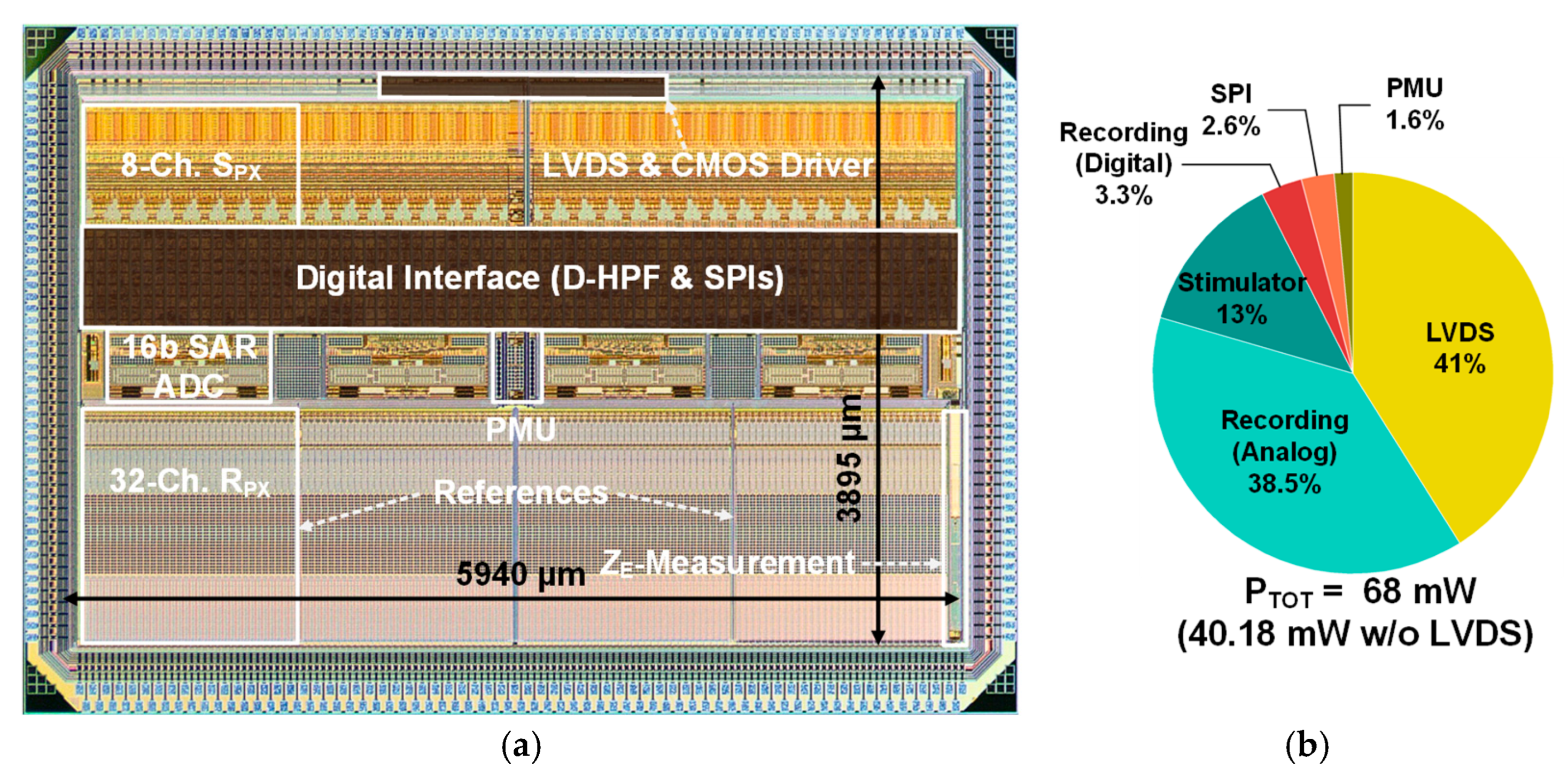

2.1. Floor-Planning and Layout Overview

2.2. Overall Circuit Architecture

3. Implementation

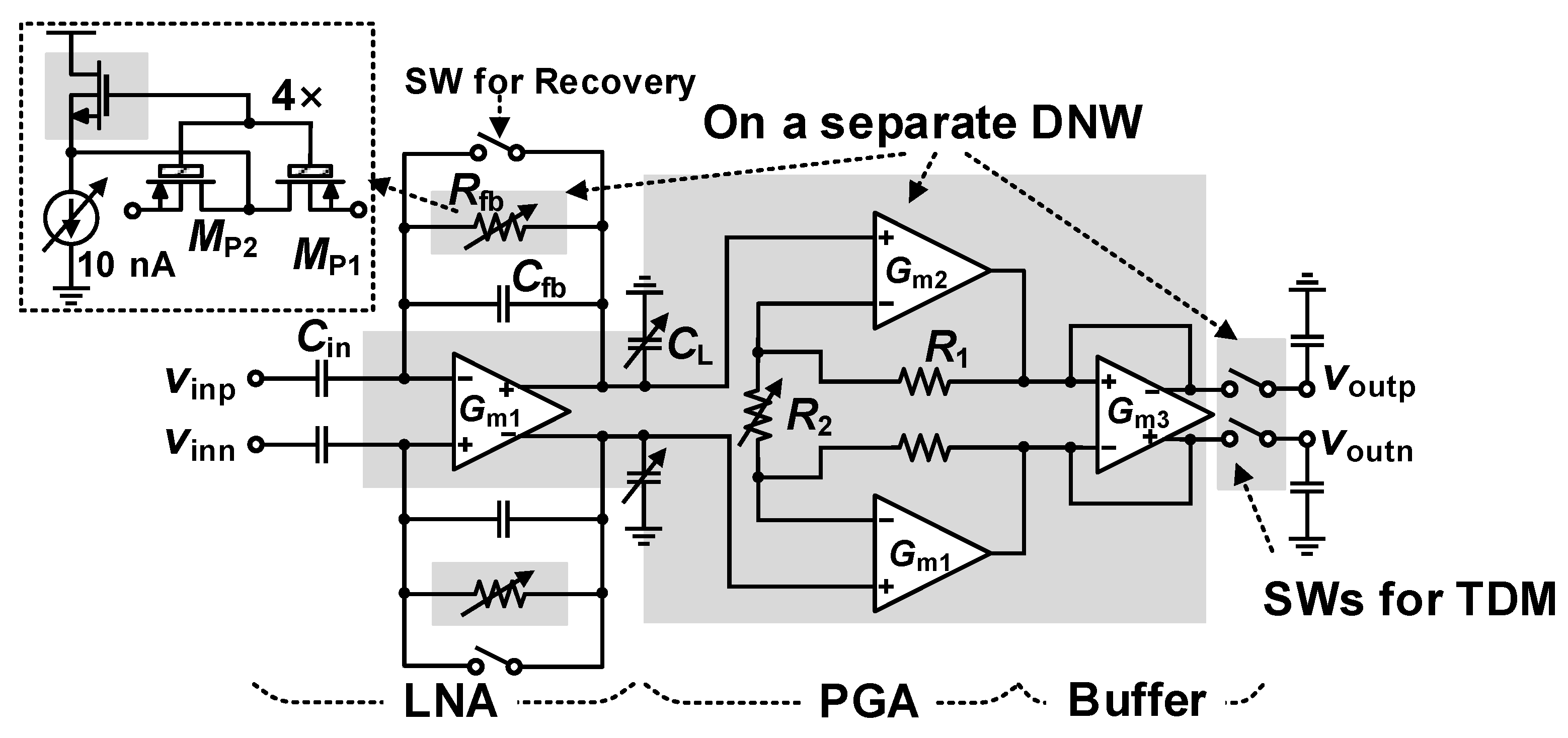

3.1. Recording Pixel (RPX)

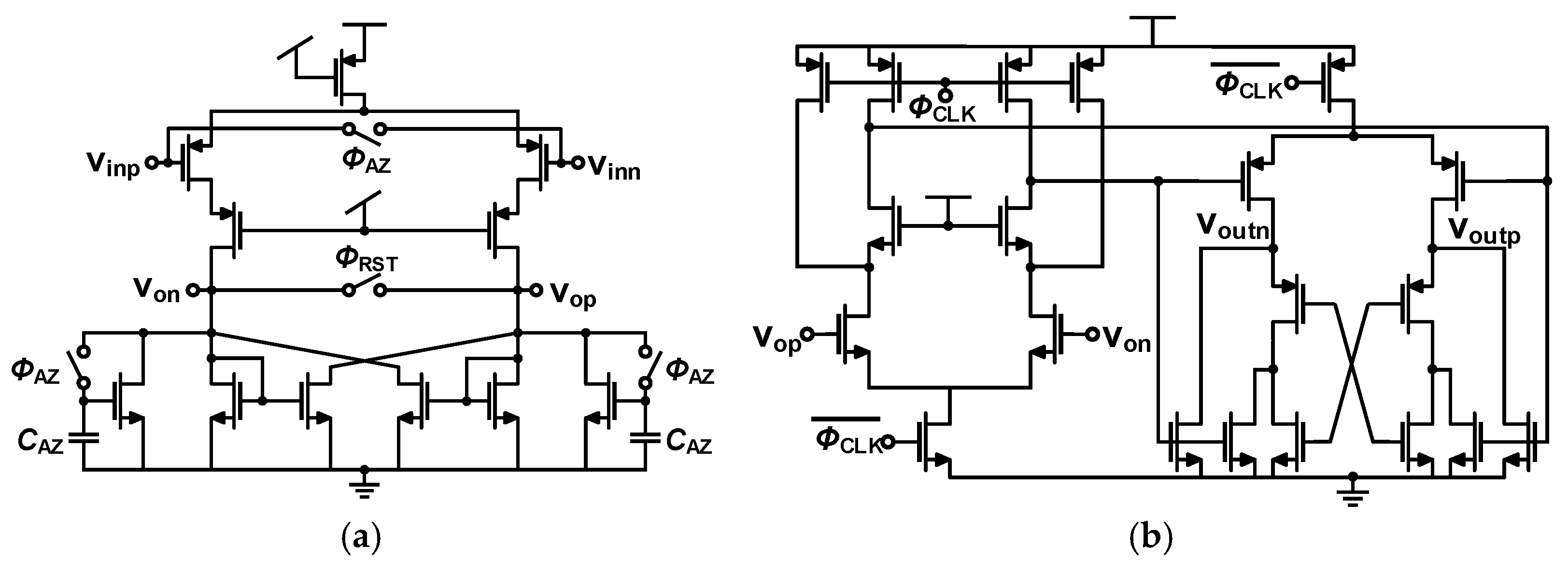

3.1.1. Low-Noise Amplifier Design

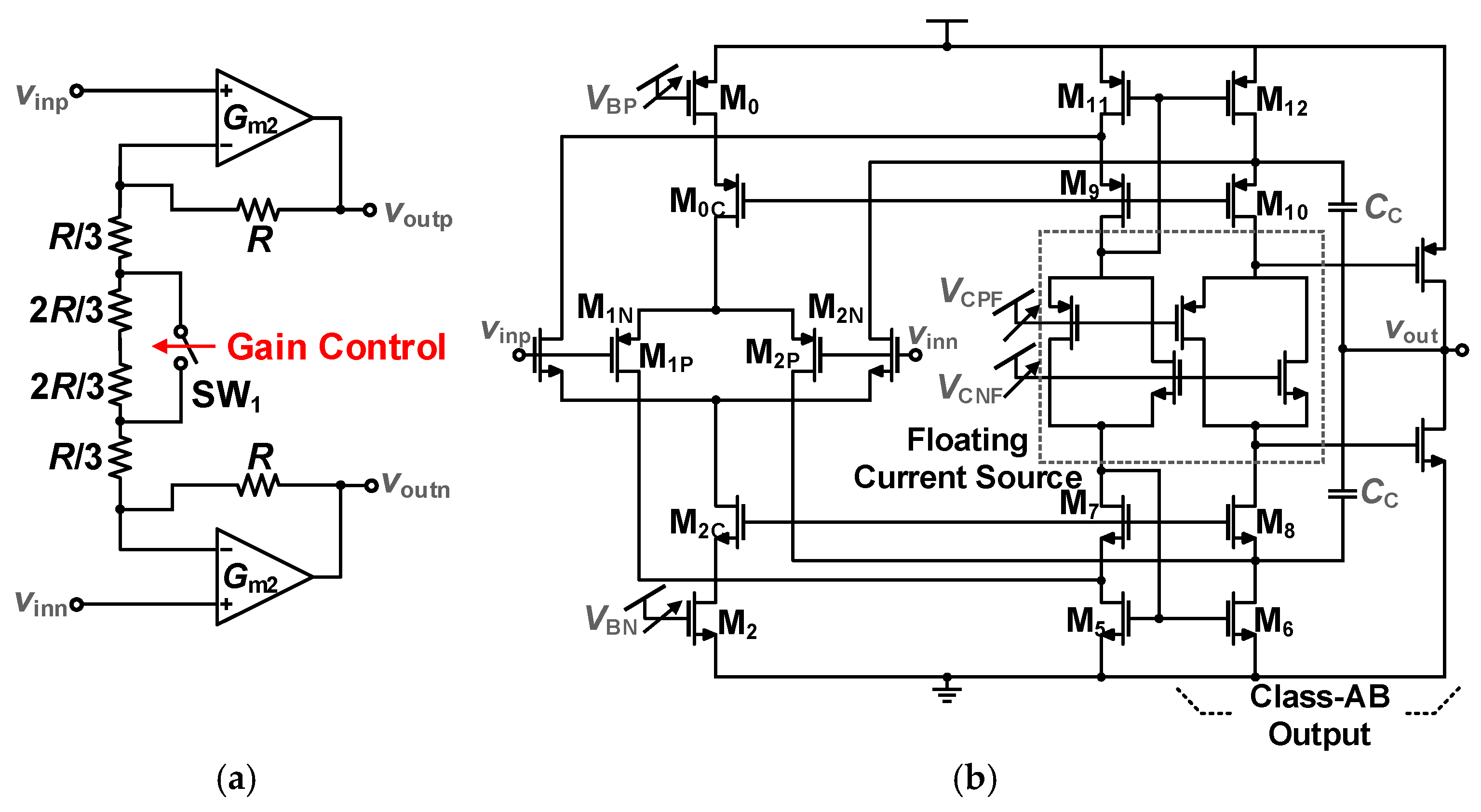

3.1.2. Programmable Gain Amplifier and TDM Buffer Design

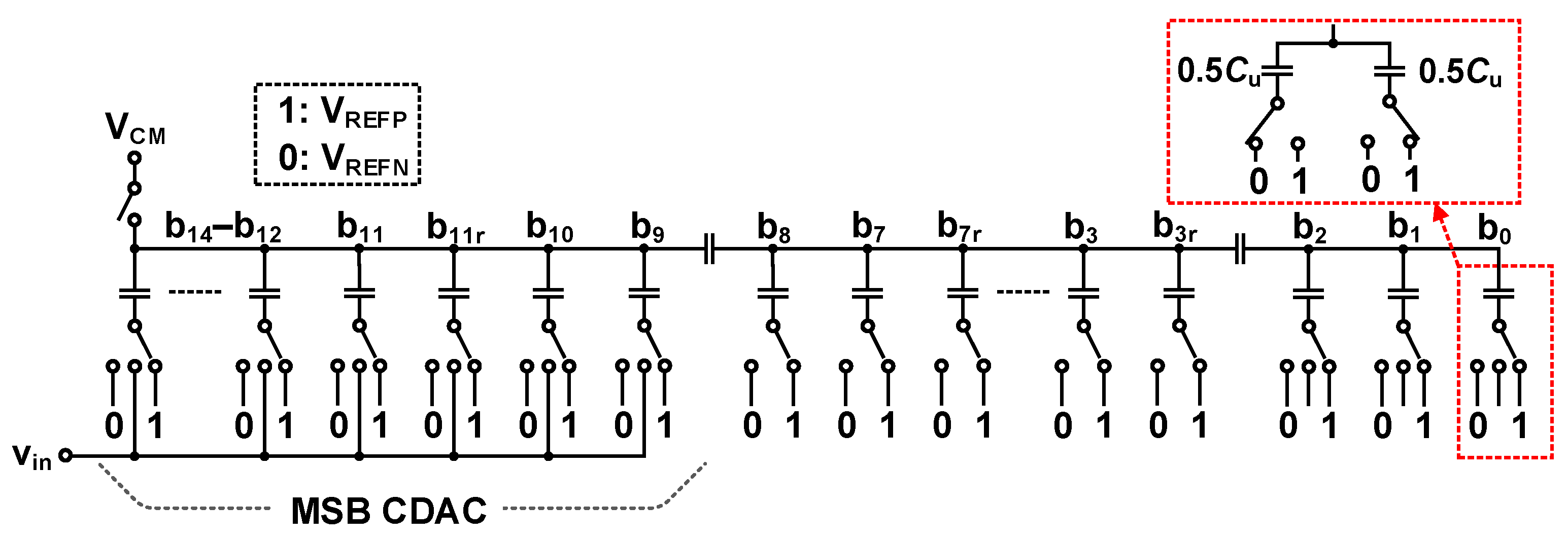

3.2. Analog-to-Digital Converter

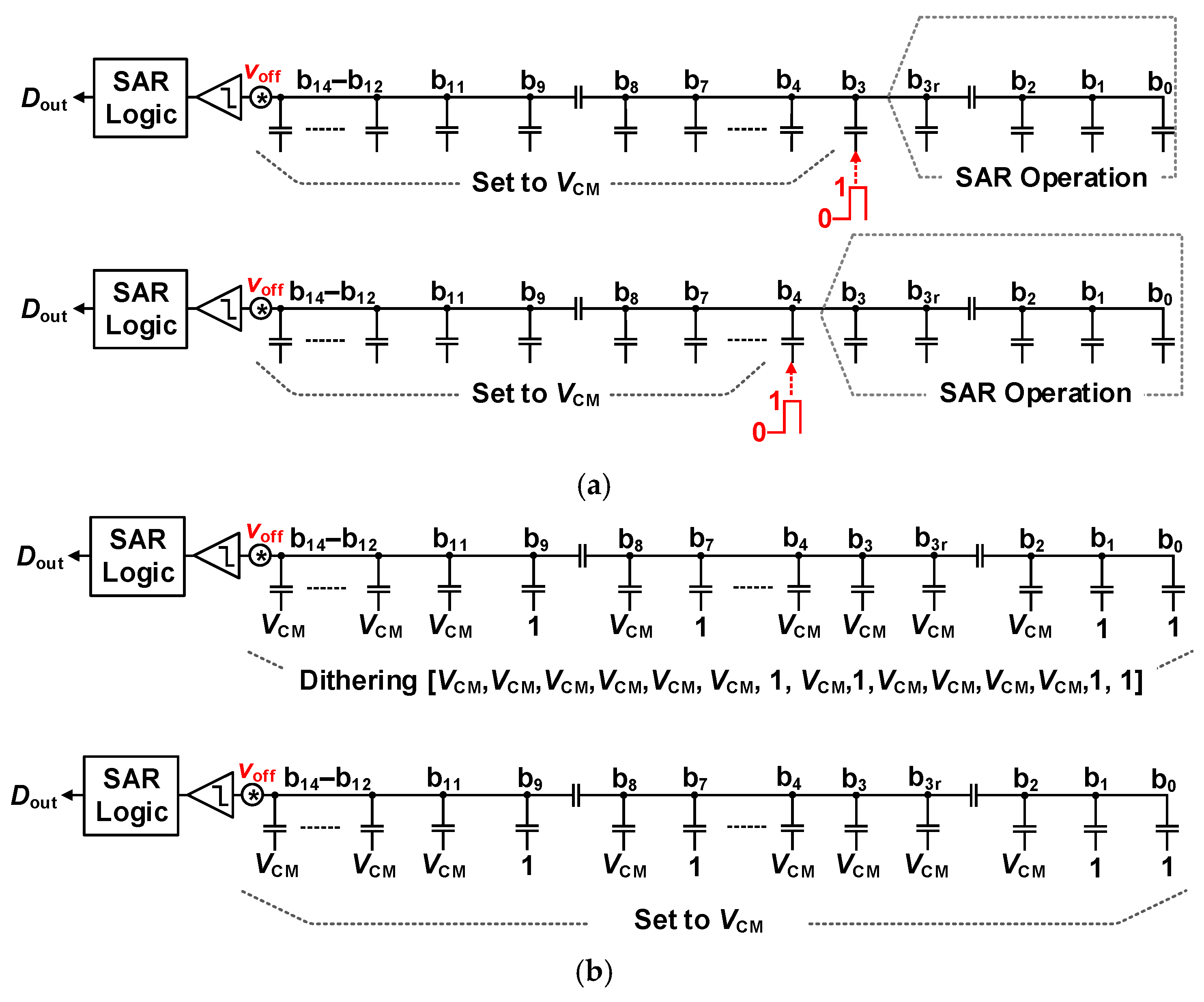

3.2.1. 16 b SAR ADC with Synchronous MSB and Asynchronous LSB Conversion

3.2.2. Foreground Calibration

3.3. Stimulation Pixel (SPX)

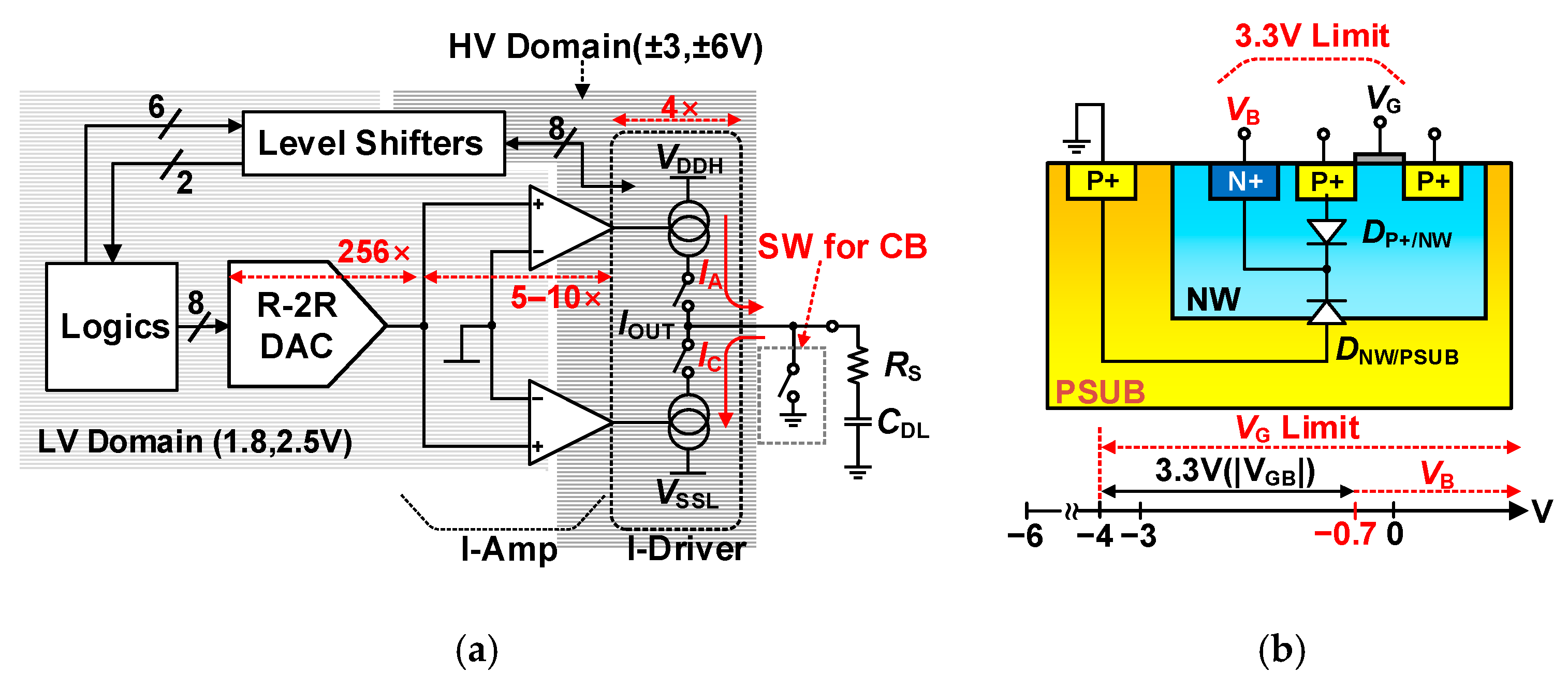

3.3.1. Current Driver for Stimulation

3.3.2. 8 b R-2R Digital-to-Analog Converter

3.3.3. Current Amplifier (I-Amp) and Level Shifters

3.4. Digital Interface

3.4.1. SPI and LVDS

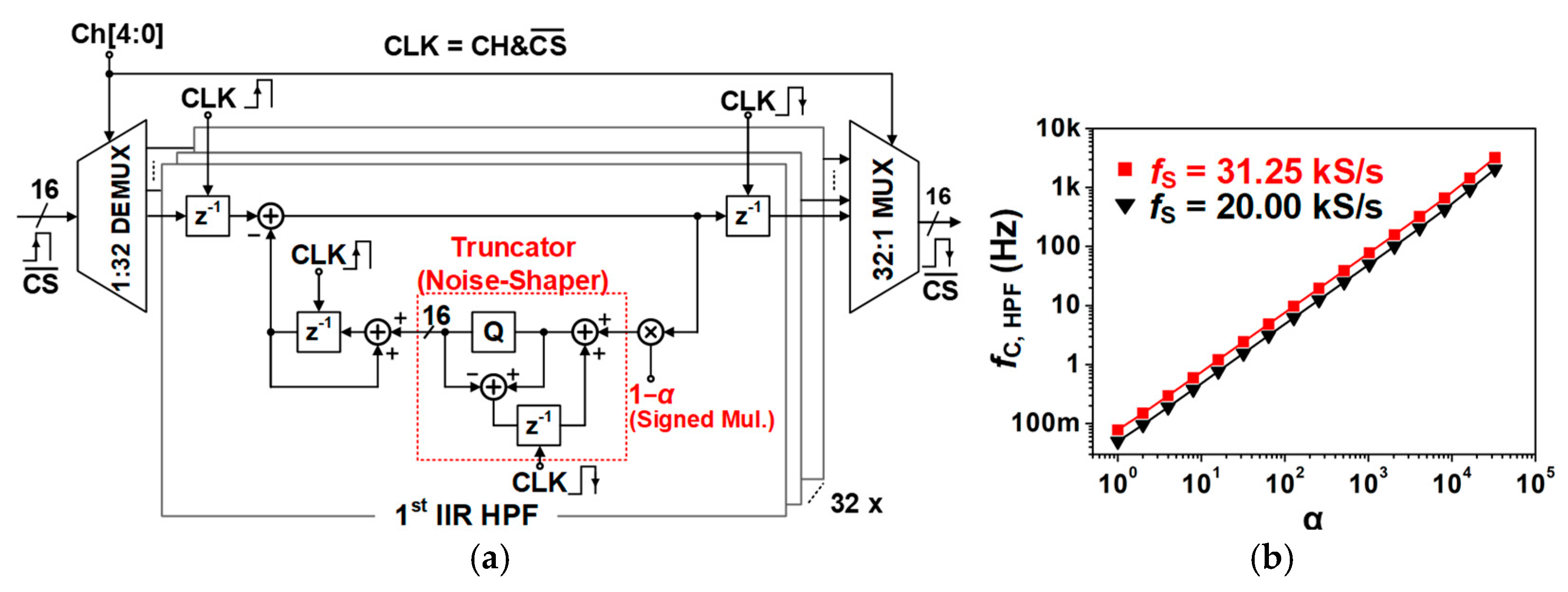

3.4.2. Digital High-Pass Filter

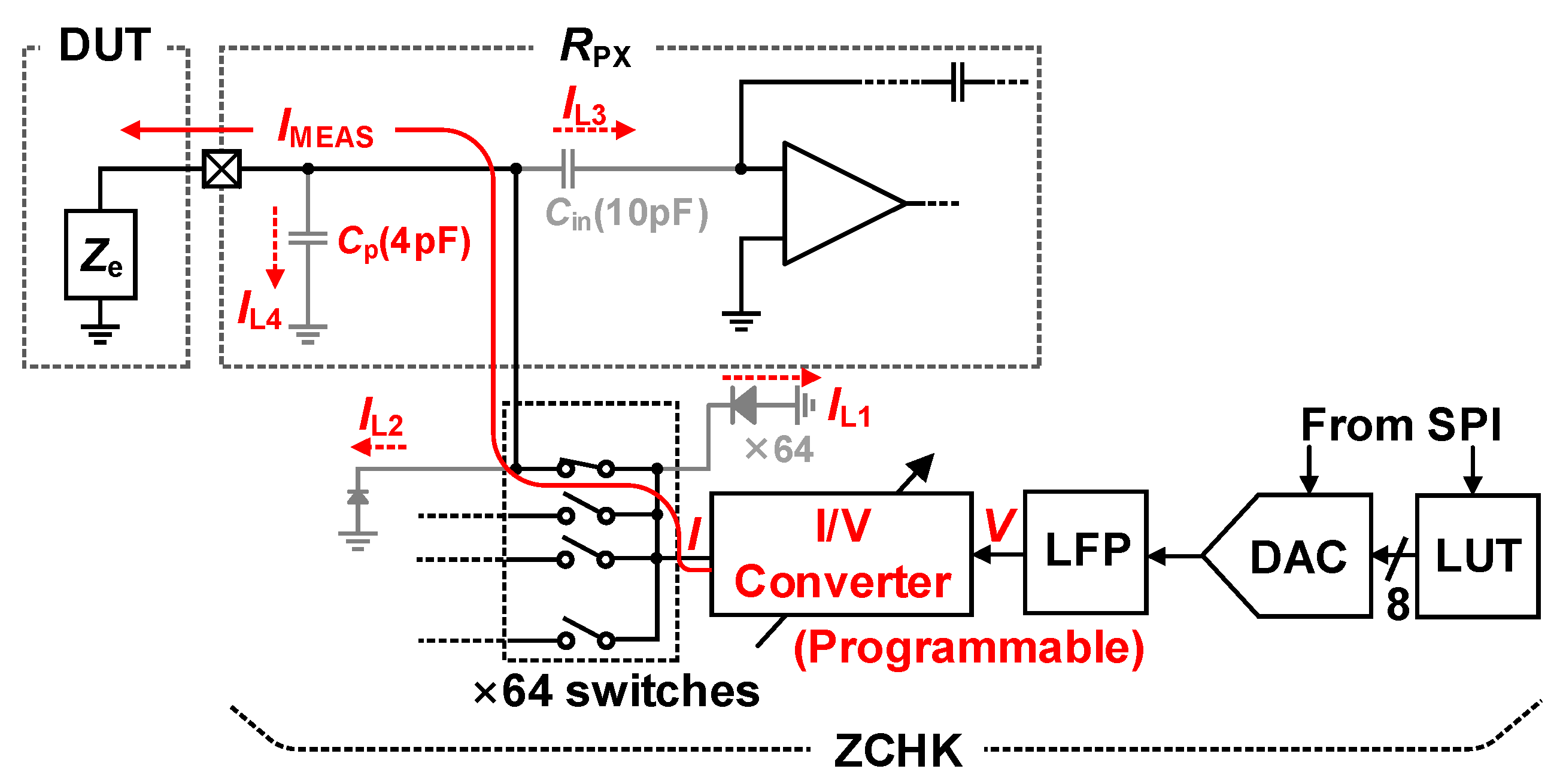

3.5. Impedance Measurement

3.6. Power Management Unit and β-Multiplier

4. Measurement

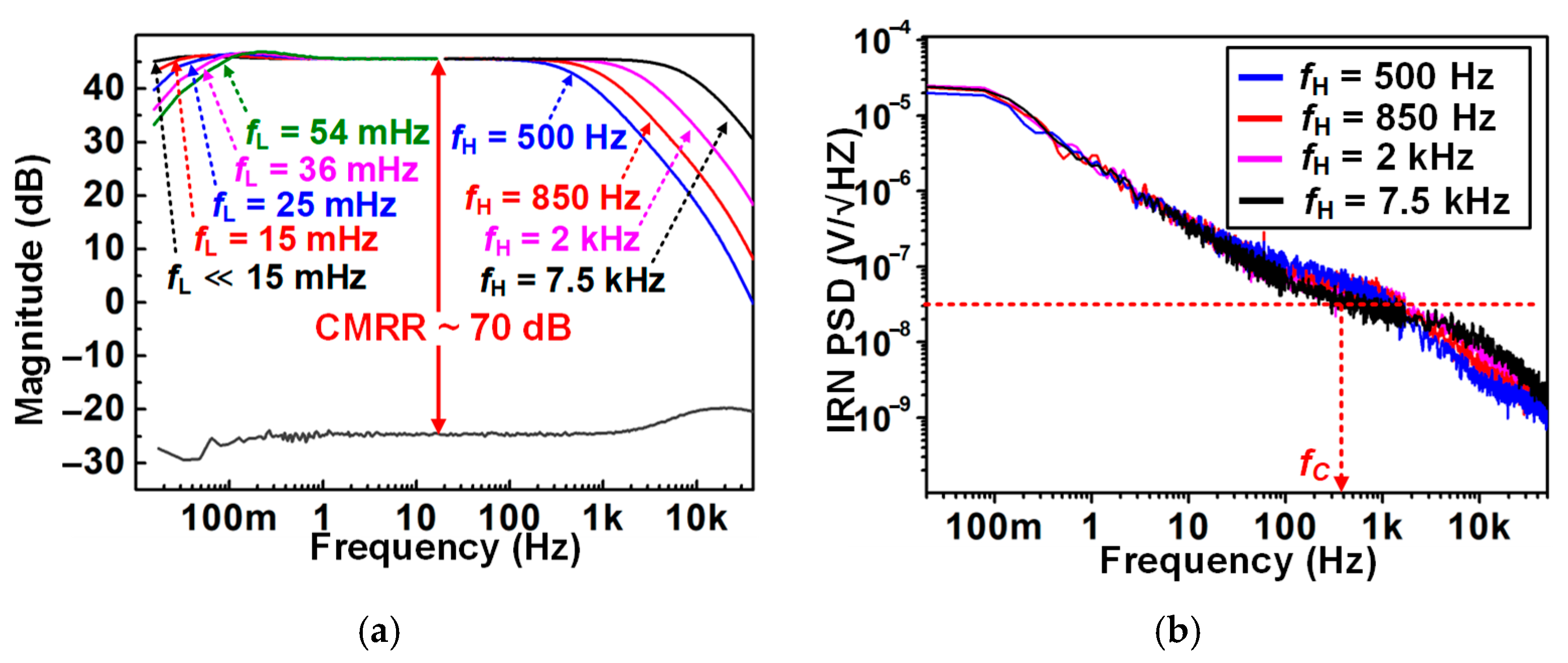

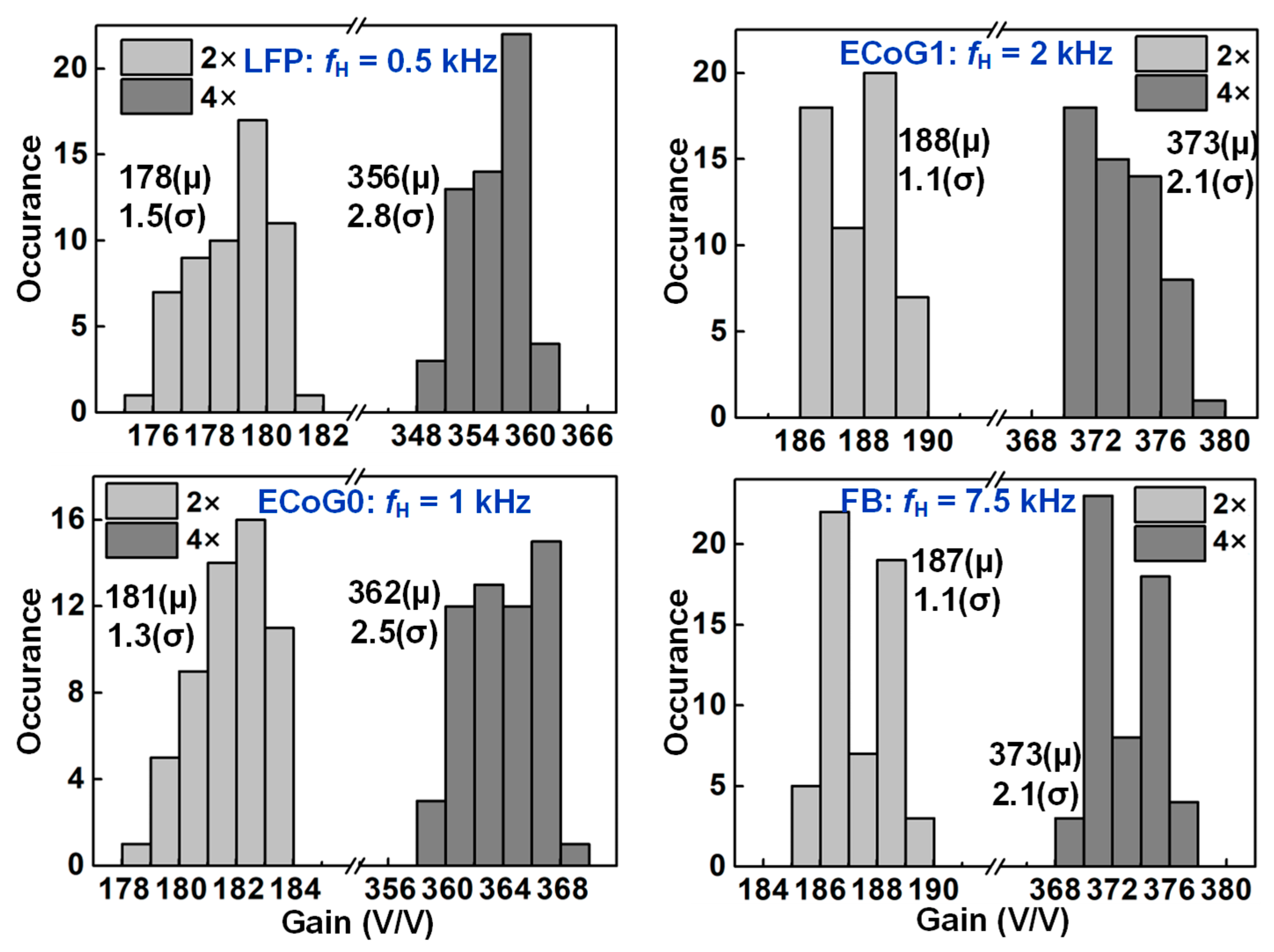

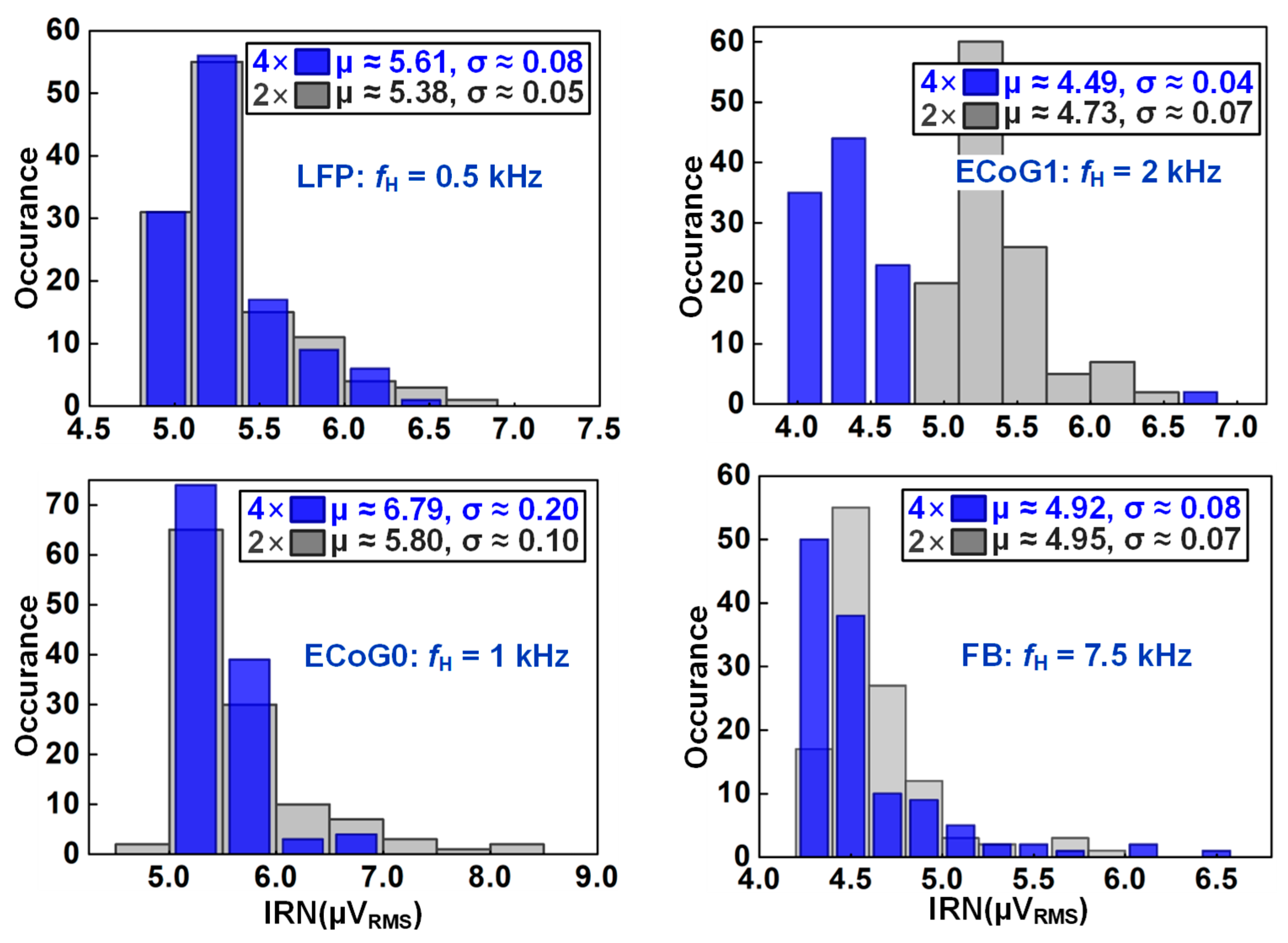

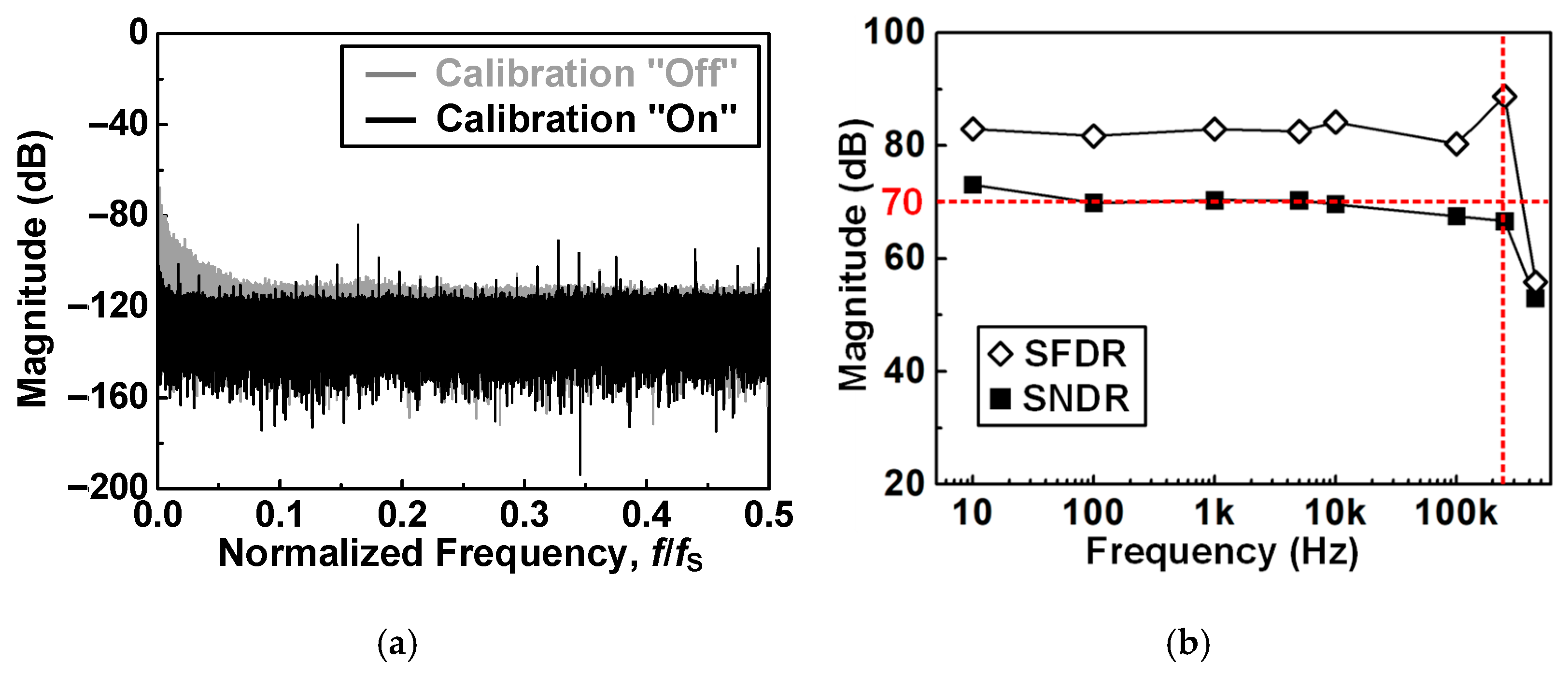

4.1. Recording Pixel (RPX) and ADC Measurement

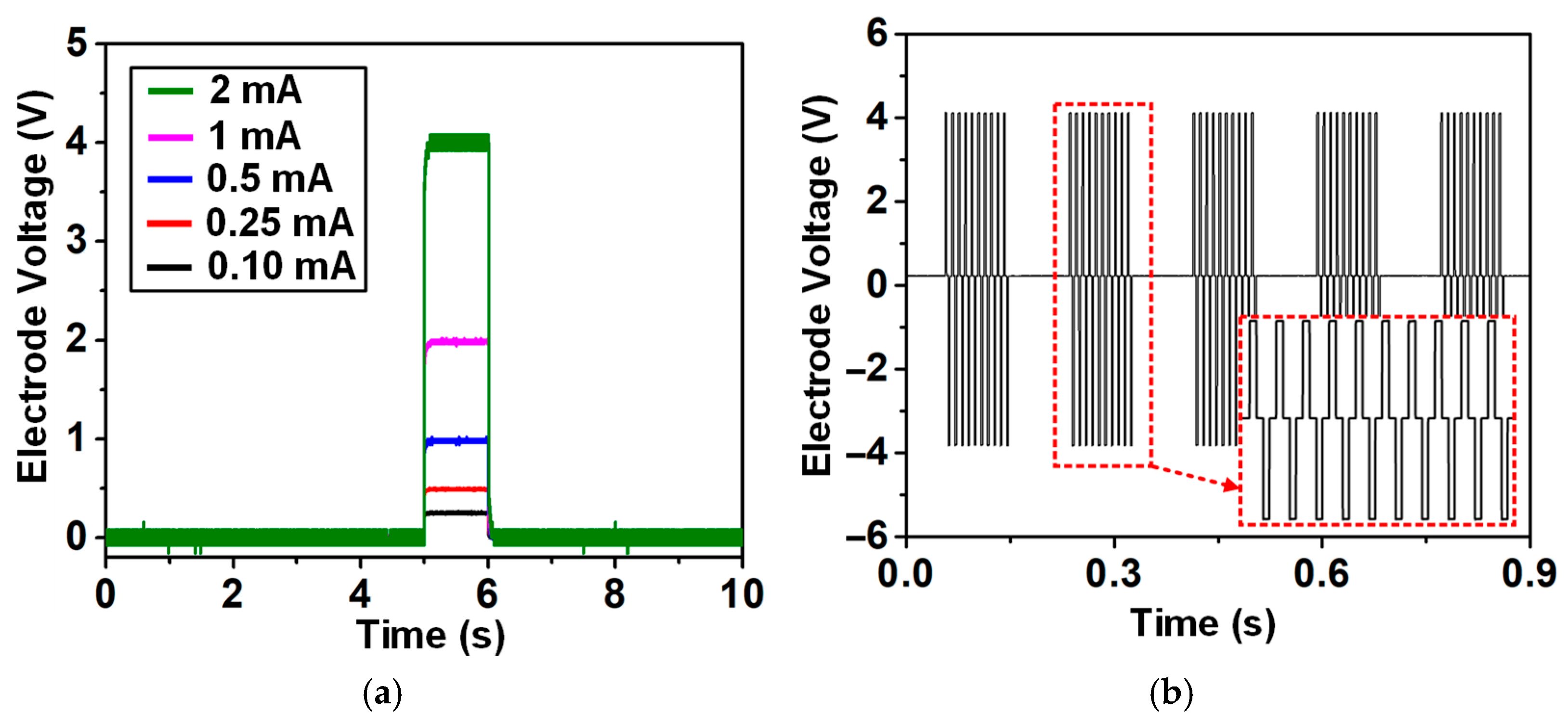

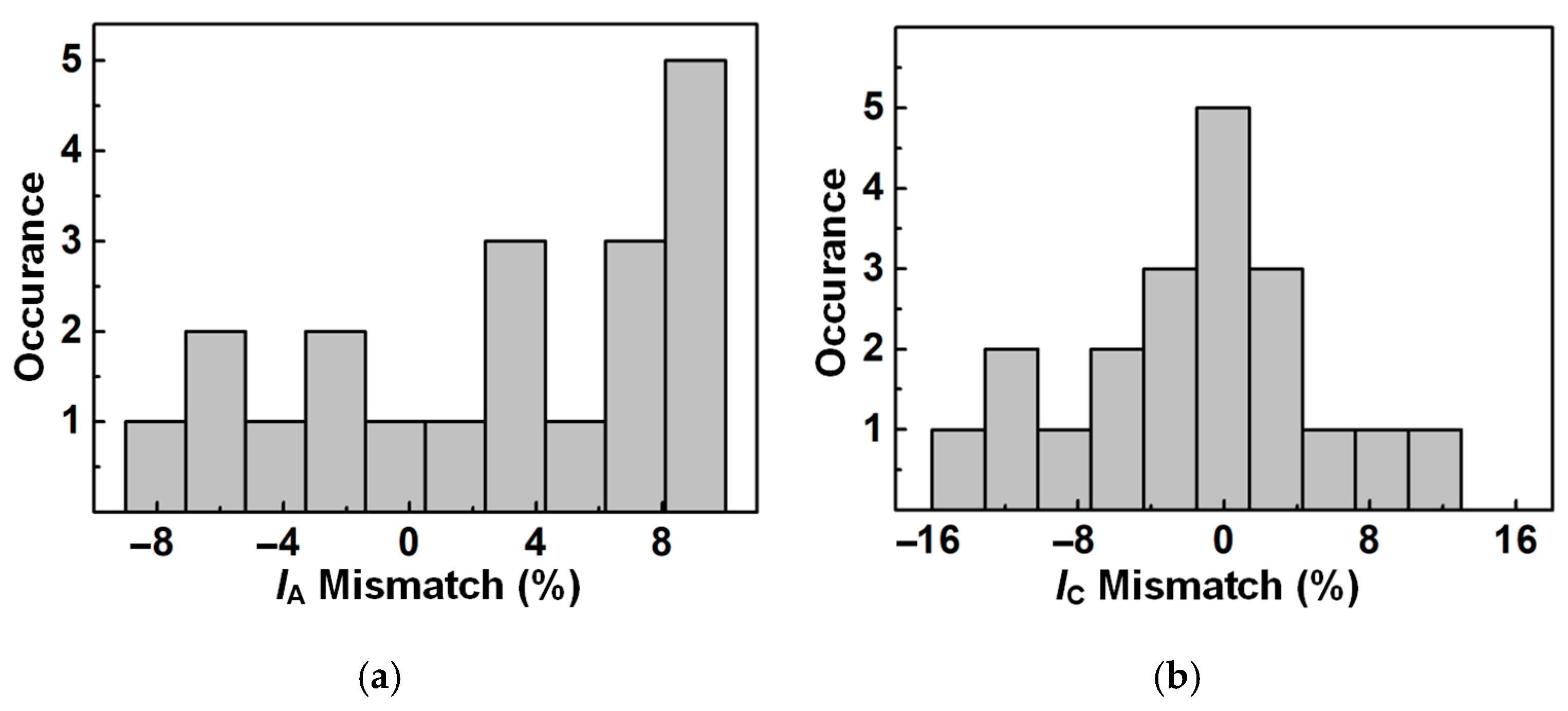

4.2. Stimulation Pixel (SPX) Measurement

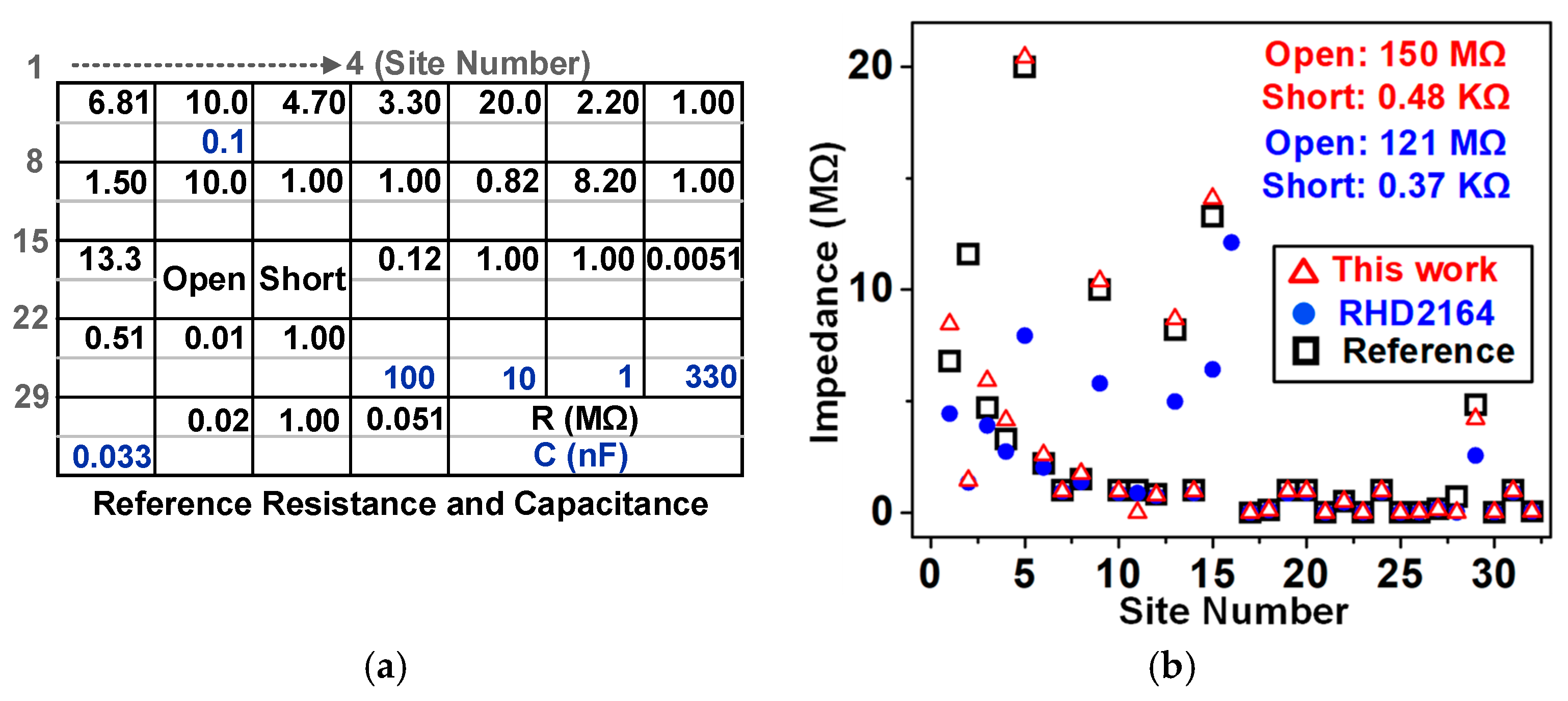

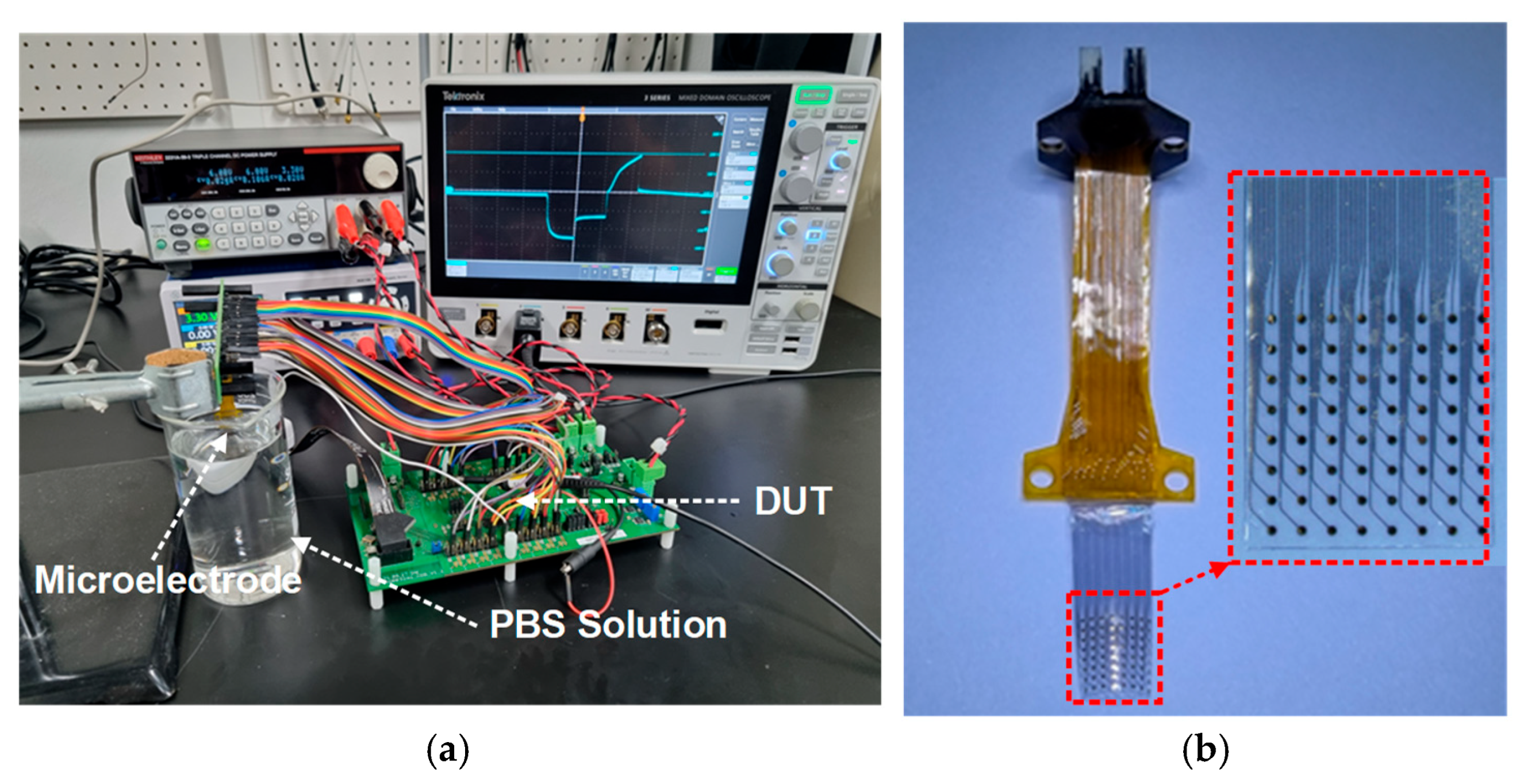

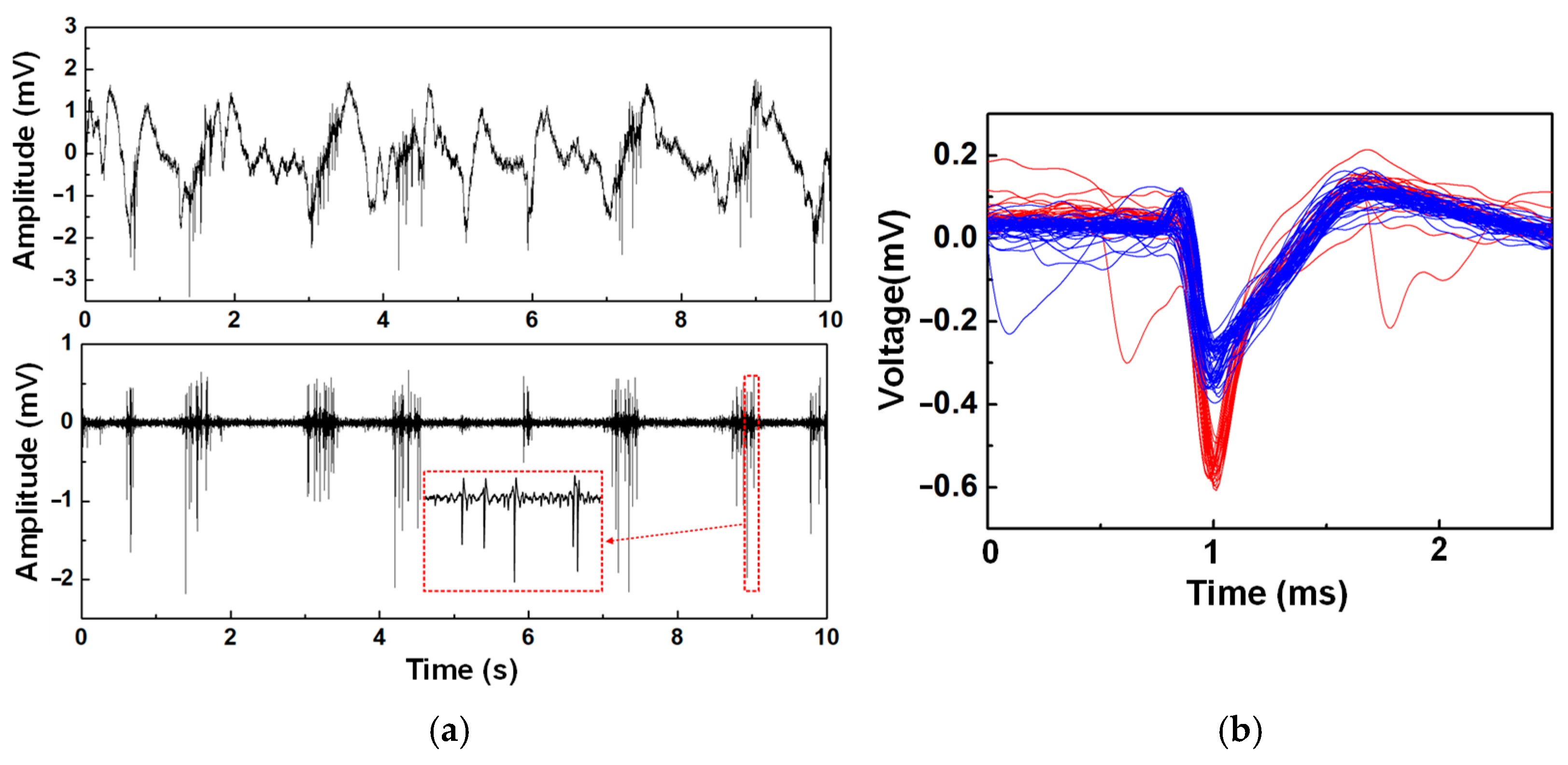

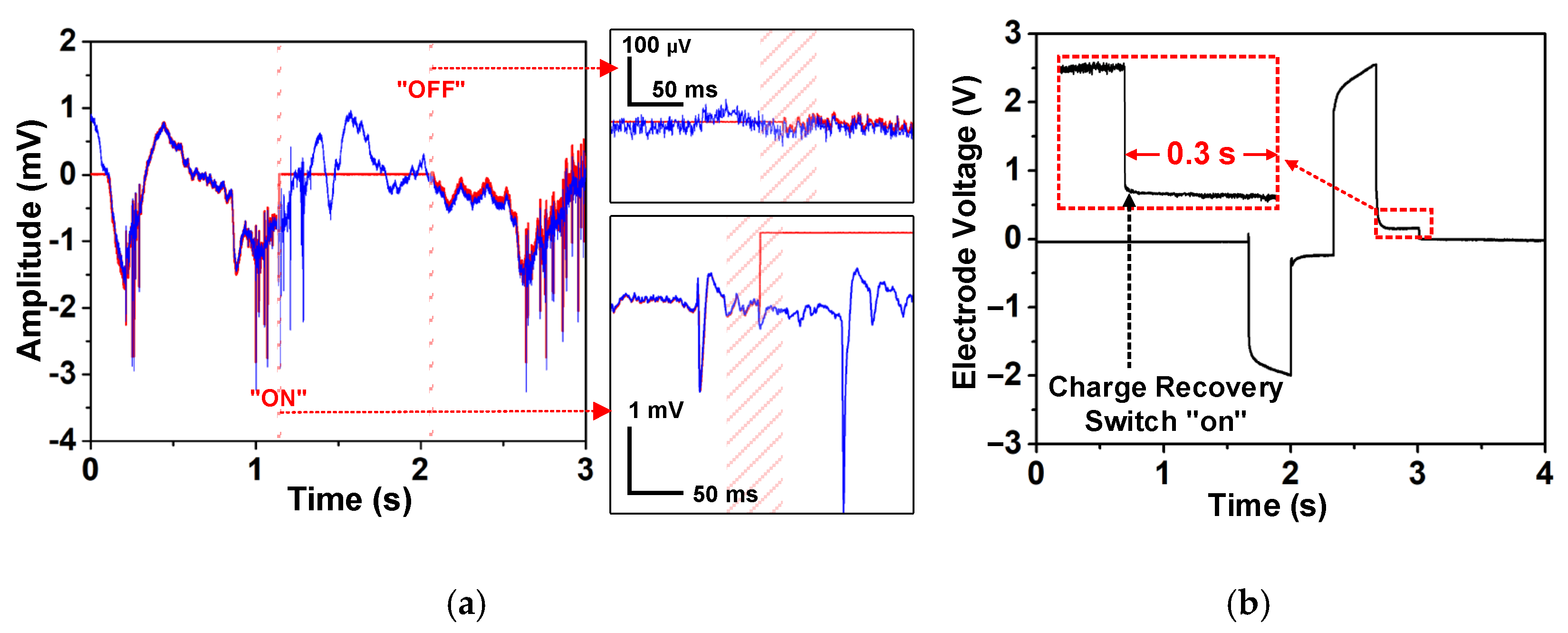

4.3. In Vitro Measurement and Summary

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Biederman, W.; Yeager, D.J.; Narevsky, N.; Leverett, J.; Neely, R.; Carmena, J.M.; Alon, E.; Rabaey, J.M. A 4.78 mm2 Fully-Integrated Neuromodulation SoC Combining 64 Acquisition Channels with Digital Compression and Simultaneous Dual Stimulation. IEEE J. Solid State Circuits 2015, 50, 1038–1047. [Google Scholar] [CrossRef]

- Reich, S.; Sporer, M.; Haas, M.; Becker, J.; Schuttler, M.; Ortmanns, M. A High-Voltage Compliance, 32-Channel Digitally Interfaced Neuromodulation System on Chip. IEEE J. Solid State Circuits 2021, 56, 2476–2487. [Google Scholar] [CrossRef]

- Pu, H.; Malekzadeh-Arasteh, O.; Danesh, A.R.; Nenadic, Z.; Do, A.H.; Heydari, P. A CMOS Dual-Mode Brain-Computer Interface Chipset with 2-mV Precision Time-Based Charge Balancing and Stimulation-Side Artifact Suppression. IEEE J. Solid State Circuits 2022, 57, 1824–1840. [Google Scholar] [CrossRef]

- Zhou, A.; Santacruz, S.R.; Johnson, B.C.; Alexandrov, G.; Moin, A.; Burghardt, F.L.; Rabaey, J.M.; Carmena, J.M.; Muller, R. A Wireless and Artefact-Free 128-Channel Neuromodulation Device for Closed-Loop Stimulation and Recording in Non-Human Primates. Nat. Biomed. Eng. 2019, 3, 15–26. [Google Scholar] [PubMed]

- Oh, S.; Kim, K.; Lopez Ruiz, J.R.; Slager, N.; Ko, E.; Vöröslakos, M.; Yoon, E. A compact, ultrahigh-density headstage with high-fidelity hybrid integration for large-scale deep-brain opto-electrophysiology. bioRxiv 2023. [Google Scholar] [CrossRef]

- Uehlin, J.P.; Smith, W.A.; Pamula, V.R.; Pepin, E.P.; Perlmutter, S.; Sathe, V.; Rudell, J.C. A Single-Chip Bidirectional Neural Interface with High-Voltage Stimulation and Adaptive Artifact Cancellation in Standard CMOS. IEEE J. Solid State Circuits 2020, 55, 1749–1761. [Google Scholar] [CrossRef]

- Park, S.-Y.; Na, K.; Voroslakos, M.; Song, H.; Slager, N.; Oh, S.; Seymour, J.P.; Buzsaki, G.; Yoon, E. A Miniaturized 256-Channel Neural Recording Interface with Area-Efficient Hybrid Integration of Flexible Probes and CMOS Integrated Circuits. IEEE Trans. Biomed. Eng. 2021, 69, 334–346. [Google Scholar] [CrossRef]

- Iwai, A.; Tanaka, M. Particle-Aligned Anisotropic Conductive Film (PAL-ACF) for Fine Pitch Interconnection; Hitachi Chemical: Tokyo, Japan, 2017. [Google Scholar]

- Jochum, T.; Denison, T.; Wolf, P. Integrated Circuit Amplifiers for Multi-Electrode Intracortical Recording. J. Neural Eng. 2009, 6, 012001. [Google Scholar] [CrossRef]

- Harrison, R.R.; Charles, C. A Low-Power Low-Noise CMOS Amplifier for Neural Recording Applications. IEEE J. Solid State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Song, S.M.; Kim, M.J.; Kim, J.G.; Park, H.T.; Park, Y.H.; Sik, K. 128-Channel Recording, 32-Channel Stimulation, Digitally Interfaced Optogenetic Neuromodulation System-on-Chip. IDEC J. Integr. Circuits Syst. 2022, 8, 1–9. [Google Scholar]

- Park, S.-Y.; Cho, J.; Na, K.; Yoon, E. Modular 128-Channel Δ-ΔΣ Analog Front-End Architecture Using Spectrum Equalization Scheme for 1024-Channel 3-D Neural Recording Microsystems. IEEE J. Solid State Circuits 2018, 53, 501–514. [Google Scholar] [CrossRef]

- Kim, H.-J.; Park, Y.; Eom, K.; Park, S.-Y. An Area- and Energy-Efficient 16-Channel, AC-Coupled Neural Recording Analog Frontend for High-Density Multichannel Neural Recordings. Electronics 2021, 10, 1972. [Google Scholar] [CrossRef]

- Ahuja, B.K. An Improved Frequency Compensation Technique for CMOS Operational Amplifiers. IEEE J. Solid State Circuits 1983, 18, 629–633. [Google Scholar]

- Hogervorst, R.; Tero, J.P.; Eschauzier, R.G.H.; Huijsing, J.H. A Compact Power-Efficient 3 V CMOS Rail-to-Rail Input/Output Operational Amplifier for VLSI Cell Libraries. IEEE Int. Solid State Circuits Conf. 1994, 29, 1505–1513. [Google Scholar] [CrossRef]

- Ginsburg, B.P.; Chandrakasan, A.P. 500-MS/s 5-bit ADC in 65-nm CMOS with Split Capacitor Array DAC. IEEE J. Solid State Circuits 2007, 42, 739–747. [Google Scholar]

- Harpe, P.; Huang, X.; Wang, X.; Dolmans, G.; De Groot, H. A 26 μW 8 bit 10 MS/s Asychronous SAR ADC for Low Energy Radios. IEEE J. Solid State Circuits 2011, 46, 7–10. [Google Scholar]

- Miyahara, M.; Asada, Y.; Paik, D.; Matsuzawa, A. A Low-Noise Self-Calibrating Dynamic Comparator for High-Speed ADCs. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Fukuoka, Japan, 3–5 November 2008; pp. 269–272. [Google Scholar]

- McNeill, J.A.; Chan, K.Y.; Coln, M.C.W.; David, C.L.; Brenneman, C. All-digital background calibration of a successive approximation ADC using the split ADC architecture. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2355–2365. [Google Scholar] [CrossRef]

- Liu, W.; Huang, P.; Chiu, Y. A 12-bit, 45-MS/s, 3-mW Redundant Successive-Approximation-Register Analog-to-Digital Converter with Digital Calibration. IEEE J. Solid State Circuits 2011, 46, 2661–2672. [Google Scholar]

- Shen, J.; Shikata, A.; Fernando, L.D.; Guthrie, N.; Chen, B.; Maddox, M.; Coln, M.C. A 16-bit 16-MS/s SAR ADC with On-Chip Calibration in 55-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 1149–1160. [Google Scholar] [CrossRef]

- Gagliardi, F.; Scintu, D.; Piotto, M.; Bruschi, P.; Dei, M. Static-Linearity Enhancement Techniques for Digital-to-Analog Converters Exploiting Optimal Arrangements of Unit Elements. IEEE Trans. Very Large Scale Integr. Syst 2024, 32, 2243–2256. [Google Scholar]

- Fan, H.; Li, J.; Maloberti, F. Order Statistics and Optimal Selection of Unit Elements in DACs to Enhance the Static Linearity. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2193–2203. [Google Scholar] [CrossRef]

- Merrill, D.R.; Bikson, M.; Jefferys, J.G.R. Electrical stimulation of excitable tissue: Design of efficacious and safe protocols. J. Neurosci. Methods 2005, 141, 171–198. [Google Scholar] [CrossRef] [PubMed]

- Georgiou, J.; Toumazou, C. A 126-μW Cochlear Chip for a Totally Implantable System. IEEE J. Solid-State Circuits 2005, 40, 430–443. [Google Scholar] [CrossRef]

- Lopes, E.M.; Rego, R.; Rito, M.; Chamadoira, C.; Dias, D.; Cunha, J.P.S. Estimation of ANT-DBS Electrodes on Target Positioning Based on a New PerceptTM PC LFP Signal Analysis. Sensors 2022, 22, 6601. [Google Scholar] [CrossRef]

- Plachta, D.T.T.; Gierthmuehlen, M.; Cota, O.; Boeser, F.; Stieglitz, T. BaroLoop: Using a multichannel cuff electrode and selective stimulation to reduce blood pressure. In Proceedings of the 2013 35th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Osaka, Japan, 3–7 July 2013; pp. 755–758. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits; Tsinghua University Press Co., Ltd.: Beijing, China, 2005. [Google Scholar]

- Hammerschmied, C.M. CMOS A/D Converters Using MOSFET-Only R-2R Ladders; Swiss Federal Institute of Technology Zurich: Zürich, Switzerland, 2000. [Google Scholar]

- Hsieh, C.C.; Ker, M.D. Monopolar Biphasic Stimulator with Discharge Function and Negative Level Shifter for Neuromodulation SoC Integration in Low-Voltage CMOS Process. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 568–579. [Google Scholar] [CrossRef]

- Yates, R.; Lyons, R.G. DC Blocker Algorithms. IEEE Signal Process. Mag. 2012, 25, 105–110. [Google Scholar]

- Intan Technology. RHD2164 Digital Electrophysiology Interface Chip; Intan Technology: Los Angeles, CA, USA, 2013. [Google Scholar]

- Plexon nanoZ User Manual. 2012. Available online: https://plexon.com/wp-content/uploads/2017/06/nanoZ-User-Manual-2012.pdf (accessed on 12 October 2025).

- Moon, H.; Jang, J.W.; Park, S.; Kim, J.H.; Kim, J.S.; Kim, S. Soft, conformal PDMS-based ECoG electrode array for long-term in vivo applications. Sens. Actuators B Chem. 2024, 401, 135099. [Google Scholar] [CrossRef]

- Intan Technology. RHS2116 Digital Electrophysiology Stimulator/Amplifier Chip; Intan Technology: Los Angeles, CA, USA, 2018. [Google Scholar]

| [1] | [2] | [3] | [4] | [35] | This Work | |

|---|---|---|---|---|---|---|

| Neuromodulation SoC | ||||||

| (a) # of Channel (R./S.) | (b) 64/2 | 32/32 | 32/4 | 128/8 | 16/16 | 128/32 |

| (c) System Integration | N | Y | Y | N | Y | Y |

| ZE Measurement | N | Y | N | N | Y | Y |

| Chip area (mm2) | 4.78 | 24.91 | 30.25(R) + 36(S) (Two chips) | 11.52 × 2 (Two chips) | 23.42 | 31.96 |

| Area/Ch (mm2) | 0.118 | 0.389 | 0.945/6 | 0.169 | 0.732 | 0.2 |

| System Power (mW) | − | (d) 6.2 | − | (h) 172 | 34.5 | 40.18 |

| Power/Ch (mW) | − | (d) 0.194 | − | (h) 1.265 | 1.078 | 0.251 |

| Technology | 65 nm CMOS | 180 nm BCD | 180 nm BCD | 180 nm BCD | − | 180 nm CMOS |

| Recording ASIC | ||||||

| IRN (μVrms) | 7.5 | 3.8/3.3 (LFP/AP) | 1.03 | (e) 1.02 | 2.4 | (i) 4 |

| BW (Hz) | 10–8 k | 0.2–7.5 k | 2–200 | (e) 1–200 | 0.1–20 k | 0.1–7.5 k |

| NEF | 3.6 | 3.1/4.5 (LFP/AP) | 2.37 | 15 | − | 8.9 |

| fS/Ch. (kS/s) | − | 20 | (e) 0.4 | 1 | 40 | 30 |

| ADC Resolution (bit) | 10 | 16 | 12 | 15 | 16 | 16 |

| ADC ENOB | 8.2 | 12.1 | 10.47 | 10.2 | − | 11.39 |

| FoMS (dB) | 167.1 | 153.2 | − | − | − | 160.4 |

| FoMW (fJ/c−s) | 4.25 | 1170 | − | − | − | 100.4 |

| Supply Voltage (V) | 1.0 | 1.8 | 1.0 | 1.0 | 3.3 | 3.3 |

| Fast Recovery | Y (switch) | N (−) | Y ((f) SSCS) | Y (Lin. Interp.) | Y (switch) | Y (switch) |

| Stimulation ASIC | ||||||

| Mono (M)-/Bipolar (B) | B | M | M | M | M | M |

| Resolution (bits) | 6 | 6 | 8 | 8 | 8 | 9 |

| Min. Current (μA) | 7 | 32 | − | − | 0.01 | 4 |

| Max. current (mA) | 0.9 | 10.2 | 12.75 | 5 | 2.55 | 2 |

| Voltage compliance (V) | 8 | ±9 | 40 | 12 | ±9 (−12/6) | ±6 |

| Multipolar stim. | N | Y | Y | Y | Y | Y |

| Charge Balancing | N | Y (switch) | Y ((g) TBCB) | Y (switch) | Y (switch) | Y (switch) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, G.; Kim, J.; Kim, M.; Kim, M.; Yoo, B.; Choi, J.; Kim, D.; Park, S.-Y. A Large-Scale Neuromodulation System-on-Chip Integrating 128-Channel Neural Recording and 32-Channel Programmable Stimulation for Neuroscientific Applications. Electronics 2025, 14, 4057. https://doi.org/10.3390/electronics14204057

Park G, Kim J, Kim M, Kim M, Yoo B, Choi J, Kim D, Park S-Y. A Large-Scale Neuromodulation System-on-Chip Integrating 128-Channel Neural Recording and 32-Channel Programmable Stimulation for Neuroscientific Applications. Electronics. 2025; 14(20):4057. https://doi.org/10.3390/electronics14204057

Chicago/Turabian StylePark, Gunwook, Joongyu Kim, Minjae Kim, Minsung Kim, Byeongwoo Yoo, Jeongho Choi, Daehong Kim, and Sung-Yun Park. 2025. "A Large-Scale Neuromodulation System-on-Chip Integrating 128-Channel Neural Recording and 32-Channel Programmable Stimulation for Neuroscientific Applications" Electronics 14, no. 20: 4057. https://doi.org/10.3390/electronics14204057

APA StylePark, G., Kim, J., Kim, M., Kim, M., Yoo, B., Choi, J., Kim, D., & Park, S.-Y. (2025). A Large-Scale Neuromodulation System-on-Chip Integrating 128-Channel Neural Recording and 32-Channel Programmable Stimulation for Neuroscientific Applications. Electronics, 14(20), 4057. https://doi.org/10.3390/electronics14204057