Abstract

In this study, a novel IR projector driver that can minimize nonuniformity in electric circuits, using a dual-current-programming structure, is proposed to generate high-quality infrared (IR) scenes for accurate sensor evaluation. Unlike the conventional current-mode structure, the proposed system reduces pixel-to-pixel nonuniformity by assigning two roles (data sampling and current driving) to a single transistor. A prototype of the proposed circuit was designed and fabricated using the SK-Hynix 0.18 µm CMOS process, and its performance was analyzed using post-layout simulation data. It was verified that nonuniformity, which is defined as the standard deviation divided by the mean radiance, could be reduced from 21% to less than 0.1%.

1. Introduction

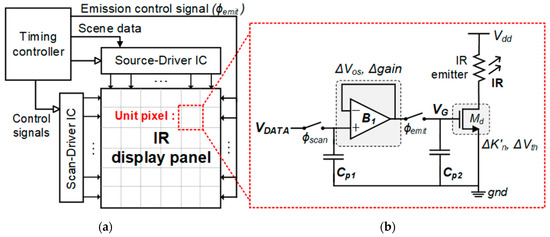

An infrared scene projector (IRSP) is a widely used piece of equipment that projects infrared (IR) images to investigate the performance of IR sensors [1,2,3,4,5,6,7]. These projectors are composed of IR emitters and driver integrated circuits (ICs) that are called read-in integrated circuits (RIICs) and are responsible for driving current to the IR emitters. High-quality IR scenes are required for accurately evaluating the performance of IR sensors; therefore, the IRSPs needs to be able to correct the nonuniformity between individual pixels of an IR emitter and an RIIC.

Currently, the look-up table (LUT) method is used to reduce the nonuniformity at each pixel [8,9,10,11,12,13,14]; however, as the radiance range of the overall pixels must be standardized to alower value to achieve uniform radiation, the performance of this method is hindered for a wide radiance range of IRSPs. Therefore, to obtain high-quality IR images for wide radiance ranges, a nonuniformity reduction in emitters and ICs is required in addition to external correction.

To improve circuit uniformities, several RIICs that adopt current-programming methods have been suggested [15,16]. However, to ensure the simultaneous IR emission of pixels [9,10], two transistors are separately needed for data sampling and current driving, hindering precise RIIC nonuniformity reduction.

In this paper, a novel RIIC design that enables precise nonuniformity compensation by adopting a dual-current-programming structure is proposed. In particular, with a mode-switching mechanism, a transistor can perform both data sampling and current driving, improving the uniformity of all pixels. Section 2 describes the implementation and analysis of the proposed nonuniformity-immune RIIC and its behavior is analyzed based on post-layout simulations presented in Section 3. Finally, conclusions are drawn in Section 4.

2. Proposed Nonuniformity-Immune RIIC

2.1. Nonuniformity Influences of the Conventional RIIC

The relationship between the current of the emitter, driven by the RIIC (Iemitter), and its final radiance (Γ) can be calculated using Equations (1) and (2) [17]:

where Temitter and Tsub are the temperatures of the emitter and substrate, respectively; Tapp is the apparent temperature considering the emissivity, ɛ, and fill factor, ff, of the IR emitter; G and R are the thermal conductance and resistance of the emitter, respectively. represents Planck’s equation; and are the wavelengths of interest; h, k and c are the Planck and Boltazman constants and the speed of light.

As indicated in Equation (1), Temitter, used to determine pixel radiance in Equation (3), is proportional to the square of Iemitter. As a result, the control of the current by RIIC is critical to reduce the radiance gap between pixels. In this study, R, G, ɛ, and ff were assumed equal to the ideal design parameters.

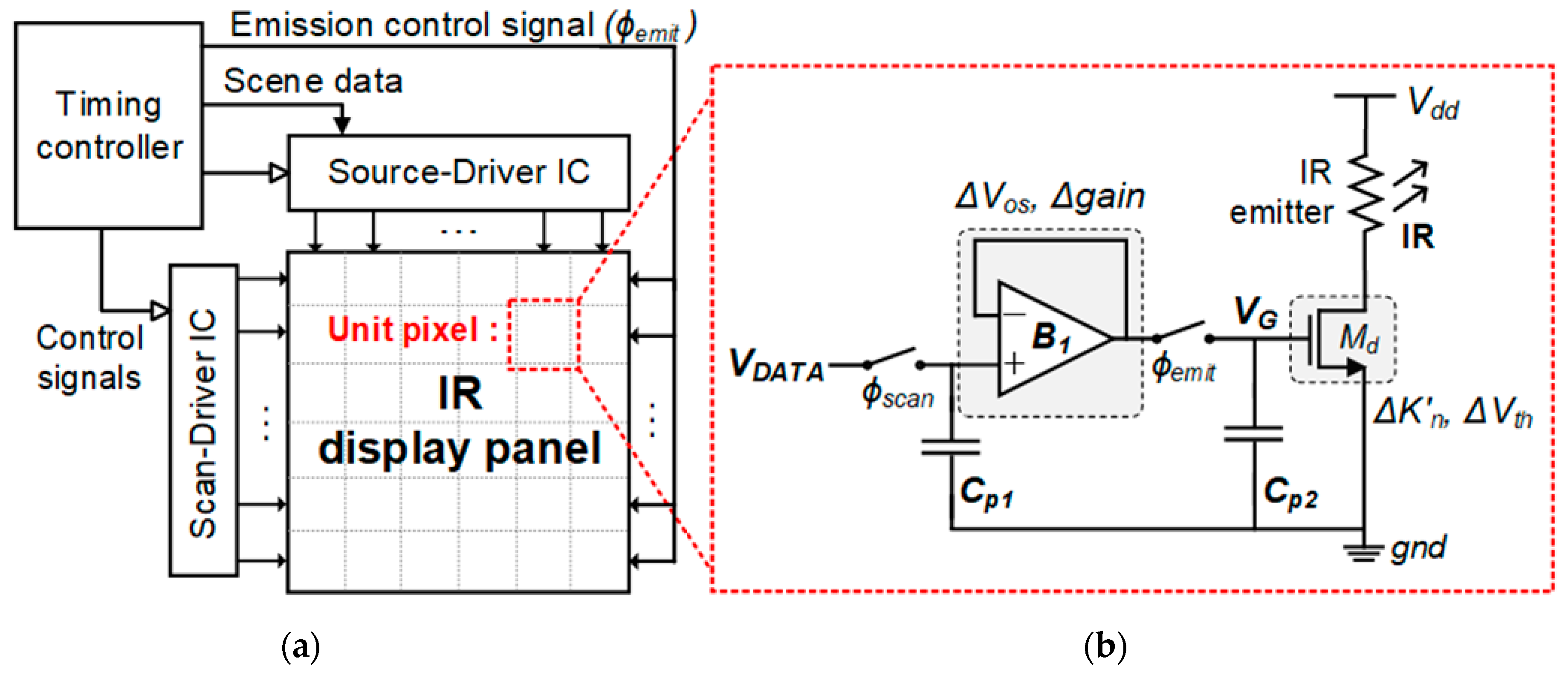

Figure 1a shows a block diagram of the RIIC. Every unit pixel of the IR display panel contains an IR emitter, represented as a resistor in Figure 1b. Conventional RIIC pixels contain two capacitors and a unity-gain buffer (B1), responsible for a synchronized IR emission (snapshot operation), resulting in high-speed scene generation without defects [17,18,19,20,21]. However, as the RIIC layout area is limited by the pitch of the emitter, the small-sized B1, shown in Figure 1b, is vulnerable to gain and offset errors that induce the nonuniformity of each pixel.

Figure 1.

(a) Overall block diagram; (b) conventional read-in integrated circuits (RIIC) unit pixel.

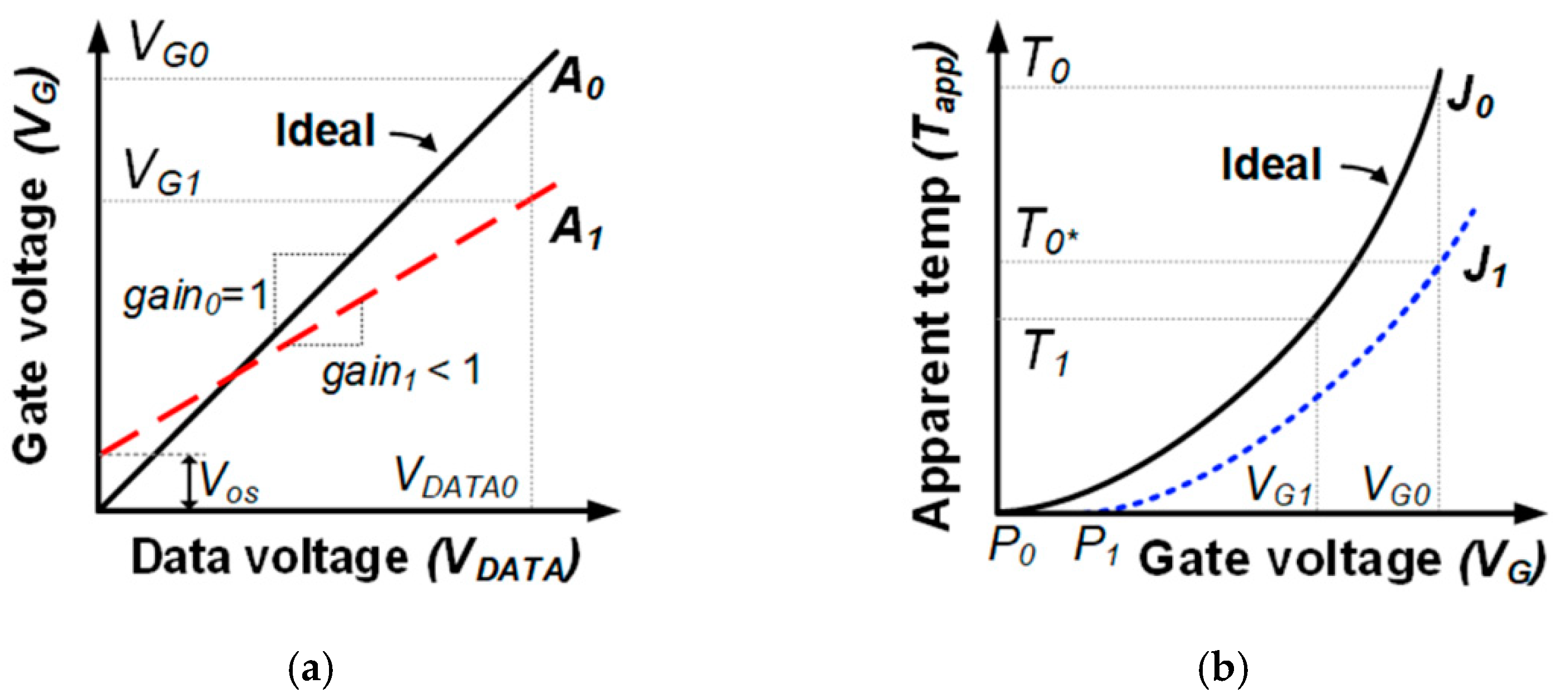

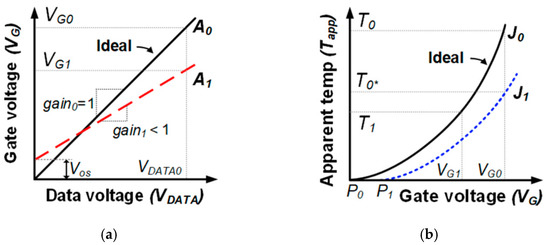

For example, in Figure 2a, the dotted line A1 represents a nonideal transfer curve affected by a gain and offset voltage (Vos) of the buffer. According to this curve, the voltage VG1, applied to the gate node (VG), is lower than that generated in an ideal situation, VG0, at the same data voltage VDATA0. This difference also affects the apparent temperature, as indicated by T0 and T1 in Figure 2b, resulting in pixel-to-pixel nonuniformity.

Figure 2.

Transfer curves: (a) data voltage against gate voltage; (b) gate voltage against apparent temperature (A1, J1: nonideal curves).

The relationship between Iemitter and VG can be represented using the following equation:

As shown in Equation (4), transistor mismatch parameters, the constant Kn (Kn = µn·Cox) and the threshold voltage Vth, result in the nonuniformity of Iemitter. As a result, even if the gate voltage is an ideal value VG0, the apparent temperature can be a nonideal value T0*, as indicated in J1 in Figure 2b. The x-axis intercept P1 and the slope of J1 are affected by the difference in Vth and K′n, respectively. Therefore, a novel circuit design that avoids buffer errors and current-driving transistor mismatch is desired.

2.2. Proposed Nonuniformity-Immune RIIC

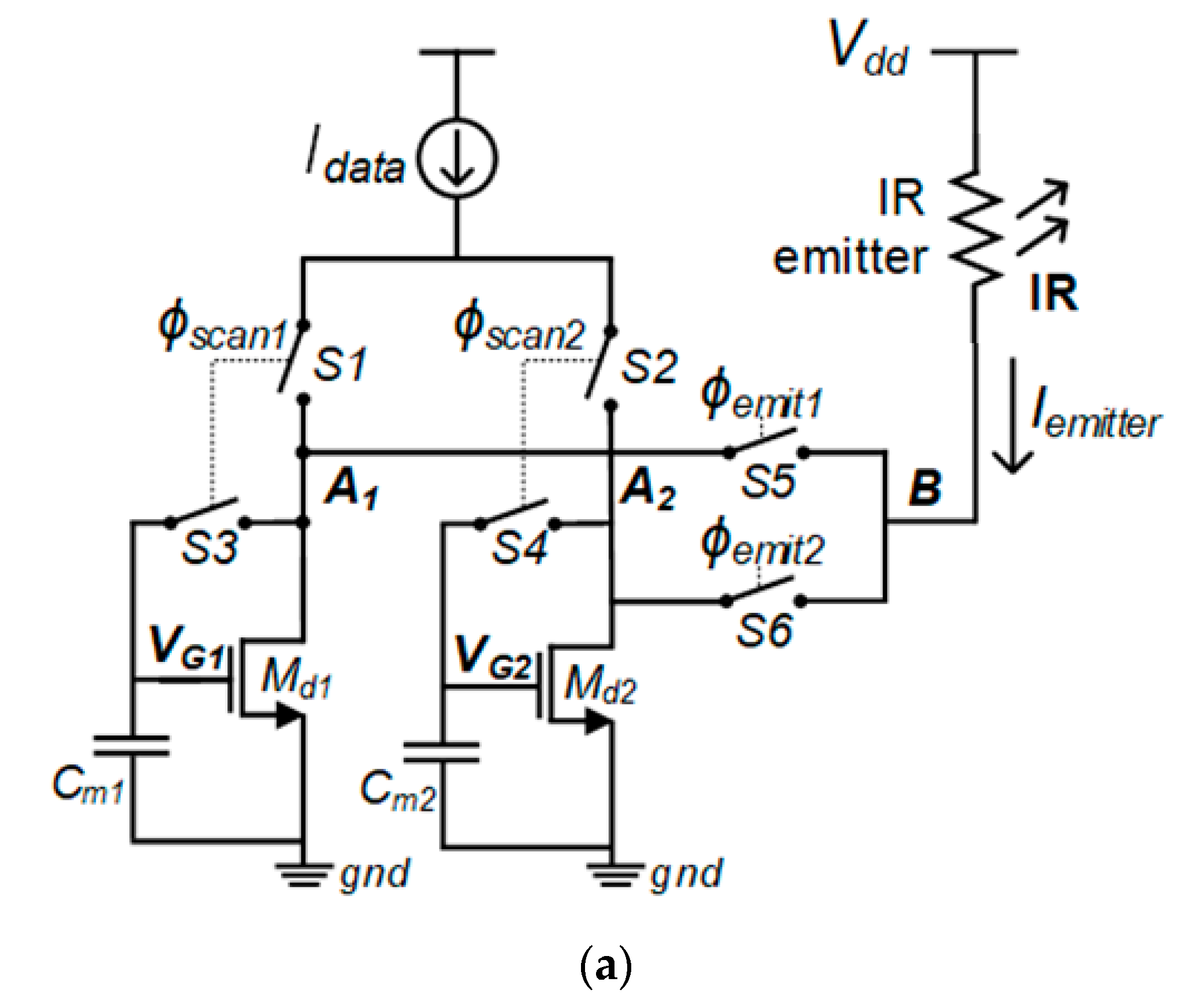

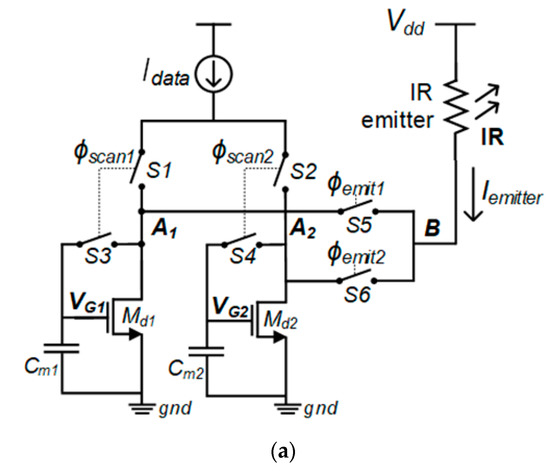

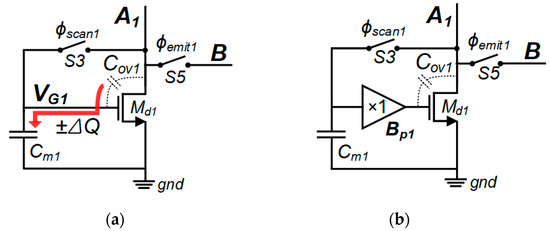

The proposed circuit comprises two current-driving transistors (Md1 and Md2), two capacitors (Cm1 and Cm2), and six switches (S1–S6), as shown in Figure 3a. The IR emitter is represented as a resistor in Figure 3a. Furthermore, Idata represents the current-type scene data, which can be designed using a current-output digital-to-analog converter or a current-output source-driver [15,16]. Meanwhile, the pixel circuit comprises a dual-current-programming structure. The first is composed of Md1, Cm1, S1, S3, and S5, while the other is formed by Md2, Cm2, S2, S4, and S6. In the timing diagram, Figure 3b, two operating phases, whose period is one frame time, continuously repeat.

Figure 3.

(a) Proposed RIIC unit pixel diagram; (b) corresponding timing diagram.

In phase I, the Idata passes through S1, S3, and Md1. As a result, the gate-source voltage of Md1 (Vgs1) is sampled in Cm1 and can be calculated using the following equation:

Unlike voltage-programmed pixels, the Vgs of the current-programmed pixel contains the mismatch parameters of Md1. In phase II, the S5 switch turns on, enabling Md1 to drive the current (Iemitter) to the emitter. In this stage, Iemitter can be calculated using the following equation:

It should be noted that the mismatch parameters of Md1 are canceled when Vgs from Equation (6) is substituted into Equation (5). As a result, when neglecting the channel-length modulation effect, the circuit can drive the emitter current regardless of the current-driving transistor mismatch. It should be noted that the Equations (4)–(6) are based on the operation in the saturation region; Md1 and Md2 need to operate in the saturation region. Thus, when designing the unit RIIC cell, the resistance of the IR emitter and the amount of current driven to the emitter needs to be considered for guaranteeing the drain-to-source voltages (Vds) of Md1 and Md2.

Md2 samples the data voltage in phase II and drives the current to the subsequent phase I. As a result, Md1 and Md2 can operate in sampling or driving modes, enabling a snapshot operation without a unity-gain buffer B1 and precise mismatch compensation. For example, in phase I, Md1 is in the sampling mode and Md2 is in the driving mode.

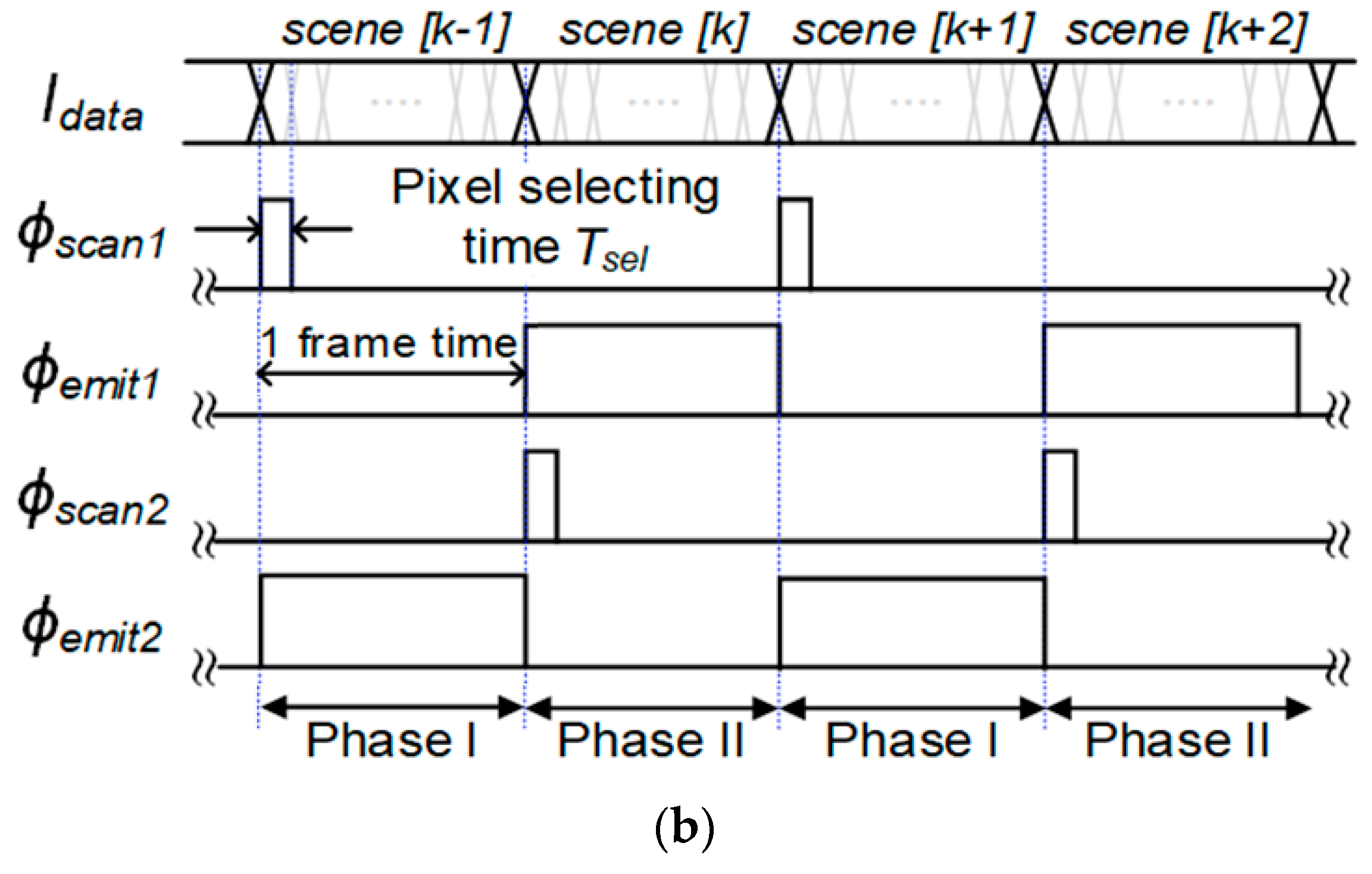

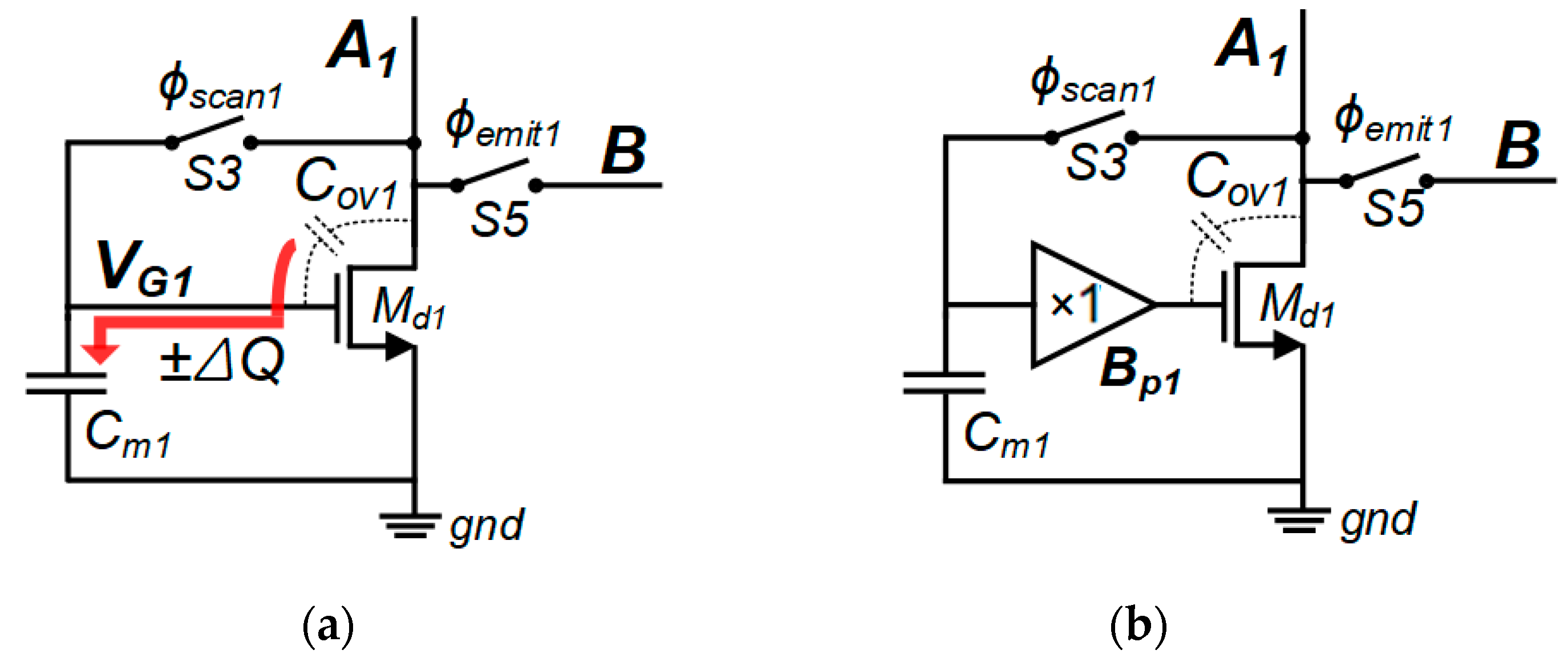

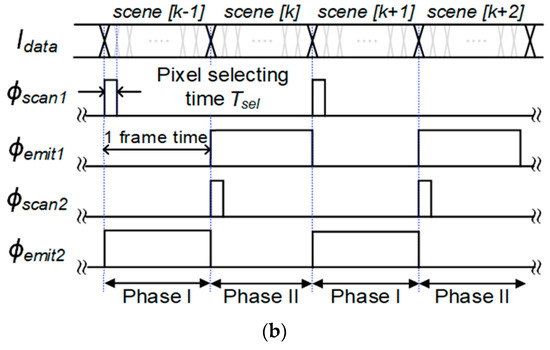

Figure 4 shows the circuit diagram between the A1 and B nodes in Figure 3a. In the sampling mode, when S3 is turned on, the drain-source voltage of Md1 (Vds1) is identical to the gate-source voltage of Md1 (Vgs1). However, in the driving mode, the Vds1 changes according to Vdd Iemitter∙R, generating an unexpected charge (ΔQ) at the gate node (VG1). This generated error voltage (Verror,gs1) can be estimated using Equation (7), derived from the charge conversion law [22]:

Figure 4.

Buffer addition to improve data sampling accuracy: (a) pixel design without a buffer; (b) pixel design with a buffer.

The error voltage also results in a current error, which can prevent accurate IR scene generation. Furthermore, the cascode structure, which is commonly used to neglect the effect of ∆Vds, cannot be used in the pixel as it prevents the dual functionality of Md1 and Md2. To avoid the existence of ΔQ, a unity-gain buffer (Bp1) is inserted, as shown in Figure 4b. In particular, Bp1 is placed in a feedback loop during the sampling mode, preventing the pixel-to-pixel nonuniformity due to buffer errors.

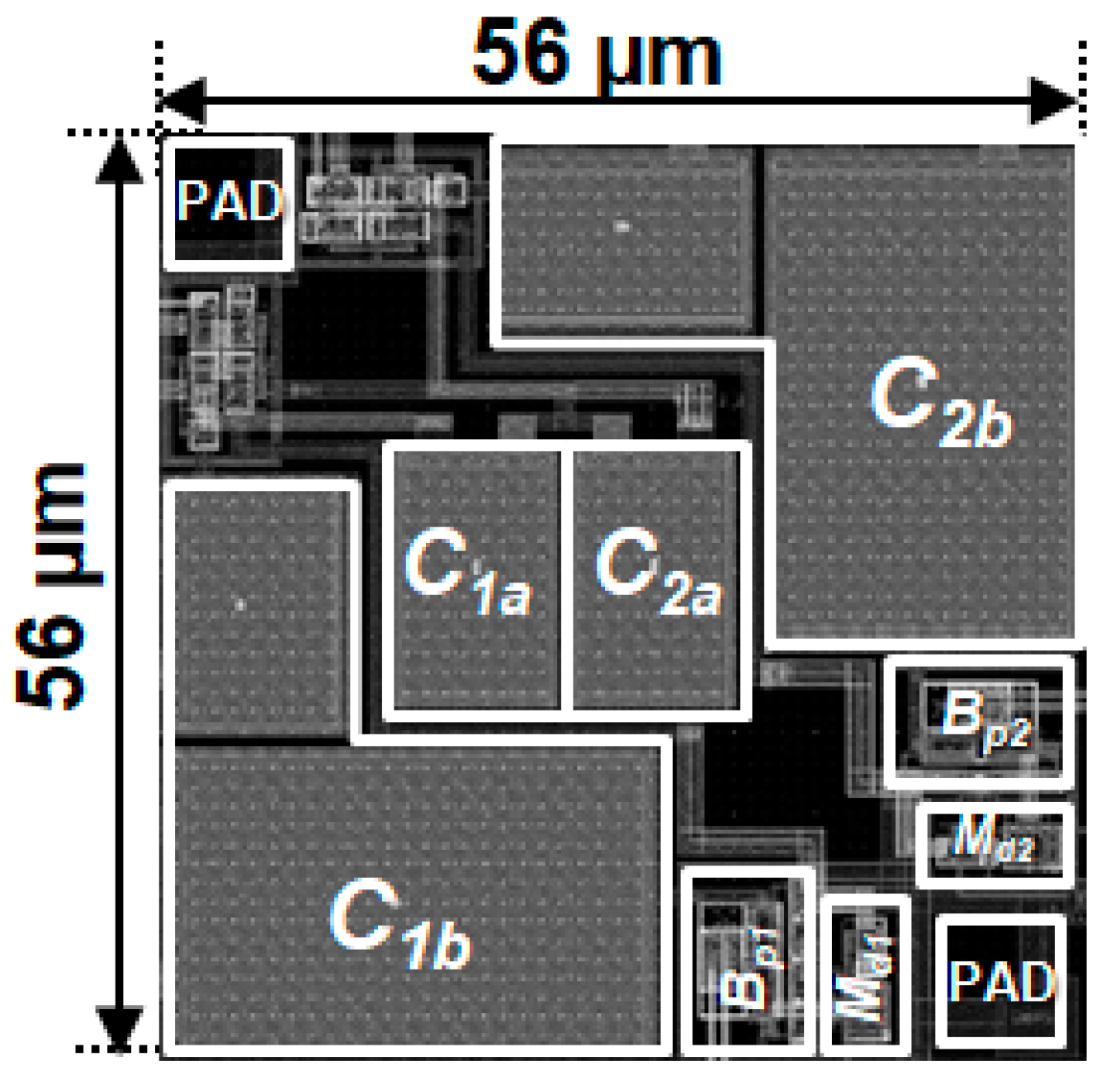

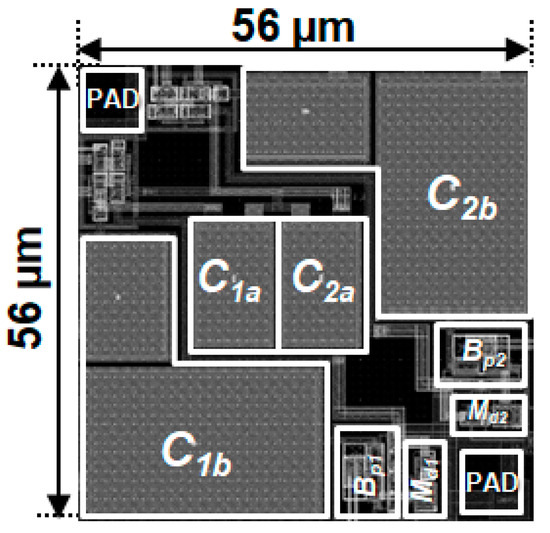

Figure 5 shows the mask layout of the proposed RIIC pixel with two buffers (Bp1, Bp2) in a 56 µm pitch. The W/L parameters of Md1 and Md2 are both 10/10. Two pads are located in each pixel to establish a connection with the IR emitter device. Considering the symmetry of the layout, C1 is divided into two subcomponents (C1a and C2b) whose sizes are 150 fF and 600 fF, as shown in Figure 5. C2 is analogously divided into C2a and C2b.

Figure 5.

Mask layout of the proposed unit pixel in a 56 µm pitch.

3. Simulation Results and Analysis

3.1. Data Sampling Accuracy

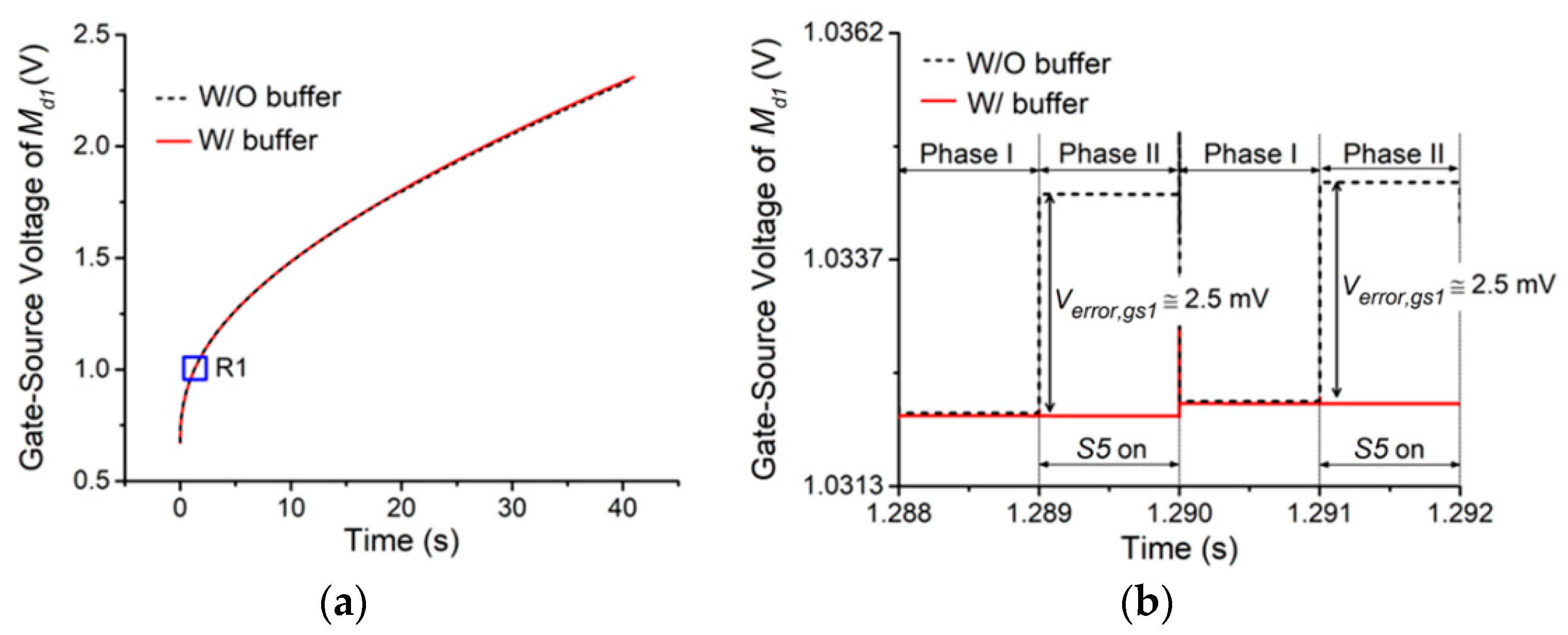

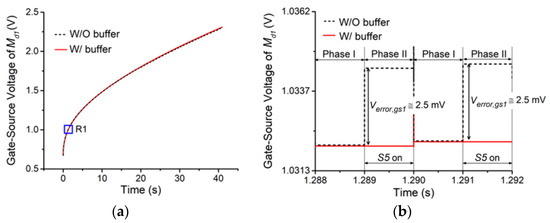

To verify the feasibility of the proposed circuit, a prototype RIIC was designed via an SK-Hynix 0.18 µm CMOS process and apost-layout simulation on Cadence software (Cadence Design Systems, Inc., San Jose, CA, USA) was performed. The data current (Idata) varied from 0.1 to 200 μA, and the measured gate-source voltage of Md1 varied as plotted in Figure 6. To verify the operating speed, the Idata varied by one frame time 1/100 Hz = 10 ms, and the pixel-selecting time (Tsel) shown in Figure 3b was set to 1/(100 × 64 × 64) = 2.4 µs.

Figure 6.

Post-layout simulation results: (a) gate-to-source voltage of Md1 while varying the current data from 0.1 to 200 μA; (b) magnified view of region R1.

From the simulation results, the gate voltage error (Verror,gs1 = 2.5 mV) disappeared by using the Bp1, as indicated by the solid line in Figure 6b. Therefore, the unity-gain buffer helps maintain the sampled voltage regardless of the operational phase of the circuit.

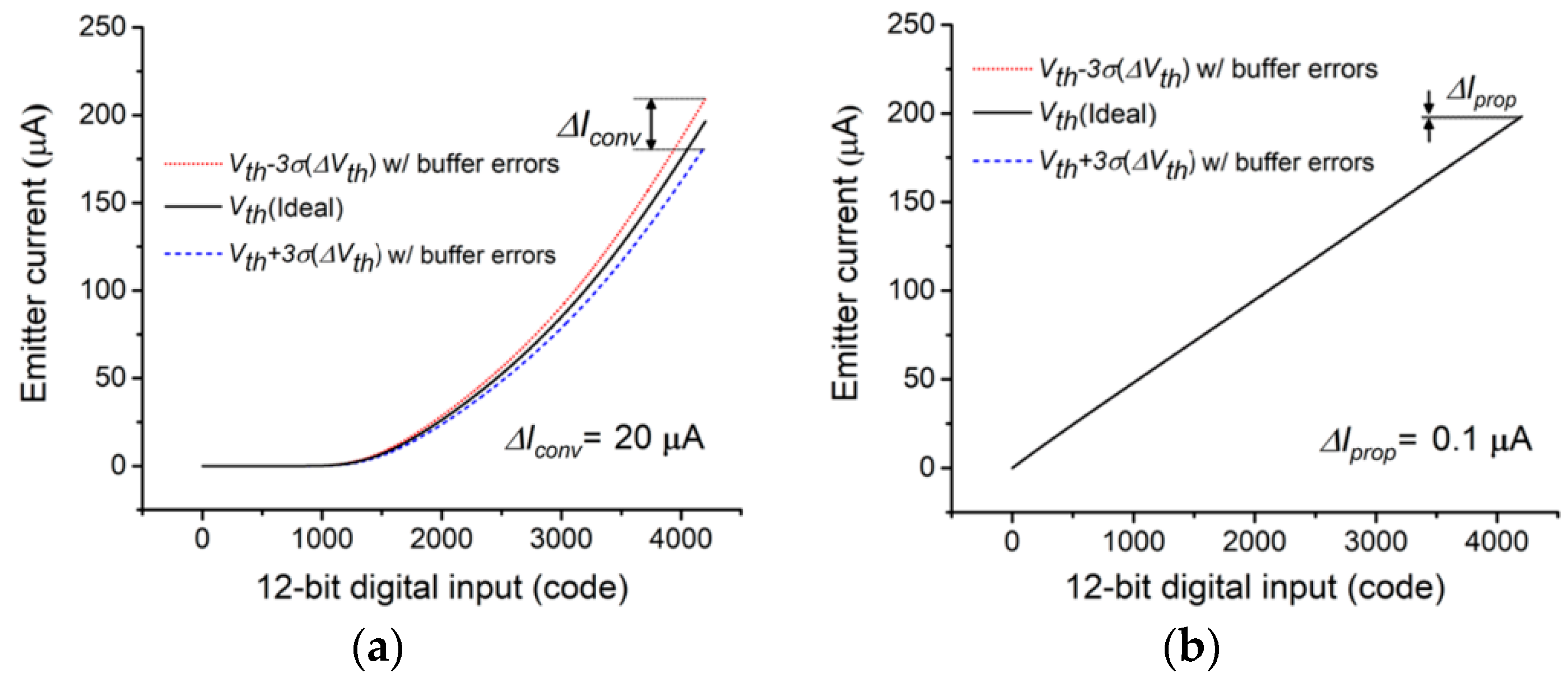

3.2. Evaluation of Nonuniformity

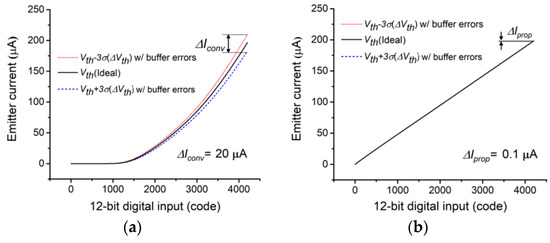

To evaluate the improvement in pixel-to-pixel uniformity, deviations in some quantities were purposefully inserted during the post-layout simulations. The offset voltage and gain error of B1, which were estimated based on the mismatch parameters of the CMOS process, were set to 16 mV and 2%, respectively. The standard deviation () of the threshold voltage was set to 3 mV following the data sheet of the CMOS process. Furthermore, the widths and lengths of Md, Md1 and Md2 were identical. Moreover, the maximum current of the conventional RIIC was defined, according to the proposed RIIC, as 200 µA. This value is sufficient for the circuit to achieve the target temperature range listed in Table 1. Figure 7a,b shows the acquired emitter current data driven by the conventional RIIC and proposed RIIC, respectively.

Table 1.

Target infrared scene projector (IRSP) properties.

Figure 7.

Emitter current of the IR emitter: (a) conventional RIIC; (b) proposed RIIC.

Using the current data acquired from the simulation, the apparent temperature was calculated using Equations (1) and (2): the desired properties of the IR emitter used in this calculation are listed in Table 2.

Table 2.

Target IR emitter properties.

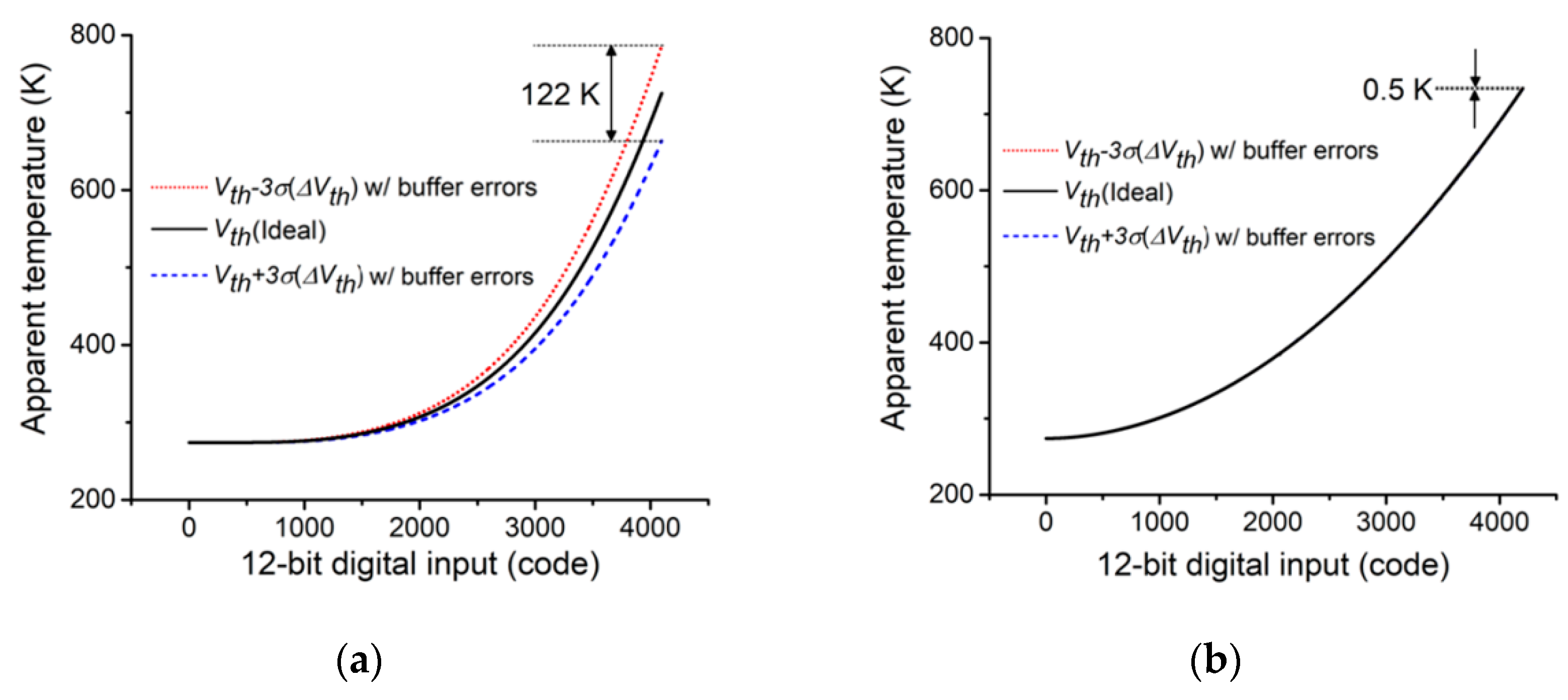

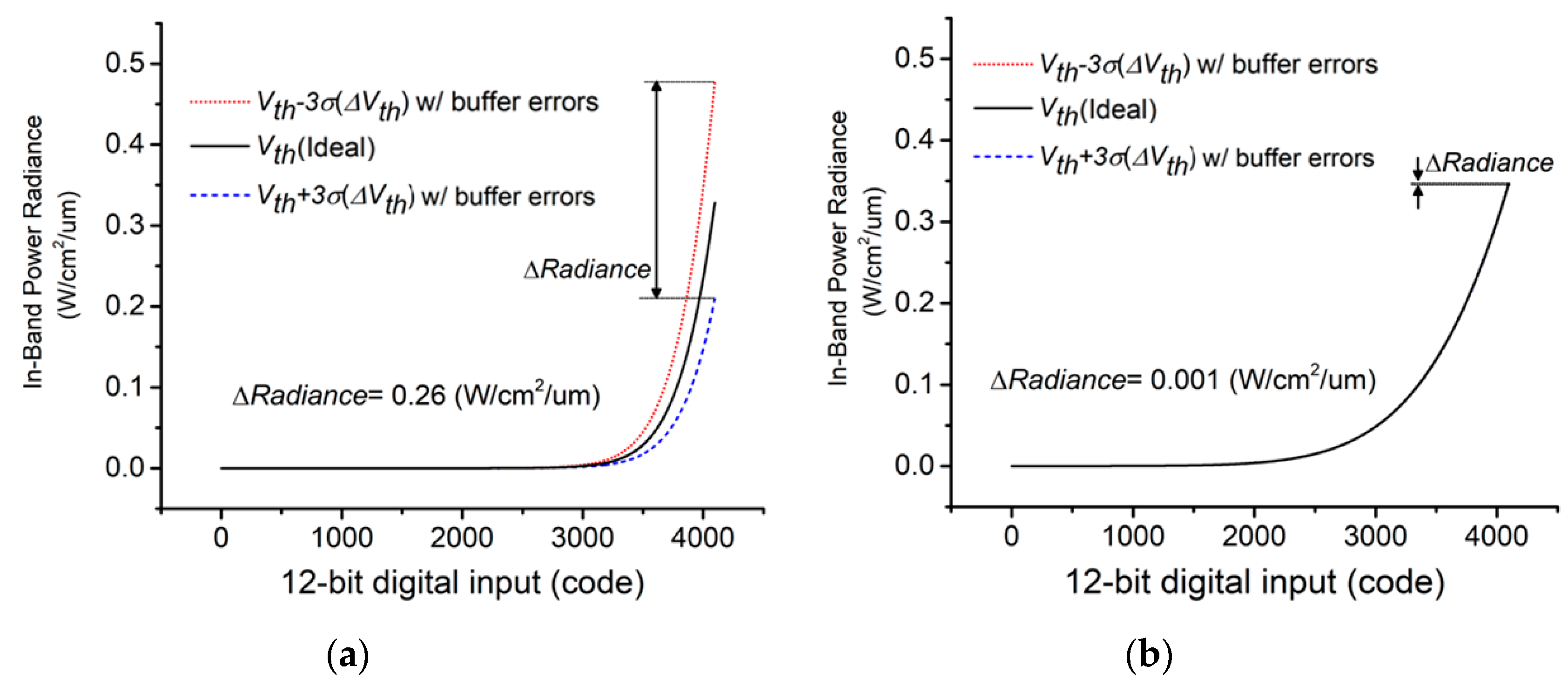

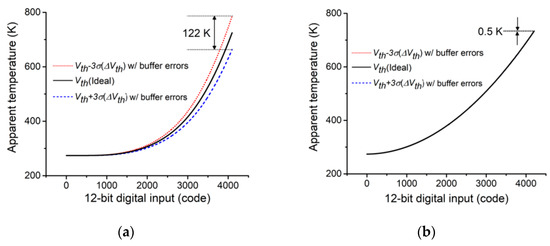

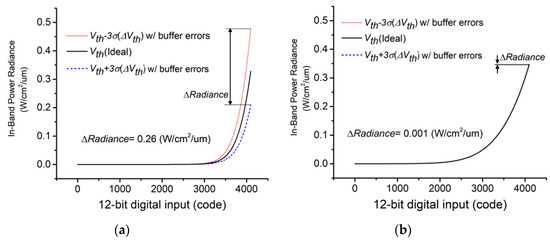

Figure 8 shows a graph of the relationship between digital input and apparent temperature considering the conventional and proposed RIIC, respectively, and Figure 9 shows a graph of the relationship between digital input and in-band power radiance. Comparing Figure 8a,b, the temperature difference between pixels decreases when using the proposed circuit structure. In particular, the maximum temperature difference decreased from 112 to 0.5 K.

Figure 8.

Apparent temperature analysis of IR emitter: (a) conventional RIIC; (b) proposed RIIC.

Figure 9.

Radiance analysis of IR emitter: (a) conventional RIIC; (b) proposed RIIC.

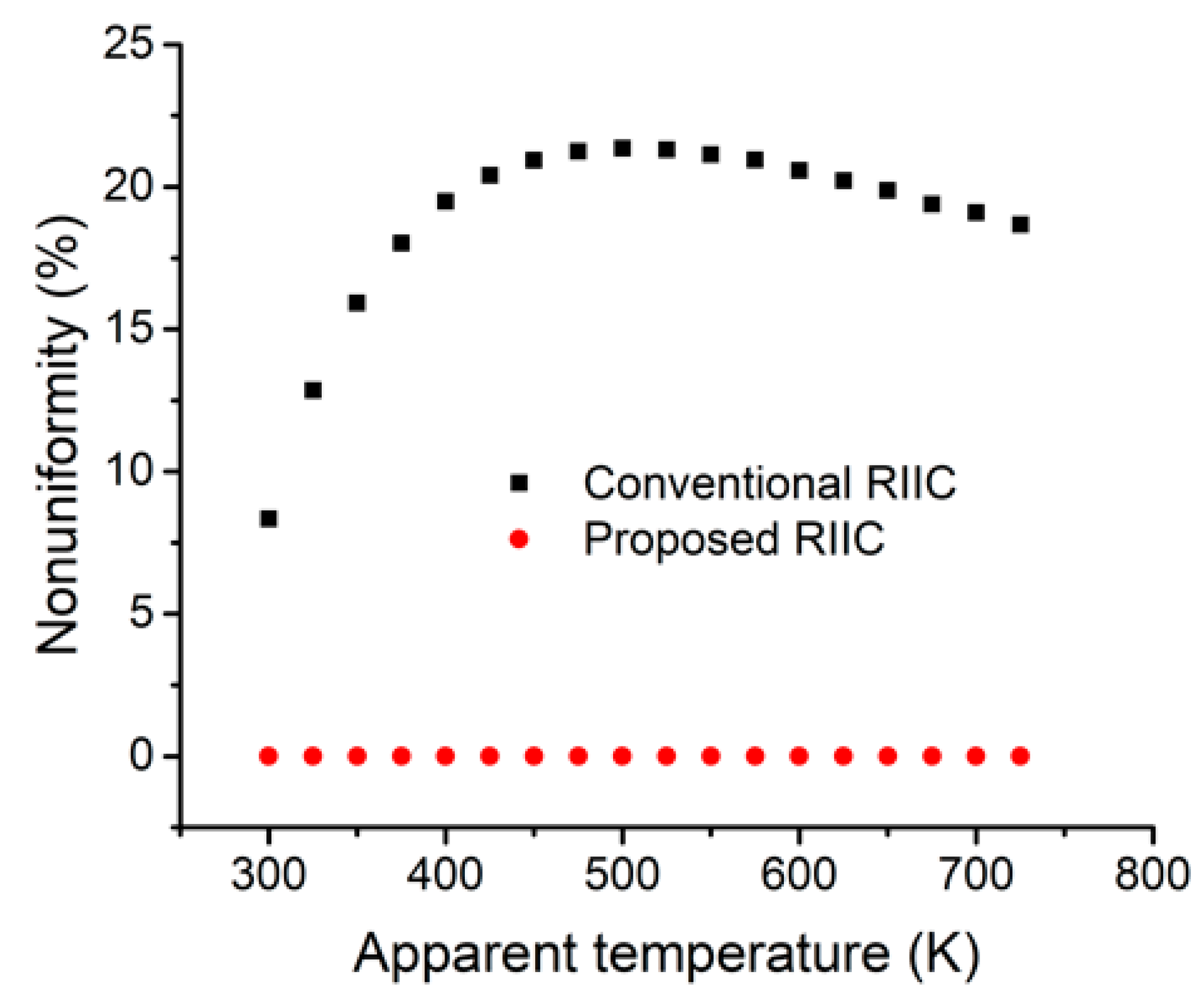

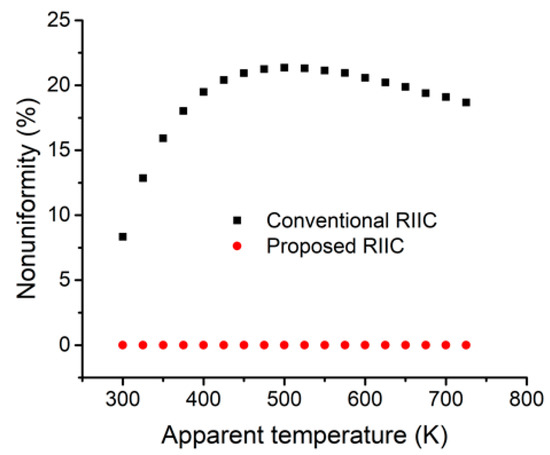

The nonuniformity, which can be calculated with Equation (8) [9], was plotted as a function of the apparent temperature, as shown in Figure 10.

Figure 10.

Nonuniformity comparison of IR emitter driven by the conventional and proposed RIICs.

The highest nonuniformity value for a conventional RIIC was 21%, however, when the proposed structure was used, this quantity became lower than 0.1%. This value, therefore, is sufficiently lower than the target specification listed in Table 1 (<3%), provingthe feasibility of the novel circuit through simulation and data analysis.

If the proposed circuit, however, was applied to a large-sized array, e.g., over 512 × 256 and operating at 200 Hz, accurate data sampling within a pixel-selecting time of nearly 0.04 µs would be needed [20]. As a result, the slow driving speed of the current-programming mechanism from the large line capacitance can prevent the performance of the proposed system [21,22,23,24,25]. In this case, the use of a column digital-to-analog converter (DAC) [26,27,28,29,30], which ensures a pixel-selecting time nearly 510 times longer than that of the single DAC structure, is a suitable solution.

4. Conclusions

We evaluated the operation and performance of a novel nonuniformity-immune RIIC composed of a dual-current-programming structure, which uses dual-functional transistors responsible for data sampling and current driving, to improve the accuracy of nonuniformity corrections. The results obtained from a post-layout simulation and data analyses indicated that the variance of the maximum apparent temperature and radiance nonuniformity were reduced from 122 to 0.5 K and from 21% to less than 0.1%, respectively. Therefore, the proposed RIIC design could be applied to IR sensor testing and evaluation applications with uniform IR scenes.

Author Contributions

D.W. supervised the research. M.C. and H.L. proposed the idea and designed the circuit. M.C. performed the simulation and analysis. M.C. and H.L. wrote the initial manuscript. D.W. revised and finalized the paper. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the Korea government (MSIT), grant number 2020R1F1A1052571.

Acknowledgments

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. 2020R1F1A1052571). This work was supported by the Catholic University of Korea, Research Fund, 2020. The authors are thankful to the IC Design Education Center in Korea for the support of design software.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Franks, G.; Laveigne, J.; Danielson, T.; McHugh, S.; Lannon, J.; Goodwin, S. Development of an ultra-high Temperature infrared scene projector at Santa Barbara Infrared Inc. Proc. SPIE 2015, 9452, 94520W. [Google Scholar]

- Norton, D.T.; LaVeigne, J.; Franks, G.; McHugh, S.; Vengel, T.; Oleson, J.; MacDougal, M.; Westerfeld, D. Development of a high-definition IR LED scene projector. Proc. SPIE 2016, 9820, 98200X. [Google Scholar]

- McHugh, S.; Franks, G.; LaVeigne, J. High-temperature MIRAGE XL (LFRA) IRSP system development. Proc. SPIE 2017, 10178, 1017809. [Google Scholar]

- Sparkman, K.; LaVeigne, J.; McHugh, S.; Lannon, J.; Goodwin, S. Ultrahigh-temperature emitter pixel development for scene projectors. Proc. SPIE 2014, 9071, 90711H. [Google Scholar]

- Cho, M.J.; Woo, D.H.; Lee, H.C. Triple-Mode Read-In Integrated Circuit for Infrared Sensor Evaluation System. IEEE Sens. J. 2019, 19, 5014–5021. [Google Scholar] [CrossRef]

- Bryant, P.; Solomon, S.; James, J. Bolometers running backward: The synergy between uncooled IR sensors and dynamic IR scene projectors. Proc. SPIE 2006, 6207, 62070J. [Google Scholar]

- Stauffer, D.; Haas, B.; Cole, B. Performance of A Thermal Scene Generator. Proc. SPIE 1989, 1050, 156. [Google Scholar]

- LaVeigne, J.; Prewarski, M.; Franks, G.; McHugh, S. A hybrid approach to non-uniformity correction of large format emitter arrays. Proc. SPIE 2012, 8356, 83560D. [Google Scholar]

- Danielson, T.; Franks, G.; LaVeigne, J.; Prewarski, M.; Nehring, B. Advances in iterative non-uniformity correction techniques for infrared scene projection. Proc. SPIE 2015, 9452, 945210. [Google Scholar]

- LaVeigne, J.; Franks, G.; Sparkman, K.; Prewarski, M.; Nehring, B. Enhanced LWIR NUC using an uncooled microbolometer camera. Proc. SPIE 2011, 8015, 801508. [Google Scholar]

- Oleson, J.; Greer, D. IR emitter non-uniformity correction (NUC): Making sense of the data. Proc. SPIE 2011, 8015, 801502. [Google Scholar]

- Swierkowski, L.; Joyce, R.A.; Williams, O. Resistor array infrared projector nonuniformity correction: Search for performance improvement IV. Proc. SPIE 2009, 7301, 73010M. [Google Scholar]

- Olson, E.M.; Murrer, R.L. Nonuniformity correction of a resistor array infrared scene projector. Proc. SPIE 1999, 3697, 403. [Google Scholar]

- Joyce, R.A.; Swierkowski, L.; Williams, O.M. Resistor array infrared projector nonuniformity correction: Search for performance improvement. Proc. SPIE 2006, 6208, 62081A. [Google Scholar]

- Cole, B.; Johnson, W. Infrared Scene Projector with Current-Mirror Control Electronics. US Patent 6,627,907, 30 September 2003. [Google Scholar]

- Shin, U.S.; Cho, M.J.; Lee, H.C. Mismatch-tolerant read-in IC with voltage-drop compensation for infrared scene projectors. IEICE Electron. Express 2018, 15, 1–8. [Google Scholar] [CrossRef]

- James, J.B.; Oleson, J.; Bryant, P.T.; Sparkman, K.; Irwin, A.; McHugh, S.W.; Solomon, S.L. MIRAGE: Developments in emitter array fabrication and performance. Proc. SPIE 2002, 4717, 91. [Google Scholar]

- LaVeigne, J.D.; Kiamilev, F.; McGee, R.; Waite, N. Extended Dynamic Range Drive Circuit for Emitter Arrays. US Patent 9,078,333, 7 July 2015. [Google Scholar]

- Parrish, W.J.; Aziz, N.Y.; Heath, J.L.; Hoelter, T.R. Constant Power Snapshot Microemitter Array with Integral Digital Interface, Isolated Substrate Current Return, and Linearized Signal Response. US Patent 6,316,777, 13 November 2001. [Google Scholar]

- McHugh, S.W.; Warner, J.A.; Pollack, M.; Irwin, A.; Hoelter, T.R.; Parrish, W.J.; Woolaway, J.T. MIRAGE dynamic IR scene projector overview and status. Proc. SPIE 1999, 3697, 209. [Google Scholar]

- Cole, B.E.; Higashi, B.; Ridley, J.A.; Holmen, J.; Newstrom, K.; Zins, C.; Nguyen, K.; Weeres, S.R.; Johnson, B.R.; Stockbridge, R.G.; et al. Innovations in IR projector arrays. Proc. SPIE 2000, 4027, 350. [Google Scholar]

- Ashtiani, S.J.; Servati, P.; Striakhilev, D.; Nathan, A. A 3-TFT current-programmed pixel circuit for AMOLEDs. IEEE Trans. Electron. Devices 2005, 52, 1514–1518. [Google Scholar] [CrossRef]

- McHugh, S.W.; Robinson, R.M.; Parish, B.; Woolaway, J.T. MIRAGE: Large-format emitter arrays 1024 × 1024 and 1024 × 2048. Proc. SPIE 2000, 4027, 399. [Google Scholar]

- Nathan, A.; Chaji, G.R.; Ashtiani, S.J. Driving schemes for a-Si and LTPS AMOLED displays. J. Disp. Technol. 2005, 1, 267–277. [Google Scholar] [CrossRef]

- Ono, S.; Kobayashi, Y. An accelerative current-programming method for AM-OLED. IEICE Trans. Electron. 2005, E88-C, 264–269. [Google Scholar] [CrossRef]

- Bang, J.S.; Kim, H.S.; Kim, K.D.; Kwon, O.J.; Shin, C.S.; Lee, J.H.; Cho, G.H. A hybrid AMOLED driver IC for real-time TFT nonuniformity compensation. IEEE J. Solid-State Circuits 2016, 51, 966–978. [Google Scholar]

- Lu, C.W.; Huang, L.C. A 10-bit LCD column driver with piecewise linear digital-to-analog converters. IEEE J. Solid-State Circuits 2008, 43, 371–378. [Google Scholar] [CrossRef]

- Kim, H.; Yang, J.; Park, S.; Ryu, S.; Cho, G. A 10-Bit Column-Driver IC With Parasitic-Insensitive Iterative Charge-Sharing Based Capacitor-String Interpolation for Mobile Active-Matrix LCDs. IEEE J. Solid-State Circuits 2014, 49, 766–782. [Google Scholar] [CrossRef]

- Jeon, Y.J.; Son, Y.S.; Jeon, J.Y.; Lee, G.H.; Lee, H.M.; Jung, S.C.; Cho, G.H. A cascaded-dividing current DAC with fine pitch for high-resolution AMOLED display drivers. Sid Symp. Dig. Tech. Pap. 2007, 1644–1646. [Google Scholar] [CrossRef]

- Lu, C.W.; Lee, P.; Chang, Y.G.; Huang, X.W.; Cheng, J.S.; Tseng, P.Y.; Chou, C.H.; Chen, P.; Chang, T.Y.; Liu, J. A 10-bit 1026-Channel Column Driver IC With Partially Segmented Piecewise Linear Digital-to-Analog Converters for UHD TFT-LCDs with One Billion Color Display. IEEE J. Solid-State Circuits 2019, 54, 2703–2716. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).