Demonstration of AlGaN/GaN MISHEMT on Si with Low-Temperature Epitaxy Grown AlN Dielectric Gate

Abstract

:1. Introduction

2. Materials and Methods

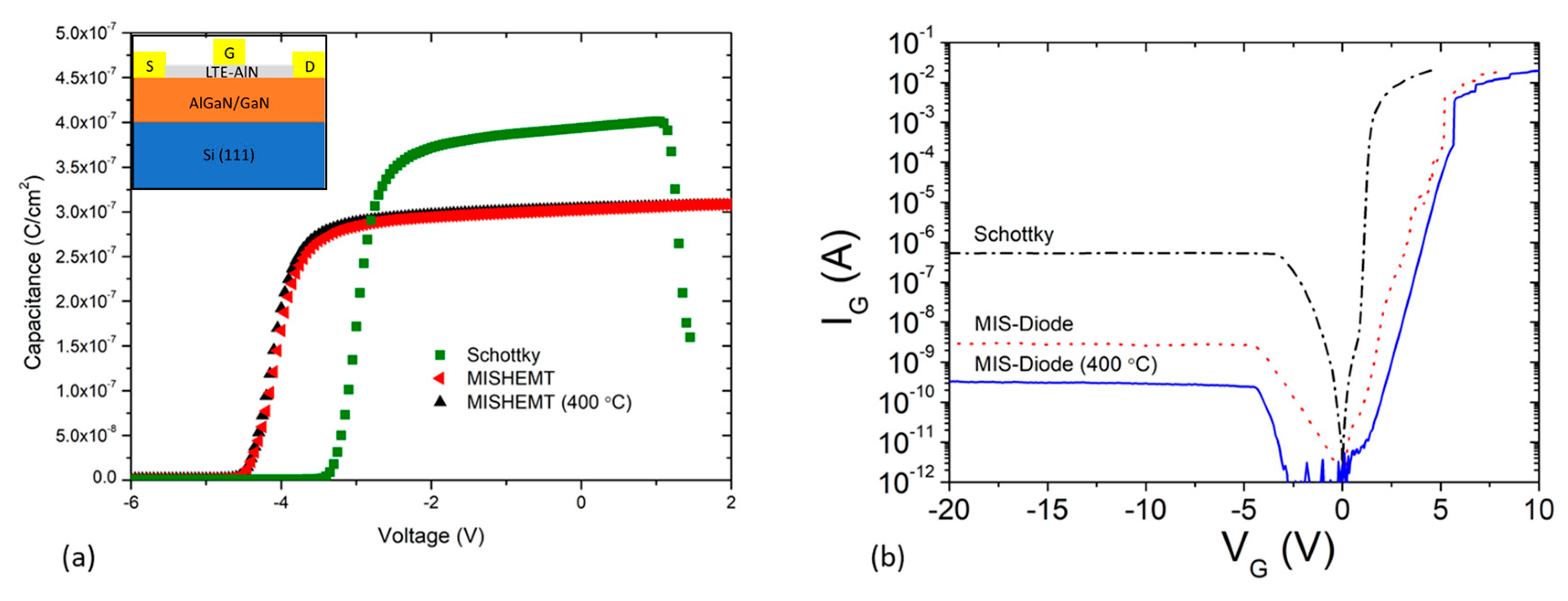

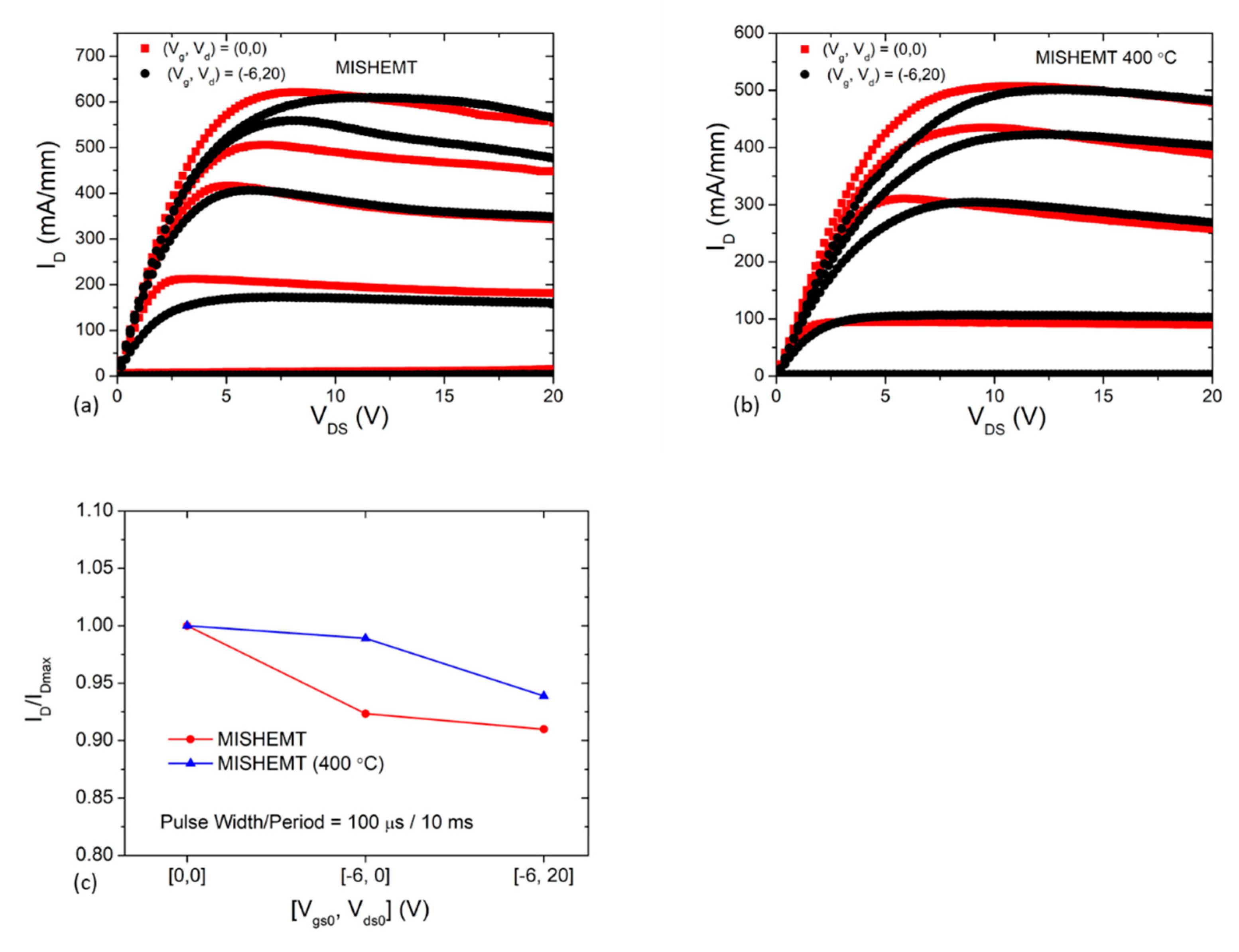

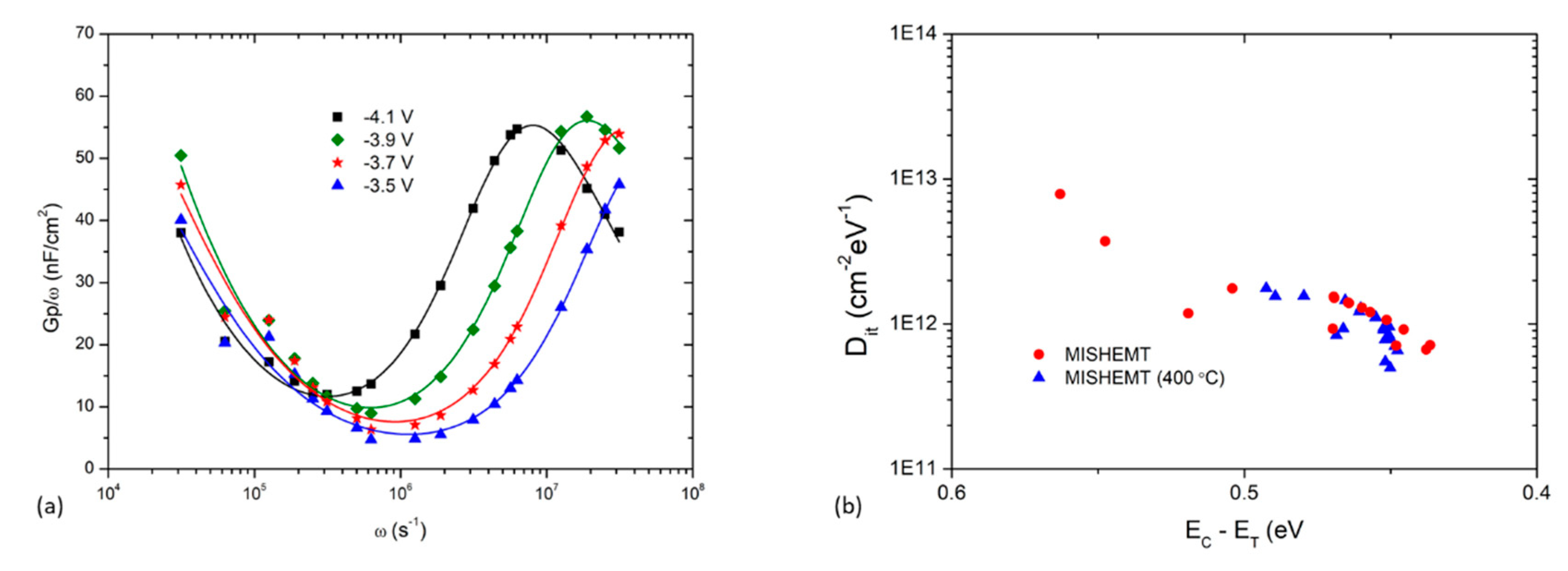

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kumar, V.; Lu, W.; Schwindt, R.; Kuliev, A.; Simin, G.; Yang, J.; Khan, M.A.; Adesida, I. AlGaN/GaN HEMTs on SiC with fT of over 120 GHz. IEEE Electron Device Lett. 2002, 23, 455–457. [Google Scholar] [CrossRef]

- Simin, G.; Hu, X.; Ilinskaya, N.; Kumar, A.; Koudymov, A.; Zhang, J.; Asif Khan, M.; Gaska, R.; Shur, M.S. 7.5kW/mm2 current switch using AlGaN/GaN metal-oxide-semiconductor heterostructure field effect transistors on SiC substrates. Electron. Lett. 2000, 36, 2043–2044. [Google Scholar] [CrossRef] [Green Version]

- Adivarahan, V.; Gaevski, M.; Sun, W.H.; Fatima, H.; Koudymov, A.; Saygi, S.; Simin, G.; Yang, J.; Khan, M.A.; Tarakji, A.; et al. Submicron Gate. IEEE Electron Device Lett. 2003, 24, 541–543. [Google Scholar] [CrossRef]

- Kordoš, P.; Heidelberger, G.; Bernát, J.; Fox, A.; Marso, M.; Lüth, H. High-power SiO2/AlGaN/GaN metal-oxide-semiconductor heterostructure field-effect transistors. Appl. Phys. Lett. 2005, 87, 143501. [Google Scholar] [CrossRef] [Green Version]

- Mizuno, S.; Ohno, Y.; Kishimoto, S.; Maezawa, K.; Mizutani, T. Large gate leakage current in AlGaN/GaN high electron mobility transistors. Jpn. J. Appl. Phys. Part 1 Regul. Pap. Short Notes Rev. Pap. 2002, 41, 5125–5126. [Google Scholar] [CrossRef]

- Kim, K.W.; Jung, S.D.; Kim, D.S.; Im, K.S.; Kang, H.S.; Lee, J.H.; Bae, Y.; Kwon, D.H.; Cristoloveanu, S. Charge trapping and interface characteristics in normally-off Al2O3/GaN-MOSFETs. Microelectron. Eng. 2011, 88, 1225–1227. [Google Scholar] [CrossRef]

- Liu, Z.H.; Ng, G.I.; Arulkumaran, S.; Maung, Y.K.T.; Teo, K.L.; Foo, S.C.; Sahmuganathan, V.; Xu, T.; Lee, C.H. High microwave-noise performance of AlGaN/GaN MISHEMTs on silicon with Al2O3 Gate Insulator Grown by ALD. IEEE Electron Device Lett. 2010, 31, 96–98. [Google Scholar] [CrossRef]

- Shih, C.F.; Hung, K.T.; Hsiao, C.Y.; Shu, S.C.; Li, W.M. Investigations of GaN metal-oxide-semiconductor capacitors with sputtered HfO2 gate dielectrics. J. Alloys Compd. 2009, 480, 541–546. [Google Scholar] [CrossRef]

- Ye, G.; Wang, H.; Arulkumaran, S.; Ng, G.I.; Hofstetter, R.; Li, Y.; Anand, M.J.; Ang, K.S.; Maung, Y.K.T.; Foo, S.C. Atomic layer deposition of ZrO2 as gate dielectrics for AlGaN/GaN metal-insulator-semiconductor high electron mobility transistors on silicon. Appl. Phys. Lett. 2013, 103, 142109. [Google Scholar] [CrossRef]

- Shih, H.A.; Kudo, M.; Suzuki, T.K. Analysis of AlN/AlGaN/GaN metal-insulator-semiconductor structure by using capacitance-frequency-temperature mapping. Appl. Phys. Lett. 2012, 101, 043501. [Google Scholar] [CrossRef]

- Kudo, M.; Shih, H.-A.; Akabori, M.; Suzuki, T. Fabrication and analysis of AlN/GaAs(001) and AlN/Ge/GaAs(001) metal–insulator–semiconductor structures. Jpn. J. Appl. Phys. 2012, 51, 02BF07. [Google Scholar] [CrossRef]

- Tsurumi, N.; Ueno, H.; Murata, T.; Ishida, H.; Uemoto, Y.; Ueda, T.; Inoue, K.; Tanaka, T. AlN passivation over AlGaN/GaN HFETs for surface heat spreading. IEEE Trans. Electron Devices 2010, 57, 980–985. [Google Scholar] [CrossRef]

- Huang, S.; Jiang, Q.; Yang, S.; Zhou, C.; Chen, K.J. Effective passivation of AlGaN/GaN HEMTs by ALD-grown AlN thin film. IEEE Electron Device Lett. 2012, 33, 516–518. [Google Scholar] [CrossRef]

- Freedsman, J.J.; Kubo, T.; Egawa, T. Effect of AlN growth temperature on trap densities of in-situ metal-organic chemical vapor deposition grown AlN/AlGaN/GaN metal-insulator-semiconductor heterostructure field-effect transistors. AIP Adv. 2012, 2, 022134. [Google Scholar] [CrossRef]

- Zhu, J.J.; Ma, X.H.; Xie, Y.; Hou, B.; Chen, W.W.; Zhang, J.C.; Hao, Y. Improved interface and transport properties of AlGaN/GaN MIS-HEMTs with peald-grown AlN gate dielectric. IEEE Trans. Electron Devices 2015, 62, 512–518. [Google Scholar] [CrossRef]

- Huang, S.; Jiang, Q.; Yang, S.; Tang, Z.; Chen, K.J. Mechanism of PEALD-Grown AlN passivation for AlGaN/GaN HEMTs: Compensation of interface traps by polarization charges. IEEE Electron Device Lett. 2013, 34, 193–195. [Google Scholar] [CrossRef]

- Hashizume, T.; Alekseev, E.; Pavlidis, D.; Boutros, K.S.; Redwing, J. Capacitance–voltage characterization of AlN/GaN metal–insulator–semiconductor structures grown on sapphire substrate by metalorganic chemical vapor deposition. J. Appl. Phys. 2000, 88, 1983–1986. [Google Scholar] [CrossRef] [Green Version]

- Imanaga, S.; Nakamura, F.; Kawai, H. Current–voltage characteristics of AlN/GaN heterostructure metal insulator semiconductor diode. Jpn. J. Appl. Phys. 2001, 40, 1194–1198. [Google Scholar] [CrossRef]

- Cao, D.; Cheng, X.; Xie, Y.H.; Zheng, L.; Wang, Z.; Yu, X.; Wang, J.; Shen, D.; Yu, Y. Effects of rapid thermal annealing on the properties of AlN films deposited by PEALD on AlGaN/GaN heterostructures. RSC Adv. 2015, 5, 37881–37886. [Google Scholar] [CrossRef] [Green Version]

- Sinhoff, V.; Diikme, Y. Low Temperature Epitaxy (LTE)—A novel approach for the volume production of GaN based devices. In Proceedings of the International Conference and Exhibition of the APE Automotive Power Electronics, Paris, France, 26–27 April 2017; Volume 1. [Google Scholar]

- Whiteside, M.; Ng, G.I.; Arulkumaran, S.; Ranjan, K.; Dikme, Y. Low temperature epitaxy grown AlN metal-insulator-semiconductor diodes on AlGaN/GaN HEMT structure. In Proceedings of the 2019 Electron Devices Technology and Manufacturing Conference (EDTM), Singapore, 12–15 March 2019; IEEE: New York, NY, USA, 2019; pp. 103–105. [Google Scholar]

- Whiteside, M.; Arulkumaran, S.; Dikme, Y.; Sandupatla, A.; Ng, G.I. Improved interface state density by low temperature epitaxy grown AlN for AlGaN/GaN metal-insulator-semiconductor diodes. Mater. Sci. Eng. B Solid-State Mater. Adv. Technol. 2020, 262, 114707. [Google Scholar] [CrossRef]

- Arulkumaran, S.; Egawa, T.; Ishikawa, H.; Umeno, M.; Jimbo, T. Effects of annealing on Ti, Pd, and Ni/n-Al0.11Ga0.89N Schottky diodes. IEEE Trans. Electron Devices 2001, 48, 573–580. [Google Scholar] [CrossRef]

- Fang, L.; Tao, W.; Bo, S.; Sen, H.; Fang, L.; Nan, M.; Fu-Jun, X.; Peng, W.; Jian-Quan, Y. Thermal annealing behaviour of Al/Ni/Au multilayer on n-GaN schottky contacts. Chin. Phys. B 2009, 18, 1618–1621. [Google Scholar] [CrossRef]

- Zhou, H.; Ng, G.I.; Liu, Z.H.; Arulkumaran, S. Improved device performance by post-oxide annealing in atomic-layer-deposited Al2O3/AlGaN/GaN metal–insulator–semiconductor high electron mobility transistor on Si. Appl. Phys. Express 2011, 4, 104102. [Google Scholar] [CrossRef]

- Liu, Z.H.; Ng, G.I.; Arulkumaran, S.; Maung, Y.K.T.; Teo, K.L.; Foo, S.C.; Sahmuganathan, V. Improved two-dimensional electron gas transport characteristics in AlGaN/GaN metal-insulator-semiconductor high electron mobility transistor with atomic layer-deposited Al2O3 as gate insulator. Appl. Phys. Lett. 2009, 95, 223501. [Google Scholar] [CrossRef]

- Liu, X.-Y.; Zhao, S.-X.; Zhang, L.-Q.; Huang, H.-F.; Shi, J.-S.; Zhang, C.-M.; Lu, H.-L.; Wang, P.-F.; Zhang, D.W. AlGaN/GaN MISHEMTs with AlN gate dielectric grown by thermal ALD technique. Nanoscale Res. Lett. 2015, 10, 109. [Google Scholar] [CrossRef] [Green Version]

- Hwang, Y.-H.; Liu, L.; Velez, C.; Ren, F.; Gila, B.P.; Hays, D.; Pearton, S.J.; Lambers, E.; Kravchenko, I.I.; Lo, C.-F.; et al. GaN metal–insulator–semiconductor high-electron-mobility transistor with plasma enhanced atomic layer deposited AlN as gate dielectric and passivation. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2013, 31, 052201. [Google Scholar] [CrossRef]

- Chen, T.; Jiao, G.; Li, Z.; Li, F.; Shao, K.; Yang, N. AlGaN/GaN MIS HEMT with AlN dielectric. In Proceedings of the 2006 International Conference on Compound Semiconductor Manufacturing Technology CS MANTECH Conference, Vancouver, BC, Canada, 24–27 April 2006; pp. 227–230. [Google Scholar]

- Kordoš, P.; Stoklas, R.; Gregušová, D.; Gaži, Š.; Novák, J. Trapping effects in Al2O3/AlGaN/GaN metal-oxide-semiconductor heterostructure field-effect transistor investigated by temperature dependent conductance measurements. Appl. Phys. Lett. 2010, 96, 013505. [Google Scholar] [CrossRef]

- Quan, S.; Hao, Y.; Ma, X.-H.; Yu, H.-Y. Investigation of AlGaN/GaN fluorine plasma treatment enhancement-mode high electronic mobility transistors by frequency-dependent capacitance and conductance analysis. Chin. Phys. B 2011, 20, 018101. [Google Scholar] [CrossRef]

- Ranjan, K.; Arulkumaran, S.; Ng, G.I. Investigations of temperature-dependent interface traps in AlGaN/GaN HEMT on CVD-diamond. Appl. Phys. Express 2019, 12, 106506. [Google Scholar] [CrossRef]

| 2DEG Parameters | AlGaN/GaN HEMT Structure | |||

|---|---|---|---|---|

| Without LTE-AlN [22] | With LTE-AlN | |||

| As-dep. [22] | Annealing Temperature °C | |||

| 400 | 450 | |||

| Sheet Resistance (Ω/□) | 591 | 523 | 520 | 512 |

| Hall Mobility (cm2V−1s−1) | 1440 | 1210 | 1330 | 1360 |

| Sheet Carrier Concentration (×1012 cm−2) | 7.35 | 9.89 | 9.02 | 8.76 |

| Reference | Thickness (nm) | Substrate | Deposition Method | Device Dimensions Lg/Wg (µm) | Idmax (mA/mm) | gmmax (mS/mm) | On/Off Ratio (Orders of Magnitude) |

|---|---|---|---|---|---|---|---|

| [15] | 10.6 | Si | ALD | 2.5/60 | 563 @ 5V | 87 | ~5 |

| [27] | 10 | Sapphire | ALD | 1/200 | 600 @ 4V | 127 | ~9 |

| [28] | 20 | Sapphire | PEALD | 0.5/50 | ~1050 @ 2 V | 289 | ~3 |

| [29] | 8 | SiC | Reactive Sputtering | 0.4/200 | ~1250 @ 2 V | 260 | ~3 |

| This work | 8 | Si | LTE | 2/(2 × 100) | 684 @ 4V | 148 | ~8 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Whiteside, M.; Arulkumaran, S.; Dikme, Y.; Sandupatla, A.; Ng, G.I. Demonstration of AlGaN/GaN MISHEMT on Si with Low-Temperature Epitaxy Grown AlN Dielectric Gate. Electronics 2020, 9, 1858. https://doi.org/10.3390/electronics9111858

Whiteside M, Arulkumaran S, Dikme Y, Sandupatla A, Ng GI. Demonstration of AlGaN/GaN MISHEMT on Si with Low-Temperature Epitaxy Grown AlN Dielectric Gate. Electronics. 2020; 9(11):1858. https://doi.org/10.3390/electronics9111858

Chicago/Turabian StyleWhiteside, Matthew, Subramaniam Arulkumaran, Yilmaz Dikme, Abhinay Sandupatla, and Geok Ing Ng. 2020. "Demonstration of AlGaN/GaN MISHEMT on Si with Low-Temperature Epitaxy Grown AlN Dielectric Gate" Electronics 9, no. 11: 1858. https://doi.org/10.3390/electronics9111858

APA StyleWhiteside, M., Arulkumaran, S., Dikme, Y., Sandupatla, A., & Ng, G. I. (2020). Demonstration of AlGaN/GaN MISHEMT on Si with Low-Temperature Epitaxy Grown AlN Dielectric Gate. Electronics, 9(11), 1858. https://doi.org/10.3390/electronics9111858