A 28 GHz Linear Power Amplifier Based on CPW Matching Networks with Series-Connected DC-Blocking Capacitors

Abstract

:1. Introduction

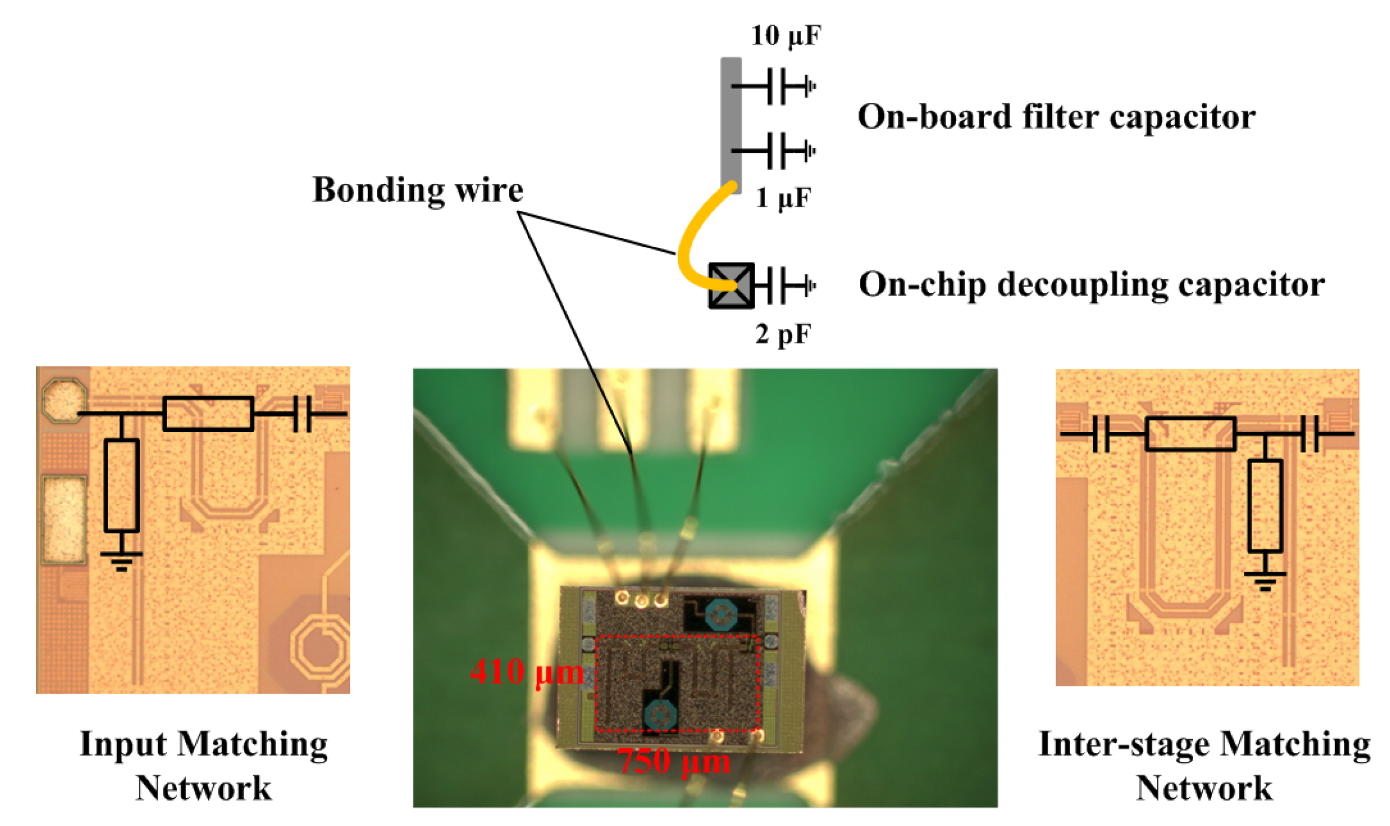

2. Design of the Linear PA

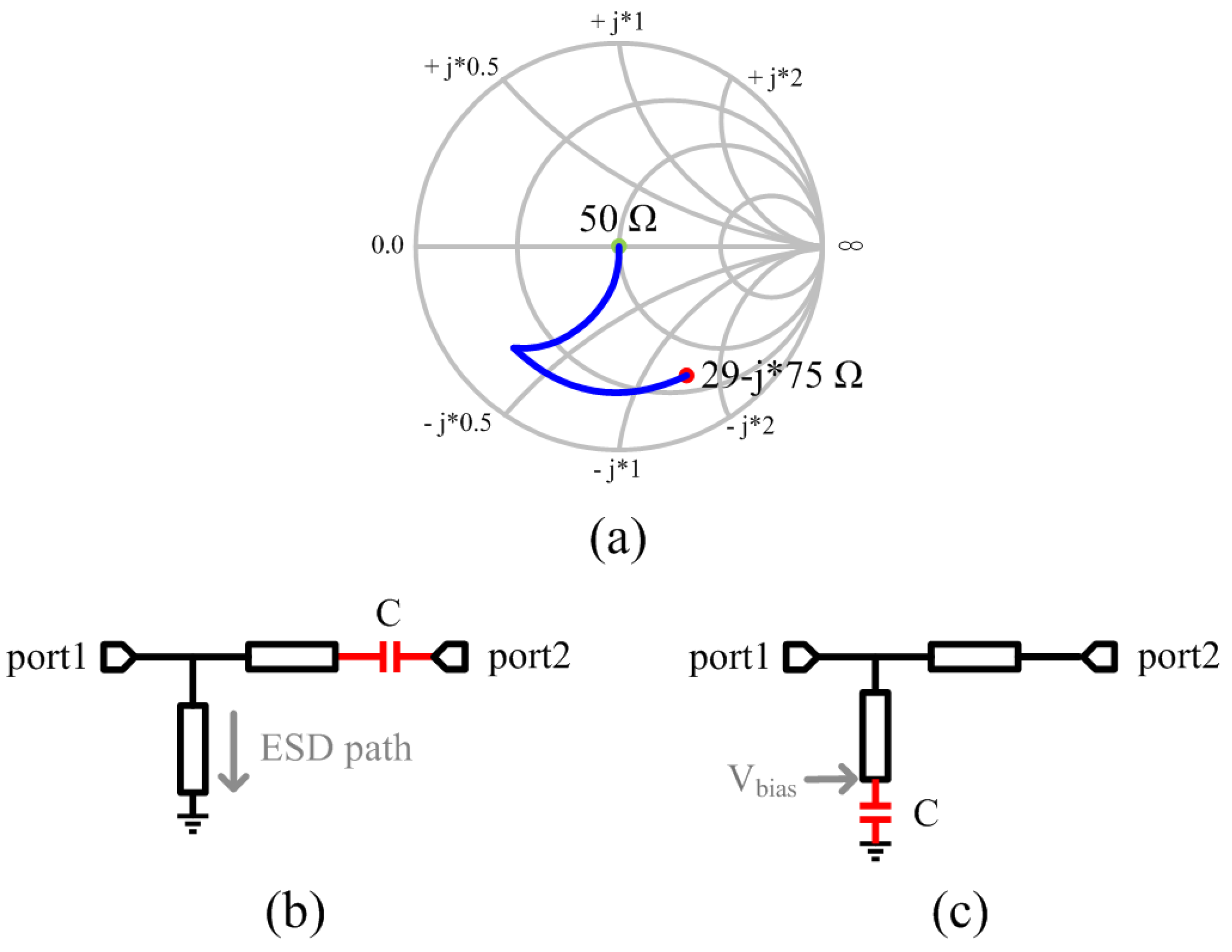

2.1. CPW Matching Networks with DC-Blocking Capacitors

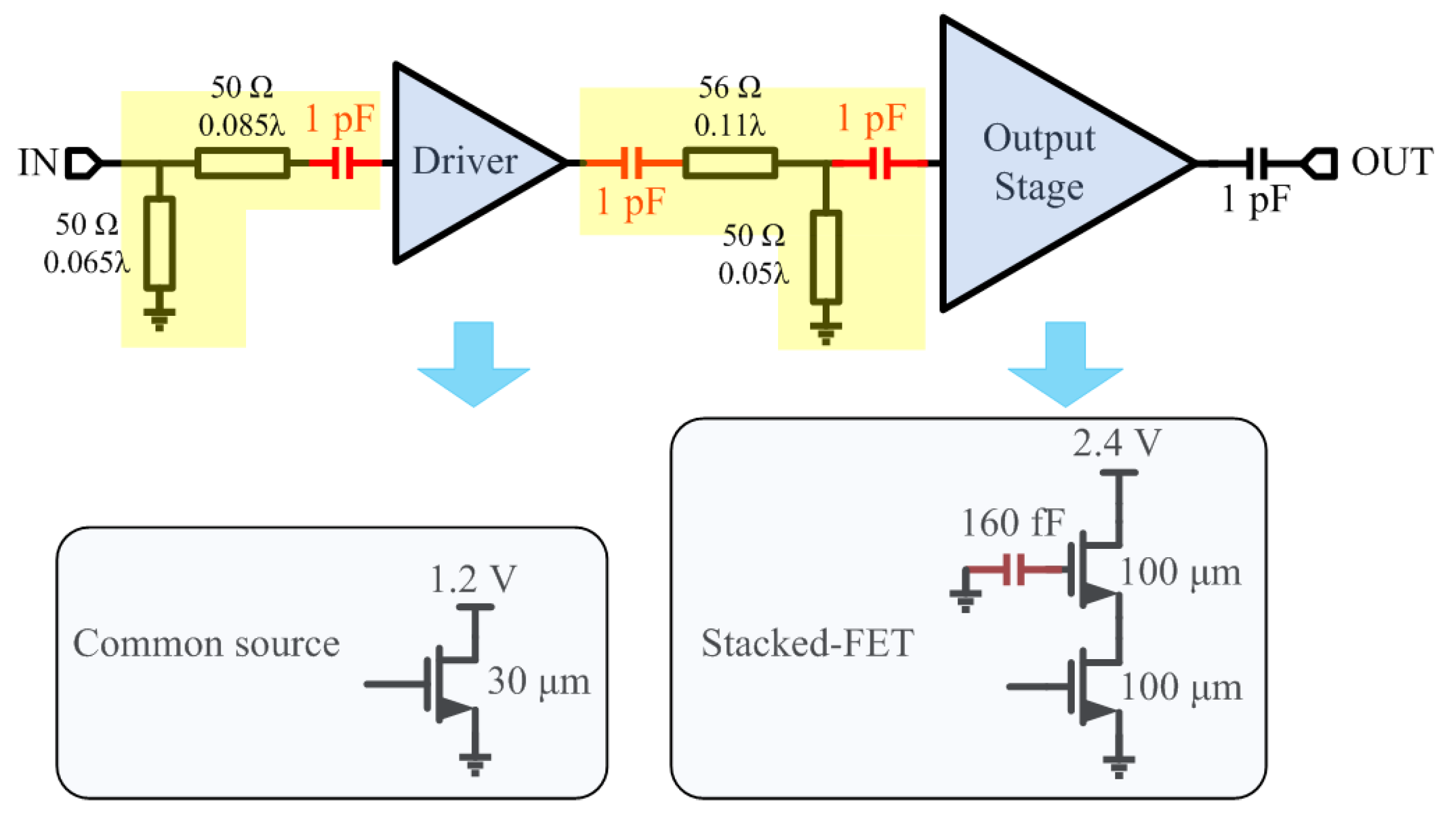

2.2. Single-End Linear PA

3. Measurements and Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kim, H.T.; Park, B.S.; Song, S.S.; Moon, T.S.; Kim, S.H.; Kim, J.M.; Chang, J.Y.; Ho, Y.C. A 28-GHz CMOS direct conversion transceiver with packaged 2 × 4 antenna array for 5G cellular system. IEEE J. Solid-State Circuits 2018, 53, 1245–1259. [Google Scholar] [CrossRef]

- Kibaroglu, K.; Sayginer, M.; Phelps, T.; Rebeiz, G.M. A 64-element 28-GHz phased-array transceiver with 52-dBm EIRP and 8-12-Gb/s 5G link at 300 meters without any calibration. IEEE Trans. Microw. Theory Tech. 2018, 66, 5796–5811. [Google Scholar] [CrossRef]

- Pang, J.; Wu, R.; Wang, Y.; Dome, M.; Kato, H.; Huang, H.; Narayanan, A.T.; Liu, H.; Liu, B.; Nakamura, T.; et al. A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio. IEEE J. Solid-State Circuits 2019, 54, 1228–1242. [Google Scholar] [CrossRef]

- Enabling Mobile Augmented and Virtual Reality with 5G Networks. Available online: http://about.att.com/innovationblog/foundry_ar_vr (accessed on 27 February 2017).

- Hu, S.; Wang, F.; Wang, H. A 28-/37-/39-GHz linear Doherty power amplifier in silicon for 5G applications. IEEE J. Solid-State Circuits 2019, 54, 1586–1599. [Google Scholar] [CrossRef]

- Shakib, S.; Park, H.C.; Dunworth, J.; Aparin, V.; Entesari, K. A highly efficient and linear power amplifier for 28-GHz 5G phased array radios in 28-nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 3020–3036. [Google Scholar] [CrossRef]

- Nikandish, G.; Staszewski, R.B.; Zhu, A. Breaking the bandwidth limit: A review of broadband Doherty power amplifier design for 5G. IEEE Microw. Mag. 2020, 21, 57–75. [Google Scholar] [CrossRef] [Green Version]

- Chou, C.F.; Wu, C.W.; Hsiao, Y.H.; Wu, Y.C.; Lin, Y.H.; Wang, H. A 60-GHz 20.6-dBm Symmetric Radial Combining Wideband Power Amplifier with 20.3% Peak PAE and 20-dB Gain in 90-nm CMOS. In Proceedings of the 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 22–27 May 2016. [Google Scholar]

- Huang, W.C.; Lin, J.L.; Lin, Y.H.; Wang, H. A K-band Power Amplifier with 26-dBm Output Power and 34% PAE with Novel Inductance-based Neutralization in 90-nm CMOS. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 228–231. [Google Scholar]

- Helmi, S.R.; Chen, J.H.; Mohammadi, S. High-efficiency microwave and mm-Wave stacked cell CMOS SOI power amplifiers. IEEE Trans. Microw. Theory Tech. 2016, 64, 2025–2038. [Google Scholar] [CrossRef]

- Fang, K.; Buckwalter, J.F. Efficient linear millimetre-wave distributed transceivers in CMOS SOI. IEEE Trans. Microw. Theory Tech. 2019, 67, 295–307. [Google Scholar] [CrossRef]

- Cheung, T.S.; Long, J.R.; Vaed, K.; Volant, R.; Chinthakindi, A.; Schnabel, C.M.; Florkey, J.; Stein, K. On-chip interconnect for mm-Wave applications using all-copper technology and wavelength reduction. ISSCC Dig. Tech. Papers 2003. [CrossRef]

- Komijani, A.; Natarajan, A.; Hajimiri, A. A 24-GHz, +14.5-dBm fully integrated power amplifier in 0.18-μm CMOS. IEEE J. Solid-State Circuits 2005, 40, 1901–1908. [Google Scholar]

- Siligaris, A.; Mounet, C.; Reig, B.; Vincent, P. CPW discontinuities modelling for circuit design up to 110 GHz in SOI CMOS technology. In Proceedings of the 2007 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Honolulu, HI, USA, 3–5 June 2007; pp. 295–298. [Google Scholar]

- Haroun, I.; Wight, J.; Plett, C.; Fathy, A.; Hsu, Y.C. A V-band 90-nm CMOS low-noise amplifier with modified CPW transmission lines for UWB systems. In Proceedings of the Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, New Orleans, LA, USA, 11–13 January 2010; pp. 160–163. [Google Scholar]

- Lee, S.Y.; Cheng, P.H.; Tsou, C.F.; Lin, C.C.; Shieh, G.S. A 2.4 GHz ISM band OOK transceiver with high energy efficiency for biomedical implantable applications. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 113–124. [Google Scholar] [CrossRef] [PubMed]

- Choe, Y.J.; Nam, H.; Park, J.D. A compact 5 GHz power amplifier using a spiral transformer for enhanced power supply rejection in 180-nm CMOS technology. Electronics 2019, 8, 1043. [Google Scholar] [CrossRef] [Green Version]

- Shu, R.; Subramanian, V.; Hamidian, A.; Malignaggi, A.; Boeck, G. Characterization of LC-tank circuits for mm-Wave applications in 90 nm CMOS. In Proceedings of the 2011 Semiconductor Conference Dresden, Dresden, Germany, 27–28 September 2011. [Google Scholar]

- Korndorfer, F.; Muhlhaus, V. Lumped modelling of integrated MIM capacitors for RF applications. In Proceedings of the 2016 88th ARFTG Microwave Measurement Conference (ARFTG), Austin, TX, USA, 8–9 December 2016. [Google Scholar]

- Beeresha, R.S.; Khan, A.M.; Manjunath Reddy, H.V. Design and EM-simulation of MIM capacitor. In Proceedings of the 2017 International Conference on Energy, Communication, Data Analytics and Soft Computing (ICECDS), Chennai, India, 1–2 August 2017; pp. 1644–1649. [Google Scholar]

- Rohani, N.; Zhang, J.; Lee, J.; Bai, J. A 28-nm CMOS 76-81-GHz power amplifier for automotive radar applications. In Proceedings of the 2017 IEEE 17th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Phoenix, AZ, USA, 15–18 January 2017; pp. 85–87. [Google Scholar]

- Dabag, H.T.; Hanafi, B.; Golcuk, F.; Agah, A.; Buckwalter, J.F.; Asbeck, P.M. Analysis and design of stacked-FET millimeter-wave power amplifiers. IEEE Trans. Microw. Theory Tech. 2013, 61, 1543–1556. [Google Scholar] [CrossRef]

| This Work | JSSC’ 19 [5] | JSSC’ 16 [6] | RFIC’ 18 [9] | JSSC’ 05 [13] | |

|---|---|---|---|---|---|

| Technology | 90 nm SOI CMOS | 130 nm SiGe | 28 nm CMOS | 90 nm CMOS | 0.18 μm CMOS |

| Matching network | CPW line | Transformer & capacitor | Transformer & capacitor | Transformer & capacitor | Slow-wave CPW line |

| Gain (dB) | 13.7 | 18.2 | 15.7 | 16.3 | 7 |

| −3 dB BW (GHz) | 6.3 | 16.4 | 3.85 | - | 3.1 |

| Psat (dBm) | 14.4 | 16.8 | 14 | 26 | 14.5 |

| Peak PAE (%) | 25 | 20.3 | 35.5 | 34.1 | 6.5 |

| Modulation | 64-QAM 1.5 Gb/s | 64-QAM 6 Gb/s | 64-QAM OFDM 1.5 Gb/s | 256-QAM PRBS15 1.6 Gb/s | - |

| EVM @ 28 GHz, (dBc) | −29.4 dBc @ 9.6 dB PBO | −26.6 dBc @ 9.6 dB PBO | −25 dBc @ 9.6 dB PBO 1 | <−32 dBc 2 | - |

| Area (mm2) | 0.31 | 1.76 | 0.16 | 0.401 3 | 1.26 3 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xia, Q.; Li, D.; Huang, J.; Li, J.; Chang, H.; Sun, B.; Liu, H. A 28 GHz Linear Power Amplifier Based on CPW Matching Networks with Series-Connected DC-Blocking Capacitors. Electronics 2020, 9, 617. https://doi.org/10.3390/electronics9040617

Xia Q, Li D, Huang J, Li J, Chang H, Sun B, Liu H. A 28 GHz Linear Power Amplifier Based on CPW Matching Networks with Series-Connected DC-Blocking Capacitors. Electronics. 2020; 9(4):617. https://doi.org/10.3390/electronics9040617

Chicago/Turabian StyleXia, Qingzhen, Dongze Li, Jiawei Huang, Jinwei Li, Hudong Chang, Bing Sun, and Honggang Liu. 2020. "A 28 GHz Linear Power Amplifier Based on CPW Matching Networks with Series-Connected DC-Blocking Capacitors" Electronics 9, no. 4: 617. https://doi.org/10.3390/electronics9040617

APA StyleXia, Q., Li, D., Huang, J., Li, J., Chang, H., Sun, B., & Liu, H. (2020). A 28 GHz Linear Power Amplifier Based on CPW Matching Networks with Series-Connected DC-Blocking Capacitors. Electronics, 9(4), 617. https://doi.org/10.3390/electronics9040617