Understanding of Polarization-Induced Threshold Voltage Shift in Ferroelectric-Gated Field Effect Transistor for Neuromorphic Applications

Abstract

:1. Introduction

2. Fabrication and Measurement

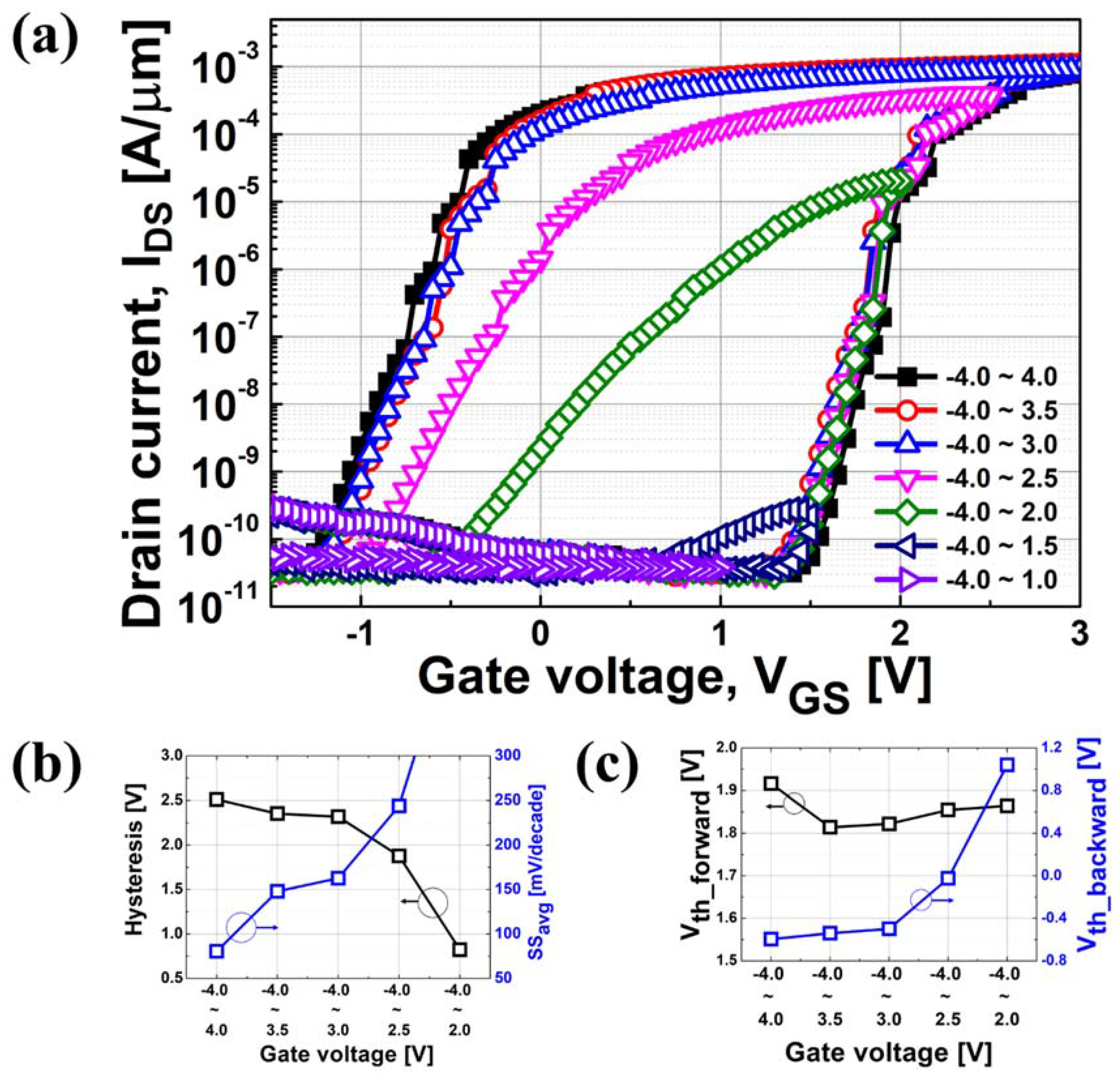

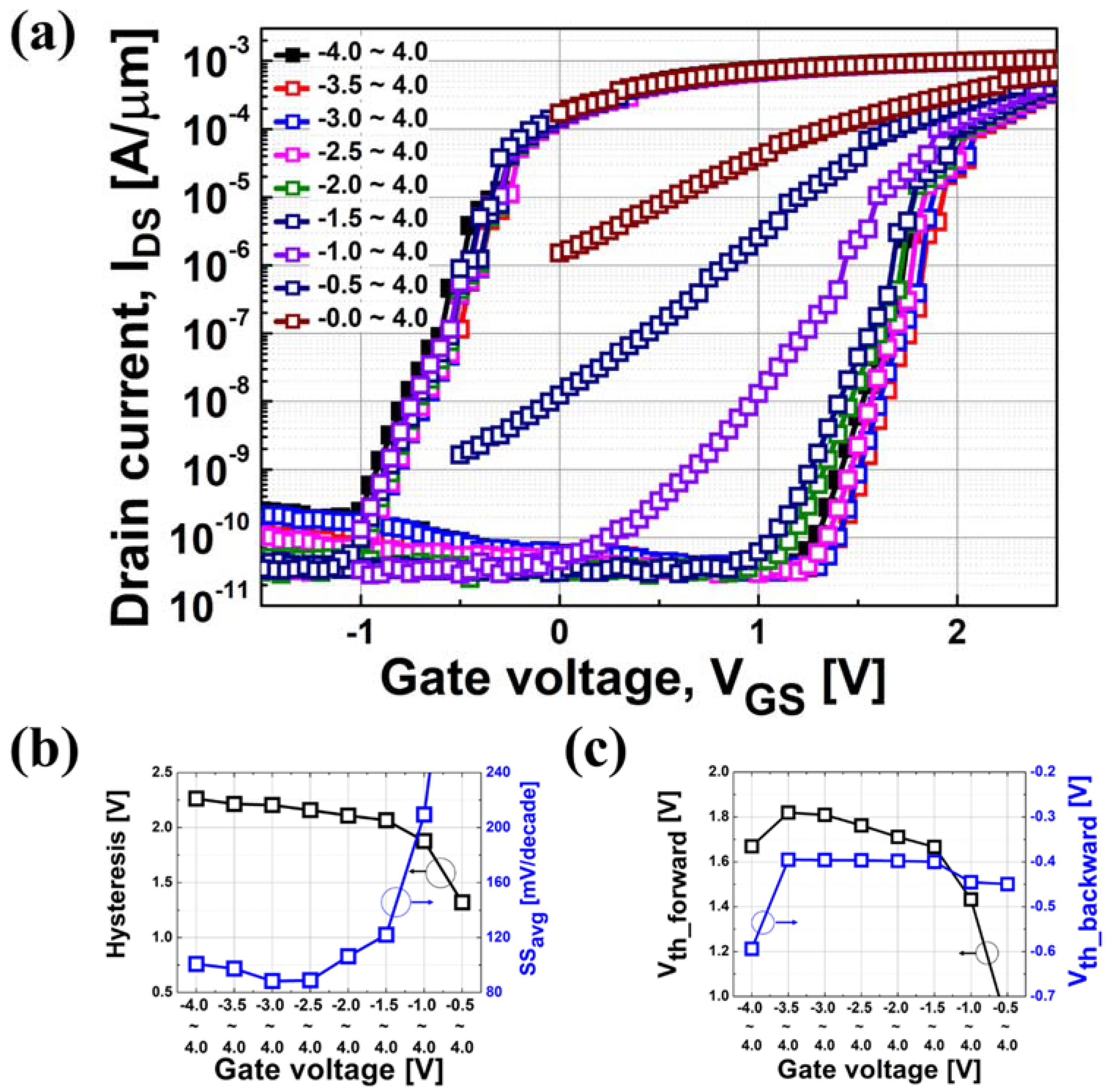

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Choi, W.Y.; Park, B.G.; Lee, J.D.; Liu, T.J.K. Tunneling Field-Effect Transistors (TFETs) With Subthreshold Swing (SS) Less Than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Shin, J.; Ko, E.; Shin, C. Super steep-switching (S ≈ 2 mV/decade) phase-FinFET with Pb(Zr0.52Ti0.48)O3 threshold switching device. Appl. Phys. Lett. 2018, 113, 102–104. [Google Scholar] [CrossRef]

- Shukla, N.; Thathachary, A.V.; Agrawal, A.; Paik, H.; Aziz, A.; Schlom, D.G.; Gupta, S.K.; Engel-Herbert, R.; Datta, S. A steep-slope transistor based on abrupt electronic phase transition. Nat. Commun. 2015, 6, 7812. [Google Scholar] [CrossRef] [Green Version]

- Lee, C.; Ko, E.; Shin, C. Steep slope silicon-on-insulator feedback field-effect transistor: Design and performance analysis. IEEE Trans. Electron Devices 2018, 66, 286–291. [Google Scholar] [CrossRef]

- Kim, M.; Kim, Y.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Steep switching characteristics of single-gated feedback field-effect transistors. Nat. Nanotechnol. 2016, 28, 055205. [Google Scholar] [CrossRef] [PubMed]

- Salahuddin, S.; Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 2008, 8, 405–410. [Google Scholar] [CrossRef] [PubMed]

- Yu, S.; Chen, P.-Y. Emerging memory technologies: Recent trends and prospects. IEEE Solid State Circuits Mag. 2016, 8, 43–56. [Google Scholar] [CrossRef]

- Wong, H.S.P.; Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 2015, 10, 191–194. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Li, Y.; Zhong, Y.; Zhang, J.; Xu, L.; Wang, Q.; Sun, H.; Tong, H.; Cheng, X.; Miao, X. tre-Dependent Synaptic Plasticity of a Chalcogenide Electronic Synapse for Neuromorphic Systems. Sci. Rep. 2014, 4, 4906. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Indiveri, G.; Liu, S.C. Memory and Information Processing in Neuromorphic Systems. Proc. IEEE. 2015, 103, 1379–1397. [Google Scholar] [CrossRef] [Green Version]

- LeCun, Y.; Bengio, Y.; Hinton, G. Deep learning. Nature 2015, 521, 436–444. [Google Scholar] [CrossRef] [PubMed]

- Wang, Z.; Khan, A.I. Ferroelectric Relaxation Oscillators and Spiking Neurons. IEEE J. Explor. Solid State Computat. 2019, 5, 151–157. [Google Scholar] [CrossRef]

- Tan, A.J.; Chatterjee, K.; Zhou, J.; Kwon, D.; Liao, Y.-H.; Cheema, S.; Hu, C.; Salahuddin, S. Experimental Demonstration of a Ferroelectric HfO2-based Content Addressable Memory Cell. IEEE Electron Dev. Lett. 2020, 41, 240–243. [Google Scholar] [CrossRef]

- Bez, R. Chalcogenide PCM: A memory technology for next decade. IEEE IEDM 2009, 5, 1. [Google Scholar]

- Wong, H.-S.P.; Raoux, S.; Kim, S.B.; Liang, J.; Reifenberg, J.P.; Rajendran, B.; Asheghi, M.; Goodson, K.E. Phase Change Memory. Proc. IEEE. 2020, 98, 2201–2227. [Google Scholar] [CrossRef]

- Moon, K.; Kwak, M.; Park, J.; Lee, D.; Hwang, H. Improved conductance linearity and conductance ratio of 1T2R synapse device for neuromorphic systems. IEEE Electron Dev. Lett. 2017, 38, 1023–1026. [Google Scholar] [CrossRef]

- Kund, M.; Beitel, G.; Pinnow, C.-U.; Rohr, T.; Schumann, J.; Symanczyk, R.; Ufert, K.; Muller, G. Conductive bridging RAM (CBRAM): An emerging non-volatile memory technology scalable to sub 20 nm. IEEE IEDM 2005, 754–757. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Ocker, J.; Muller, S.; Noack, M.; Muller, J.; Polakowski, P.; Mikolajick, T.; Slesazeck, S. Novel ferroelectric FET based synapse for neuromorphic systems. Symp. VLLSI Tech. Dig. 2017, T176–T177. [Google Scholar] [CrossRef]

- Ishiwara, H. Proposal of Adaptive Neuron Circuits with Ferroelectric Analog-Memory Weights. Jpn. J. Appl. Phys. 1993, 32, 442–446. [Google Scholar] [CrossRef]

- Jo, J.; Choi, W.Y.; Park, J.-D.; Shim, J.W.; Yu, H.-Y.; Shin, C. Negative capacitance in organic/ferroelectric capacitor to implement steep switching MOS devices. Nano Lett. 2015, 15, 4553–4556. [Google Scholar] [CrossRef]

- Ko, E.; Lee, J.W.; Shin, C. Negative Capacitance FinFET with Sub-20-mV/decade Subthreshold Slope and Minimal Hysteresis of 0.48 V. IEEE Electron Device Lett. 2017, 38, 418–421. [Google Scholar] [CrossRef]

- Nishitani, Y.; Kaneko, Y.; Ueda, M.; Fujii, E. Three-terminal ferroelectric synapse device with concurrent learning function for artificial neural networks. J. Appl. Phys. 2012, 111, 124108. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Ocker, J.; Muller, S.; Schroeder, U.; Muller, J.; Polakowski, P.; Flachowsky, S.; Bentum, R.V.; Mikolajick, T.; Slesazeck, S. Switching Kinetics in Nanoscale Hafnium Oxide Based Ferroelectric Field-Effect Transistors. Appl. Mater. Interfaces 2017, 9, 3792–3798. [Google Scholar] [CrossRef]

- Oh, S.; Kim, T.; Kwak, M.; Song, J.; Woo, J.; Jeon, S.; Yoo, I.K.; Hwang, H. HfZrOx -based ferroelectric synapse device with 32 levels of conductance states for neuromorphic applications. IEEE Electron Device Lett. 2017, 38, 732–735. [Google Scholar] [CrossRef]

- Fang, Y.; Gomez, J.; Wang, Z.; Datta, S.; Khan, A.I.; Raychowdhury, A. Neuro-Mimetic Dynamics of a Ferroelectric FET-Based Spiking Neuron. IEEE Electron Device Lett. 2019, 40, 1213–1216. [Google Scholar] [CrossRef]

- Wang, Z.; Crafton, B.; Gomez, J.; Xu, R.; Luo, A.; Krivokapic, Z.; Martin, L.; Datta, S.; Raychowdhury, A.; Khan, A.I. Experimental Demonstration of Ferroelectric Spiking Neurons for Unsupervised Clustering. IEEE IEDM 2018. [Google Scholar] [CrossRef] [Green Version]

- Wang, Z.; Khandelwal, S.; Khan, A.I. Ferroelectric Oscillators and Their Coupled Networks. IEEE Electron Device Lett. 2017, 38, 1614–1617. [Google Scholar] [CrossRef]

- Seo, M.; Kang, M.H.; Jeon, S.B.; Bae, H.; Hur, J.; Jang, B.C.; Yun, S.; Cho, S.; Kim, W.K.; Kim, M.S.; et al. Firsrt Demonstration of a Logic-Process Compatible Junctionless Ferroelectric FinFET Synapse for Neuromorphic Applications. IEEE Electron Device Lett. 2018, 39, 1445–1448. [Google Scholar] [CrossRef]

- Alessandri, C.; Pandey, P.; Abusleme, A.; Seabaugh, A. Switching Dynamics of Ferroelectric Zr-Doped HfO2. IEEE Electron Device Lett. 2018, 39, 1780–1783. [Google Scholar] [CrossRef]

- Zubko, P.; Wojdel, J.C.; Hadjimichael, M.; Fernandez-Pena, S.; Sené, A.; Luk’yanchuk, I.; Triscone, J.M.; Íñiguez, J. Negative capacitance in multidomain ferroelectric superlattices. Nature 2016, 534, 524–538. [Google Scholar] [CrossRef] [Green Version]

- Randall, C.A.; Kim, N.; Kucera, J.; Cao, W.W.; Shrout, T.R. Intrinsic and extrinsic size effects in fine-grained morphotropic-phase-boundary lead zirconate titanate ceramics. J. Am. Ceram. Soc. 1998, 81, 677–688. [Google Scholar] [CrossRef]

- Yongqiang, T.; Jialiang, Z.; Yanqing, W.; Chunlei, W.; Vladimir, K.; Baogui, S.; Haitao, Y.; Ruth, M.; Giuseppe, V.; Haixue, Y. Unfolding grain size effects in barium titanate ferroelectric ceramics. Sci. Rep. 2015, 5, 9953. [Google Scholar]

- Hoshina, T.; Takizawa, K.; Li, J.; Kasama, T.; Kakemoto, H.; Tsurumi, T. Domain size effect on dielectric properties of barium titanate ceramics. Jpn. J. Appl. Phys. 2008, 47, 7607–7611. [Google Scholar] [CrossRef]

- Ghosh, D.; Sakata, A.; Carter, J.; Thomas, P.A.; Han, H.; Nino, J.C.; Jones, J.L. Domain wall displacement is the origin of superior permittivity and piezoelectricity in BaTiO3 at intermediate grain sizes. Adv. Func. Mater. 2014, 24, 885–896. [Google Scholar] [CrossRef] [Green Version]

- Shin, Y.; Grinberg, I.; Chen, I.; Rappe, A.M. Nucleation and Growth Mechanism of Ferroelectric Domain-Wall Motion. Nature 2007, 449, 881–884. [Google Scholar] [CrossRef] [Green Version]

- Kato, Y.; Kaneko, Y.; Tananka, H.; Shimada, Y. Nonvolatile Memory Using Epitaxially Grown Composite-Oxide-Film Technology. Jpn. J. Appl. Phys. 2008, 47, 2719–2724. [Google Scholar] [CrossRef]

- Wong, J.C.; Salahuddin, S. Negative Capacitance Transistors. Proc. IEEE 2019, 107, 49–62. [Google Scholar] [CrossRef]

- Zhou, J.; Han, G.; Li, J.; Liu, Y.; Peng, Y.; Zhang, J.; Sun, Q.-Q.; Zhang, D.W.; Hao, Y. Effects of the variation of VGS sweep range on the performance of negative capacitance FETs. IEEE Trans. Electron Device Lett. 2018, 39, 618–621. [Google Scholar] [CrossRef]

- Khan, A.I.; Yeung, C.W.; Hu, C.; Salahuddin, S. Ferroelectric negative capacitance MOSFET: Capacitance tuning & antiferroelectric operation. IEDM Tech. Dig. 2011, 255–258. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moon, S.; Shin, J.; Shin, C. Understanding of Polarization-Induced Threshold Voltage Shift in Ferroelectric-Gated Field Effect Transistor for Neuromorphic Applications. Electronics 2020, 9, 704. https://doi.org/10.3390/electronics9050704

Moon S, Shin J, Shin C. Understanding of Polarization-Induced Threshold Voltage Shift in Ferroelectric-Gated Field Effect Transistor for Neuromorphic Applications. Electronics. 2020; 9(5):704. https://doi.org/10.3390/electronics9050704

Chicago/Turabian StyleMoon, Seungjun, Jaemin Shin, and Changhwan Shin. 2020. "Understanding of Polarization-Induced Threshold Voltage Shift in Ferroelectric-Gated Field Effect Transistor for Neuromorphic Applications" Electronics 9, no. 5: 704. https://doi.org/10.3390/electronics9050704