A New Three-Phase Hybrid Multilevel Topology with Hybrid Modulation and Control Strategy for Front-End Converter Applications

Abstract

:1. Introduction

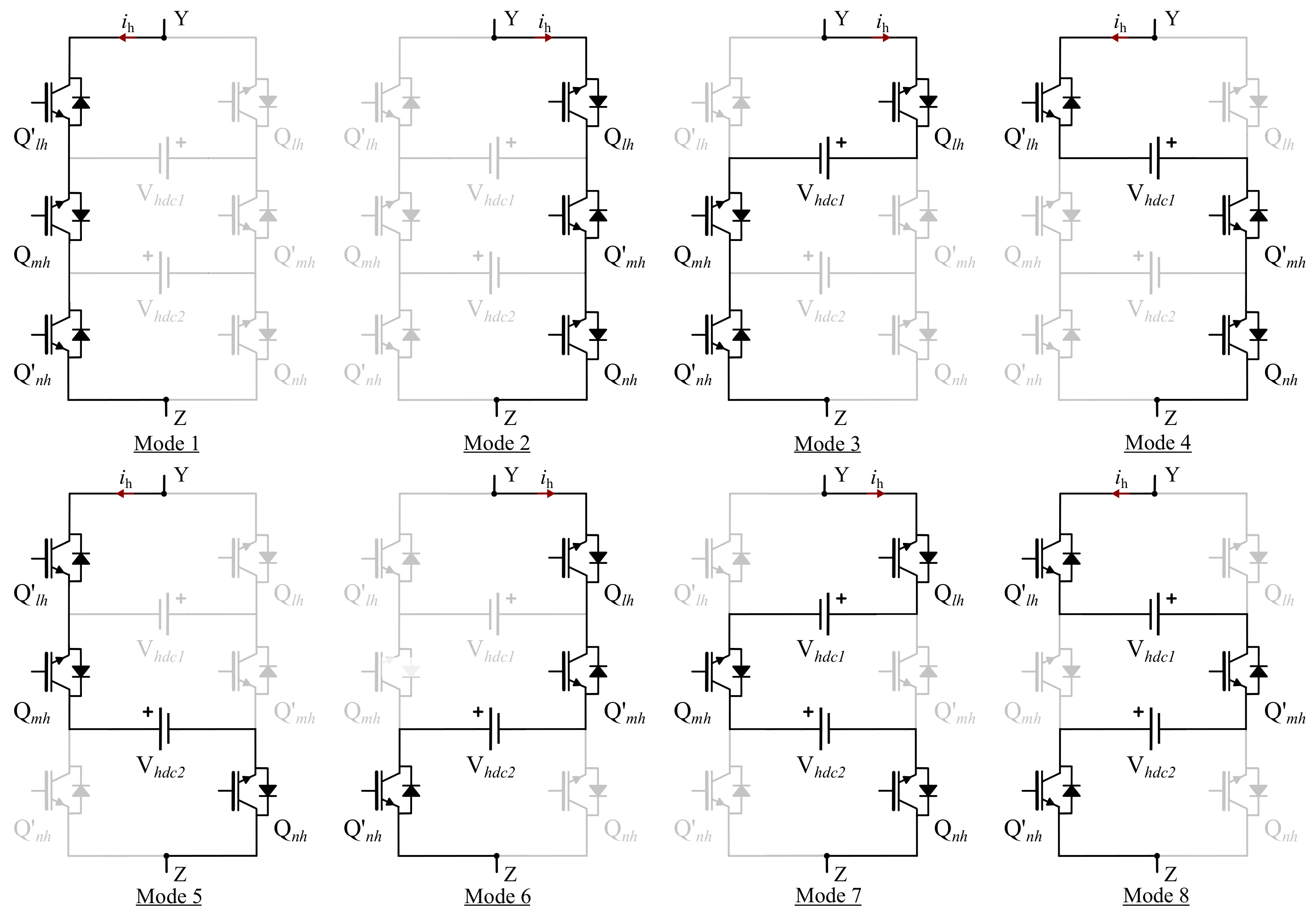

2. Proposed Converter Configuration

3. Hybrid Modulation Technique

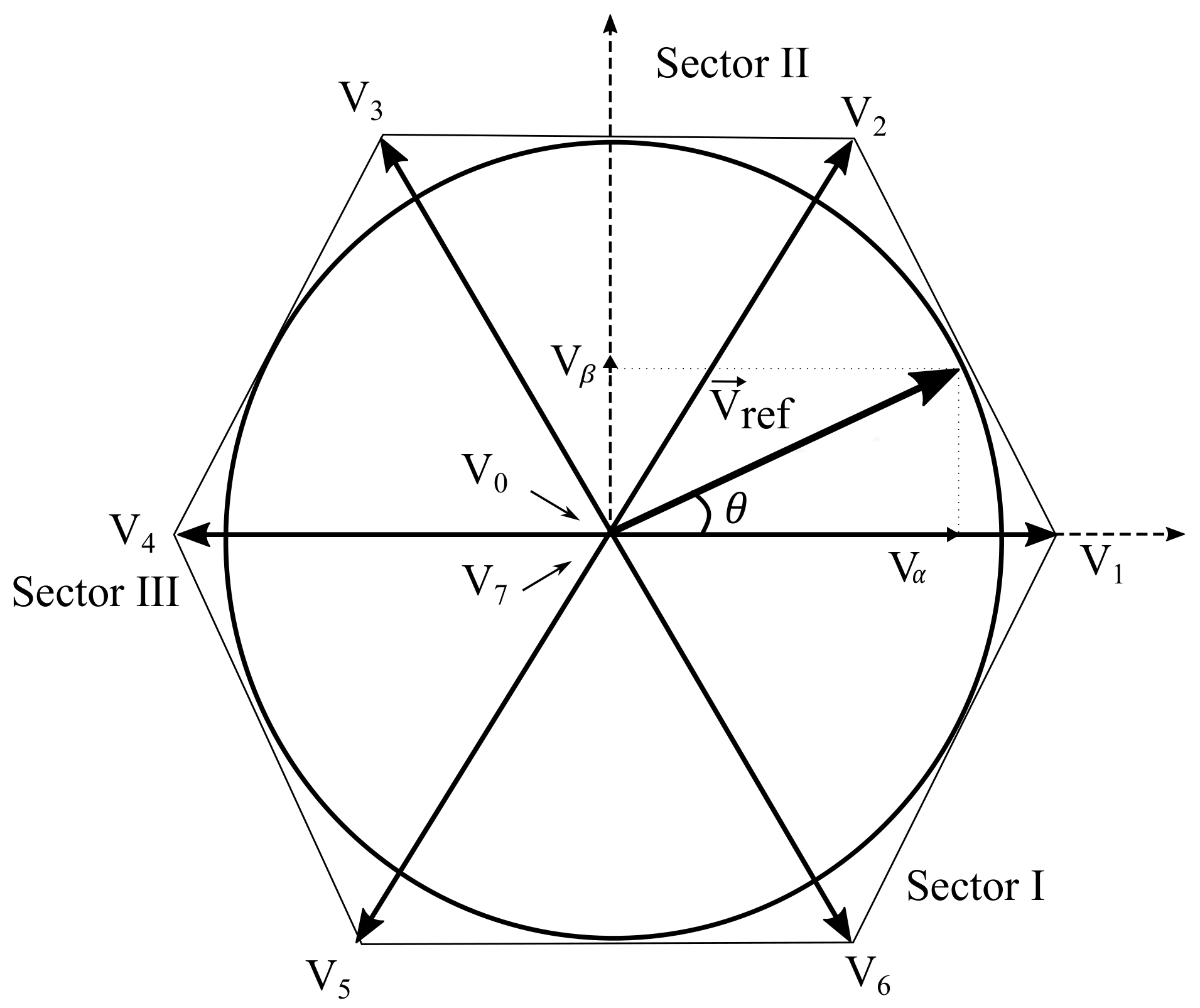

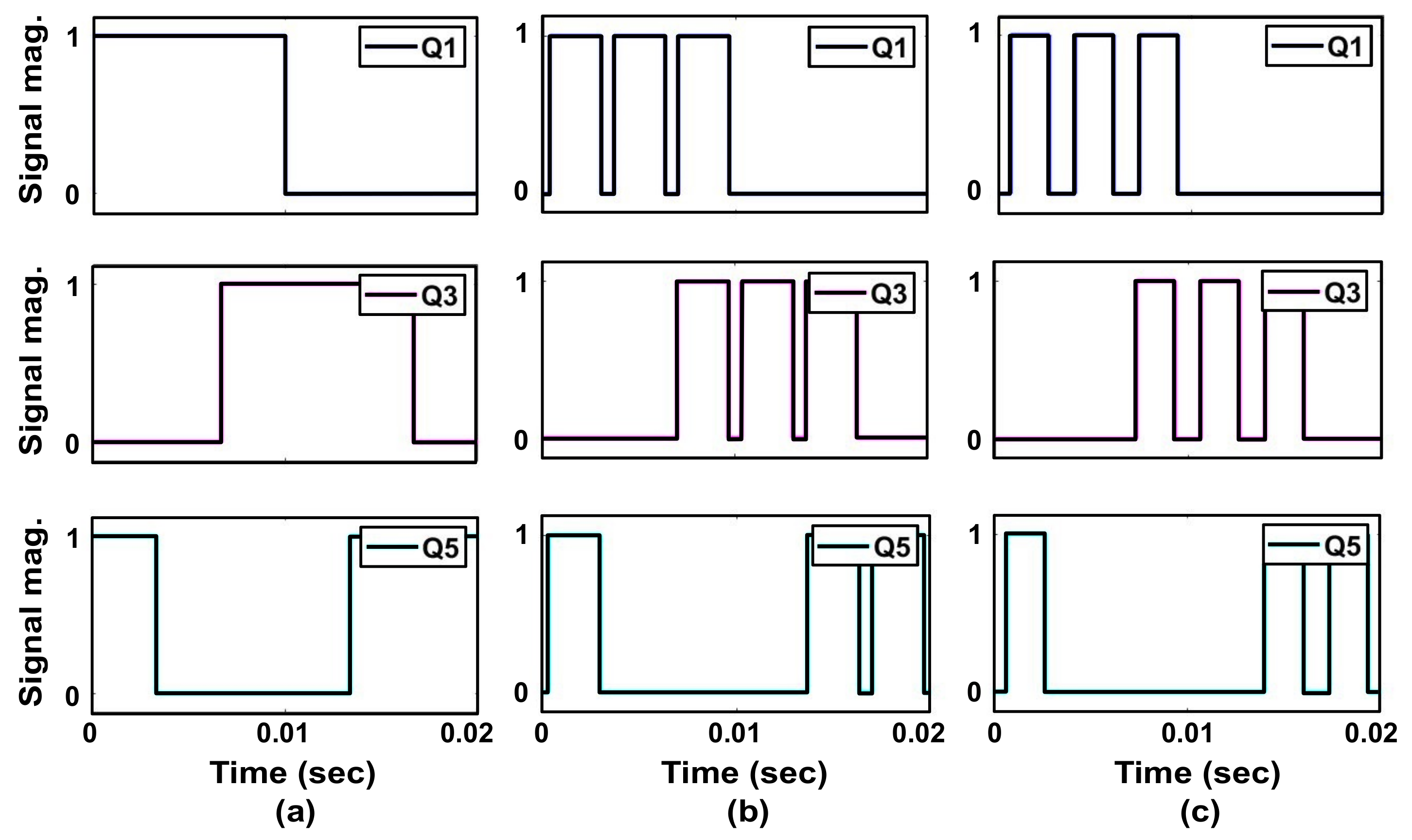

3.1. Modulation Strategy for Three-ph Full Bridge

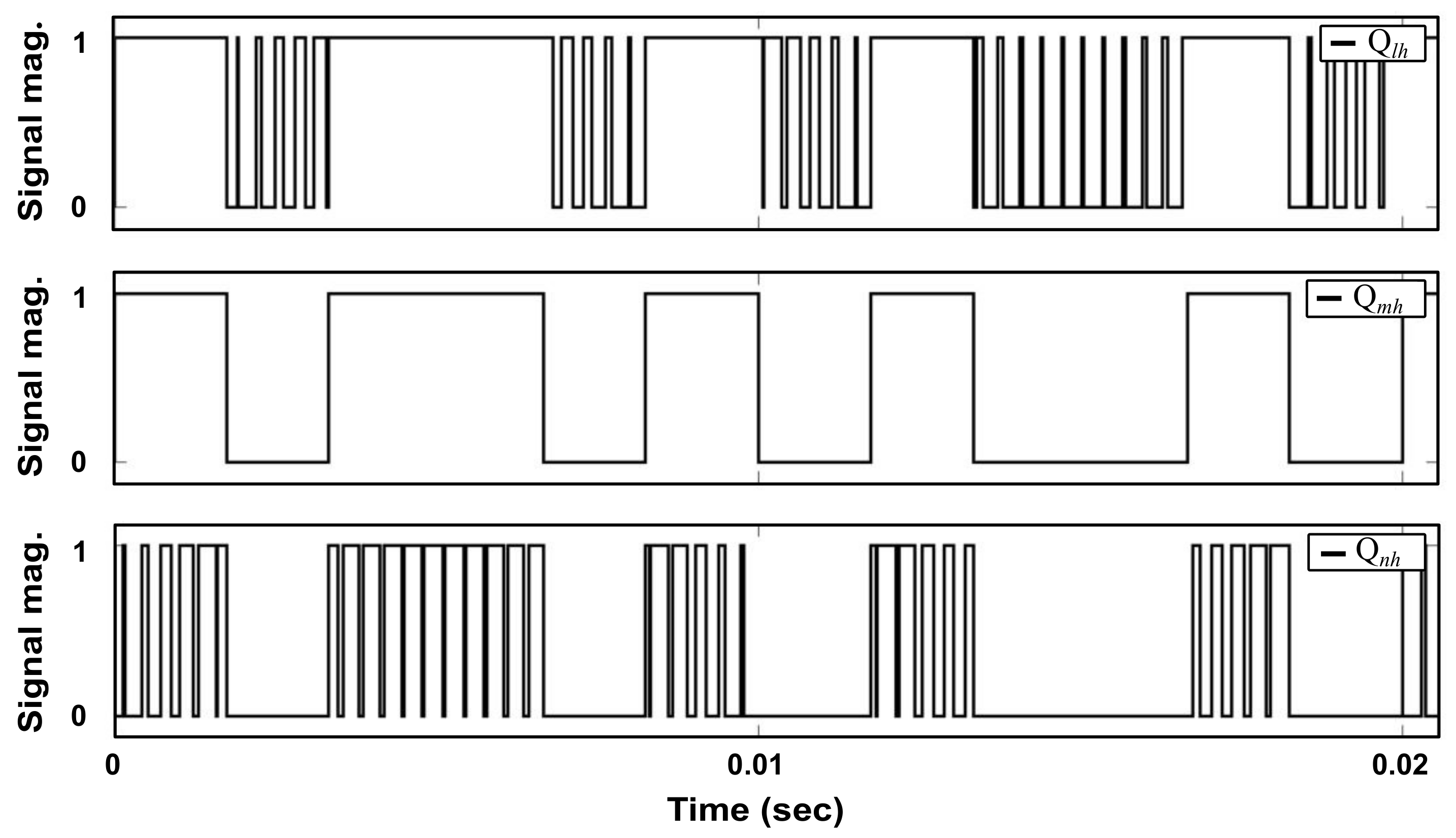

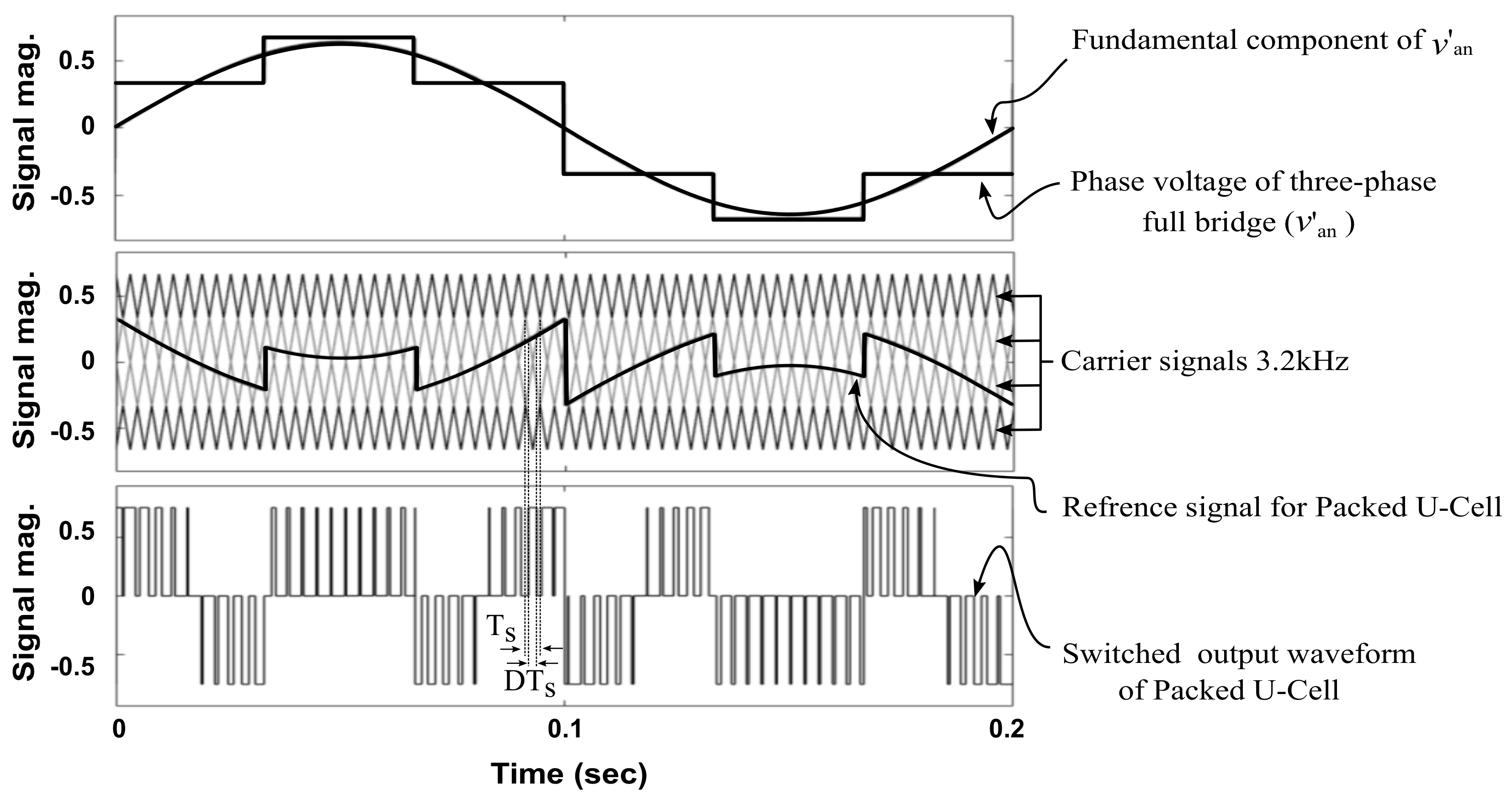

3.2. Modulation Strategy for Packed U-Cell

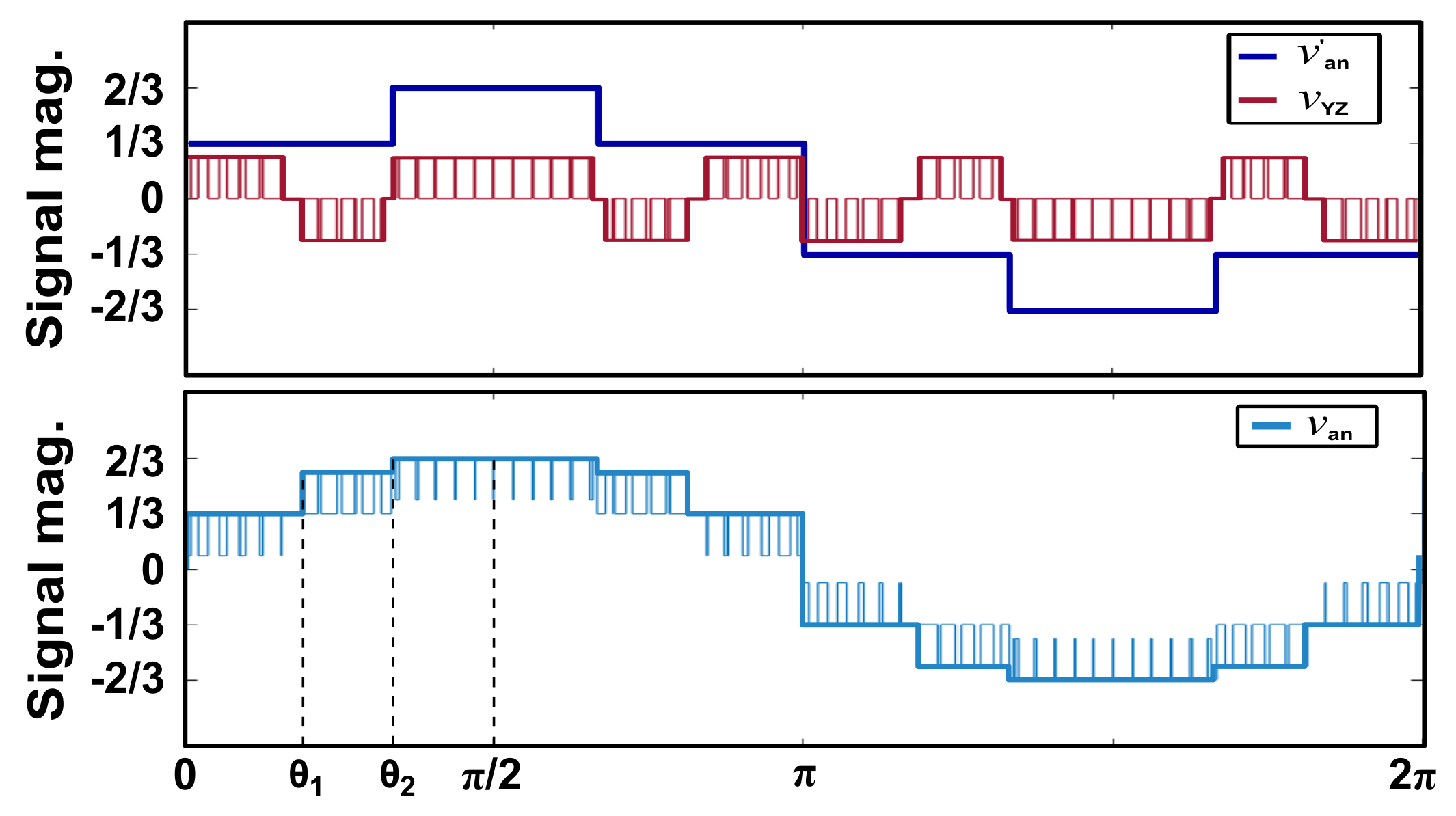

3.3. Modulation Range

3.4. Switch Losses

3.5. Total Harmonic Distortion

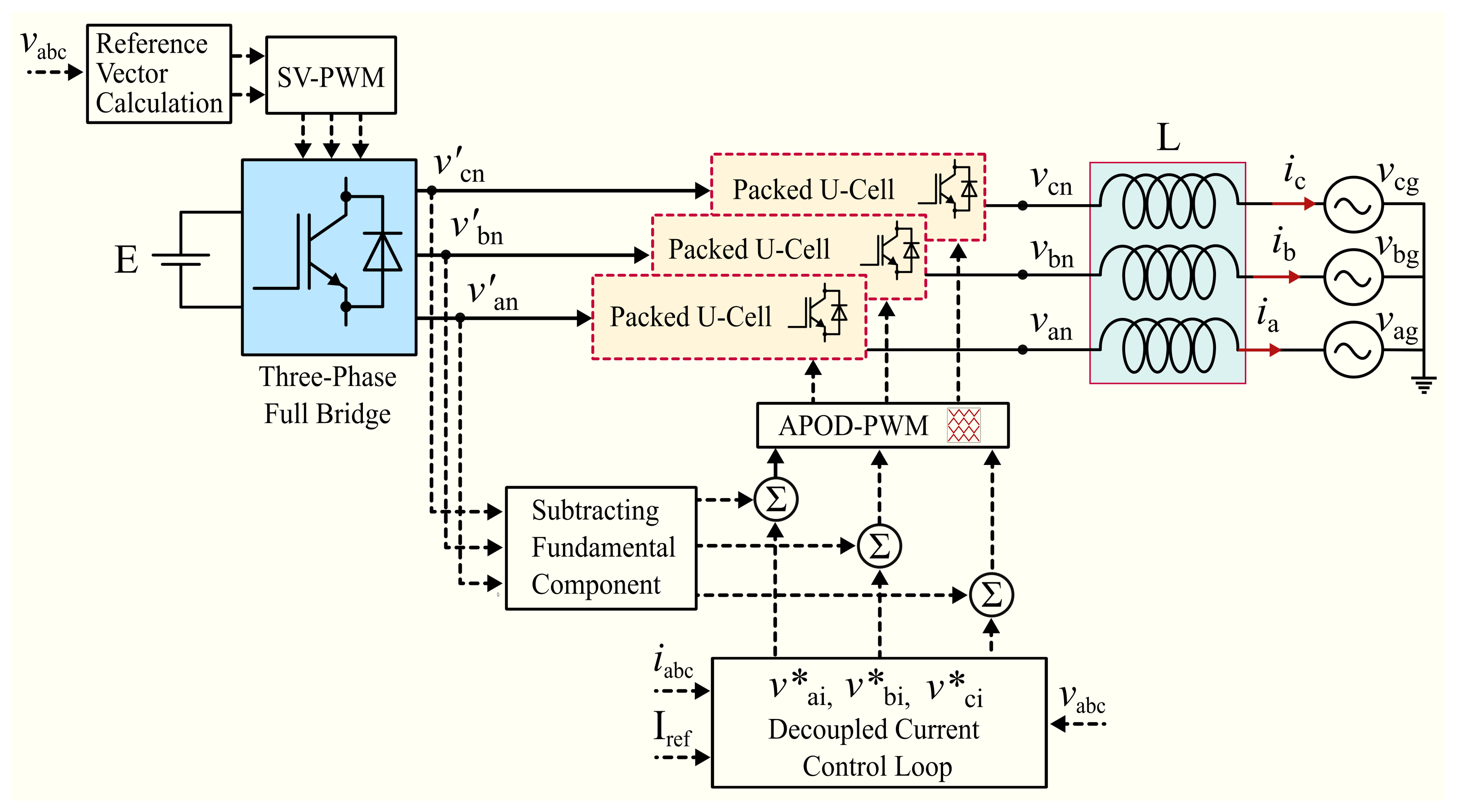

4. Control Scheme

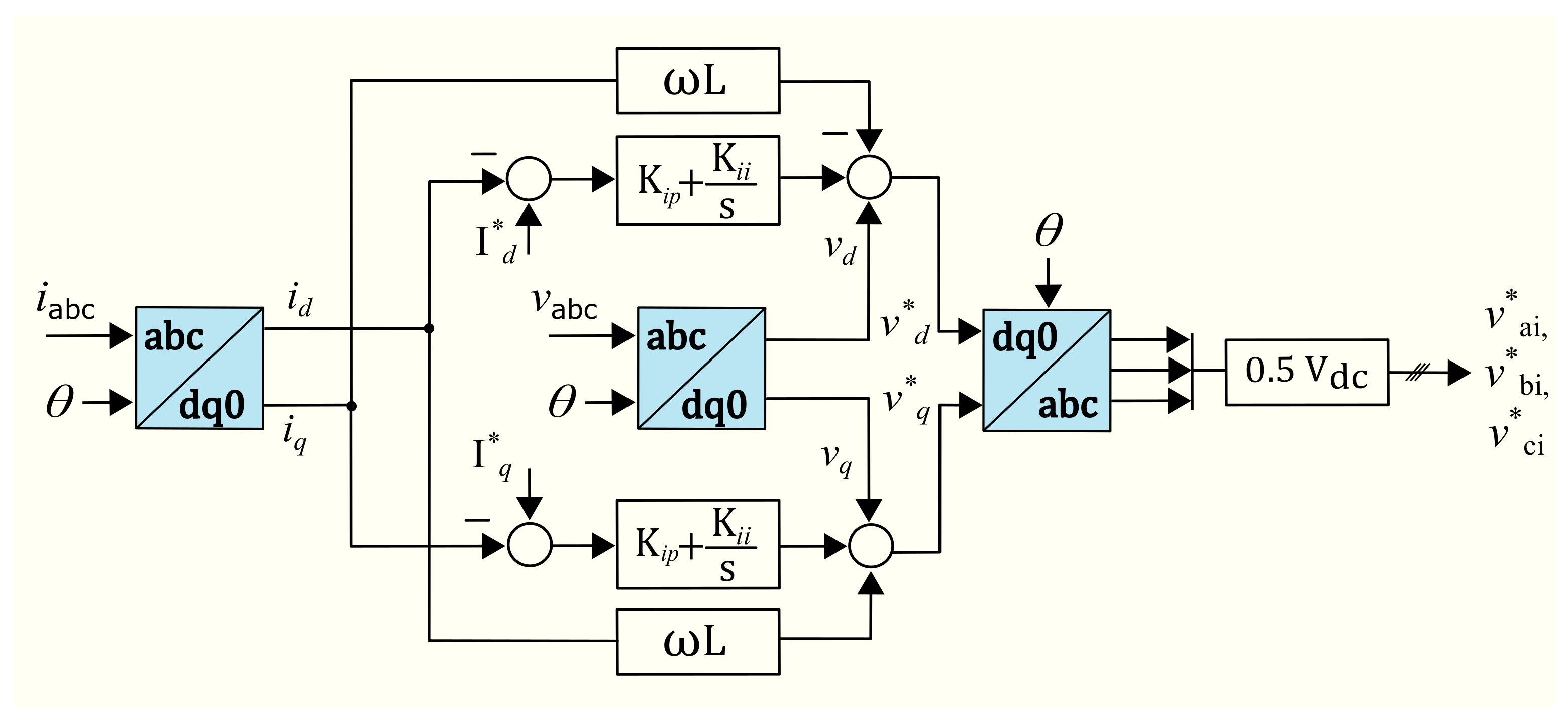

Feedback Control Mechanism

5. Results and Discussion

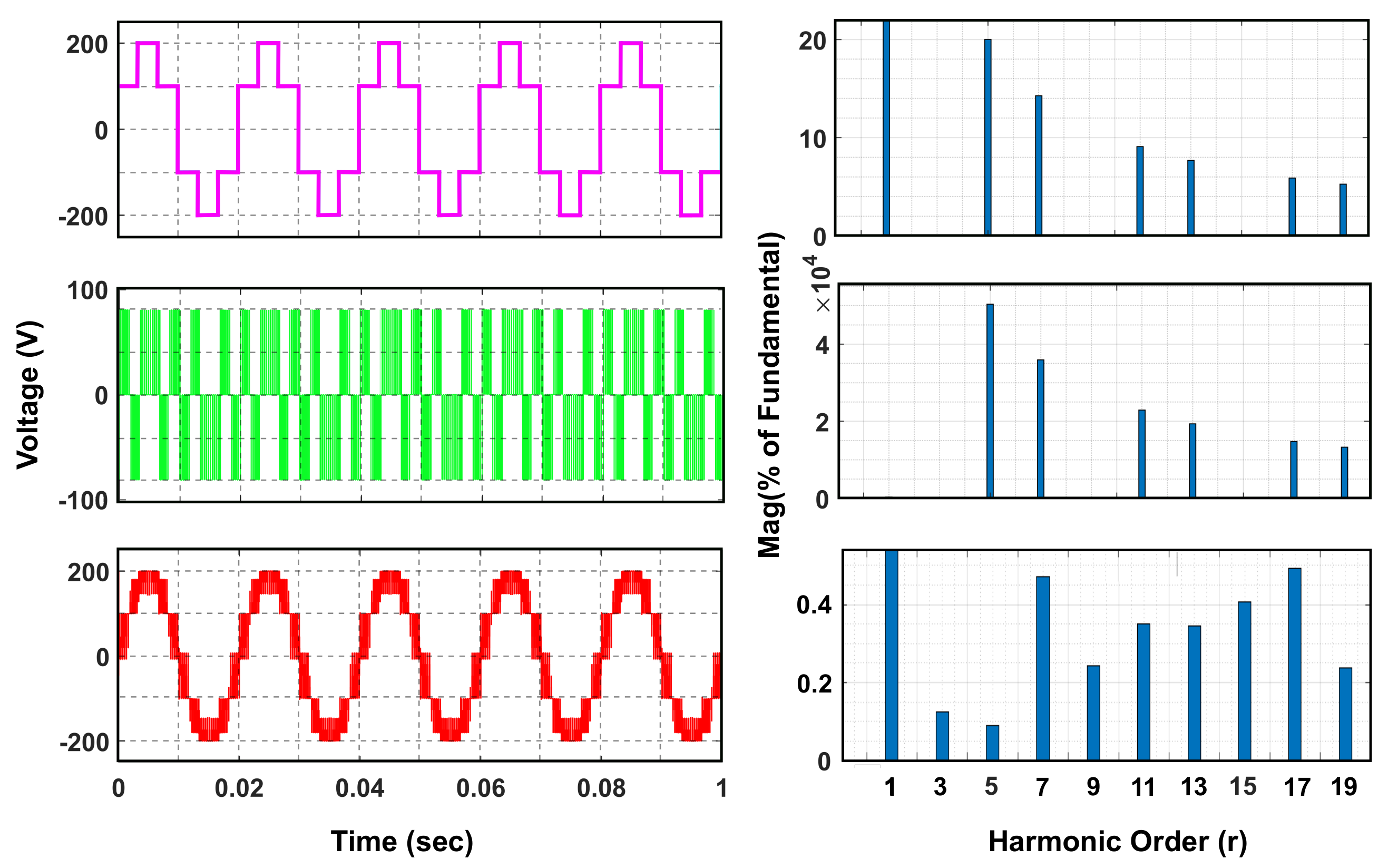

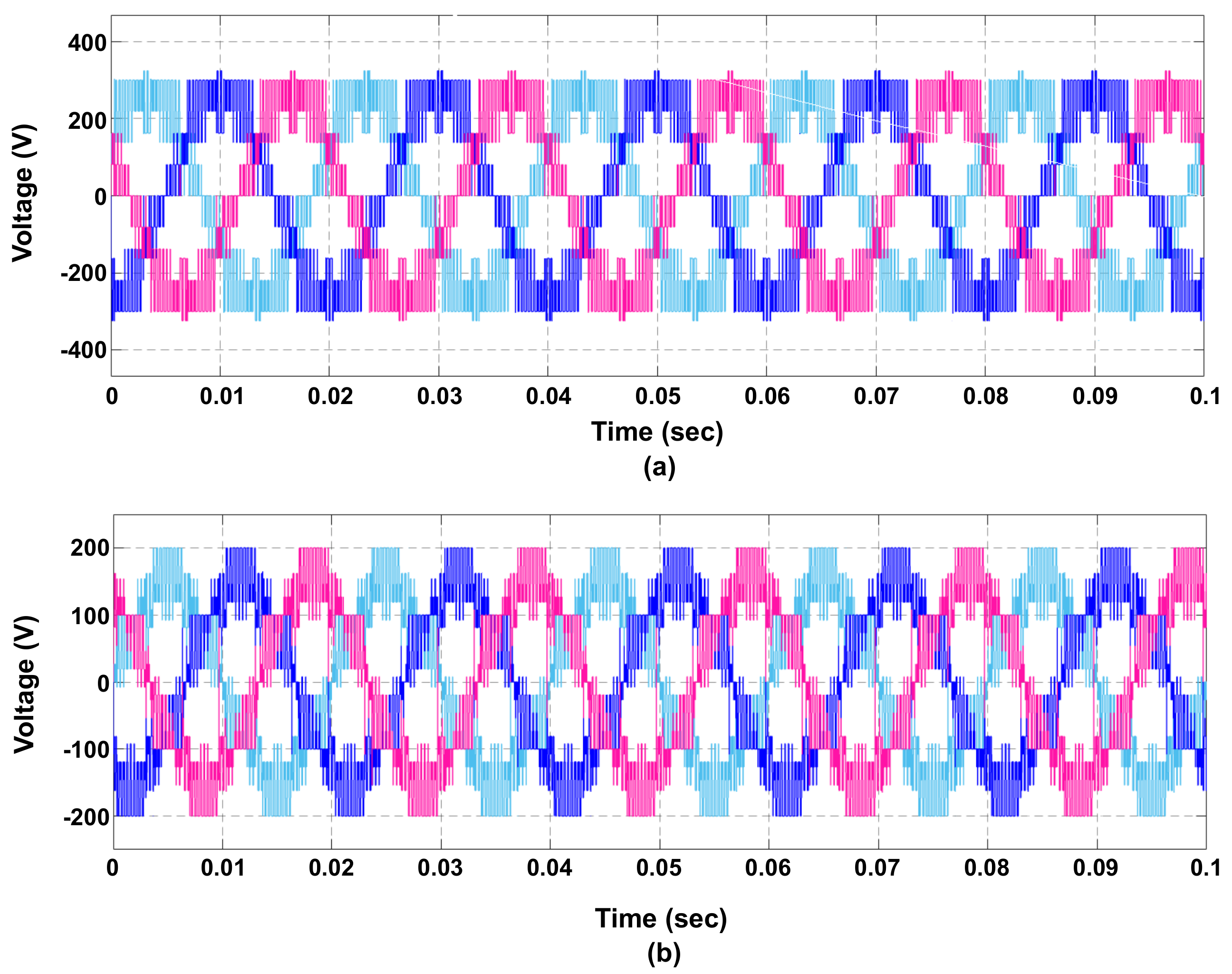

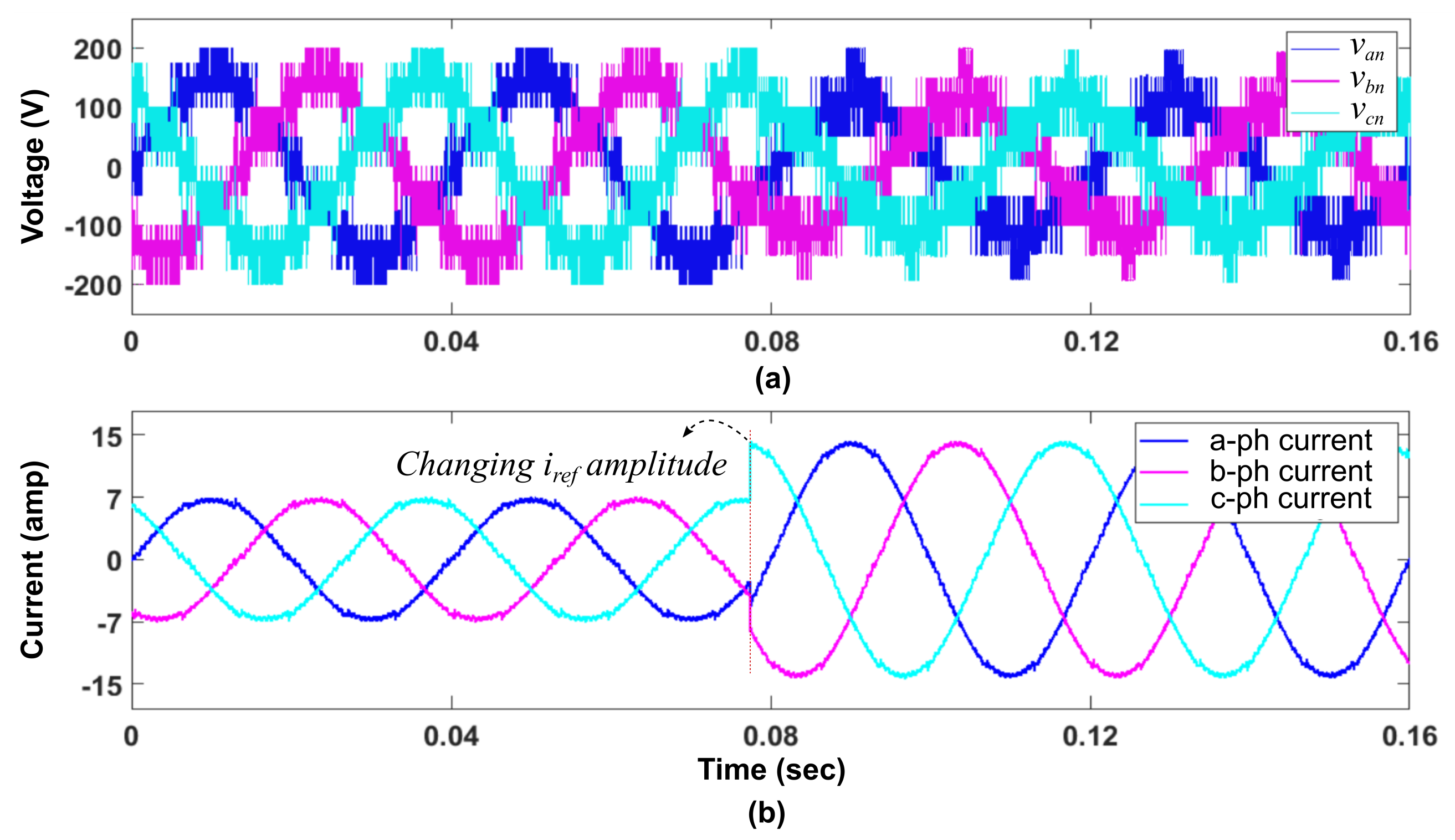

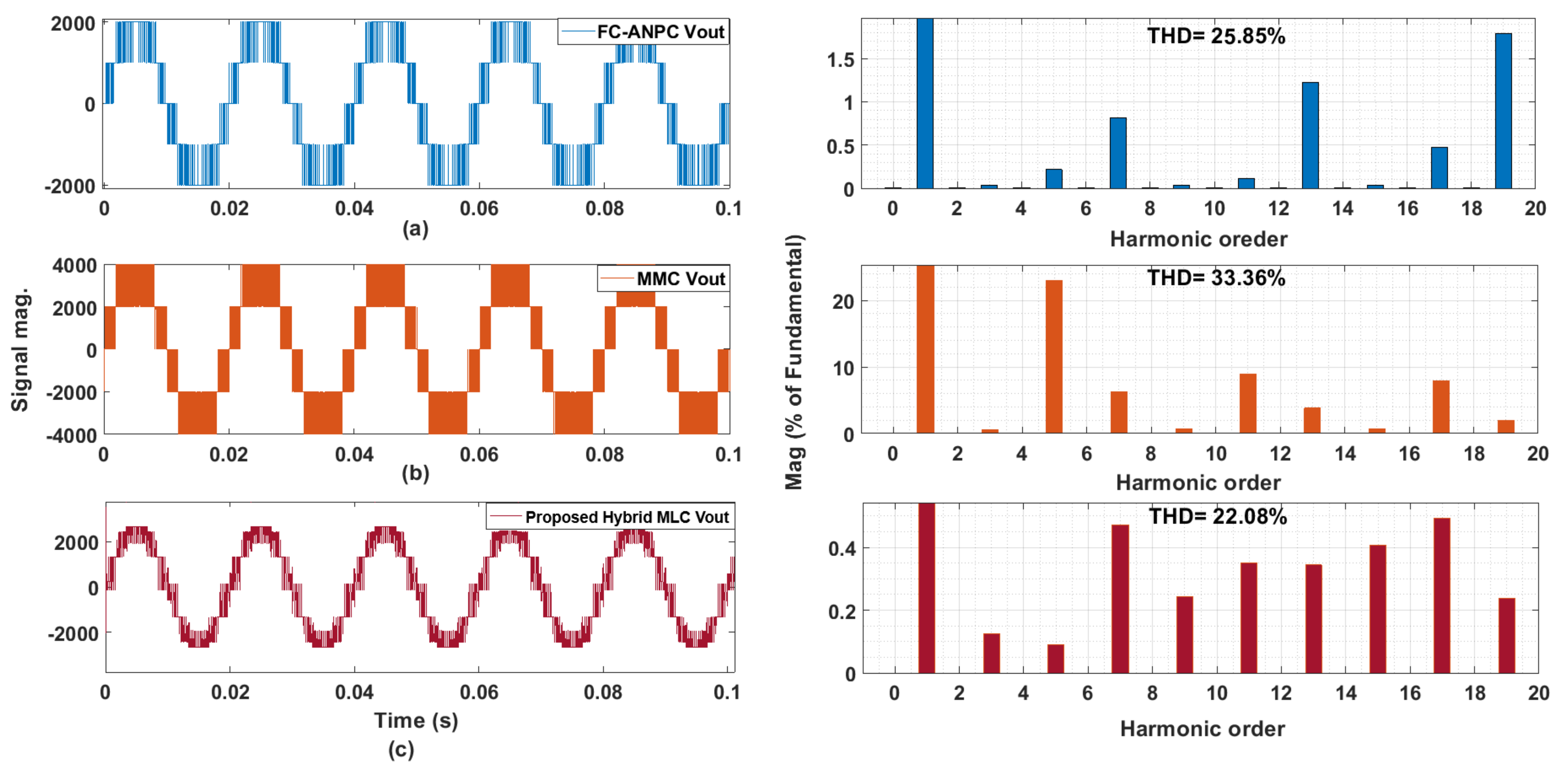

5.1. Simulation Results

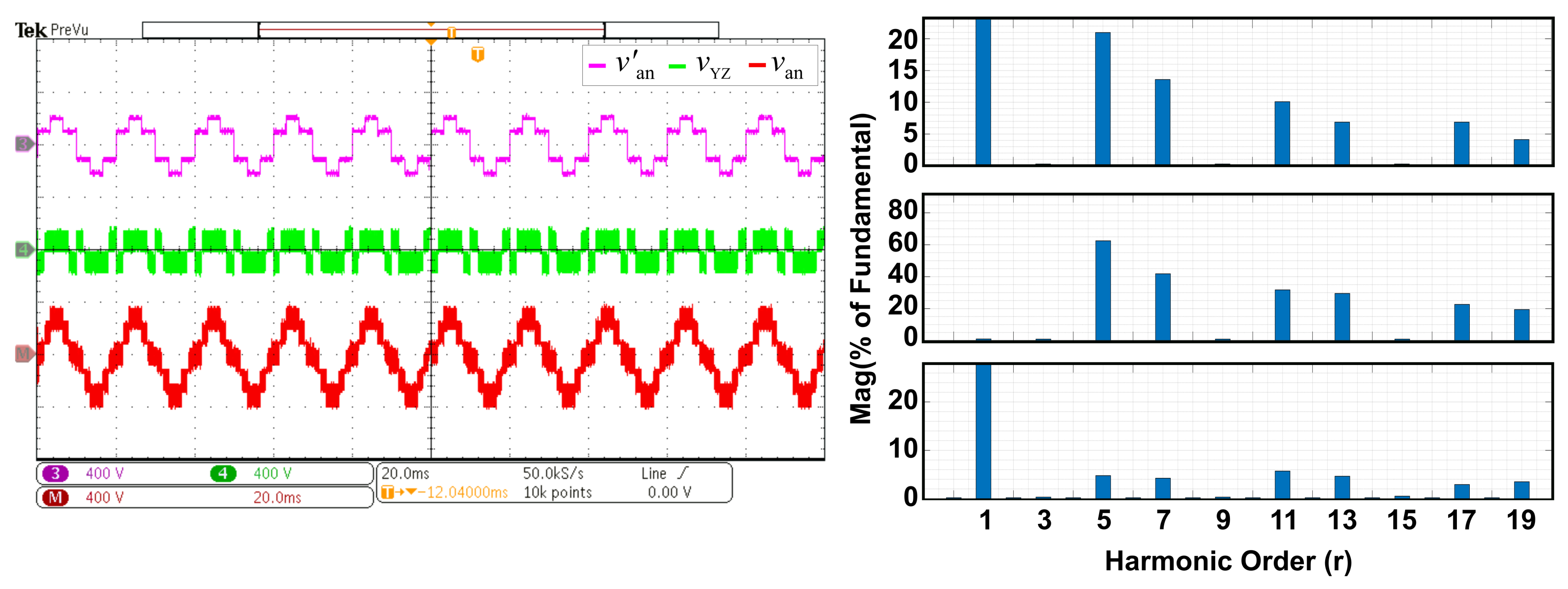

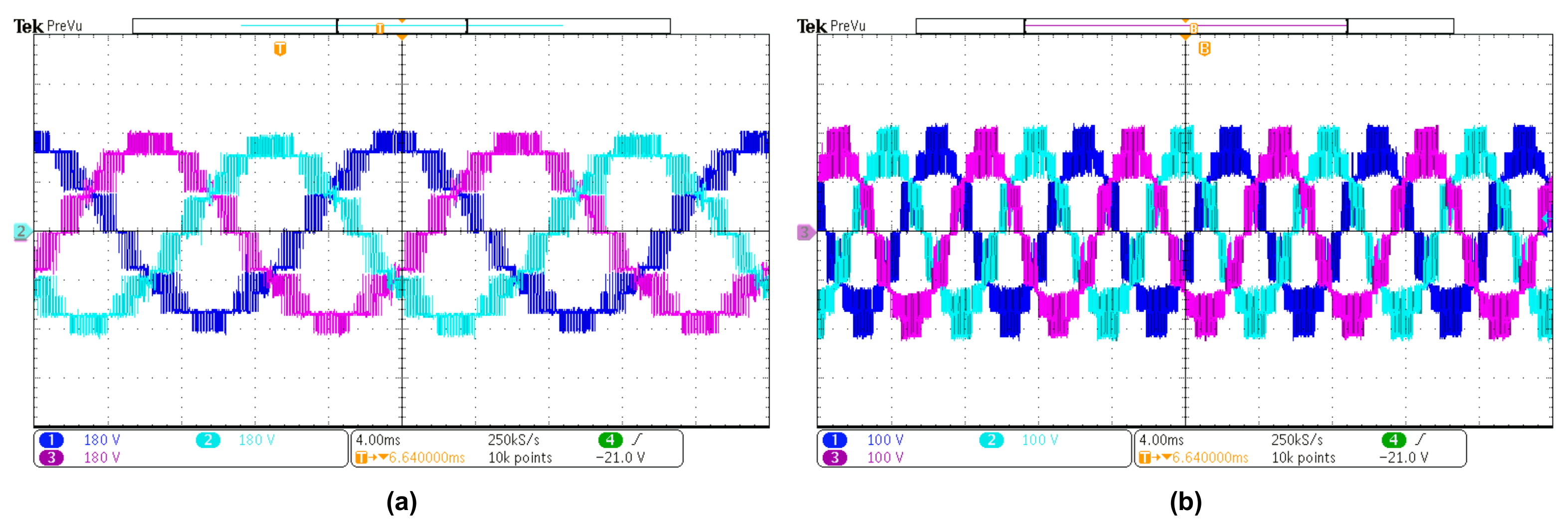

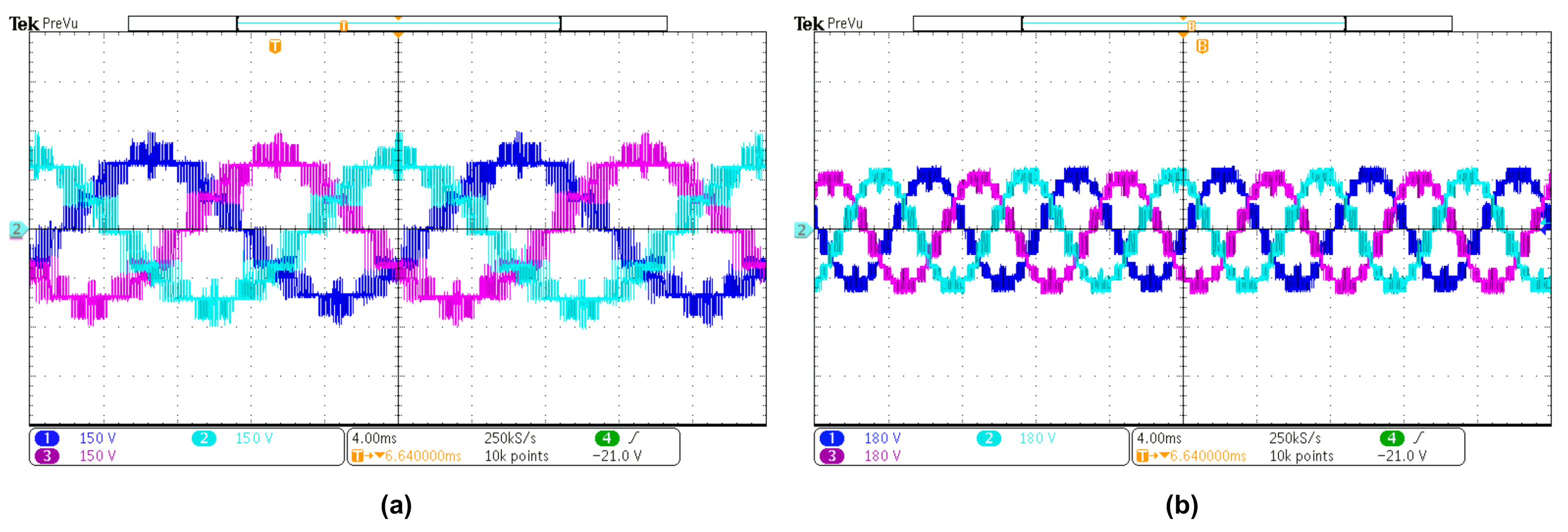

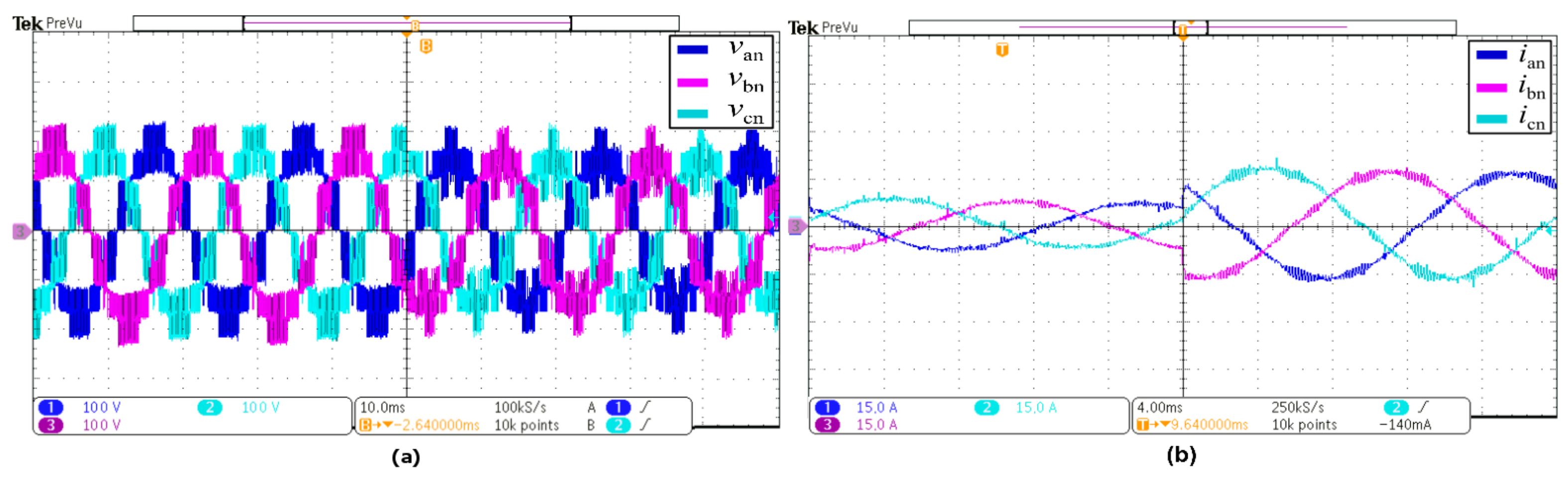

5.2. Experiment Results

6. Comparative Analysis

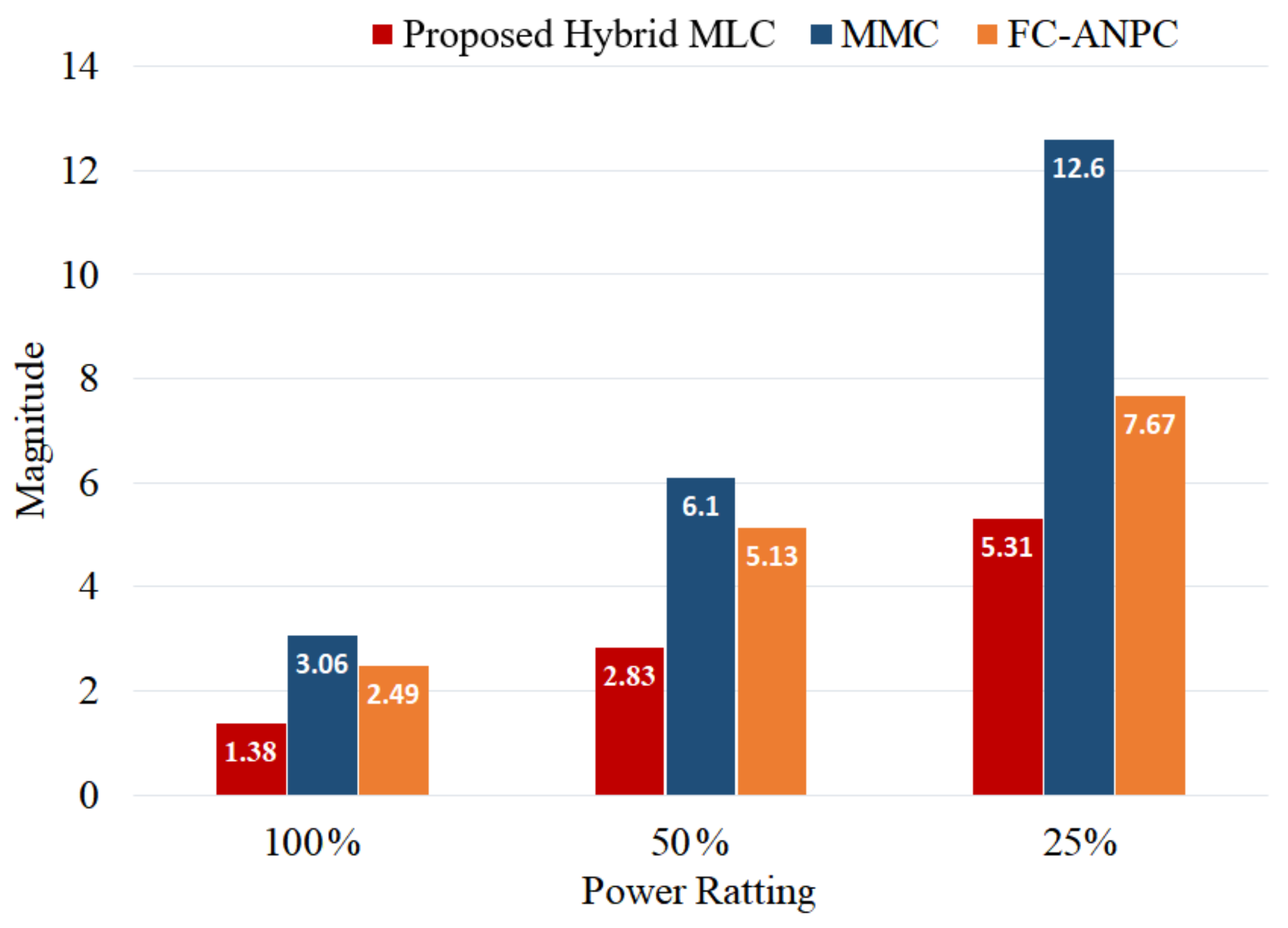

6.1. Comparison Based on Voltage and Current THD

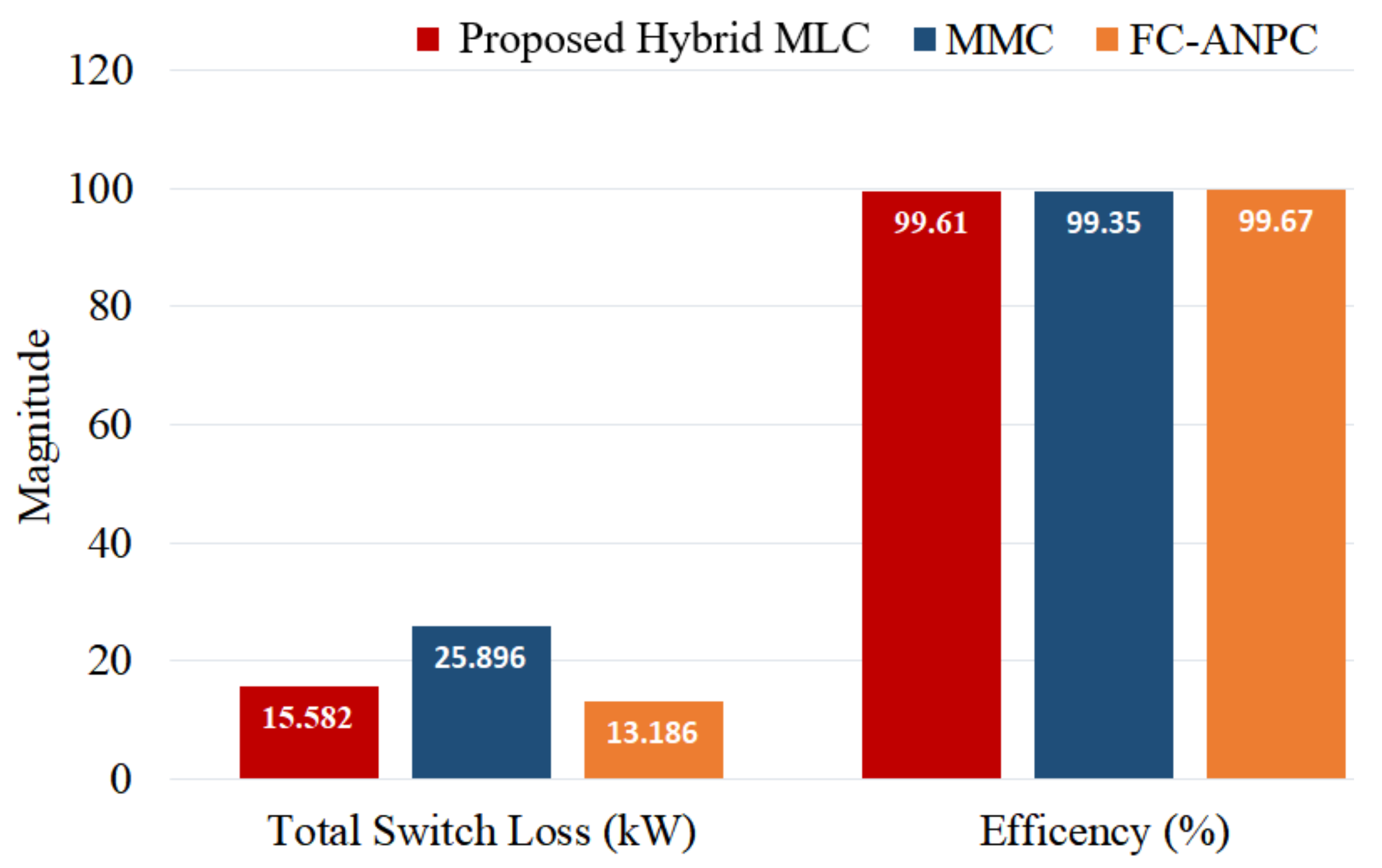

6.2. Comparison Based on Converter Switch Loss and Efficiency

6.3. Comparison Based on Component Count

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Alahmad, A.; Kaçar, F. Medium-Voltage (MV) Motor Drives Topologies and Applications. In Proceedings of the 2022 International Conference on Electrical, Computer and Energy Technologies (ICECET), Prague, Czech Republic, 20–22 July 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Sharifi, S.; Ferencz, I.F.; Kamel, T.; Petreuş, D.; Tricoli, P. Medium-voltage DC electric railway systems: A review on feeding arrangements and power converter topologies. IET Electr. Syst. Transp. 2022, 12, 223–237. [Google Scholar] [CrossRef]

- Rahouma, A.; Oggier, G.G.; Balda, J.C. A Review of Medium-Voltage Front-End Converters for Grid-Connected Battery Energy Storage Systems. In Proceedings of the 2022 IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Kiel, Germany, 26–29 June 2022; pp. 1–7. [Google Scholar] [CrossRef]

- Rabiul Islam, M.; Mahfuz-Ur-Rahman, A.M.; Muttaqi, K.M.; Sutanto, D. State-of-the-Art of the Medium-Voltage Power Converter Technologies for Grid Integration of Solar Photovoltaic Power Plants. IEEE Trans. Energy Convers. 2019, 34, 372–384. [Google Scholar] [CrossRef]

- IEEE Std 519-2022 (Revision of IEEE Std 519-2014); IEEE Standard for Harmonic Control in Electric Power Systems. IEEE: Piscataway, NJ, USA, 2022; pp. 1–31. [CrossRef]

- Mondol, M.H.; Biswas, S.P.; Rahman, M.A.; Islam, M.R.; Mahfuz-Ur-Rahman, A.M.; Muttaqi, K.M. A New Hybrid Multilevel Inverter Topology With Level Shifted Multicarrier PWM Technique for Harvesting Renewable Energy. IEEE Trans. Ind. Appl. 2022, 58, 2574–2585. [Google Scholar] [CrossRef]

- Fazel, S.S. Investigation and Comparison of Multi-Level Converters for Medium Voltage Applications. 2007. Available online: https://depositonce.tu-berlin.de/items/6cd2e1d6-ae7f-42b5-8bb7-0410560b21b4 (accessed on 11 June 2021).

- Krug, D.; Bernet, S.; Fazel, S.S.; Jalili, K.; Malinowski, M. Comparison of 2.3-kV Medium-Voltage Multilevel Converters for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2979–2992. [Google Scholar] [CrossRef]

- Tolbert, L.; Peng, F.Z.; Habetler, T. Multilevel converters for large electric drives. IEEE Trans. Ind. Appl. 1999, 35, 36–44. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Alepuz, S.; Busquets-Monge, S.; Bordonau, J.; Gago, J.; Gonzalez, D.; Balcells, J. Interfacing Renewable Energy Sources to the Utility Grid Using a Three-Level Inverter. IEEE Trans. Ind. Electron. 2006, 53, 1504–1511. [Google Scholar] [CrossRef]

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Lai, J.S.; Peng, F.Z. Multilevel converters-a new breed of power converters. IEEE Trans. Ind. Appl. 1996, 32, 509–517. [Google Scholar] [CrossRef]

- Goel, R.; Dey, A. Higher Level Multilevel Inverter for Medium Voltage Drives with High DC-link Voltage Utilization. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Hammond, P. A new approach to enhance power quality for medium voltage drives. In Proceedings of the Industry Applications Society 42nd Annual Petroleum and Chemical Industry Conference, Denver, CO, USA, 11–13 September 1995; pp. 231–235. [Google Scholar] [CrossRef]

- Zolfagharian, O.; Farsijani, M.; Keyvanloo, E.; Tavakoli Bina, M. A New Modulation Technique for Improving the Performance of Two-Phase Cascaded H-bridge Multilevel Inverter. In Proceedings of the 2022 13th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–3 February 2022; pp. 202–206. [Google Scholar] [CrossRef]

- Ipoum-Ngome, P.G.; Mon-Nzongo, D.L.; Flesch, R.C.C.; Tang, J.; Jin, T.; Wang, M.; Lai, C. Multiobjective Model-Free Predictive Control for Motor Drives and Grid-Connected Applications: Operating with Unbalanced Multilevel Cascaded H-Bridge Inverters. IEEE Trans. Power Electron. 2023, 38, 3014–3028. [Google Scholar] [CrossRef]

- Guo, X.; Wang, X.; Wang, C.; Lu, Z.; Hua, C.; Blaabjerg, F. Improved Modulation Strategy for Singe-Phase Cascaded H-Bridge Multilevel Inverter. IEEE Trans. Power Electron. 2022, 37, 2470–2474. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-Voltage Multilevel Converters—State of the Art, Challenges, and Requirements in Industrial Applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Motwani, J.K.; Liu, J.; Burgos, R.; Zhou, Z.; Dong, D. Hybrid Modular Multilevel Converters for High-AC/Low-DC Medium-Voltage Applications. IEEE Open J. Power Electron. 2023, 4, 265–282. [Google Scholar] [CrossRef]

- Almakhles, D.J.; Ali, J.S.M.; Padmanaban, S.; Bhaskar, M.S.; Subramaniam, U.; Sakthivel, R. An Original Hybrid Multilevel DC-AC Converter Using Single-Double Source Unit for Medium Voltage Applications: Hardware Implementation and Investigation. IEEE Access 2020, 8, 71291–71301. [Google Scholar] [CrossRef]

- Motwani, J.K.; Liu, J.; Boroyevich, D.; Burgos, R.; Zhou, Z.; Dong, D. Modeling and Control of a Hybrid Modular Multilevel Converter for High-AC/Low-DC Medium-Voltage Applications. IEEE Trans. Power Electron. 2024, 39, 5371–5385. [Google Scholar] [CrossRef]

- Sarkar, I.; Fernandes, B.G. A Hybrid Symmetric Cascaded H-Bridge Multilevel Converter Topology. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 4032–4044. [Google Scholar] [CrossRef]

- Ali, M.; Hafeez, G.; Farooq, A.; Shafiq, Z.; Ali, F.; Usman, M.; Mihet-Popa, L. A Novel Control Approach to Hybrid Multilevel Inverter for High-Power Applications. Energies 2021, 14, 4563. [Google Scholar] [CrossRef]

- Ali, M.; Khan, M.M.; Xu, J.; Faiz, M.T.; Ali, Y.; Hashmi, K.; Tang, H. Series Active Filter Design Based on Asymmetric Hybrid Modular Multilevel Converter for Traction System. Electronics 2018, 7, 134. [Google Scholar] [CrossRef]

- Ali, M.; Mansoor, M.; Tang, H.; Rana, A. Analysis of a seven-level asymmetrical hybrid multilevel converter for traction systems. IET Power Electron. 2017, 10, 1878–1888. [Google Scholar] [CrossRef]

- Veenstra, M.; Rufer, A. Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives. IEEE Trans. Ind. Appl. 2005, 41, 655–664. [Google Scholar] [CrossRef]

- Adam, G.P.; Anaya-Lara, O.; Burt, G.M.; Telford, D.; Williams, B.W.; Mcdonald, J.R. Modular multilevel inverter: Pulse width modulation and capacitor balancing technique. IET Power Electron. 2010, 3, 702–715. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Kolar, J.W. The New High-Efficiency Hybrid Neutral-Point-Clamped Converter. IEEE Trans. Ind. Electron. 2013, 60, 1919–1935. [Google Scholar] [CrossRef]

- Xu, S.; Zhang, J.; Hu, X.; Jiang, Y. A Novel Hybrid Five-Level Voltage-Source Converter Based on T-Type Topology for High-Efficiency Applications. IEEE Trans. Ind. Appl. 2017, 53, 4730–4743. [Google Scholar] [CrossRef]

- Schweizer, M.; Friedli, T.; Kolar, J.W. Comparative Evaluation of Advanced Three-Phase Three-Level Inverter/Converter Topologies against Two-Level Systems. IEEE Trans. Ind. Electron. 2013, 60, 5515–5527. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Yu, H.; Chen, B.; Yao, W.; Lu, Z. Hybrid Seven-Level Converter Based on T-Type Converter and H-Bridge Cascaded under SPWM and SVM. IEEE Trans. Power Electron. 2018, 33, 689–702. [Google Scholar] [CrossRef]

- Silva, C.A.; Cordova, L.A.; Lezana, P.; Empringham, L. Implementation and Control of a Hybrid Multilevel Converter with Floating DC Links for Current Waveform Improvement. IEEE Trans. Ind. Electron. 2011, 58, 2304–2312. [Google Scholar] [CrossRef]

- Pulikanti, S.R.; Konstantinou, G.; Agelidis, V.G. DC-Link Voltage Ripple Compensation for Multilevel Active-Neutral-Point-Clamped Converters Operated with SHE-PWM. IEEE Trans. Power Deliv. 2012, 27, 2176–2184. [Google Scholar] [CrossRef]

- Colak, I.; Kabalci, E.; Bayindir, R. Review of multilevel voltage source inverter topologies and control schemes. Energy Convers. Manag. 2011, 52, 1114–1128. [Google Scholar] [CrossRef]

- Hasan, N.S.; Rosmin, N.; Osman, D.A.A.; Musta’amal, A.H. Reviews on multilevel converter and modulation techniques. Renew. Sustain. Energy Rev. 2017, 80, 163–174. [Google Scholar] [CrossRef]

- Ostadrahimi, A.; Bifaretti, S. A Simplified Multilevel Space Vector Pulsewidth Modulation (SVPWM) Based on Boundary Lines, Including Overmodulation Zone. IEEE Open J. Ind. Appl. 2023, 4, 215–226. [Google Scholar] [CrossRef]

- Tawfiq, K.B.; Ibrahim, M.N.; Sergeant, P. Multiphase Electric Motor Drive with Improved and Reliable Performance: Combined Star-Pentagon Synchronous Reluctance Motor Fed from Matrix Converter. Mathematics 2022, 10, 3351. [Google Scholar] [CrossRef]

- Ali, M.; Farooq, A.; Khan, M.Q.; Khan, M.M.; Mihet-Popa, L. Analysis of Asymmetric Hybrid Modular Multilevel Topology for Medium-Voltage Front-End Converter Applications. Energies 2023, 16, 1572. [Google Scholar] [CrossRef]

- Wu, M.; Li, Y.W.; Konstantinou, G. A Comprehensive Review of Capacitor Voltage Balancing Strategies for Multilevel Converters under Selective Harmonic Elimination PWM. IEEE Trans. Power Electron. 2021, 36, 2748–2767. [Google Scholar] [CrossRef]

- Yadav, S.K.; Mishra, N.; Singh, B. Multilevel Converter with Nearest Level Control for Integrating Solar Photovoltaic System. IEEE Trans. Ind. Appl. 2022, 58, 5117–5126. [Google Scholar] [CrossRef]

- Prabaharan, N.; Palanisamy, K. A comprehensive review on reduced switch multilevel inverter topologies, modulation techniques and applications. Renew. Sustain. Energy Rev. 2017, 76, 1248–1282. [Google Scholar] [CrossRef]

- Ramírez, R.O.; Baier, C.R.; Villarroel, F.; Espinosa, E.; Arevalo, M.; Espinoza, J.R. Reduction of DC Capacitor Size in Three-Phase Input/Single-Phase Output Power Cells of Multi-Cell Converters through Resonant and Predictive Control: A Characterization of Its Impact on the Operating Region. Mathematics 2023, 11, 3038. [Google Scholar] [CrossRef]

- Ivakhno, V.; Zamaruiev, V.; Ilina, O. Estimation of Semiconductor Switching Losses under Hard Switching using Matlab/Simulink Subsystem. Electr. Control Commun. Eng. 2013, 2, 20–26. [Google Scholar] [CrossRef]

- Stabile, A.; Boccaletti, C.; Marques Cardoso, A.J. A Power Loss Measurement Method Applied to Static Power Converters. IEEE Trans. Instrum. Meas. 2013, 62, 344–352. [Google Scholar] [CrossRef]

- Lu, Y.; Liu, Z.; Lyu, J.; Wei, X. Hierarchical Power Allocation Control for Star-Connected Hybrid Energy Storage System Using Cascaded Multilevel Converters. Front. Energy Res. 2021, 9, 748508. [Google Scholar] [CrossRef]

- Kesler, M.; Kisacikoglu, M.C.; Tolbert, L.M. Vehicle-to-Grid Reactive Power Operation Using Plug-In Electric Vehicle Bidirectional Offboard Charger. IEEE Trans. Ind. Electron. 2014, 61, 6778–6784. [Google Scholar] [CrossRef]

- Sanchez-Ruiz, A.; Mazuela, M.; Alvarez, S.; Abad, G.; Baraia, I. Medium Voltage–High Power Converter Topologies Comparison Procedure, for a 6.6 kV Drive Application Using 4.5 kV IGBT Modules. IEEE Trans. Ind. Electron. 2012, 59, 1462–1476. [Google Scholar] [CrossRef]

- Fazel, S.S.; Bernet, S.; Krug, D.; Jalili, K. Design and Comparison of 4-kV Neutral-Point-Clamped, Flying-Capacitor, and Series-Connected H-Bridge Multilevel Converters. IEEE Trans. Ind. Appl. 2007, 43, 1032–1040. [Google Scholar] [CrossRef]

- Akagi, H.; Fujita, H.; Yonetani, S.; Kondo, Y. A 6.6-kV Transformerless STATCOM Based on a Five-Level Diode-Clamped PWM Converter: System Design and Experimentation of a 200-V 10-kVA Laboratory Model. IEEE Trans. Ind. Appl. 2008, 44, 672–680. [Google Scholar] [CrossRef]

- Zhang, X.; Yue, W. Neutral point potential balance algorithm for three-level NPC inverter based on SHEPWM. Electron. Lett. 2017, 53, 1542–1544. [Google Scholar] [CrossRef]

| Angle | |||

|---|---|---|---|

| E | E − | ||

| E | E + | ||

| E | E − |

| Parameter | Symbol | Value |

|---|---|---|

| Inductor | L | mH |

| DC-link source | V | 85 V |

| Packed U-Cell | PWM | kHz |

| Grid Voltage (rms) | V | 110 V |

| Grid Current (rms) | I | A |

| DC Source Voltage | E | 300 V |

| 3-Ph Full bridge | SW | 150 Hz |

| Parameters | Value |

|---|---|

| Grid Voltage | 2.6 kV (rms) |

| Converter Current | 1000 Amp (rms) |

| DC Bus Voltage | 4 kV |

| DC Link Capacitor (FC-ANPC) | 2 kV |

| FCs (FC-ANPC) | 1 kV |

| Submodule Capacitor (MMC) | 2 kV |

| DC Sources (Proposed Hybrid MLC) | 0.82 kV |

| L | 0.6 mH |

| FC-ANPC Converter | 3.2 Hz |

| Proposed Hybrid MLC | 3.2 Hz |

| MMC Converter | 1.6 kHz |

| Device Type | Stress | Device Number | Device Parameters | |||

|---|---|---|---|---|---|---|

| IGBT | 1200 V | 2.05 V | ||||

| A | IGBT Module | Diode | 820 V | FF1400R12IP4P | 1200 V | 1.85 V |

| IGBT | 1700 V | 2.1 V | ||||

| B | IGBT Module | Diode | 1000 V | FF1800R17IP5 | 1700 V | 1.7 V |

| IGBT | 3300 V | 4.3 V | ||||

| C | IGBT Module | Diode | 2200 V | FZ1200R33KF2C | 3300 V | 2.8 V |

| D | IGCT | 3200 V | 5SHY42L6500 | 4000 V | 1.8 V | |

| Diode | 3200 V | DD1200S45KL3 | 4500 V | 2.5 V | ||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ali, M.; Faiz, M.T.; Khan, M.M.; Ng, V.; Loo, K.-H. A New Three-Phase Hybrid Multilevel Topology with Hybrid Modulation and Control Strategy for Front-End Converter Applications. Mathematics 2024, 12, 2116. https://doi.org/10.3390/math12132116

Ali M, Faiz MT, Khan MM, Ng V, Loo K-H. A New Three-Phase Hybrid Multilevel Topology with Hybrid Modulation and Control Strategy for Front-End Converter Applications. Mathematics. 2024; 12(13):2116. https://doi.org/10.3390/math12132116

Chicago/Turabian StyleAli, Muhammad, Muhammad Talib Faiz, Muhammad Mansoor Khan, Vincent Ng, and Ka-Hong Loo. 2024. "A New Three-Phase Hybrid Multilevel Topology with Hybrid Modulation and Control Strategy for Front-End Converter Applications" Mathematics 12, no. 13: 2116. https://doi.org/10.3390/math12132116