Shallow Trench Isolation Patterning to Improve Photon Detection Probability of Single-Photon Avalanche Diodes Integrated in FD-SOI CMOS Technology

Abstract

1. Introduction

2. Materials and Methods

2.1. SPAD FD-SOI Architecture and Constructive Interferences

2.1.1. SPAD Integrated in FD-SOI CMOS Technology

2.1.2. Constructive Interferences with STI Patterning (for FSI)

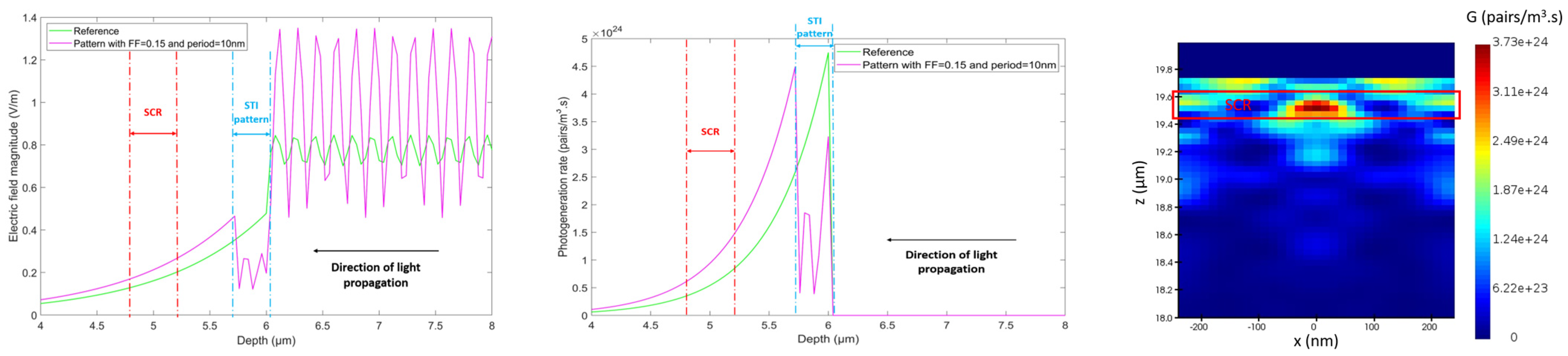

2.2. STI Nanostructuration Optimization

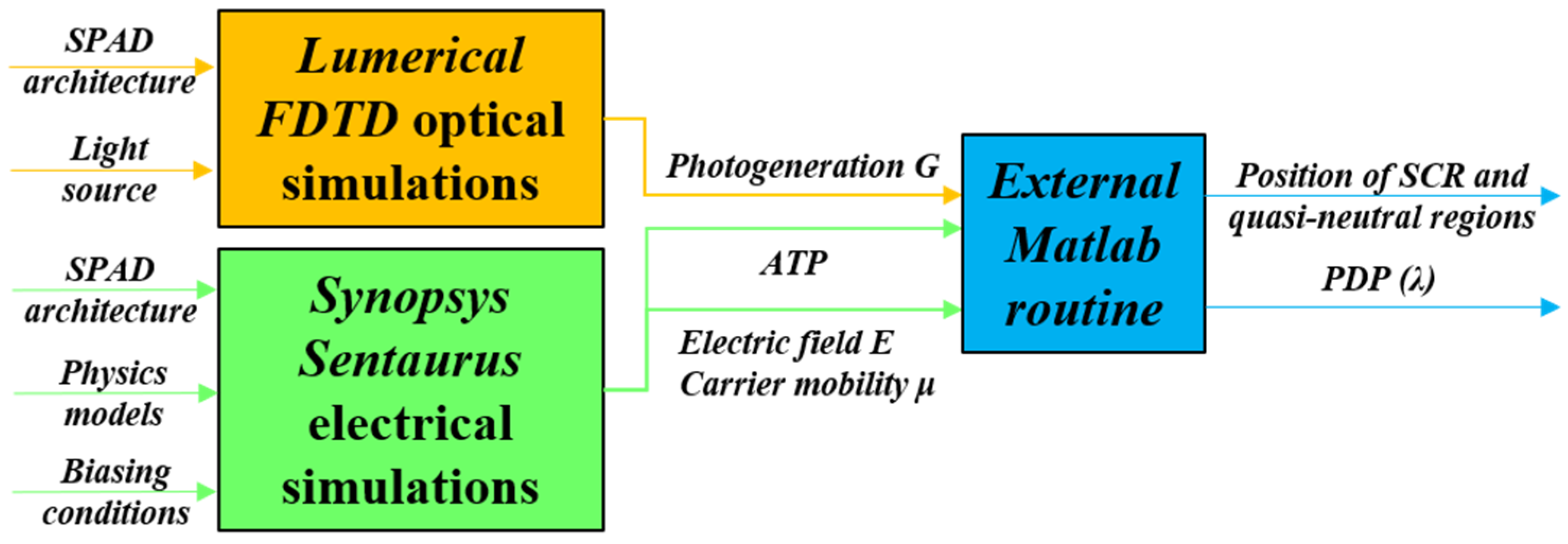

2.2.1. Simulation Framework and Assumption

- STI blocks have a depth defined by the technological process and must respect the process design rules in terms of width, length, and spacing.

- The FSI is adversely affected by the presence of Back-End-Of-Line (BEOL) layers, which are not optimized for optical light transmission (moreover, their optical properties are not fully characterized).

2.2.2. Optimization Methodology

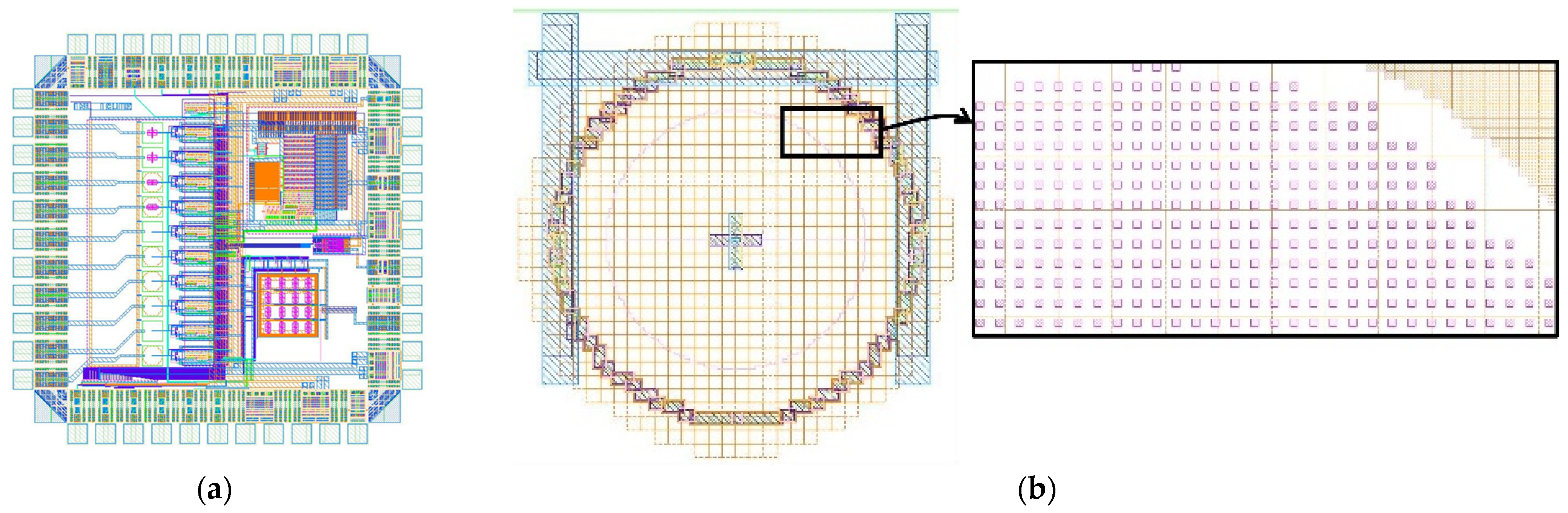

2.3. Test Chip Presentation

3. Results

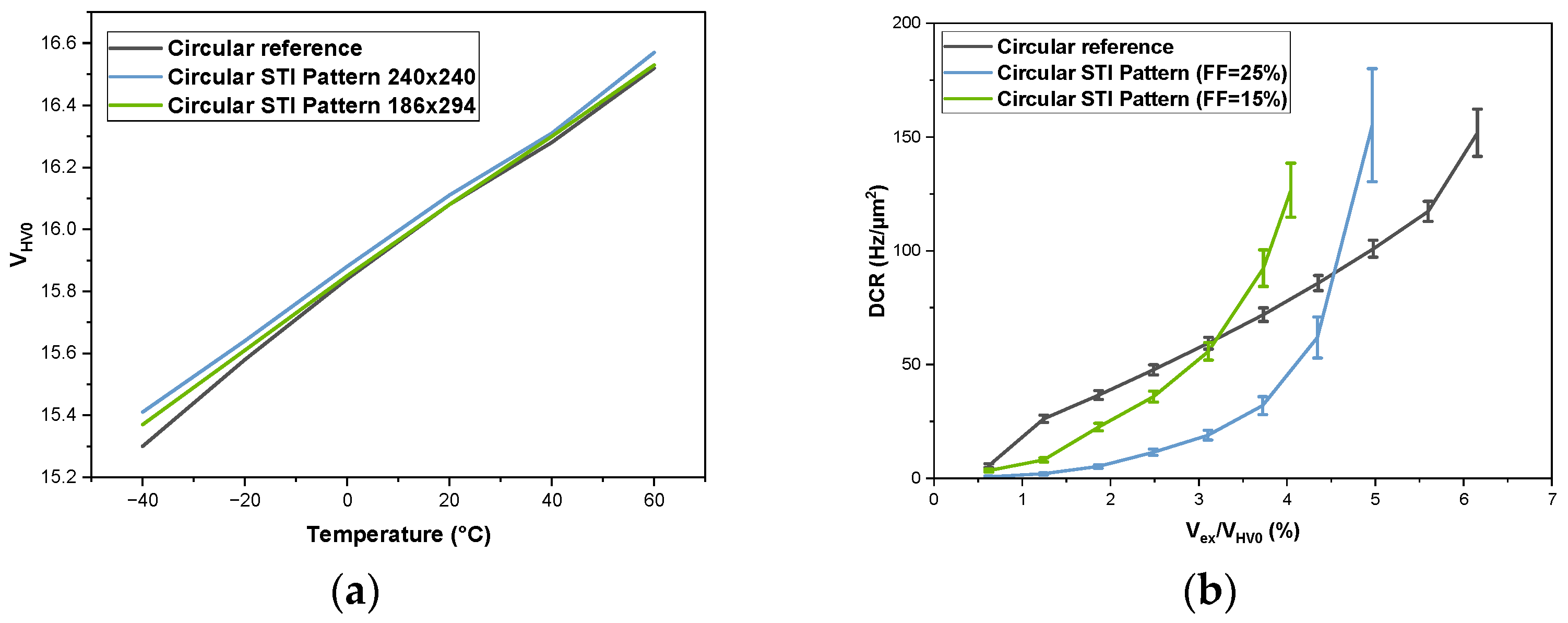

3.1. Dark Count Rate (DCR) Experimental Results

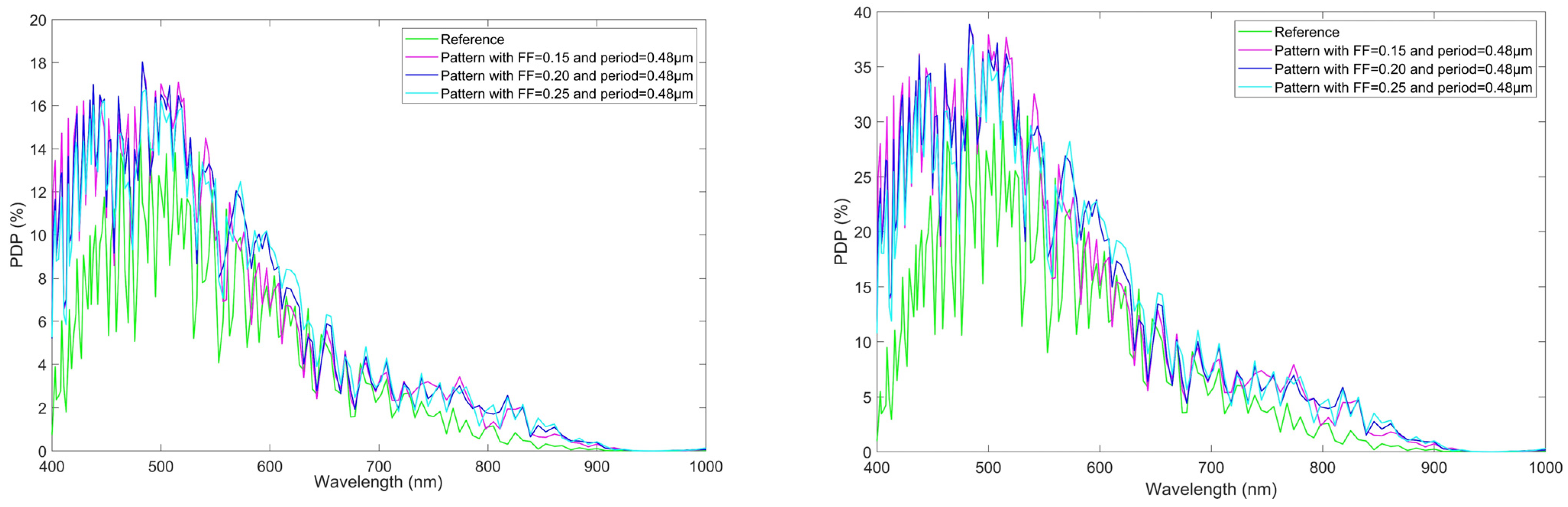

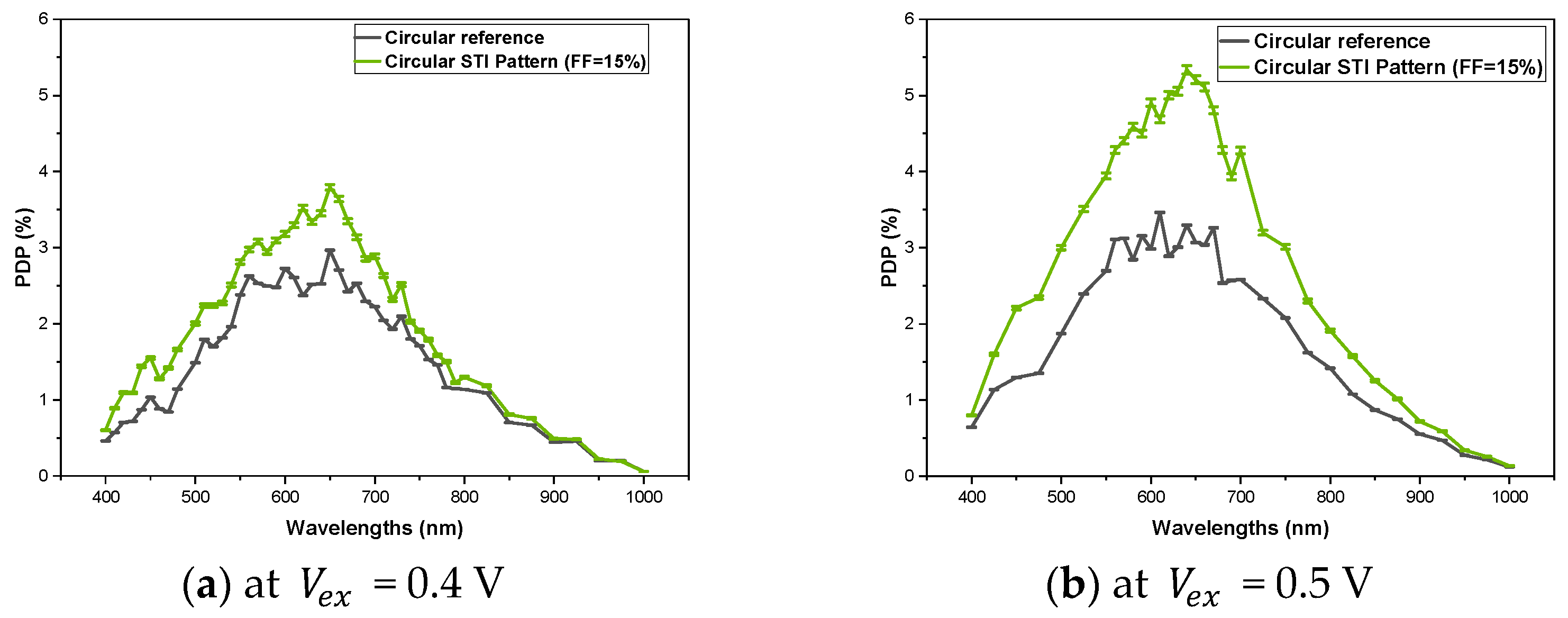

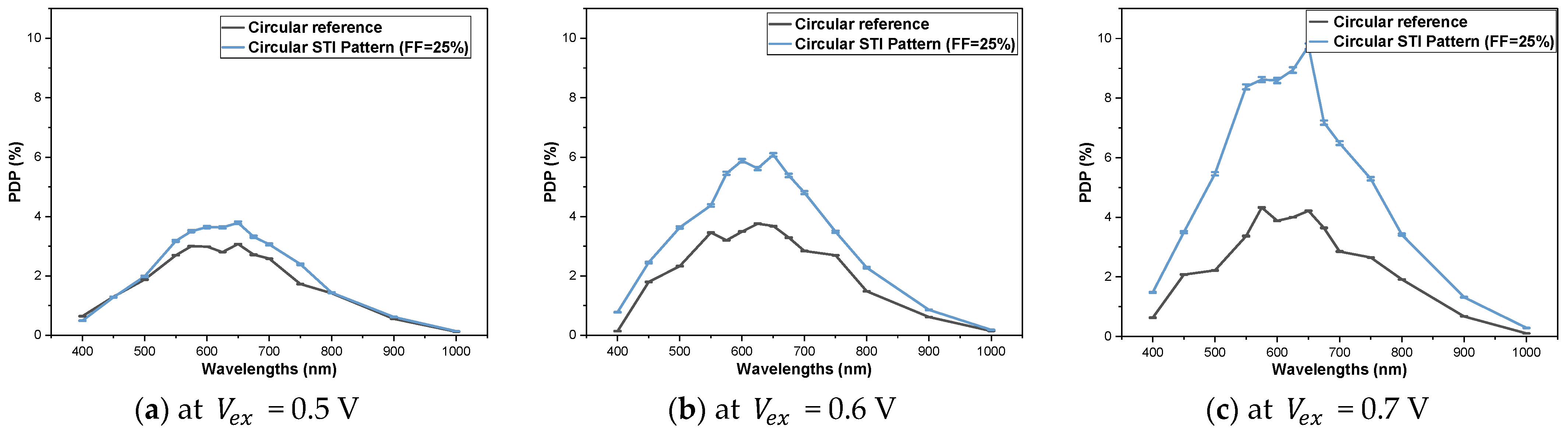

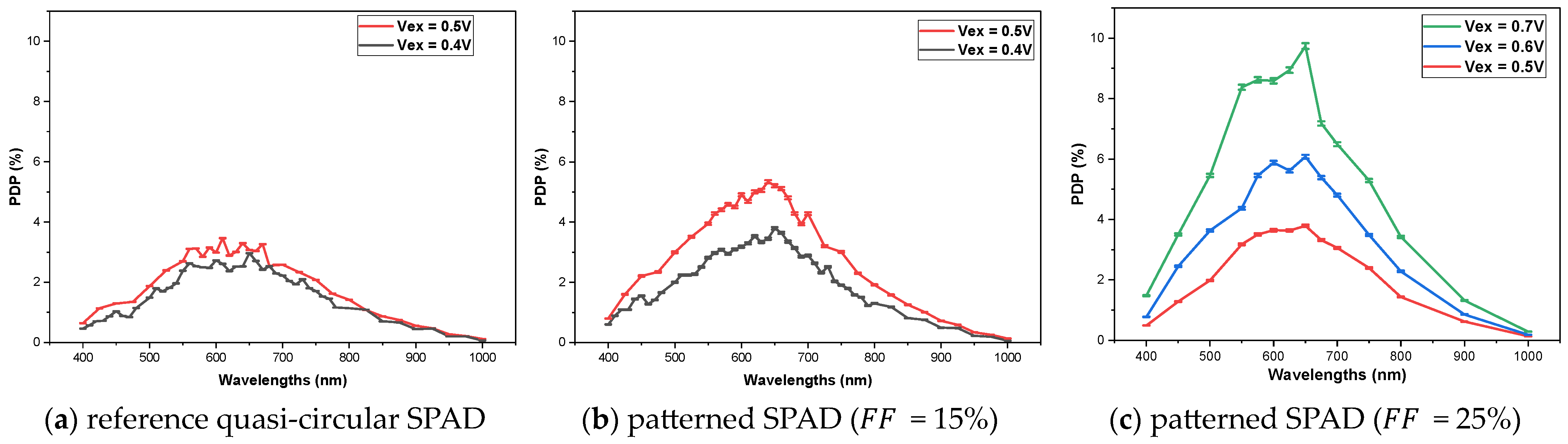

3.2. Photon Detection Efficiency (PDP) Experimental Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Gyongy, I.; Erdogan, A.T.; Dutton, N.A.; Martín, G.M.; Gorman, A.; Mai, H.; Della Rocca, F.M.; Henderson, R.K. A Direct Time-of-Flight Image Sensor with In-Pixel Surface Detection and Dynamic Vision. IEEE J. Sel. Top. Quantum Electron. 2023, 30, 3800111. [Google Scholar] [CrossRef]

- Pellegrini, S.; Buller, G.S.; Smith, J.M.; Wallace, A.M.; Cova, S. Laser-based distance measurement using picosecond resolution time-correlated single-photon counting. Meas. Sci. Technol. 2000, 11, 712–716. [Google Scholar] [CrossRef]

- Martin, F.; Mellot, P.; Caley, A.; Rae, B.; Campbell, C.; Hall, D.; Pellegrini, S. An all-in-one 64-zone SPAD-based Direct-Time-of-Flight Ranging Sensor with Embedded Illumination. In Proceedings of the 2021 IEEE Sensors, Sydney, Australia, 31 October–3 November 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Charbon, E. Single-photon imaging in complementary metal oxide semiconductor processes. Philos. Trans. R. Soc. A 2014, 372, 20130100. [Google Scholar] [CrossRef] [PubMed]

- Pancheri, L.; Ficorella, A.; Brogi, P.; Collazuol, G.; Betta, G.-F.D.; Marrocchesi, P.S.; Morsani, F.; Ratti, L.; Savoy-Navarro, A.; Sulaj, A. First Demonstration of a Two-Tier Pixelated Avalanche Sensor for Charged Particle Detection. IEEE J. Electron Devices Soc. 2017, 5, 404–410. [Google Scholar] [CrossRef]

- Henderson, R.K.; Johnston, N.; Della Rocca, F.M.; Chen, H.; Li, D.D.-U.; Hungerford, G.; Hirsch, R.; Mcloskey, D.; Yip, P.; Birch, D.J.S. A 192 × 128 Time Correlated SPAD Image Sensor in 40-nm CMOS Technology. IEEE J. Solid-State Circuits 2019, 54, 1907–1916. [Google Scholar] [CrossRef]

- Ma, J.; Chan, S.; Fossum, E.R. Review of Quanta Image Sensors for Ultralow-Light Imaging. IEEE Trans. Electron Devices 2022, 69, 2824–2839. [Google Scholar] [CrossRef]

- Shimada, S.; Otake, Y.; Yoshida, S.; Jibiki, Y.; Fujii, M.; Endo, S.; Nakamura, R.; Tsugawa, H.; Fujisaki, Y.; Yokochi, K.; et al. A SPAD Depth Sensor Robust against Ambient Light: The Importance of Pixel Scaling and Demonstration of a 2.5 μm Pixel with 21.8% PDE at 940 nm. In Proceedings of the 2022 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2022; pp. 37.3.1–37.3.4. [Google Scholar] [CrossRef]

- Morimoto, K.; Iwata, J.; Shinohara, M.; Sekine, H.; Abdelghafar, A.; Tsuchiya, H.; Kuroda, Y.; Tojima, K.; Endo, W.; Maehashi, Y.; et al. 3.2 Megapixel 3D-Stacked Charge Focusing SPAD for Low-Light Imaging and Depth Sensing. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 20.2.1–20.2.4. [Google Scholar] [CrossRef]

- Van Sieleghem, E.; Karve, G.; De Munck, K.; Vinci, A.; Cavaco, C.; Suss, A.; Van Hoof, C.; Lee, J. A Backside-Illuminated Charge-Focusing Silicon SPAD with Enhanced Near-Infrared Sensitivity. IEEE Trans. Electron Devices 2022, 69, 1129–1136. [Google Scholar] [CrossRef]

- Frey, L.; Marty, M.; Andre, S.; Moussy, N. Enhancing near-infrared photodetection efficiency in spad with silicon surface nanostructuration. IEEE J. Electron Devices Soc. 2018, 6, 392–395. [Google Scholar] [CrossRef]

- Vines, P.; Kuzmenko, K.; Kirdoda, J.; Dumas, D.C.S.; Mirza, M.M.; Millar, R.W.; Paul, D.J.; Buller, G.S. High performance planar germanium-on-silicon single-photon avalanche diode detectors. Nat. Commun. 2019, 10, 1086. [Google Scholar] [CrossRef] [PubMed]

- de Albuquerque, T.C.; Calmon, F.; Clerc, R.; Pittet, P.; Benhammou, Y.; Golanski, D.; Jouan, S.; Rideau, D.; Cathelin, A. Integration of SPAD in 28 nm FDSOI CMOS technology. In Proceedings of the 48th European Solid-State Device Research Conference (ESSDERC 2018), Dresden, Germany, 3–6 September 2018; pp. 82–85. [Google Scholar] [CrossRef]

- Lakeh, M.D.; Kammerer, J.-B.; Schell, J.-B.; Issartel, D.; Gao, S.; Cathelin, A.; Dartigues, A.; Calmon, F.; Uhring, W. Integration of an ultra-fast active quenching circuit with a monolithic 3D SPAD pixel in a 28 nm FD-SOI CMOS technology. Sens. Actuators A 2023, 363, 114744. [Google Scholar] [CrossRef]

- Issartel, D.; Gao, S.; Pittet, P.; Cellier, R.; Golanski, D.; Cathelin, A.; Calmon, F. Architecture optimization of SPAD integrated in 28 nm FD-SOI CMOS technology to reduce the DCR. Solid-State Electron. 2022, 191, 108297. [Google Scholar] [CrossRef]

- Gao, S.; Issartel, D.; Lakeh, M.D.; Mandorlo, F.; Orobtchouk, R.; Kammerer, J.-B.; Cathelin, A.; Golanski, D.; Uhring, W.; Calmon, F. Correlations between DCR and PDP of SPAD integrated in a 28 nm FD-SOI CMOS Technology. In Proceedings of the International Image Sensor Workshop (IISW), Crieff, UK, 21–25 May 2023. [Google Scholar] [CrossRef]

- Gao, S.; Issartel, D.; Orobtchouk, R.; Mandorlo, F.; Golanski, D.; Cathelin, A.; Calmon, F. 3D Electro-optical Simulations for Improving the Photon Detection Probability of SPAD Implemented in FD-SOI CMOS Technology. In Proceedings of the 2021 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Dallas, TX, USA, 27–29 September 2021; pp. 301–304. [Google Scholar] [CrossRef]

- Mandorlo, F.; Amara, M.; Nguyen, H.S.; Charlety-Meano, A.; Belarouci, A.; Orobtchouk, R. Color management of semi-transparent nano-patterned surfaces. Opt. Eng. 2021, 60, 055101. [Google Scholar] [CrossRef]

| Fill Factor | Relative Gain at Peak Sensitivity ~645 nm) | Average Relative Gain in the Range [400–1000 nm] |

|---|---|---|

| = 15% | 28% @ = 0.4 V | 33% @ = 0.4 V |

| 62% @ = 0.5 V | 55% @ = 0.5 V | |

| = 25% | 23% @ = 0.5 V | 12% @ = 0.5 V |

| 65% @ = 0.6 V | 53% @ = 0.6 V | |

| 131% @ = 0.7 V | 116% @ = 0.7 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, S.; Vu, D.-T.; Cazimajou, T.; Pittet, P.; Le Berre, M.; Dolatpoor Lakeh, M.; Mandorlo, F.; Orobtchouk, R.; Schell, J.-B.; Kammerer, J.-B.; et al. Shallow Trench Isolation Patterning to Improve Photon Detection Probability of Single-Photon Avalanche Diodes Integrated in FD-SOI CMOS Technology. Photonics 2024, 11, 526. https://doi.org/10.3390/photonics11060526

Gao S, Vu D-T, Cazimajou T, Pittet P, Le Berre M, Dolatpoor Lakeh M, Mandorlo F, Orobtchouk R, Schell J-B, Kammerer J-B, et al. Shallow Trench Isolation Patterning to Improve Photon Detection Probability of Single-Photon Avalanche Diodes Integrated in FD-SOI CMOS Technology. Photonics. 2024; 11(6):526. https://doi.org/10.3390/photonics11060526

Chicago/Turabian StyleGao, Shaochen, Duc-Tung Vu, Thibauld Cazimajou, Patrick Pittet, Martine Le Berre, Mohammadreza Dolatpoor Lakeh, Fabien Mandorlo, Régis Orobtchouk, Jean-Baptiste Schell, Jean-Baptiste Kammerer, and et al. 2024. "Shallow Trench Isolation Patterning to Improve Photon Detection Probability of Single-Photon Avalanche Diodes Integrated in FD-SOI CMOS Technology" Photonics 11, no. 6: 526. https://doi.org/10.3390/photonics11060526

APA StyleGao, S., Vu, D.-T., Cazimajou, T., Pittet, P., Le Berre, M., Dolatpoor Lakeh, M., Mandorlo, F., Orobtchouk, R., Schell, J.-B., Kammerer, J.-B., Cathelin, A., Golanski, D., Uhring, W., & Calmon, F. (2024). Shallow Trench Isolation Patterning to Improve Photon Detection Probability of Single-Photon Avalanche Diodes Integrated in FD-SOI CMOS Technology. Photonics, 11(6), 526. https://doi.org/10.3390/photonics11060526