4H-SiC MOSFET Threshold Voltage Instability Evaluated via Pulsed High-Temperature Reverse Bias and Negative Gate Bias Stresses

Abstract

:1. Introduction

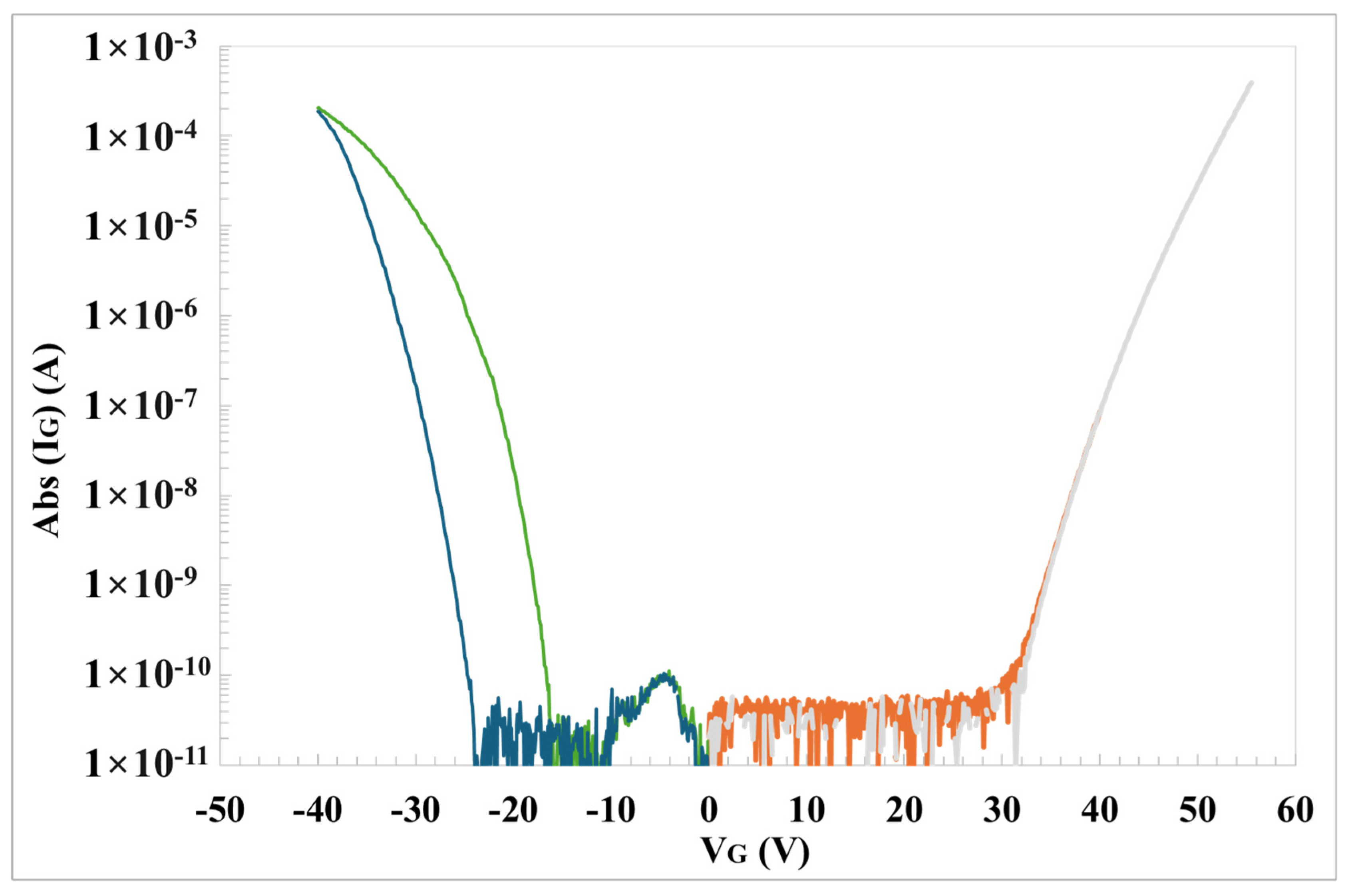

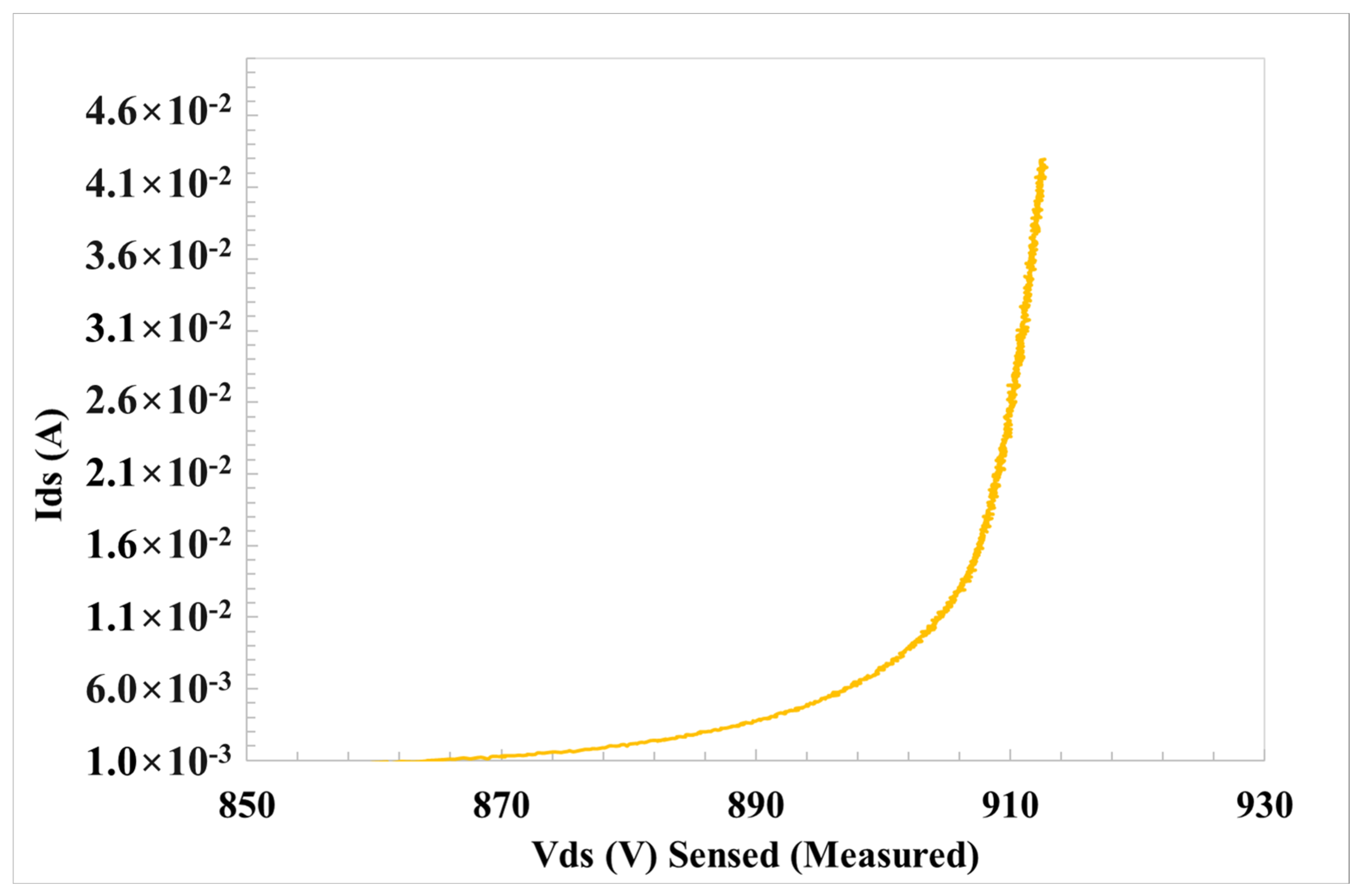

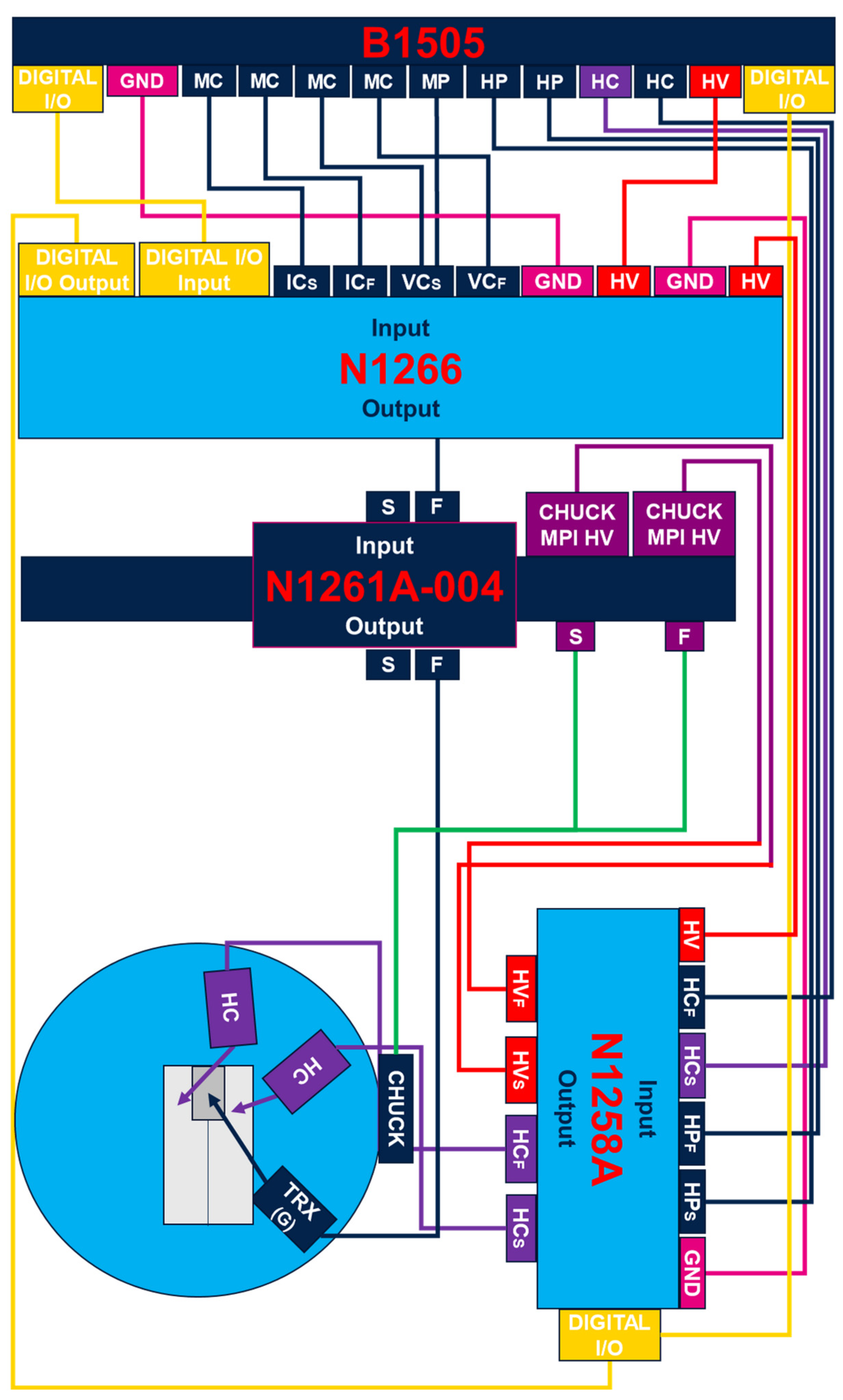

2. Materials and Methods

3. Device and Stress Procedure Description

4. Data/Results and Discussion

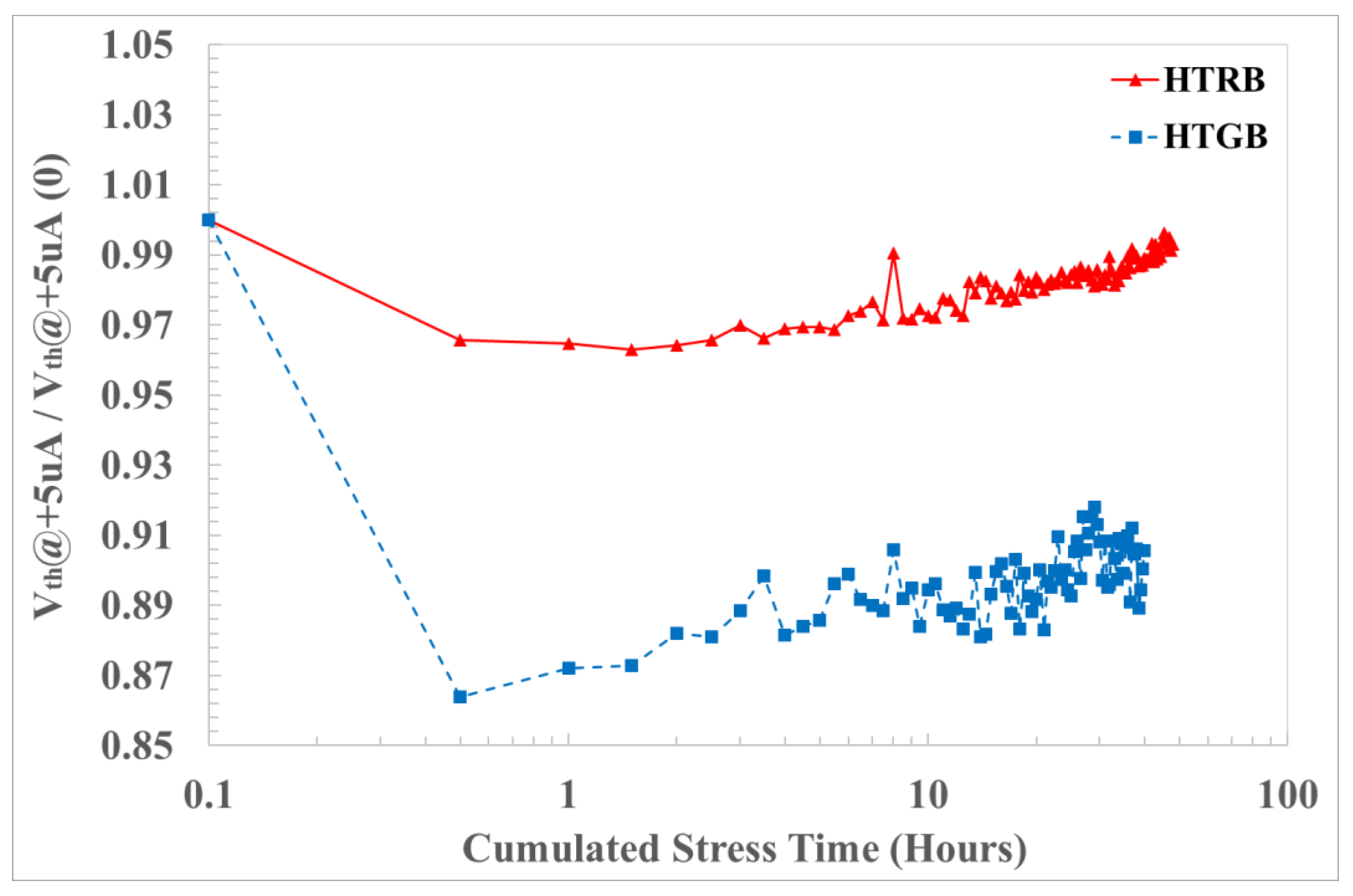

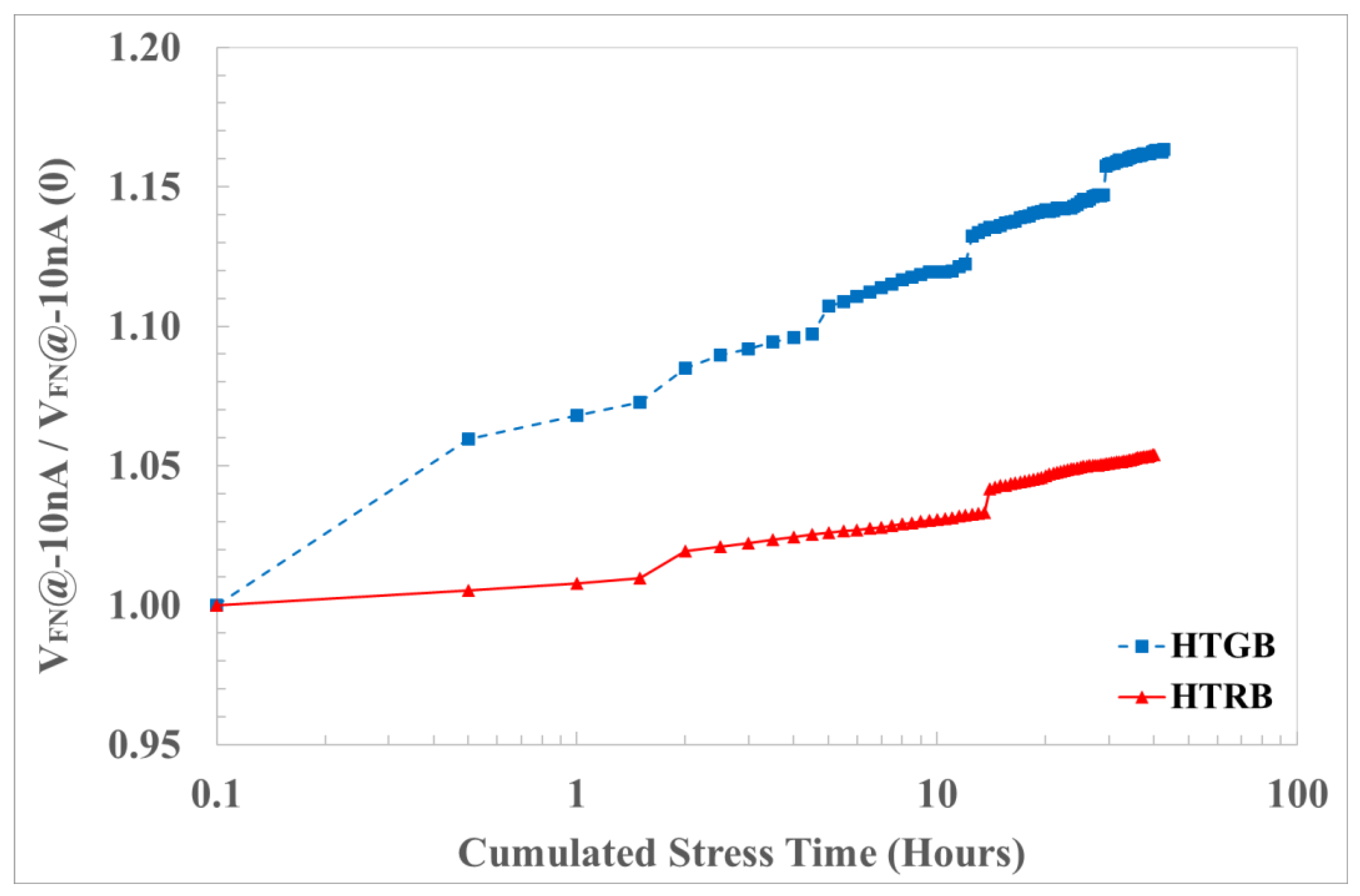

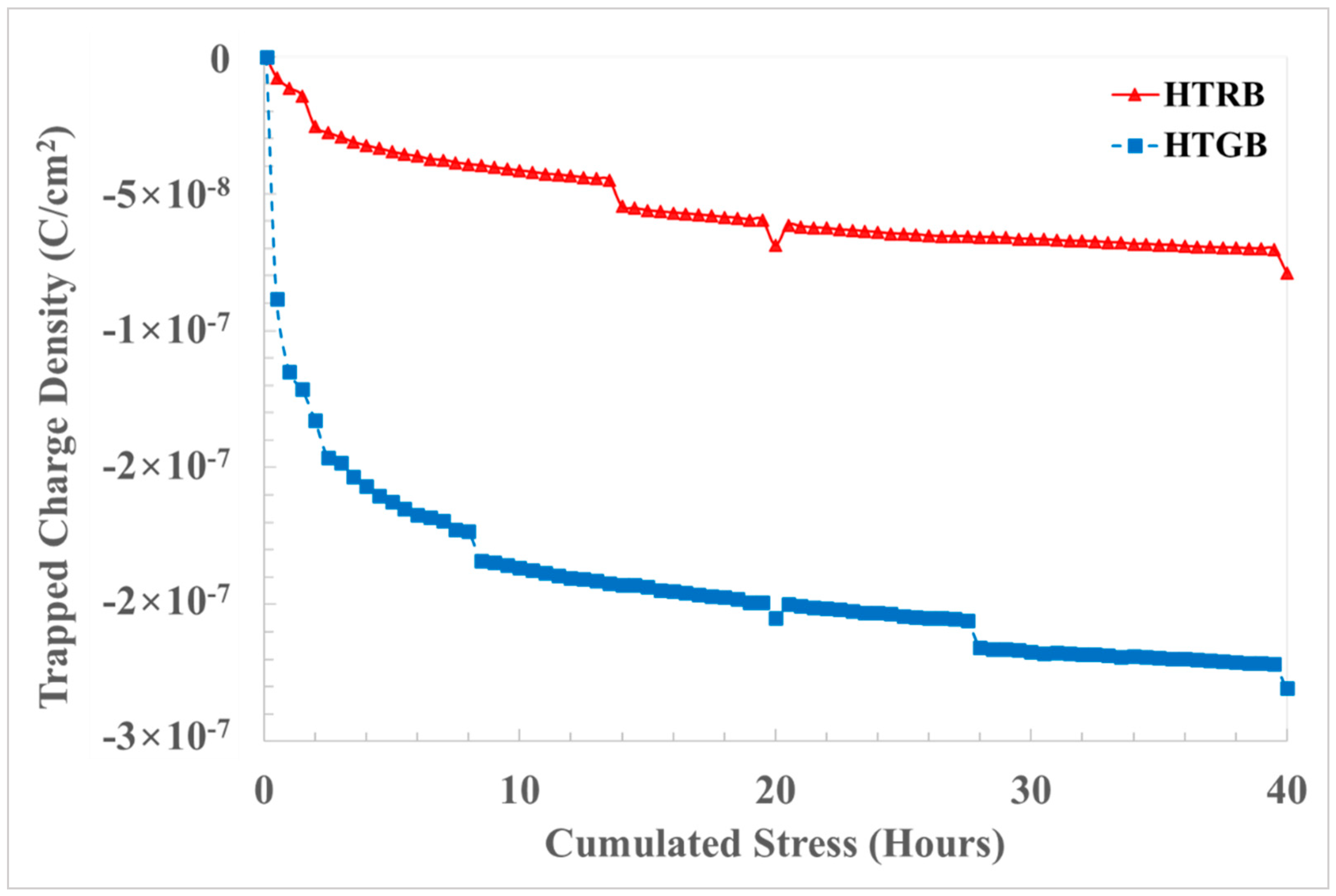

4.1. HTRB Test

4.2. HTGB Test

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; John Wiley Sons Singapore Pre. Ltd.: Singapore, 2014. [Google Scholar]

- Gil, B.; Keshavarz, M.; Wales, D.; Darzi, A.; Yeatman, E. Orthogonal Surface-Enhanced RamanScattering/Field-Effect Transistor Detectionof Breast and Colorectal Cancer-Derived Exosomesusing Graphene as a Tag-Free Diagnostic Template. Adv. NanoBiomed Res. 2023, 3, 2300055. [Google Scholar] [CrossRef]

- Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- Langpoklakpam, C.; Liu, A.-C.; Chu, K.-H.; Hsu, L.-H.; Lee, W.-C.; Chen, S.-C.; Sun, C.-W.; Shih, M.-H.; Lee, K.-Y.; Kuo, H.-C. Review of Silicon Carbide Processing for Power MOSFET. Crystals 2022, 12, 245. [Google Scholar] [CrossRef]

- Guo, X.; Xun, Q.; Li, Z.; Du, S.J.M. Silicon Carbide Converters and MEMS Devices for High-temperature Power Electronics: A Critical Review. Micromachines 2019, 10, 406. [Google Scholar] [CrossRef] [PubMed]

- Lichtenwalner, D.J.; Sabri, S.; van Brunt, E.; Hull, B.; Ryu, S.H.; Steinmann, P.; Romero, A.; Ganguly, S.; Gajewski, D.A.; Allen, S.; et al. Accelerated Testing of SiC Power Devices. In Proceedings of the 2020 IEEE International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 9–14 October 2022. [Google Scholar]

- Yang, L.; Castellazzi, A. High temperature gate-bias and reverse-bias tests on SiC MOSFETs. Microelectron. Reliab. 2013, 53, 1771–1773. [Google Scholar] [CrossRef]

- Yano, H.; Kanafuji, N.; Osawa, A.; Hatayama, T.; Fuyuki, T. Threshold voltage instability in 4H-SiC MOSFETs with phosphorus-doped and nitrided gate oxides. IEEE Trans. Electron. Dev. 2015, 62, 324. [Google Scholar] [CrossRef]

- Lelis, A.J.; Habersat, D.; Green, R.; Ogunniyi, A.; Gurfinkel, M.; Suehle, J.; Goldsman, N. Time dependence of bias-stress-induced SiC MOSFET threshold-voltage instability measurements. IEEE Trans. Electron. Dev. 2008, 55, 1835. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B.; El, M. Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs. IEEE Trans. Electron. Dev. 2015, 62, 316. [Google Scholar] [CrossRef]

- Cabello, M.; Soler, V.; Rius, G.; Montserrat, J.; Rebollo, J.P. Godignon; Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. Mater. Sci. Semicond. Process. 2018, 78, 22–31. [Google Scholar] [CrossRef]

- Singh, R. Reliability and performance limitations in SiC power devices. Microelectron. Reliab. 2006, 46, 713–730. [Google Scholar] [CrossRef]

- Van Brunt, E.; Lichtenwalner, D.J.; Park, J.H.; Ganguly, S.J.W. McPherson; Lifetime Modeling of the 4H-SiC MOS Interface in the HTRB Condition Under the Influence of Screw Dislocations. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023. [Google Scholar]

- Ganguly, S.; Lichtenwalner, D.J.; Isaacson, C.; Gajewski, D.A.; Steinmann, P.; Foarde, R.; Hull, B.; Ryu, S.-H.; Allen, S.; Palmour, J.W. Negative Gate Bias TDDB evaluation of n-Channel SiC Vertical Power MOSFETs. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS) 8B. 1-1-8B, Dallas, TX, USA, 27–31 March 2022; pp. 1–6. [Google Scholar]

- Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Moens, P.; Geenen, F.; De Schepper, L.; Cano, J.F.; Lettens, J.; Maslougkas, S.; Franchi, J.; Domeij, M. The Concept of Safe Operating Area for Gate Dielectrics: The SiC/SiO2 Case Study. In IEEE International Reliability Physics Symposium Proceedings; IEEE: Piscataway, NJ, USA, 2023. [Google Scholar]

- Masin, F.; De Santi, C.; Lettens, J.; Franchi, J.; Domeij, M.; Moens, P.; Zanoni, E. Non-monotonic threshold voltage variation in 4H-SiC MOSFET: Investigation and modeling. JAP 2021, 130, 7285. [Google Scholar] [CrossRef]

- Zhu, S.; Liu, T.; White, M.H.; Agarwal, A.K.; Salemi, A.; Sheridan, D. Investigation of gate leakage current behavior for commercial 1.2 kV 4H-SiC power mosfets. In Proceedings of the IRPS 2021, Monterey, CA, USA, 21–25 March 2021; pp. 1–7. [Google Scholar]

- Green, R.; Lelis, A.; Habersat, D. Threshold-voltage biastemperature instability in commercially-available SiC MOSFETs. Jpn. J. Appl. Phys. 2016, 55, 4. [Google Scholar] [CrossRef]

- Rescher, G.; Pobegen, G.; Grasser, T. Threshold voltage instabilities of present SiC-power MOSFETs under positive bias temperature stress. Mater. Sci. Forum. 2016, 858, 481–484. [Google Scholar] [CrossRef]

- Fiorenza, P.; Zignale, M.; Camalleri, M.; Scalia, L.; Zanetti, E.; Saggio, M.; Giannazzo, F.; Roccaforte, F. Impact of the NO annealing duration on the SiO2/4H–SiC interface properties in lateral MOSFETs: The energetic profile of the near-interface-oxide traps. Mater. Sci. Semicond. Process. 2024, 169, 107866. [Google Scholar] [CrossRef]

- El Hageali, S.A.; Guthrey, H.; Johnston, S.; Soto, J.; Odekirk, B.; Gorman, B.P. Mowafak Al-Jassim; Nondestructive microstructural investigation of defects in 4H-SiC epilayers using a multiscale luminescence analysis approach. J. Appl. Phys. 2022, 131, 185705. [Google Scholar] [CrossRef]

- Fiorenza, P.; La Magna, A.; Vivona, M.; Roccaforte, F. Near interface traps in SiO2/4H-SiC metal-oxide-semiconductor field effect transistors monitored by temperature dependent gate current transient measurements. Appl. Phys. Lett. 2016, 109, 012102. [Google Scholar] [CrossRef]

- Fiorenza, P.; Vivona, M.; Iucolano, F.; Severino, A.; Lorenti, S.; Nicotra, G.; Bongiorno, C.; Giannazzo, F.; Roccaforte, F. Temperature-dependent Fowler-Nordheim electron barrier height in SiO2/4H-SiC MOS capacitors. Mater. Sci. Semicond. Process. 2018, 78, 38–42. [Google Scholar] [CrossRef]

- Chanana, R.K.; McDonald, K.; Di Ventra, M.; Pantelides, S.T.; FeldmanG, L.C.; Chung, Y.; Tin, C.C.; Williams, J.R.; Weller, R.A. Fowler–Nordheim hole tunneling in p-SiC/SiO2 structures. Appl. Phys. Lett. 2000, 77, 2560–2562. [Google Scholar] [CrossRef]

- Fiorenza, P.; Cordiano, F.; Alessandrino, S.M.; Russo, A.; Zanetti, E.; Saggio, M.; Bongiorno, C.; Giannazzo, F.; Roccaforte, F. Consideration on the extrapolation of the low insulator field TDDB in 4H-SiC power MOSFETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Liu, T.; Zhu, S.; Yu, S.; Xing, D.; Salemi, A.; Kang, M.; Booth, K.; White, M.H.; Agarwal, A.K. Gate oxide reliability studies of commercial 1.2 kV 4H-SiC power MOSFETs. In Proceedings of the IRPS 2020, Dallas, TX, USA, 28 April–30 May 2020; pp. 1–5. [Google Scholar]

- Fayyaz, A.; Castellazzi, A. High temperature pulsed-gate robustness testing of SiC power MOSFETs. Microelectron. Reliab. 2015, 55, 1724–1728. [Google Scholar] [CrossRef]

- DiMaria, D.J.; Stasiak, J.W. Trap creation insilicon dioxide produced by hot electrons. J. Appl. Phys. 1989, 65, 2342. [Google Scholar] [CrossRef]

- Fiorenza, P.; Bongiorno, C.; Giannazzo, F.; Alessandrino, M.S.; Messina, A.; Saggio, M.; Roccaforte, F. Interfacial electrical and chemical properties of deposited SiO2 layers in lateral implanted 4H-SiC MOSFETs subjected to different nitridations. Appl. Surf. Sci. 2021, 557, 149752. [Google Scholar] [CrossRef]

| Vth (V) @ IDS = 5 µA VDS = 0.1 V | VFN+ (V) @ IGS = +10 nA | VFN- (V) @ IGS = −10 nA | BVDSS (V) @ IDS = 1 mA G & S Grounded | ||

|---|---|---|---|---|---|

| DEV33–WF1 | 0.523 | 33.42 | −17.30 | 879.11 | Parametric data Before HTRB stress |

| DEV36-WF1 | 0.510 | 33.58 | −17.78 | 881.43 | |

| DEV19-WF2 | 0.814 | 36.00 | −18.59 | 853.08 | |

| DEV20-WF2 | 0.842 | 35.82 | −18.14 | 853.34 | |

| DEV33–WF1 | 0.989 | 1.01 | 1.07 | 1.00 | Drift analysis After HTRB stress |

| DEV36-WF1 | 0.950 | 1.01 | 1.05 | 1.00 | |

| DEV19-WF2 | 1.014 | 1.01 | 1.06 | 1.00 | |

| DEV20-WF2 | 1.010 | 1.01 | 1.07 | 1.00 |

| Vth (V) @ IDS = 5 µA VDS = 0.1 V | VFN+ (V) @ IGS = +10 nA | VFN- (V) @ IGS = −10 nA | BVDSS (V) @ IDS = 1 mA G & S Grounded | ||

|---|---|---|---|---|---|

| DEV34–WF1 | 0.45 | 33.68 | −17.59 | 879.82 | Parametric data Before HTGB stress |

| DEV37-WF1 | 0.51 | 32.98 | −17.38 | 878.16 | |

| DEV21-WF2 | 0.89 | 36.21 | −18.41 | 840.66 | |

| DEV22-WF2 | 0.82 | 35.46 | −18.55 | 844.32 | |

| DEV34–WF1 | 0.96 | 1.01 | 1.16 | 1.01 | Drift analysis After HTGB stress |

| DEV37-WF1 | 0.91 | 1.01 | 1.15 | 1.01 | |

| DEV21-WF2 | 0.99 | 1.01 | 1.11 | 1.01 | |

| DEV22-WF2 | 1.00 | 1.01 | 1.10 | 1.01 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Anoldo, L.; Zanetti, E.; Coco, W.; Russo, A.; Fiorenza, P.; Roccaforte, F. 4H-SiC MOSFET Threshold Voltage Instability Evaluated via Pulsed High-Temperature Reverse Bias and Negative Gate Bias Stresses. Materials 2024, 17, 1908. https://doi.org/10.3390/ma17081908

Anoldo L, Zanetti E, Coco W, Russo A, Fiorenza P, Roccaforte F. 4H-SiC MOSFET Threshold Voltage Instability Evaluated via Pulsed High-Temperature Reverse Bias and Negative Gate Bias Stresses. Materials. 2024; 17(8):1908. https://doi.org/10.3390/ma17081908

Chicago/Turabian StyleAnoldo, Laura, Edoardo Zanetti, Walter Coco, Alfio Russo, Patrick Fiorenza, and Fabrizio Roccaforte. 2024. "4H-SiC MOSFET Threshold Voltage Instability Evaluated via Pulsed High-Temperature Reverse Bias and Negative Gate Bias Stresses" Materials 17, no. 8: 1908. https://doi.org/10.3390/ma17081908