T-Channel Field Effect Transistor with Three Input Terminals (Ti-TcFET)

Abstract

:1. Introduction

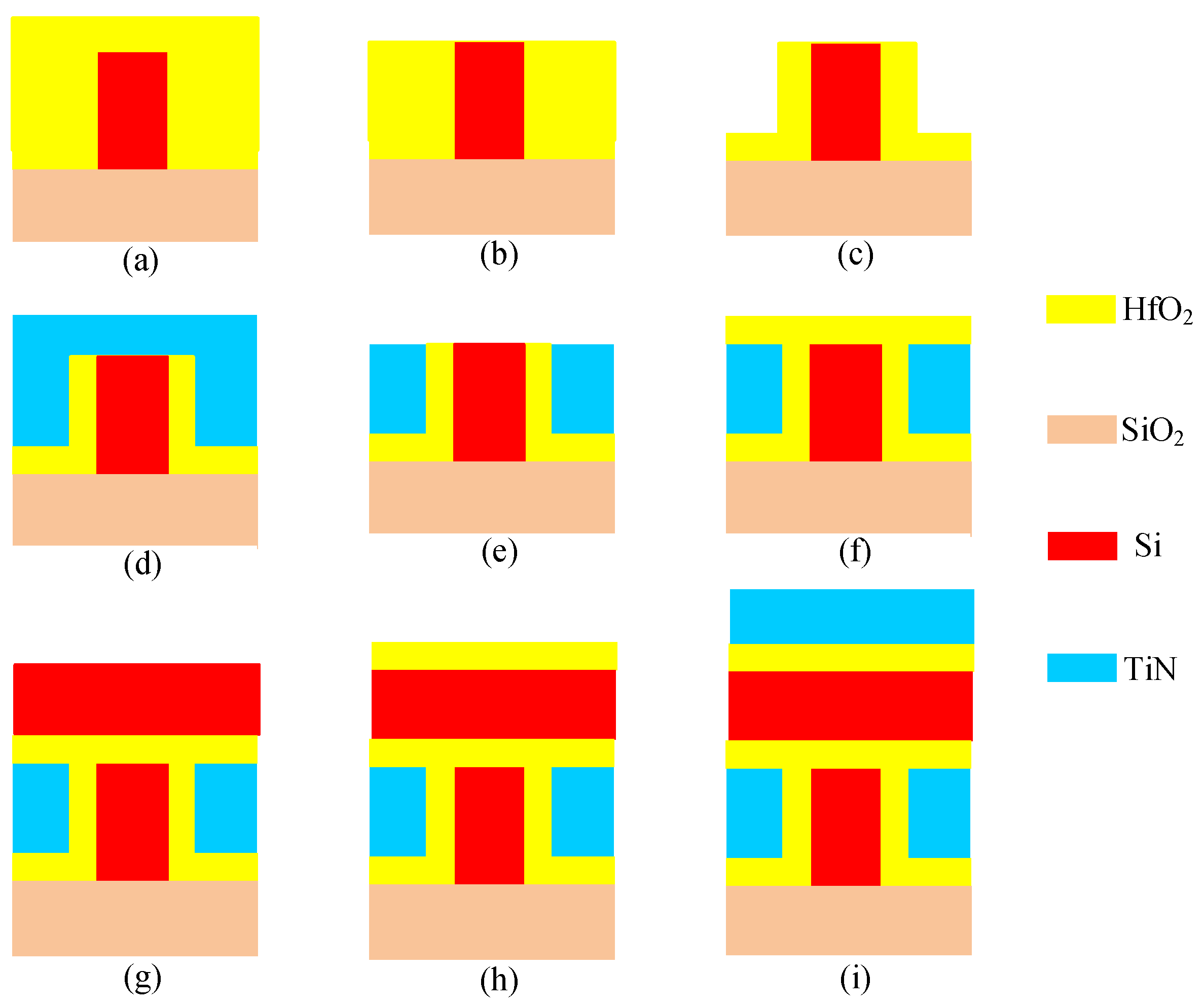

2. Device Structure and Description

2.1. The Structure of the Ti-TcFET

2.2. Key Processing Steps for the Ti-TcFET Device

3. Results and Discussion

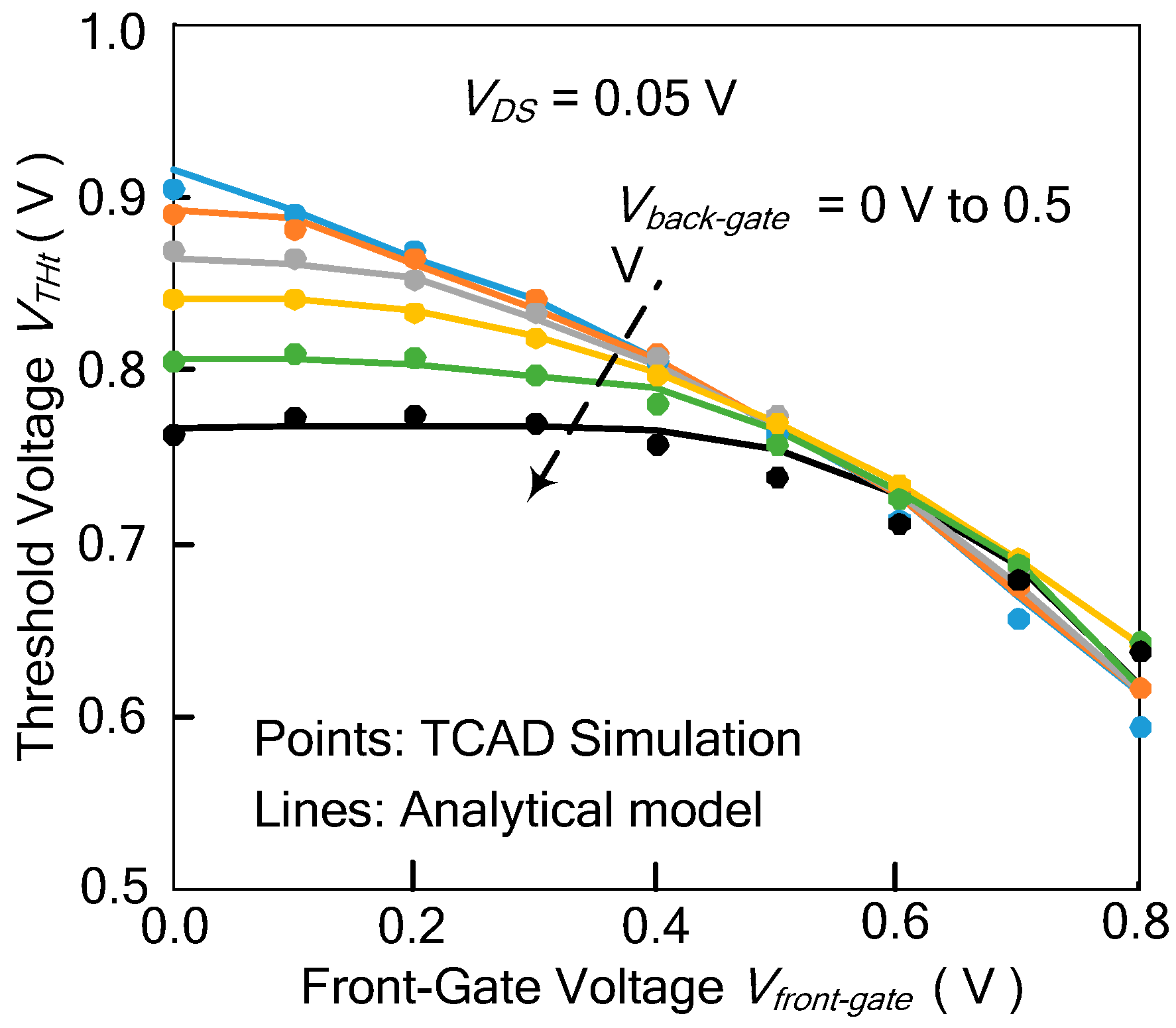

3.1. The Threshold Voltage of Ti-TcFET Devices

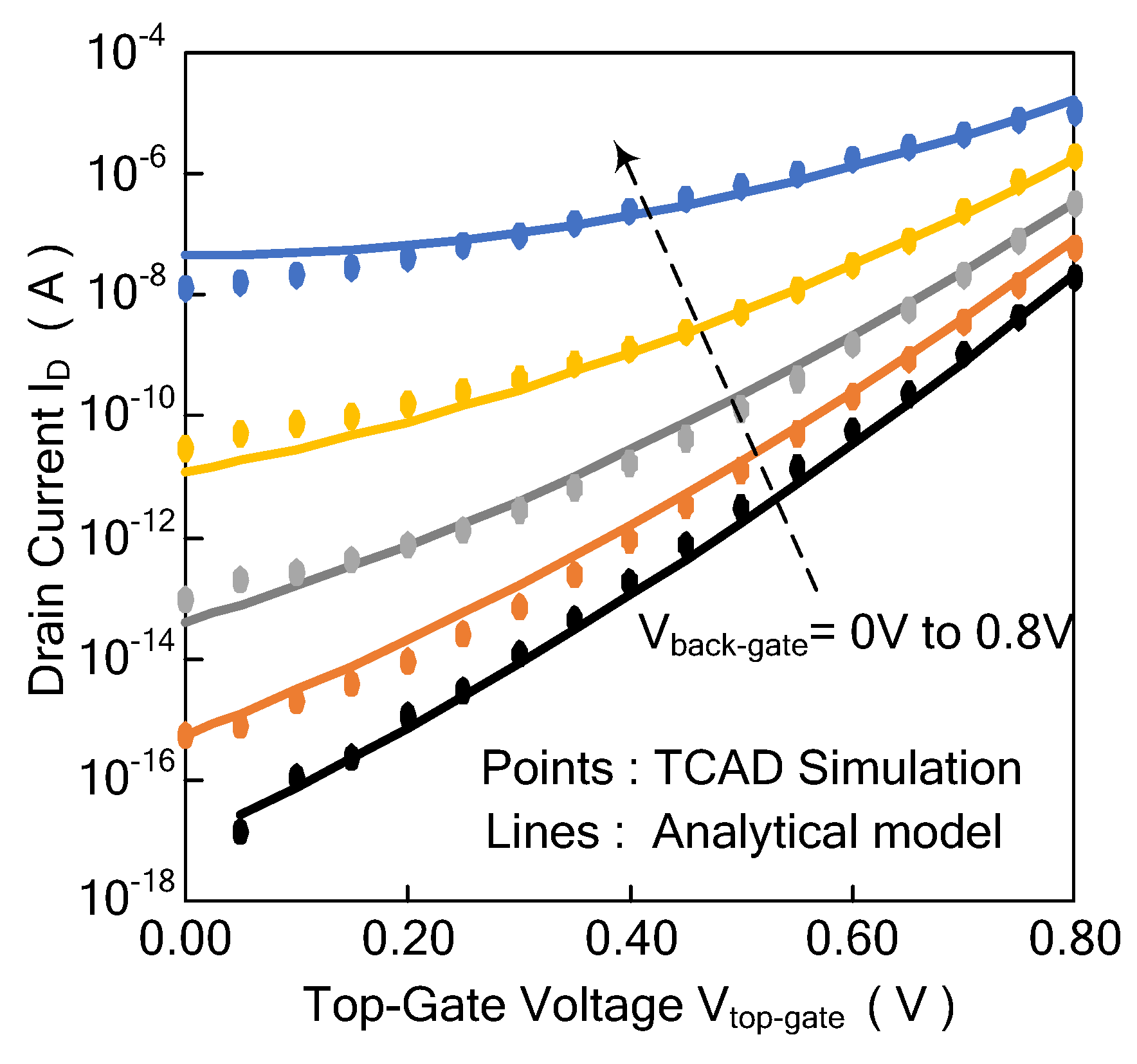

3.2. Drain Current of the Ti-TcFET

3.3. Subthreshold Current of the Ti-TcFET

3.4. Performance Optimization of the Ti-TcFET Devices

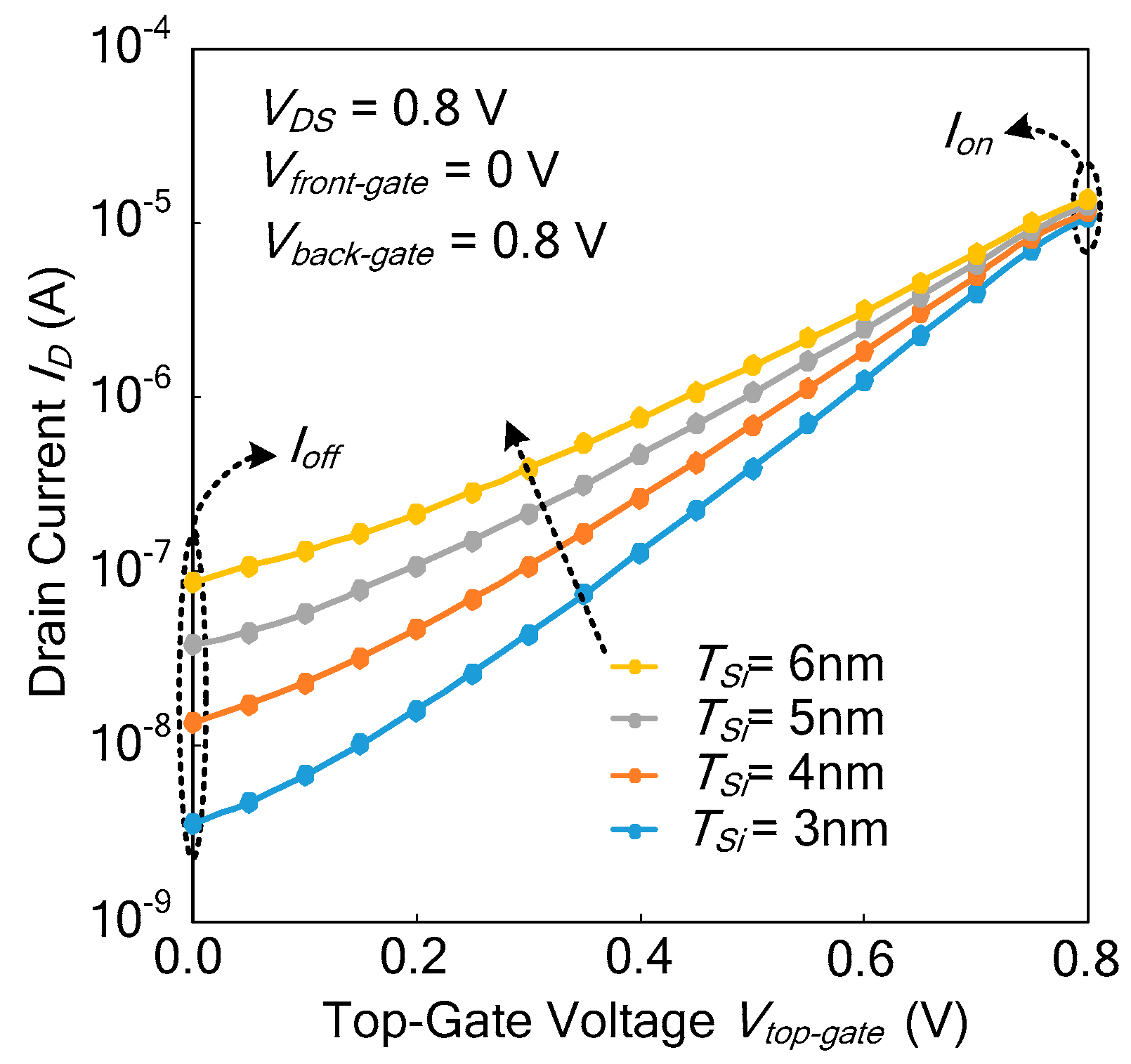

3.4.1. Effect of Channel Thickness on Current Characteristics

3.4.2. Effect of Gate Oxide Thickness on Current Characteristics

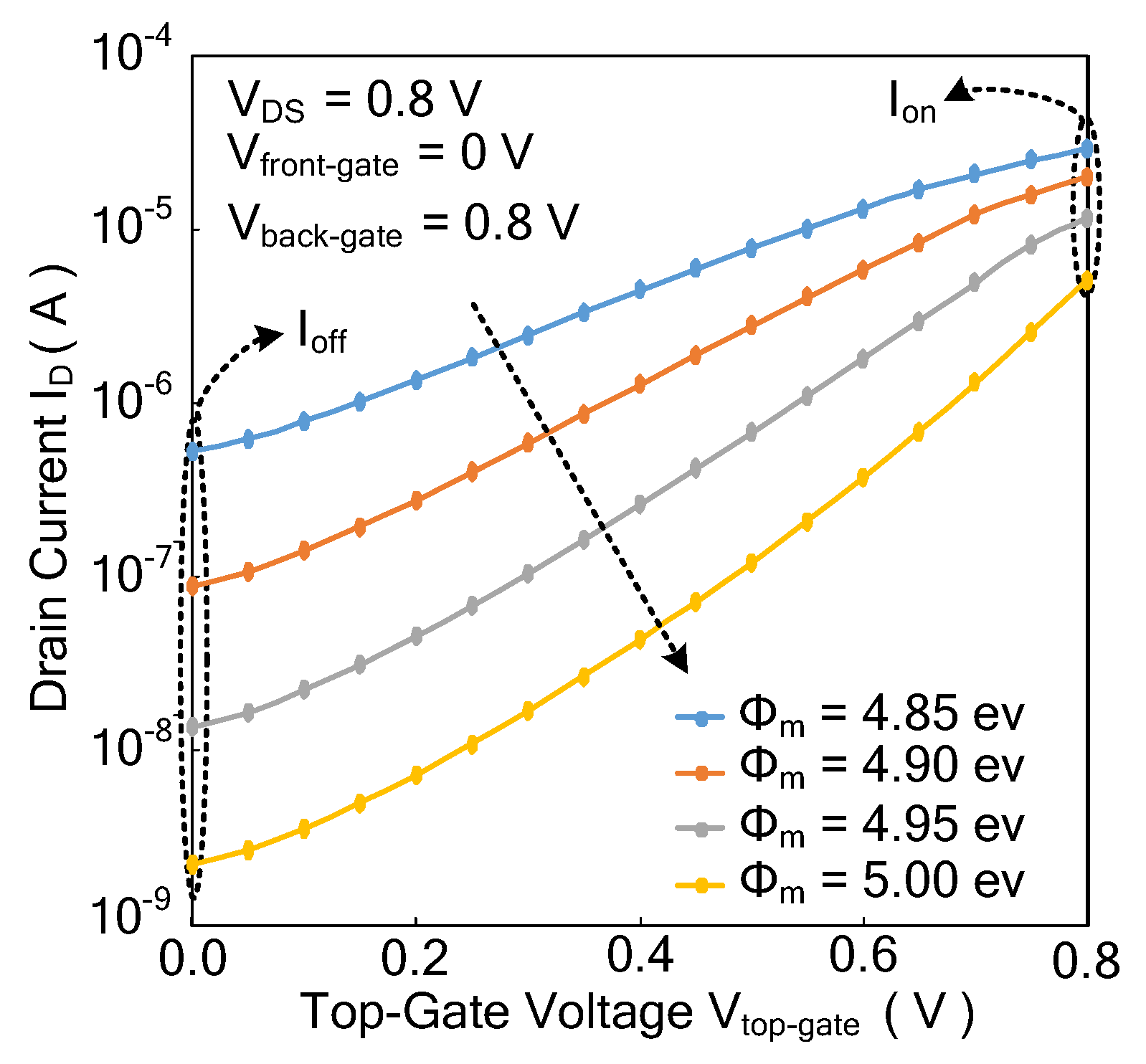

3.4.3. Effect of Gate Work Function on Current Characteristics

3.5. Drain-Induced Barrier Lowering (DIBL) and S of the Optimized Ti-TcFET Devices

3.6. Scaling Factors of the Ti-TcFET Devices

3.7. Performance Analysis of the Ti-TcFET Devices

3.8. Logic Cells Based on Ti-TcFET Devices

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Colinge, J.P.; Gao, M.H.; Romano-Rodriguez, A.; Maes, H.; Claeys, C. Silicon-on-insulator’gate-all-around device’. In Proceedings of the 1990 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 9–12 December 1990; pp. 595–598. [Google Scholar]

- Kavalieros, J.; Doyle, B.; Datta, S.; Dewey, G.; Doczy, M.; Jin, B.; Lionberger, D.; Metz, M.; Rachmady, W.; Radosavljevic, M.; et al. Tri-gate transistor architecture with high-k gate dielectrics, metal gates and strain engineering. In Proceedings of the 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers, Honolulu, HI, USA, 13–15 June 2006; pp. 50–51. [Google Scholar]

- Yang, F.L.; Chen, H.Y.; Chen, F.C.; Huang, C.C.; Chang, C.Y.; Chiu, H.K.; Lee, C.C.; Chen, C.C.; Huang, H.T.; Chen, C.J.; et al. 25 nm CMOS omega FETs. In Proceedings of the 2002 International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; pp. 255–258. [Google Scholar]

- Liu, C.; Zheng, F.; Sun, Y.; Li, X.; Shi, Y. Highly flexible SRAM cells based on novel tri-independent-gate FinFET. Superlattices Microstruct. 2017, 110, 330–338. [Google Scholar] [CrossRef]

- Liu, C.; Zheng, F.; Sun, Y.; Li, X.; Shi, Y. Novel tri-independent-gate FinFET for multi-current modes control. Superlattices Microstruct. 2017, 109, 374–381. [Google Scholar] [CrossRef]

- Datta, A.; Goel, A.; Cakici, R.T.; Mahmoodi, H.; Lekshmanan, D.; Roy, K. Modeling and circuit synthesis for independently controlled double gate FinFET devices. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2007, 26, 1957–1966. [Google Scholar] [CrossRef]

- Tawfik, S.A.; Kursun, V. Low-power and compact sequential circuits with independent-gate FinFETs. IEEE Trans. Electron Devices 2007, 55, 60–70. [Google Scholar] [CrossRef]

- Gupta, S.K.; Kulkarni, J.P.; Roy, K. Tri-mode independent gate FinFET-based SRAM with pass-gate feedback: Technology–circuit co-design for enhanced cell stability. IEEE Trans. Electron Devices 2013, 60, 3696–3704. [Google Scholar] [CrossRef]

- Zhang, X.; Hu, J.; Luo, X. Optimization of dual-threshold independent-gate FinFETs for compact low power logic circuits. In Proceedings of the 2016 IEEE 16th International Conference on Nanotechnology (IEEE-NANO), Sendai, Japan, 22–25 August 2016; pp. 529–532. [Google Scholar]

- Ni, H.; Hu, J.; Yang, H.; Zhu, H. Comprehensive Optimization of Dual Threshold Independent-Gate FinFET and SRAM Cells. Act. Passive Electron. Compon. 2018, 2018, 1–10. [Google Scholar] [CrossRef]

- Fried, D.M.; Duster, J.S.; Kornegay, K.T. Improved independent gate N-type FinFET fabrication and characterization. IEEE Electron Device Lett. 2003, 24, 592–594. [Google Scholar] [CrossRef]

- ATLAS User’s Manual Volume I. Silvaco International. Available online: https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silen-manuals&nm=atlas (accessed on 30 August 2016).

- Amaru, L.; Gaillardon, P.E.; De Micheli, G. Majority-inverter graph: A new paradigm for logic optimization. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2015, 35, 806–819. [Google Scholar] [CrossRef] [Green Version]

- Amarú, L.; Gaillardon, P.E.; De Micheli, G. Majority-inverter graph: A novel data-structure and algorithms for efficient logic optimization. In Proceedings of the 51st Annual Design Automation Conference, San Francisco, CA, USA, 1 June 2014; pp. 1–6. [Google Scholar]

- Han, J.W.; Kim, C.J.; Choi, Y.K. Universal potential model in tied and separated double-gate MOSFETs with consideration of symmetric and asymmetric structure. IEEE Trans. Electron Devices 2008, 55, 1472–1479. [Google Scholar] [CrossRef]

- Ghai, D.; Mohanty, S.P.; Thakral, G. Comparative analysis of double gate FinFET configurations for analog circuit design. In Proceedings of the 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 4 August 2013; pp. 809–812. [Google Scholar]

- Granzner, R.; Schwierz, F.; Polyakov, V.M. An analytical model for the threshold voltage shift caused by two-dimensional quantum confinement in undoped multiple-gate MOSFETs. IEEE Trans. Electron Devices 2007, 54, 2562–2565. [Google Scholar] [CrossRef]

- Fossum, J.G. Physical insights on nanoscale multi-gate CMOS design. Solid-State Electron. 2007, 51, 188–194. [Google Scholar] [CrossRef]

- Hu, C. Low-voltage CMOS device scaling. In Proceedings of the IEEE International Solid-State Circuits Conference-ISSCC’94, San Francisco, CA, USA, 16 February 1994; pp. 86–87. [Google Scholar]

- Lin, X.; Wang, Y.; Pedram, M. Stack sizing analysis and optimization for FinFET logic cells and circuits operating in the sub/near-threshold regime. In Proceedings of the Fifteenth International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 3 March 2014; pp. 341–348. [Google Scholar]

- Harris, D.M.; Keller, B.; Karl, J.; Keller, S. A transregional model for near-threshold circuits with application to minimum-energy operation. In Proceedings of the 2010 International Conference on Microelectronics, Cairo, Egypt, 19 December 2010; pp. 64–67. [Google Scholar]

- Rostami, M.; Mohanram, K. Dual-Vth independent-gate FinFETs for low power logic circuits. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2011, 30, 337–349. [Google Scholar] [CrossRef]

- Masahara, M.; Surdeanu, R.; Witters, L.; Doornbos, G.; Nguyen, V.H.; Vrancken, C.; Jurczak, M.; Biesemans, S. Experimental investigation of optimum gate workfunction for CMOS four-terminal multigate MOSFETs (MUGFETs). IEEE Trans. Electron Devices 2007, 54, 1431–1437. [Google Scholar] [CrossRef]

- McGuire, F.A.; Lin, Y.C.; Price, K.; Rayner, G.B.; Khandelwal, S.; Salahuddin, S.; Franklin, A.D. Sustained sub-60 mV/decade switching via the negative capacitance effect in MoS2 transistors. Nano Lett. 2017, 17, 4801–4806. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef] [PubMed]

- Chu, Z.; Tang, X.; Soeken, M.; Petkovska, A.; Zgheib, G.; Amarù, L.; Xia, Y.; Ienne, P.; De Micheli, G.; Gaillardon, P.E. Improving circuit mapping performance through mig-based synthesis for carry chains. In Proceedings of the on Great Lakes Symposium on VLSI 2017, New York, NY, USA, 10 May 2017; pp. 131–136. [Google Scholar]

- Navi, K.; Moaiyeri, M.H.; Mirzaee, R.F.; Hashemipour, O.; Nezhad, B.M. Two new low-power full adders based on majority-not gates. Microelectron. J. 2009, 40, 126–130. [Google Scholar] [CrossRef]

| Parameter | Optimized Value | Parameter | Optimized Value |

|---|---|---|---|

| Gate dielectric thickness (Tox) | 3 nm | Drain doping (Ndrain) | 2 × 1020 cm−3 |

| Channel thickness 1 (TSi1) | 4 nm | Source doping (Nsource) | 2 × 1020 cm−3 |

| Channel thickness 2 (TSi2) | 4 nm | Channel doping (Nchannel) | 1 × 1016 cm−3 |

| Fin height 1 (HFin1) | 40 nm | Gate work function (Φm) | 4.52 eV (P-type) |

| Fin height 2 (HFin2) | 84 nm | 4.95 eV (N-type) | |

| Gate length (Lg) | 24 nm | - | - |

| State | Vtop-gate, Vfront-gate, Vback-gate | ID (A) | Normalized |

|---|---|---|---|

| Turn-off mode 1 | 0.8 V, 0 V, 0 V | 2.06 × 10−8 | 0.0005 |

| Turn-off mode 2 | 0 V, 0.8 V, 0 V | 1.40 × 10−8 | 0.0004 |

| Turn-off mode 3 | 0 V, 0 V, 0.8 V | 1.40 × 10−8 | 0.0004 |

| Turn-off mode 4 | 0 V, 0 V, 0 V | 1.47 × 10−17 | 3.81 × 10−13 |

| Turn-on mode 1 | 0 V, 0.8 V, 0.8 V | 1.17 × 10−5 | 0.3031 |

| Turn-on mode 2 | 0.8 V, 0 V, 0.8 V | 1.17 × 10−5 | 0.3031 |

| Turn-on mode 3 | 0.8 V, 0.8 V, 0 V | 1.14 × 10−5 | 0.2953 |

| Turn-on mode 4 | 0.8 V, 0.8 V, 0.8 V | 3.86 × 10−5 | 1.0000 |

| State | Vtop-gate, Vfront-gate, Vback-gate | ID (A) | Normalized |

|---|---|---|---|

| Turn-off mode 1 | 0 V, 0.8 V, 0.8 V | 1.57 × 10−8 | 0.0007 |

| Turn-off mode 2 | 0.8 V, 0 V, 0.8 V | 1.06 × 10−8 | 0.0004 |

| Turn-off mode 3 | 0.8 V, 0.8 V, 0 V | 1.06 × 10−8 | 0.0004 |

| Turn-off mode 4 | 0.8 V, 0.8 V, 0.8 V | 2.75 × 10−17 | 1.15 × 10−12 |

| Turn-on mode 1 | 0.8 V, 0 V, 0 V | 7.48 × 10−6 | 0.3116 |

| Turn-on mode 2 | 0 V, 0.8 V, 0 V | 7.09 × 10−6 | 0.2954 |

| Turn-on mode 3 | 0 V, 0 V, 0.8 V | 7.09 × 10−6 | 0.2954 |

| Turn-on mode 4 | 0 V, 0 V, 0 V | 2.40 × 10−6 | 1.0000 |

| Full Adder | Power Consumption (nW) | Delay (pS) | Power Delay Product (zJ) |

|---|---|---|---|

| FinFET | 19.29 | 44.38 | 856 |

| Ti-TcFET | 9.26 | 59.59 | 554 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Z.; Hu, J.; Ye, H.; Chu, Z. T-Channel Field Effect Transistor with Three Input Terminals (Ti-TcFET). Micromachines 2020, 11, 64. https://doi.org/10.3390/mi11010064

Chen Z, Hu J, Ye H, Chu Z. T-Channel Field Effect Transistor with Three Input Terminals (Ti-TcFET). Micromachines. 2020; 11(1):64. https://doi.org/10.3390/mi11010064

Chicago/Turabian StyleChen, Zeqi, Jianping Hu, Hao Ye, and Zhufei Chu. 2020. "T-Channel Field Effect Transistor with Three Input Terminals (Ti-TcFET)" Micromachines 11, no. 1: 64. https://doi.org/10.3390/mi11010064