Interaction of Negative Bias Instability and Self-Heating Effect on Threshold Voltage and SRAM (Static Random-Access Memory) Stability of Nanosheet Field-Effect Transistors

Abstract

:1. Introduction

2. Device Structure and Simulation Setup

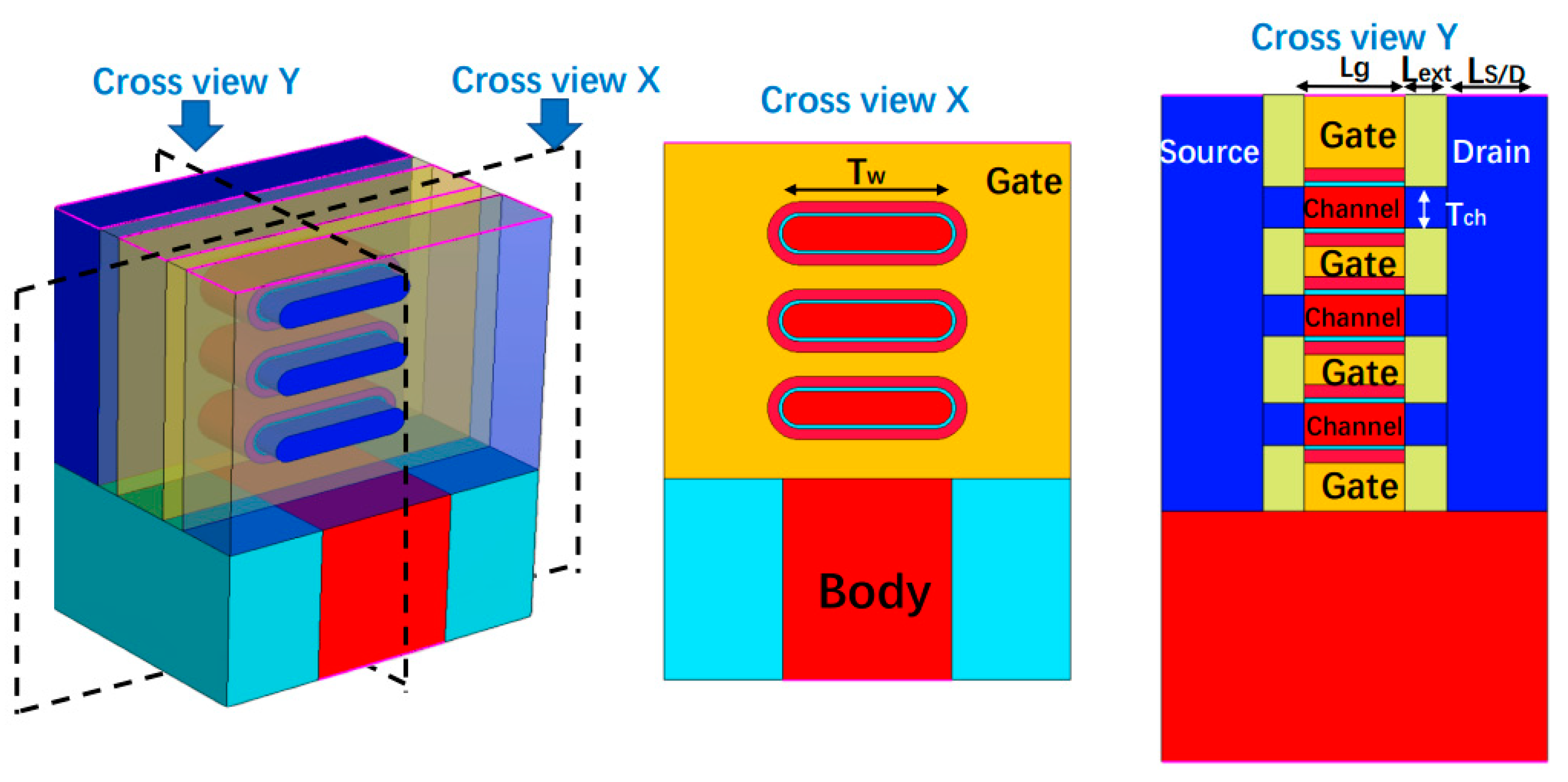

2.1. Device Structure

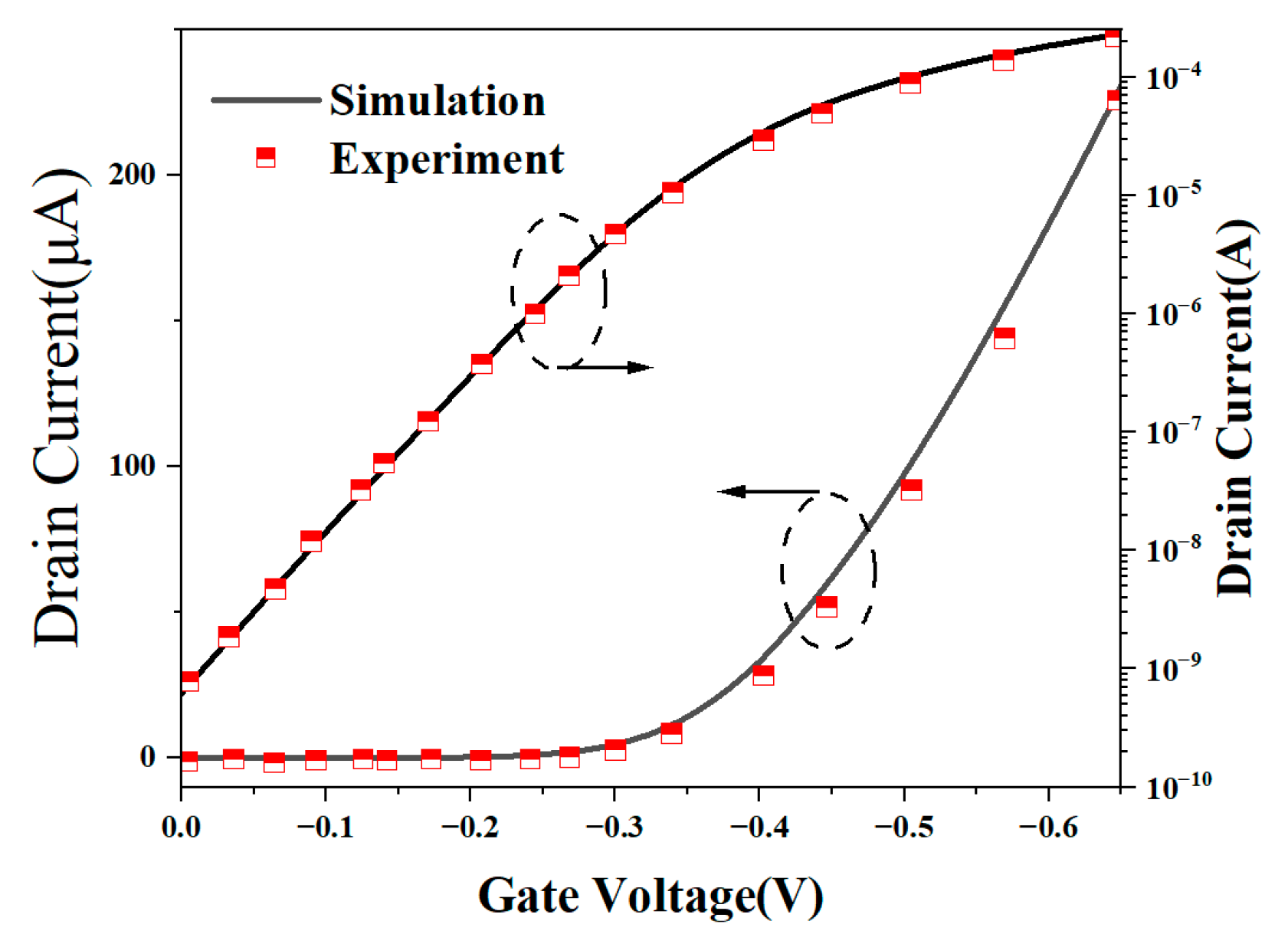

2.2. TCAD Simulation

2.3. NBTI Simulation Framework

3. Results and Discussion

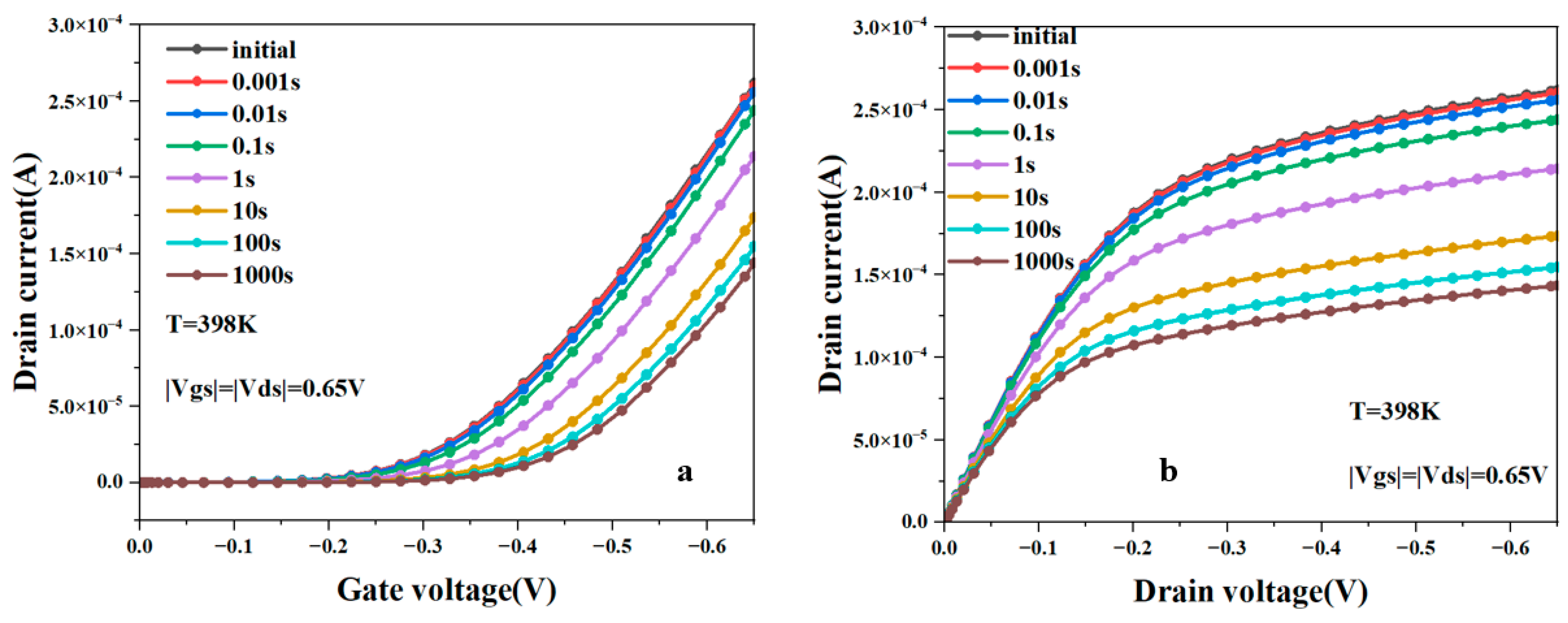

3.1. NBTI under the Influence of Self-Heating Effect

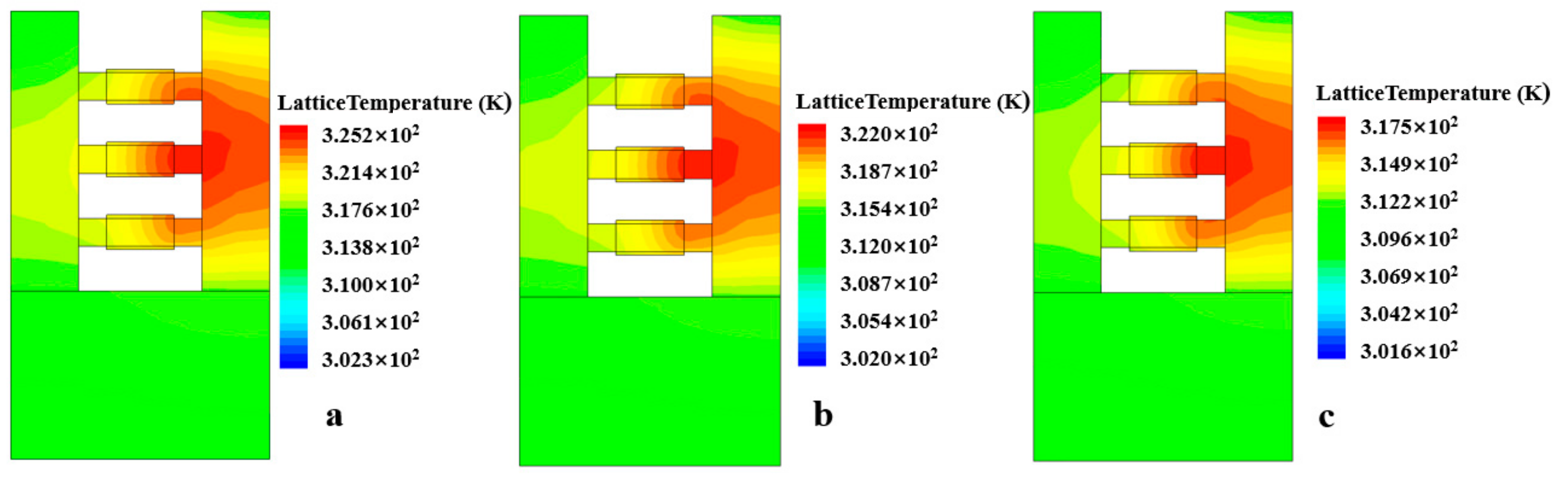

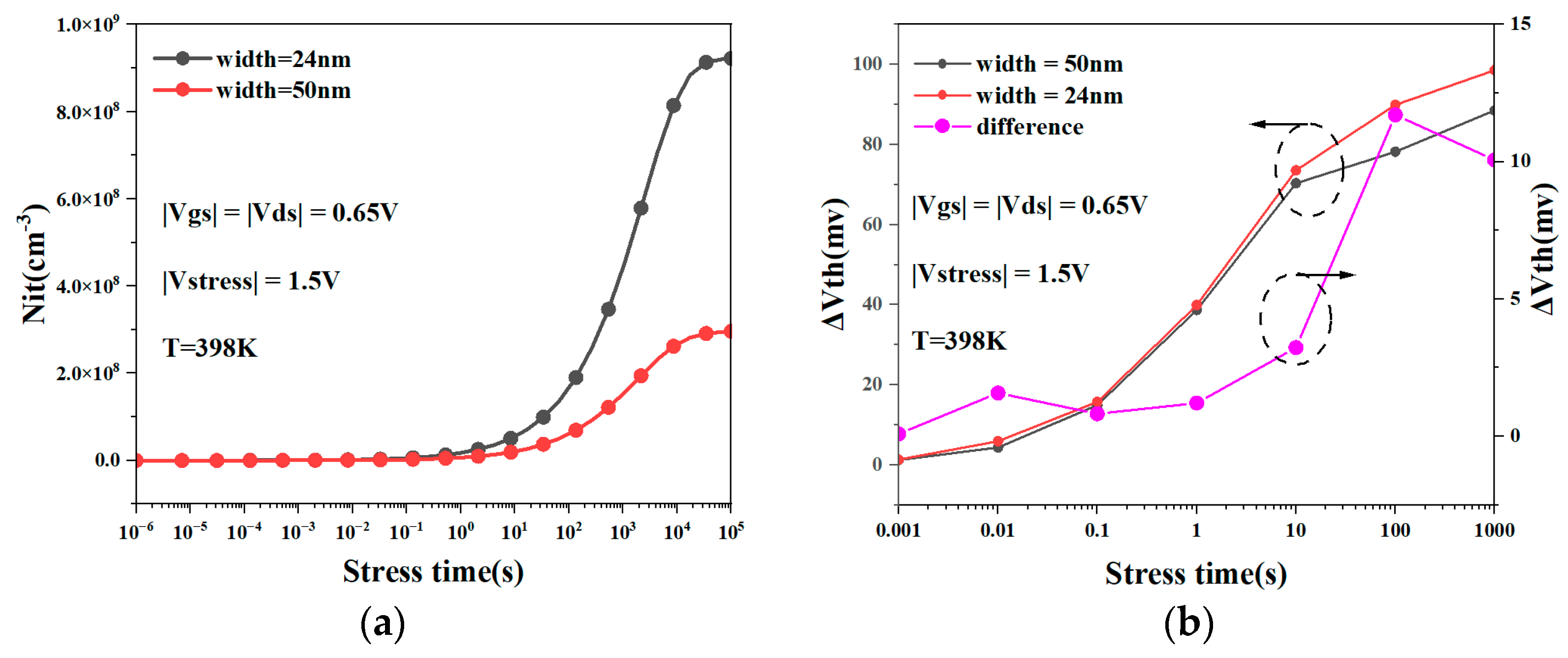

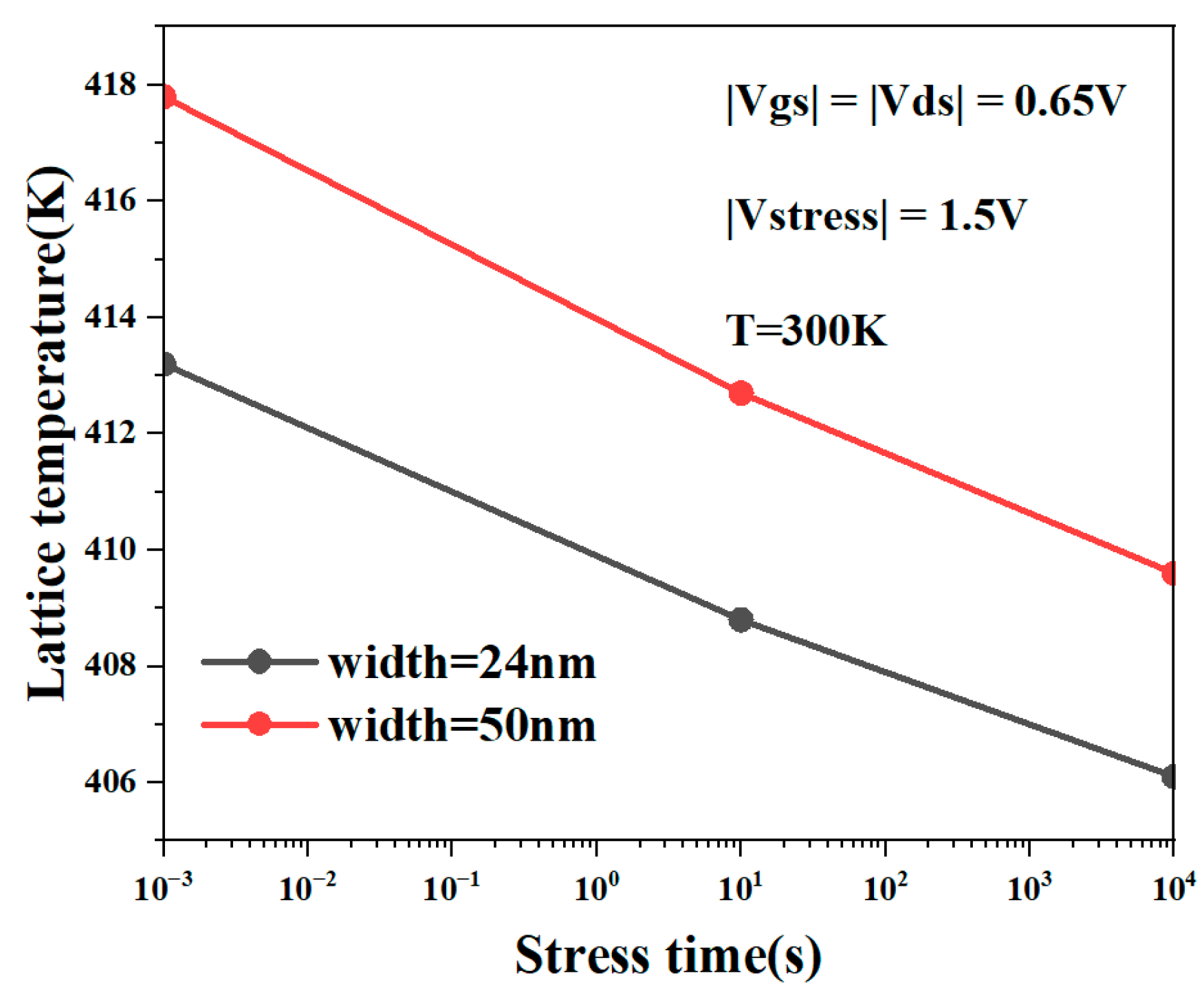

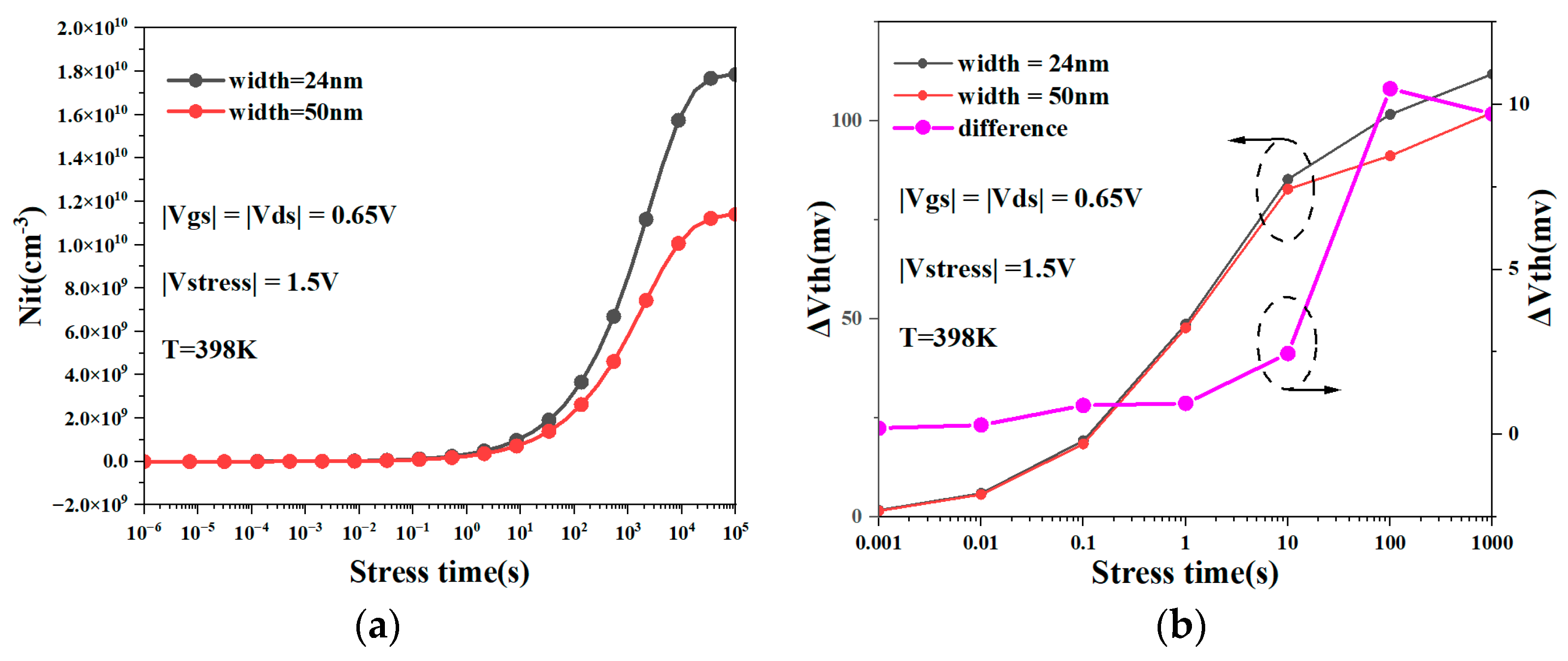

3.2. Effect of Nanosheet Width on NBTI and SHE

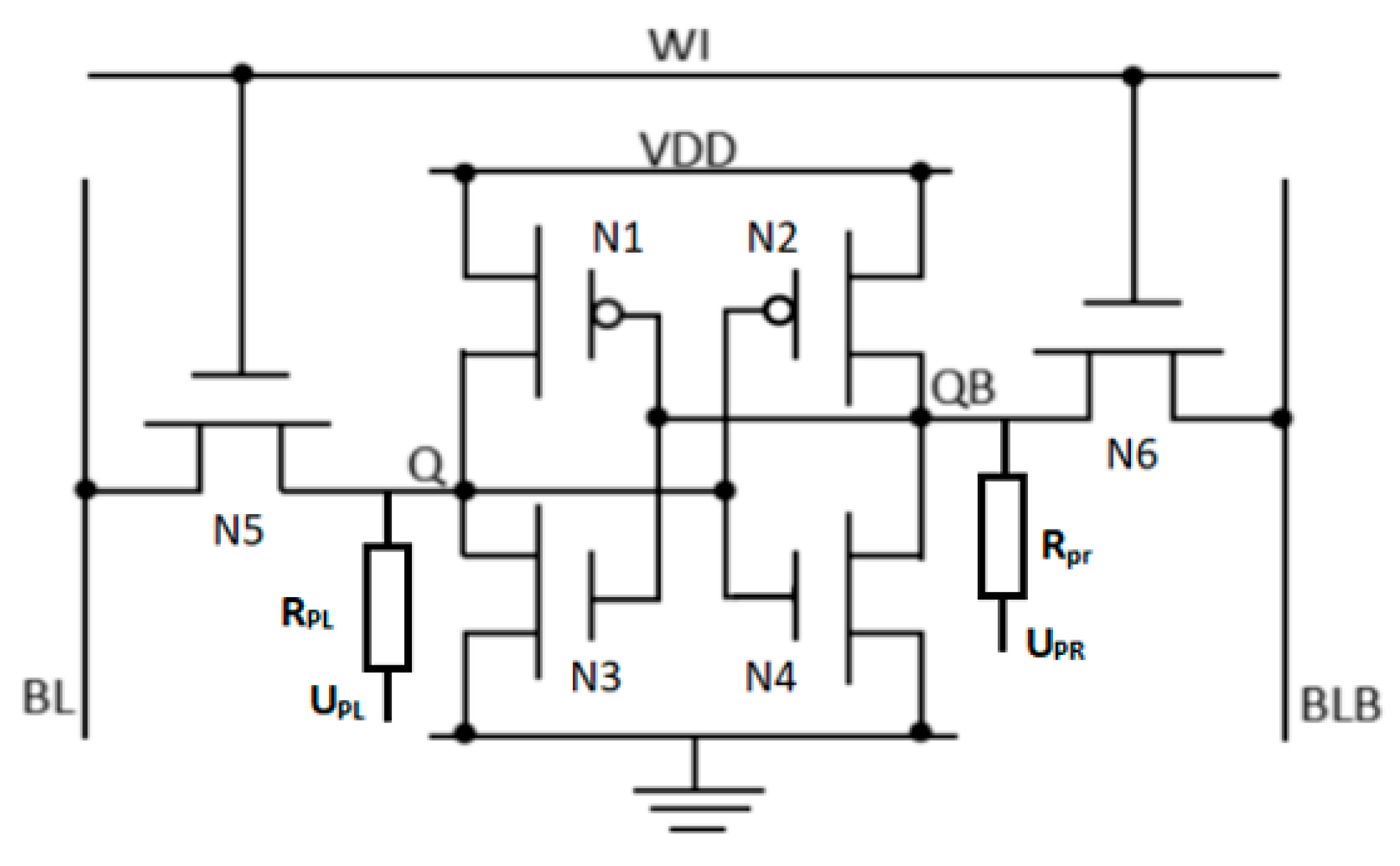

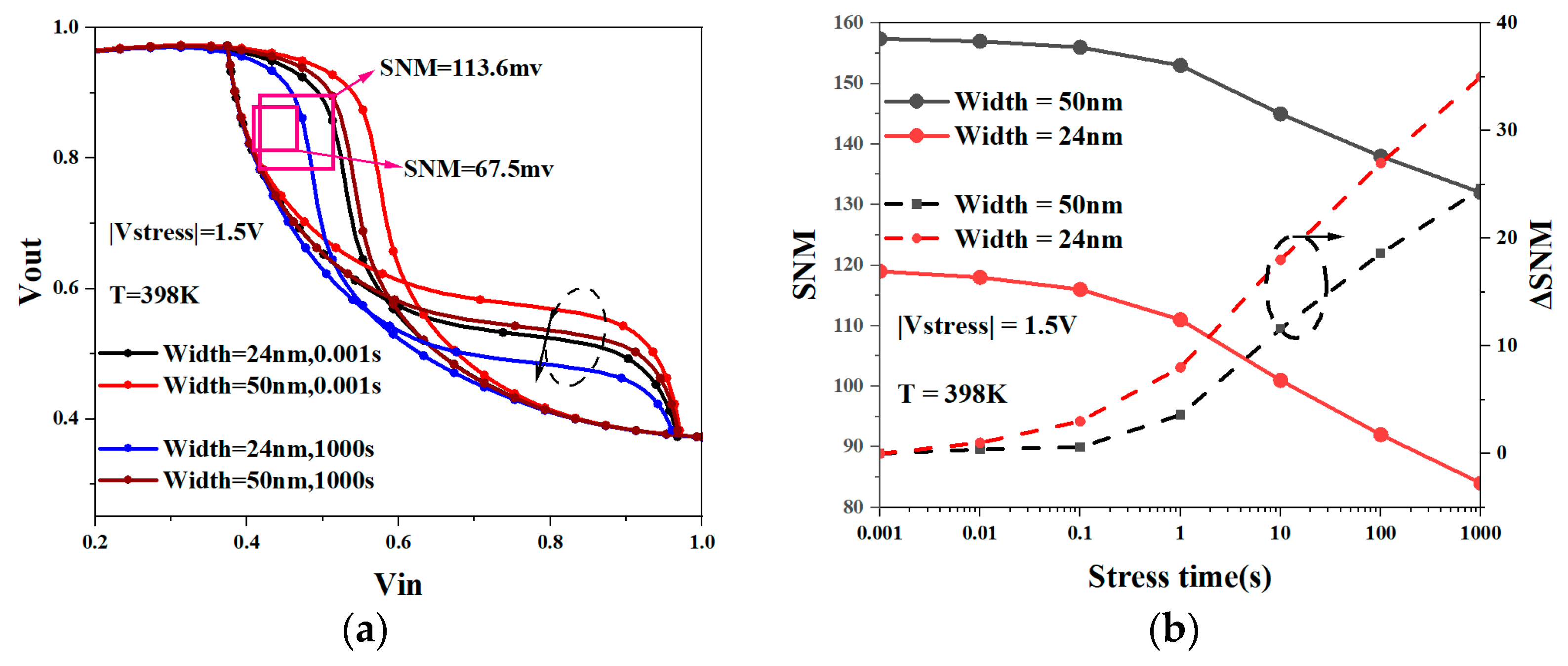

3.3. Influence of NBTI and SHE on SRAM

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Schaller, R.R. Moore’s law: Past, present and future. IEEE Spectr. 1997, 34, 52–59. [Google Scholar] [CrossRef]

- Iwai, H. Future of nano CMOS technology. Solid-State Electron. 2015, 112, 56–67. [Google Scholar] [CrossRef]

- Yakimets, D.; Eneman, G.; Schuddinck, P.; Bao, T.H.; Bardon, M.G.; Raghavan, P.; Veloso, A.; Collaert, N.; Mercha, A.; Verkest, D.; et al. Vertical GAAFETs for the ultimate CMOS scaling. IEEE Trans. Electron. Devices 2015, 62, 1433–1439. [Google Scholar] [CrossRef]

- Ryu, D.; Kim, M.; Yu, J.; Kim, S.; Lee, J.-H.; Park, B.-G. Investigation of Sidewall High-k Interfacial Layer Effect in Gate-All-Around Structure. IEEE Trans. Electron. Devices 2020, 67, 1859–1863. [Google Scholar] [CrossRef]

- Young, K.K. Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans. Electron. Devices 1989, 36, 399–402. [Google Scholar] [CrossRef]

- D’Agostino, F.; Quercia, D. Short-channel effects in MOSFETs. Introd. VLSI Des. 2000, 467, 71–72. [Google Scholar]

- Huang, Y.-C.; Chiang, M.-H.; Wang, S.-J.; Fossum, J.G. GAAFET versus pragmatic FinFET at the 5 nm Si-based CMOS technology node. IEEE J. Electron. Devices Soc. 2017, 5, 164–169. [Google Scholar] [CrossRef]

- Kushwaha, P.; Dasgupta, A.; Kao, M.-Y.; Agarwal, H. Design Optimization Techniques in Nanosheet Transistor for RF Applications. IEEE Trans. Electron Devices 2020, 67, 4515–4520. [Google Scholar] [CrossRef]

- Kuhn, K.J. Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2012, 59, 1813–1828. [Google Scholar] [CrossRef]

- Cheng, S.L.; Li, C.; Dong, X.Y.; Lv, S.S.; You, H.L. NSFET performance optimization through SiGe channel design—A simulation study. Microelectron. Reliab. 2023, 148, 115037. [Google Scholar] [CrossRef]

- Mohapatra, E.; Jena, D.; Das, S.; Maiti, C.K.; Dash, T.P. Design and optimization of stress/strain in GAA nanosheet FETs for improved FOMs at sub-7 nm nodes. Phys. Scr. 2023, 98, 065919. [Google Scholar] [CrossRef]

- Cheng, S.L.; Lv, S.S.; Li, C.; Dong, X.Y.; You, H.L. Investigate on DC Characteristics and NBTI of SiGe Core-Shell Nanosheet FET. In Proceedings of the 2022 IEEE 16th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Nangjing, China, 25–28 October 2022. [Google Scholar]

- Rathore, S.; Jaisawal, R.K.; Kondekar, P.N.; Bagga, N. Trap and self-heating effect based reliability analysis to reveal early aging effect in nanosheet FET. Solid-State Electron. 2023, 200, 108546. [Google Scholar] [CrossRef]

- Kimizuka, N.; Yamaguchi, K.; Imai, K.; Iizuka, T.; Liu, C.T.; Keller, R.C.; Horiuchi, T. NBTI Enhancement by Nitrogen Incorporation into Ultrathin Gate Oxide for 010 $\mu$m Gate CMOS Generation. In Proceedings of the 2000 Symposium on VLSI Technology. Digest of Technical Papers (Cat. No. 00CH37104), Honolulu, HI, USA, 13–15 June 2000. [Google Scholar]

- Wang, Y.Q.; Li, G.P.; Li, C.; Kuang, F.Y.; Li, O.W.; You, H.L. Bias Temperature Instability Analysis of Nanosheet Based SRAM. In Proceedings of the 2022 IEEE 16th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Nangjing, China, 25–28 October 2022. [Google Scholar]

- Tiwari, R.; Parihar, N.; Thakor, K.; Wong, H.Y.; Mahapatra, S. TCAD Framework to Estimate the NBTI Degradation in FinFET and GAA NSFET Under Mechanical Strain. In Proceedings of the 2019 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Udine, Italy, 4–6 September 2019. [Google Scholar]

- Wang, M.; Zhang, J.; Zhou, H.; Southwick, R.G.; Chao, R.H.K.; Miao, X.; Basker, V.S.; Yamashita, T.; Guo, D.; Karve, G.; et al. Bias Temperature Instability Reliability in Stacked Gate-All-Around Nanosheet Transistor. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019. [Google Scholar]

- Rathore, S.; Jaisawal, R.K.; Kondekar, P.N.; Bagga, N. Design Optimization of Three-Stacked Nanosheet FET From Self-Heating Effects Perspective. IEEE Trans. Device Mater. Reliab. 2022, 22, 396–402. [Google Scholar] [CrossRef]

- Verdonckt-Vandebroek, S.; Crabbe, E.F.; Meyerson, B.S.; Harame, D.L.; Restle, P.J.; Stork, J.M.; Johnson, J.B. SiGe-Channel Heteroj unc tion p-MOSFET’ s. IEEE Trans. Electron Devices 1994, 41, 90–101. [Google Scholar] [CrossRef]

- Hwang, J.R.; Ho, J.H.; Ting, S.M.; Chen, T.P.; Hsieh, Y.S.; Huang, C.C.; Chiang, Y.Y.; Lee, H.K.; Liu, A.; Shen, T.M.; et al. Performance of 70 nm Strained-Silicon CMOS Devices. In Proceedings of the 2003 Symposium on VLSI Technology. Digest of Technical Papers (IEEE Cat. No. 03CH37407), Kyoto, Japan, 10–12 June 2003. [Google Scholar]

- Bathula, S.; Jayasimhadri, M.; Dhar, A. Mechanical properties and microstructure of spark 313 plasma sintered nanostructured p-type SiGe thermoelectric alloys. Mater. Des. 2015, 87, 414–420. [Google Scholar] [CrossRef]

- Sootkaneung, W.; Howimanporn, S.; Chookaew, S. Thermal Effect on Performance, Power, and BTI Aging in FinFET-Based Designs. In Proceedings of the 2017 Euromicro Conference on Digital System Design (DSD), Vienna, Austria, 30 August–1 September 2017. [Google Scholar]

- Jin, M.; Liu, C.; Kim, J.; Kim, J.; Choo, S.; Kim, Y.; Shim, H.; Zhang, L.; Nam, K.J.; Park, J.; et al. Hot Carrier Reliability Characterization in Consideration of Self-Heating in FinFET Technology. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016. [Google Scholar]

- Son, D.; Hong, K.; Shim, H.; Pae, S.; Shin, H. New Insight Into Negative Bias Temperature Instability Degradation During Self-Heating in Nanoscale Bulk FinFETs. IEEE Electron Device Lett. 2019, 40, 1354–1357. [Google Scholar] [CrossRef]

- Prakash, O.; Amrouch, H.; Manhas, S.; Henkel, J. Impact of NBTI Aging on Self-Heating in Nanowire FET. In Proceedings of the 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2020. [Google Scholar]

- Choudhury, N.; Mahapatra, S. A Method to Isolate Intrinsic HCD and NBTI Contributions Under Self Heating During Varying VG/VD Stress in GAA Nanosheet PFETs. IEEE Trans. Electron Devices 2022, 67, 3535–3541. [Google Scholar] [CrossRef]

- Huang, P.C.; Chen, L.A.; Sheu, J.T. Electric-Field Enhancement of a Gate-All-Around Nanowire Thin-Film Transistor Memory. IEEE Electron Device Lett. 2010, 31, 216–218. [Google Scholar] [CrossRef]

- Arden, W.M. The International Technology Roadmap for Semiconductors—Perspectives and 335 challenges for the next 15 years. Curr. Opin. Solid State Mater. Sci. 2002, 6, 371–377. [Google Scholar] [CrossRef]

- Anju, E.; Muneta, I.; Kakushima, K.; Tsutsui, K.; Wakabayashi, H. Self-Heating-Effect-Free p/n-Stacked-NW on Bulk-FinFETs and 6T-SRAM Layout. In Proceedings of the 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM), Kobe, Japan, 13–16 March 2018. [Google Scholar]

- Fan, J.; Li, M.; Xu, X.; Yang, Y.; Xuan, H.; Huang, R. Insight Into Gate-Induced Drain Leakage in Silicon Nanowire Transistors. IEEE Trans. Electron Devices 2015, 62, 213–219. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar]

- Parihar, N.; Goel, N.; Mukhopadhyay, S.; Mahapatra, S. BTI Analysis Tool—Modeling of NBTI DC, AC Stress and Recovery Time Kinetics, Nitrogen Impact, and EOL Estimation. IEEE Trans. Electron Devices 2017, 65, 392–403. [Google Scholar] [CrossRef]

- Manual, T.S.U. Sentaurus™ Device User Guide Version N-2017.09; Synopsys: Mountain View, CA, USA, 2017. [Google Scholar]

- Desai, S.; Mukhopadhyay, S.; Goel, N.; Nanaware, N.; Jose, B.; Joshi, K.; Mahapatra, S. A Comprehensive AC/DC NBTI Model: Stress, Recovery, Frequency, Duty Cycle and Process Dependence. In Proceedings of the 2013 IEEE international reliability physics symposium (IRPS), Monterey, CA, USA, 14–18 April 2013. [Google Scholar]

- Choudhury, N.; Parihar, N.; Goel, N.; Thirunavukkarasu, A.; Mahapatra, S. A Model for Hole Trapping-Detrapping Kinetics During NBTI in p-Channel FETs: (Invited Paper). In Proceedings of the 2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Penang, Malaysia, 6–21 April 2020. [Google Scholar]

- Choudhury, N.; Parihar, N.; Mahapatra, S. Analysis of The Hole Trapping Detrapping Component of NBTI Over Extended Temperature Range. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020. [Google Scholar]

- Parihar, N.; Sharma, U.; Southwick, R.G.; Wang, M.; Stathis, J.H.; Mahapatra, S. Ultrafast measurements and physical modeling of NBTI stress and recovery in RMG FinFETs under Diverse DC–AC experimental conditions. IEEE Trans. Electron Devices 2017, 65, 23–30. [Google Scholar] [CrossRef]

- Mishra, S.; Wong, H.Y.; Tiwari, R.; Chaudhary, A.; Parihar, N.; Rao, R.; Motzny, S.; Moroz, V.; Mahapatra, S. Predictive TCAD for NBTI Stress-Recovery in Various Device Architectures and Channel Materials. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017. [Google Scholar]

- Tayal, S.; Smaani, B.; Rahi, S.B.; Upadhyay, A.K.; Bhattacharya, S.; Ajayan, J.; Jena, B.; Myeong, I.; Park, B.G.; Song, Y.S. Incorporating Bottom-Up Approach Into Device/Circuit Co-Design for SRAM-Based Cache Memory Applications. IEEE Trans. Electron Devices 2022, 69, 6127–6132. [Google Scholar] [CrossRef]

- Gadhe, A.; Shirode, U. Read stability and Write ability analysis of different SRAM cell structures. Int. J. Eng. Res. Appl. (IJERA) 2013, 3, 1073–1078. [Google Scholar]

| Symbol | Implication | Value |

|---|---|---|

| Lg | Gate length | 12 nm |

| Lext | Extension length | 5 nm |

| Ls/d | S/D length, | 12 nm |

| Tch | Channel height | 5 nm |

| Tw | Channel width | 25 nm |

| Nc | Channel doping concentration | 1 × 1016 cm−3 |

| Nd | Drain doping concentration | 1 × 1020 cm−3 |

| Ns | Source doping concentration | 1 × 1020 cm−3 |

| Eot | Equivalent oxide thickness | 0.9 nm |

| Vth0 | Initial Vth before NBTI effect | −0.3792 V |

| Aging Time | Initial | NBTI Aging |

|---|---|---|

| 0.001 s | −0.3729 V | −0.3746 |

| 0.01 s | −0.3729 V | −0.3784 |

| 0.1 s | −0.3729 V | −0.3862 |

| 1 s | −0.3729 V | −0.4126 |

| 10 s | −0.3729 V | −0.4467 |

| 100 s | −0.3729 V | −0.4629 |

| 1000 s | −0.3729 V | −0.4726 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, X.; Shao, Y.; Wang, Y.; Liu, F.; Kuang, F.; Zhuang, Y.; Li, C. Interaction of Negative Bias Instability and Self-Heating Effect on Threshold Voltage and SRAM (Static Random-Access Memory) Stability of Nanosheet Field-Effect Transistors. Micromachines 2024, 15, 420. https://doi.org/10.3390/mi15030420

Li X, Shao Y, Wang Y, Liu F, Kuang F, Zhuang Y, Li C. Interaction of Negative Bias Instability and Self-Heating Effect on Threshold Voltage and SRAM (Static Random-Access Memory) Stability of Nanosheet Field-Effect Transistors. Micromachines. 2024; 15(3):420. https://doi.org/10.3390/mi15030420

Chicago/Turabian StyleLi, Xiaoming, Yali Shao, Yunqi Wang, Fang Liu, Fengyu Kuang, Yiqi Zhuang, and Cong Li. 2024. "Interaction of Negative Bias Instability and Self-Heating Effect on Threshold Voltage and SRAM (Static Random-Access Memory) Stability of Nanosheet Field-Effect Transistors" Micromachines 15, no. 3: 420. https://doi.org/10.3390/mi15030420