Improving ESD Protection Robustness Using SiGe Source/Drain Regions in Tunnel FET

Abstract

:1. Introduction

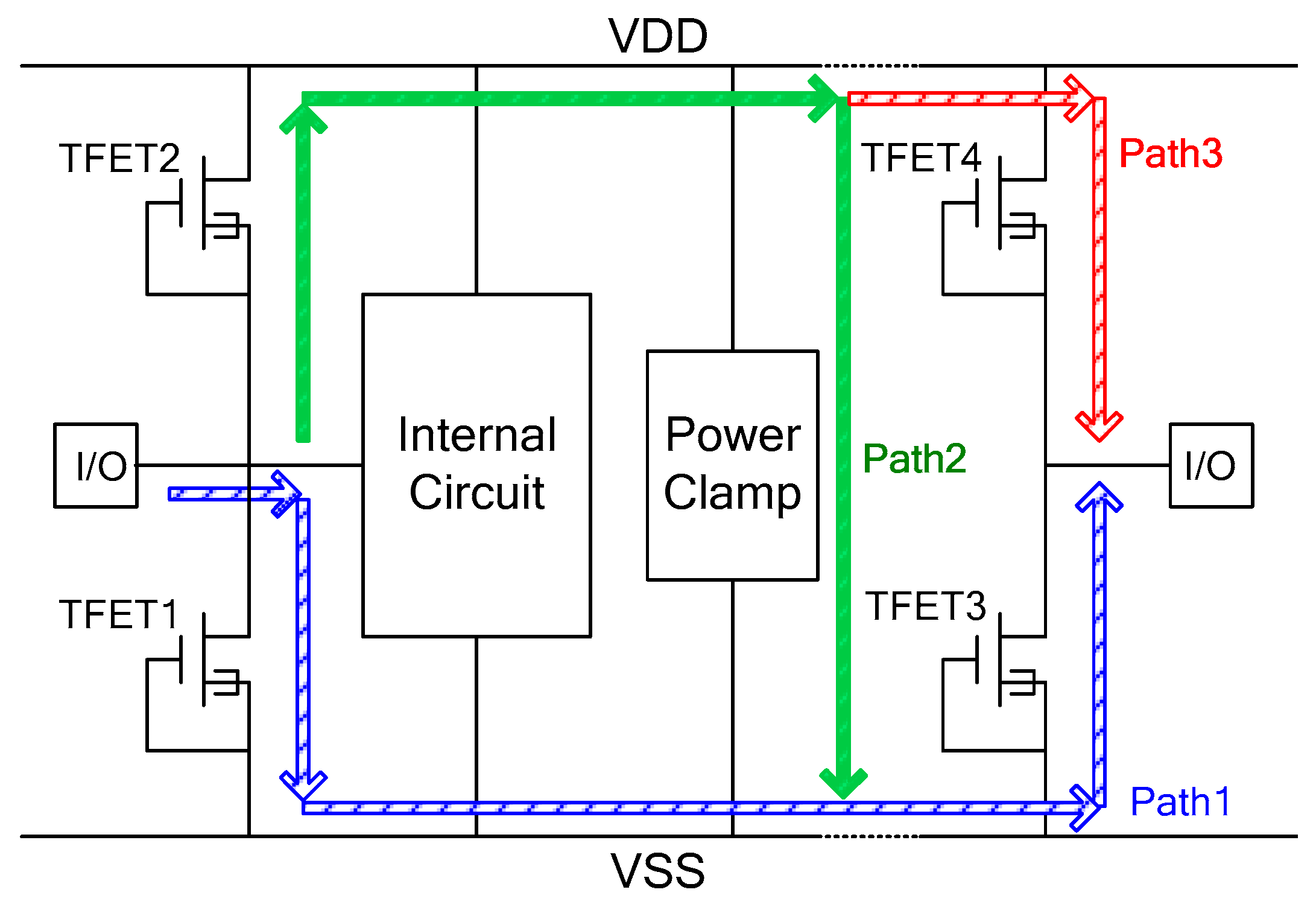

2. Basic Concept of Electrostatic Discharge (ESD) Protection Tunnel Field-Effect Transistor (TFET) and the Protection Network

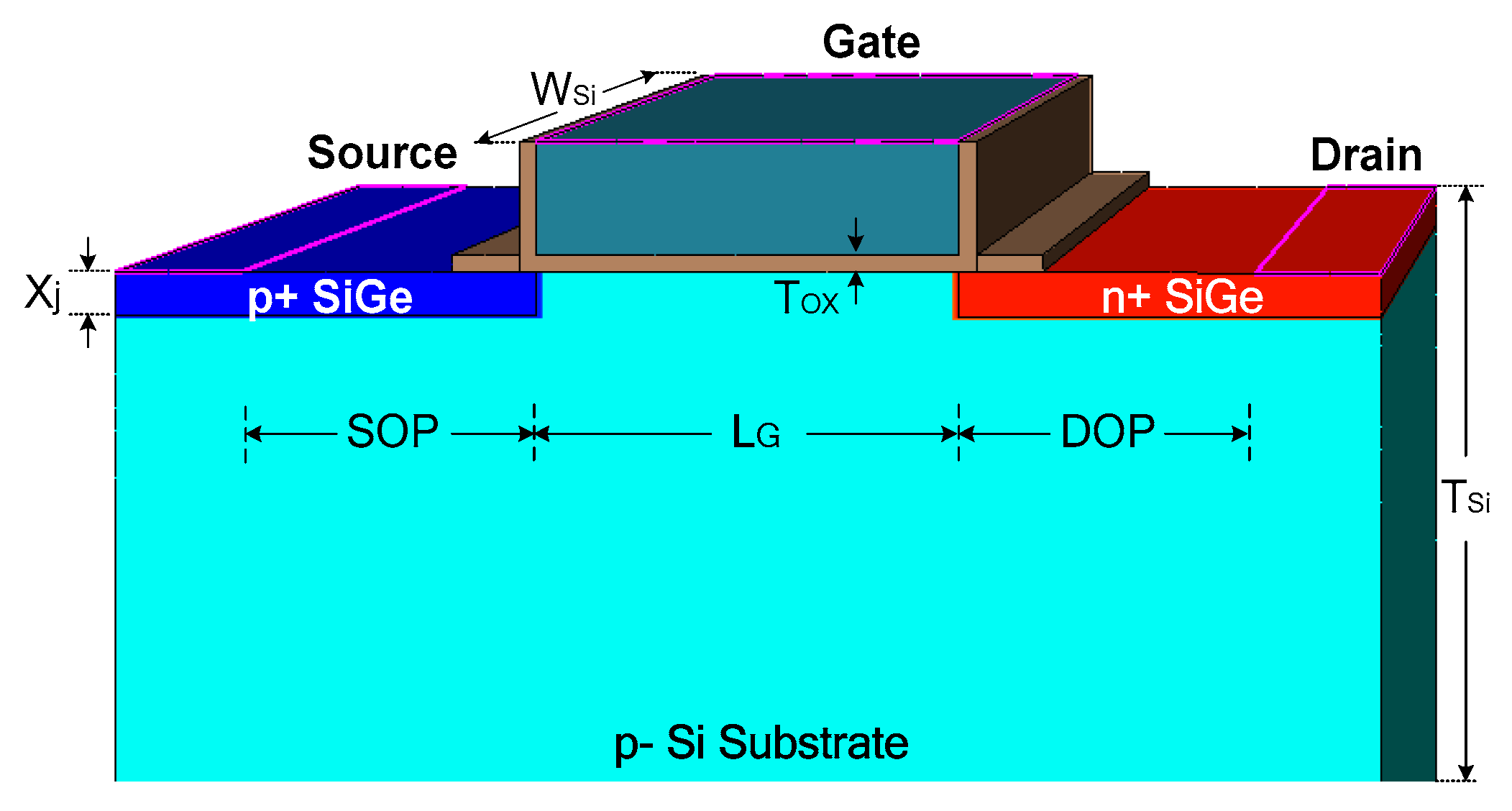

3. Device Structure and Simulation Setup

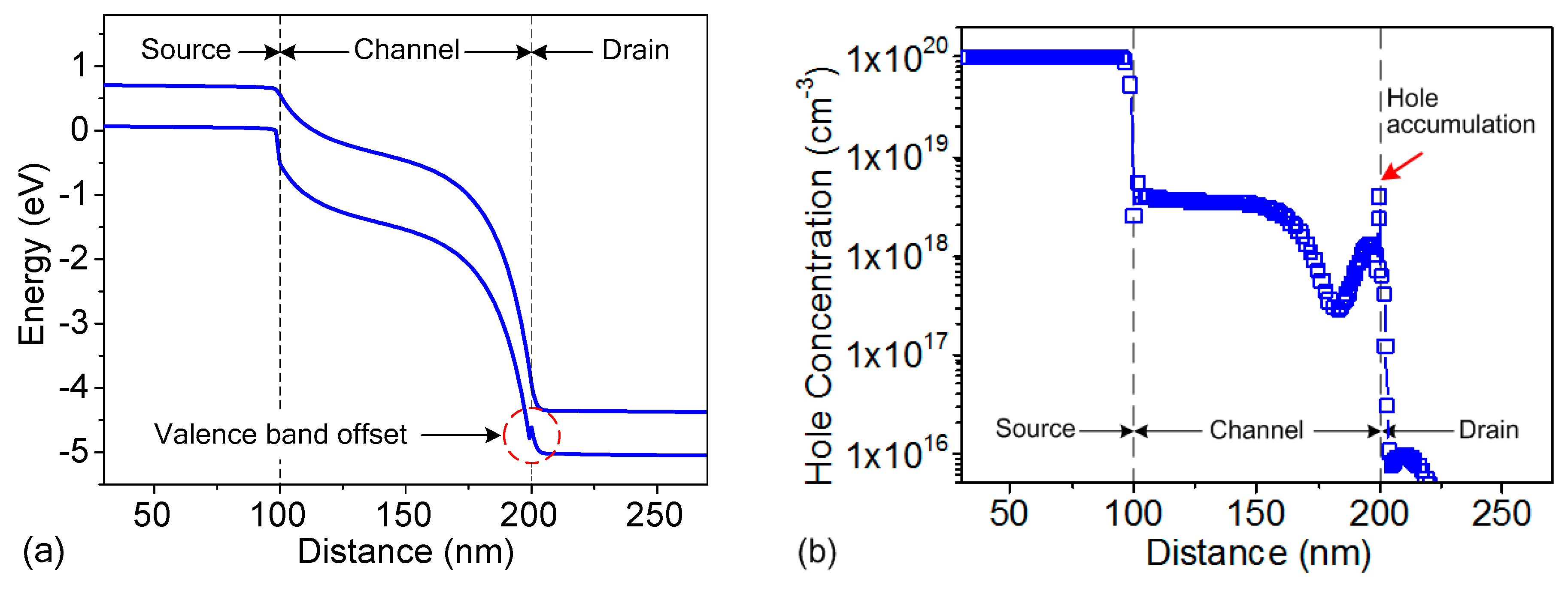

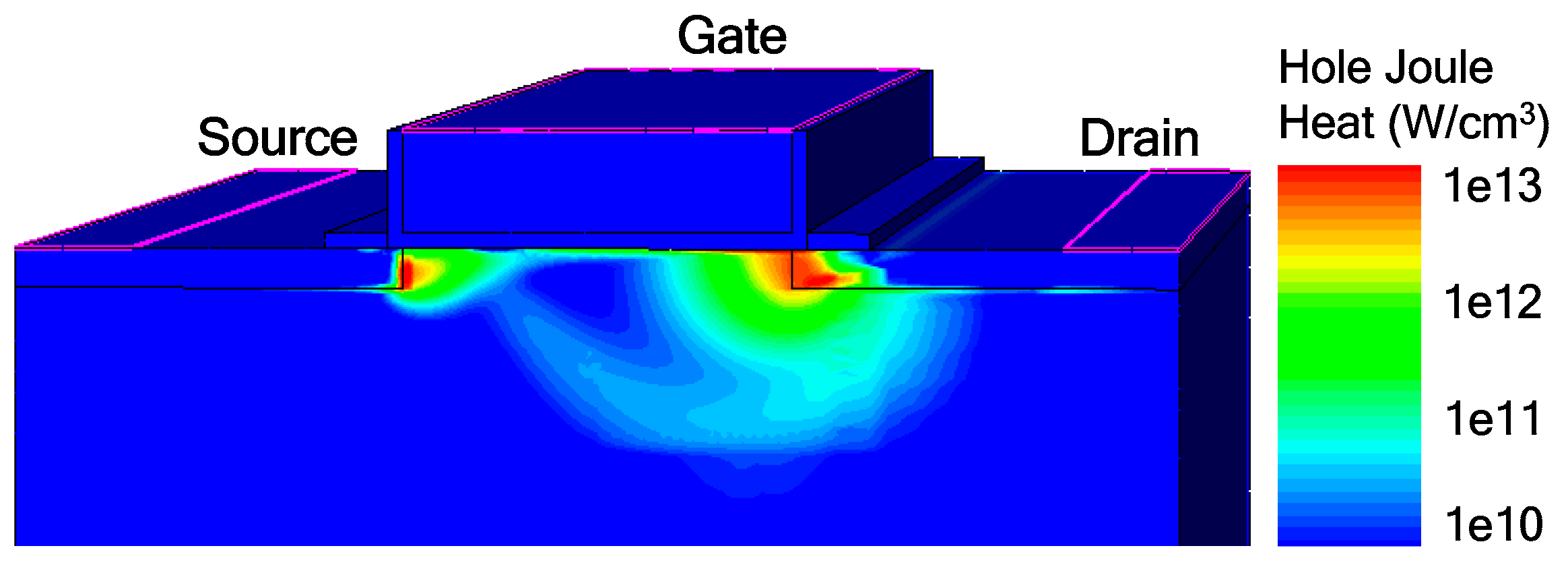

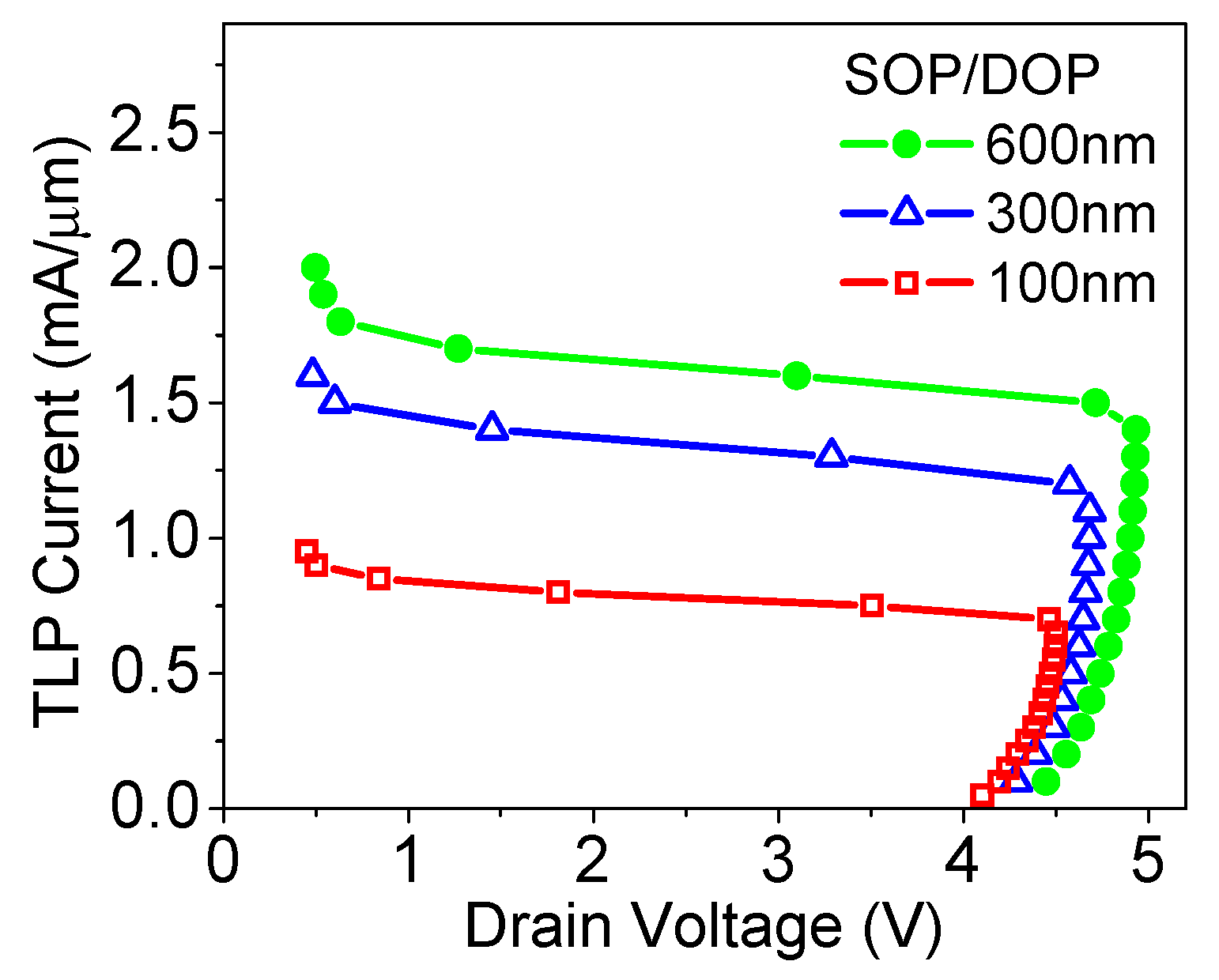

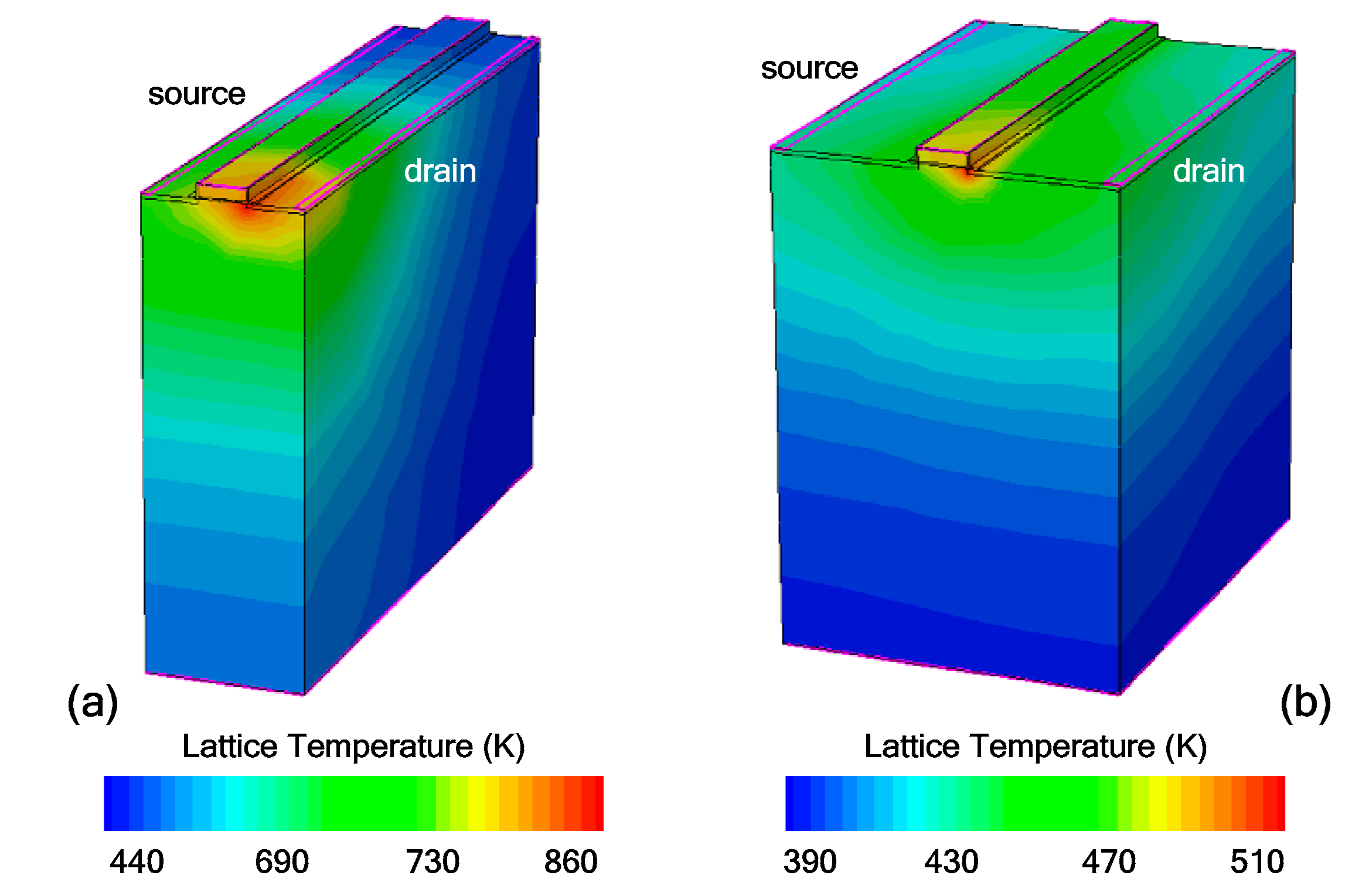

4. Simulation Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Cristoloveanu, S.; Wan, J.; Zaslavsky, A. A review of sharp switching devices for ultra-low power applications. IEEE J. Electron Devices Soc. 2016, 4, 215–226. [Google Scholar] [CrossRef]

- Hueting, R.J.E. The Balancing Act in Ferroelectric Transistors: How Hard Can It Be? Micromachines 2018, 9, 582. [Google Scholar] [CrossRef]

- Seabaugh, A.; Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 2010, 98, 2095–2110. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef]

- Chen, S.; Wang, S.; Liu, H.; Li, W.; Wang, Q.; Wang, X. Symmetric U-Shaped Gate Tunnel Field-Effect Transistor. IEEE Trans. Electron Devices 2017, 64, 1343–1349. [Google Scholar] [CrossRef]

- Chen, Y.-N.; Fan, M.-L.; Hu, P.-H.; Su, P.; Chuang, C.-T. Evaluation of stability, performance of ultra-low voltage MOSFET, TFET, and mixed TFET-MOSFET SRAM cell with write-assist circuits. IEEE J. Emerg. Sel. Topic Circuits Syst. 2014, 4, 389–399. [Google Scholar] [CrossRef]

- Strangio, S.; Palestri, P.; Esseni, D.; Selmi, L.; Crupi, F.; Richter, S.; Zhao, Q.T.; Mantl, S. Impact of TFET unidirectionality and ambipolarity on the performance of 6T SRAM cells. IEEE J. Electron Devices Soc. 2015, 3, 223–232. [Google Scholar] [CrossRef]

- Lanuzza, M.; Strangio, S.; Crupi, F.; Palestri, P.; Esseni, D. Mixed tunnel-FET/MOSFET level shifters: A new proposal to extend the tunnel-FET application domain. IEEE Trans. Electron Devices 2015, 62, 3973–3979. [Google Scholar] [CrossRef]

- Sithanandam, R.; Kumar, M.J. A new on-chip ESD strategy using TFETs-TCAD based device and network simulations. IEEE J. Electron Devices Soc. 2018, 6, 298–308. [Google Scholar] [CrossRef]

- Liou, J.J. Challenges of designing electrostatic discharge (ESD) protection in modern and emerging CMOS technologies. Proc. ISNE 2014, 4, 1–3. [Google Scholar]

- Galy, P. ElectroStatic Discharge (ESD) one real life event: Physical impact and protection challenges in advanced CMOS technologies. In Proceedings of the 2014 International Semiconductor Conference (CAS), Sinaia, Romania, 13–15 October 2014; pp. 31–34. [Google Scholar]

- Boschke, R.; Linten, D.; Hellings, G.; Chen, S.-H.; Scholz, M.; Mitard, J.; Witters, L.; Collaert, N.; Thean, A.; Groeseneken, G. ESD characterization of diodes and ggMOS in Germanium FinFET technologies. In Proceedings of the 2015 37th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Reno, NV, USA, 27 September–2 October 2015; pp. 1–9. [Google Scholar]

- Boschke, R.; Chen, S.-H.; Scholz, M.; Hellings, G.; Linten, D.; Witters, L.; Collaert, N.; Groeseneken, G. ESD Ballasting of SiGe FinFET ggNMOS devices. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017. [Google Scholar]

- Lin, C.-Y.; Wu, Y.-H.; Ker, M.-D. Low-leakage and low-trigger-voltage SCR device for ESD protection in 28-nm high-k metal gate CMOS process. IEEE Electron Device Lett. 2016, 37, 1387–1389. [Google Scholar] [CrossRef]

- Galy, P.; Athanasiou, S. Preliminary results on TFET-gated diode in thin silicon film for IO design & ESD protection in 28 nm UTBB FD-SOI CMOS technology. In Proceedings of the 2016 International Conference on IC Design and Technology (ICICDT), Ho Chi Minh City, Vietnam, 27–29 June 2016; pp. 1–4. [Google Scholar]

- Kranthi, N.K.; Shrivastava, M. ESD behavior of tunnel FET devices. IEEE Trans. Electron Devices 2017, 64, 28–36. [Google Scholar] [CrossRef]

- Yang, Z.; Zhang, Y.; Yang, Y.; Yu, N. Investigation of the double current path phenomenon in gate-grounded tunnel FET. IEEE Electron Device Lett. 2018, 39, 103–106. [Google Scholar] [CrossRef]

- Yang, Z.; Yu, N.; Liou, J.J. Impact of the gate structure on ESD characteristic of tunnel field-effect transistors. In Proceedings of the 2018 7th International Symposium on Next Generation Electronics (ISNE), Taipei, Taiwan, 7–9 May 2018; pp. 1–4. [Google Scholar]

- Mayer, F.; Le Royer, C.; Damlencourt, J.-F.; Romanjek, K.; Andrieu, F.; Tabone, C.; Previtali, B.; Deleonibus, S. Impact of SOI, Si1−xGexOI and GeOI substrates on CMOS compatible tunnel FET performance. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–5. [Google Scholar]

- Kim, S.H.; Agarwal, S.; Jacobson, Z.A.; Matheu, P.; Hu, C.; Liu, T.-J.K. Tunnel field effect transistor with raised germanium source. IEEE Electron Device Lett. 2010, 31, 1107–1109. [Google Scholar] [CrossRef]

- Schmidt, M.; Schäfer, A.; Minamisawa, R.A.; Buca, D.; Trellenkamp, S.; Hartmann, J.-M.; Zhao, Q.-T.; Mantl, S. Line and point tunneling in scaled Si/SiGe heterostructure TFETs. IEEE Electron Device Lett. 2014, 35, 699–701. [Google Scholar] [CrossRef]

- Wang, W.; Wang, P.F.; Zhang, C.M.; Lin, X.; Liu, X.Y.; Sun, Q.Q.; Zhou, P.; Zhang, D.W. Design of U-shape channel tunnel FETs with SiGe source regions. IEEE Trans. Electron Devices 2014, 61, 193–197. [Google Scholar] [CrossRef]

- Sithanandam, R.; Kumar, M.J. A novel cascade-free 5-V ESD clamp using I-MOS: Proposal and analysis. IEEE Trans. Device Mater. Reliab. 2016, 16, 200–207. [Google Scholar] [CrossRef]

- Sze, S.M. Physics of Semiconductor Devices, 3rd ed.; Wiley: New York, NY, USA, 2006; pp. 39–41. [Google Scholar]

- Sarkar, D.; Singh, N.; Banerjee, K. A novel enhanced electric-field impact-ionization MOS transistor. IEEE Electron Device Lett. 2010, 31, 1175–1177. [Google Scholar] [CrossRef]

- Synopsys. User Manual, Ver. I-2013.03, Synopsys TCAD Sentaurus; Synopsys: San Jose, CA, USA, 2013. [Google Scholar]

- Shrivastava, M.; Agrawal, M.; Mahajan, S.; Gossner, H.; Schulz, T.; Kumar Sharma, D.; Rao, V.P. Physical insight toward heat transport and an improved electrothermal modeling framework for FinFET architectures. IEEE Trans. Electron Devices 2012, 59, 1353–1363. [Google Scholar] [CrossRef]

- Aksamija, Z.; Knezevic, I. Reduced thermal conductivity in SiGe alloy-based superlattices for thermoelectric applications. In Proceedings of the International Silicon-Germanium Technology and Device Meeting, Berkeley, CA, USA, 4–6 June 2012; pp. 1–2. [Google Scholar]

- Thijs, S.; Griffoni, A.; Linten, D.; Chen, S.-H.; Hoffmann, T.; Groeseneken, G. On gated diodes for ESD protection in bulk FinFET CMOS technology. In Proceedings of the EOS/ESD Symposium Proceedings, Anaheim, CA, USA, 11–16 September 2011; pp. 1–8. [Google Scholar]

- Zhang, X.Y.; Banerjee, K.; Amerasekera, A.; Gupta, V.; Yu, Z.; Dutton, R.W. Process and layout dependent substrate resistance modeling for deep sub-micron ESD protection devices. In Proceedings of the 2000 IEEE International Reliability Physics Symposium Proceedings, San Jose, CA, USA, 10–13 April 2000; pp. 295–303. [Google Scholar]

- Griffoni, A.; Thijs, S.; Russ, C.; Trémouilles, D.; Linten, D.; Scholz, M.; Collaert, N.; Witters, L.; Meneghesso, G.; Groeseneken, G. Next generation bulk FinFET devices and their benefits for ESD robustness. In Proceedings of the 2009 31st EOS/ESD Symposium, Anaheim, CA, USA, 30 August–4 September 2009; pp. 1–10. [Google Scholar]

| Gate Length | 50 nm | 100 nm | 150 nm | 200 nm |

|---|---|---|---|---|

| Triggering Voltage | 4.06 V | 4.1 V | 4.18 V | 4.28 V |

| Failure Current | 0.65 mA/μm | 0.7 mA/μm | 0.725 mA/μm | 0.75 mA/μm |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, Z.; Yang, Y.; Yu, N.; Liou, J.J. Improving ESD Protection Robustness Using SiGe Source/Drain Regions in Tunnel FET. Micromachines 2018, 9, 657. https://doi.org/10.3390/mi9120657

Yang Z, Yang Y, Yu N, Liou JJ. Improving ESD Protection Robustness Using SiGe Source/Drain Regions in Tunnel FET. Micromachines. 2018; 9(12):657. https://doi.org/10.3390/mi9120657

Chicago/Turabian StyleYang, Zhaonian, Yuan Yang, Ningmei Yu, and Juin J. Liou. 2018. "Improving ESD Protection Robustness Using SiGe Source/Drain Regions in Tunnel FET" Micromachines 9, no. 12: 657. https://doi.org/10.3390/mi9120657