Design and Analysis of Double-Gate MOSFETs for Ultra-Low Power Radio Frequency Identification (RFID): Device and Circuit Co-Design

Abstract

:1. Introduction

2. Background of Ultra-Low Power RFID Design

2.1. General Architecture of RFID Tag

2.2. Scope of Weak or Moderate Inversion for RFID Design

- Increase of the current efficiency (measured by the Gm/ID ratio) which results in a further reduction of the power consumption.

- Decrease of the bias voltages results in lower electrical fields within the device. This avoids velocity saturation and hot electron effects. Having no velocity saturation results in transit frequency scaling as 1/L2 compared to only 1/L when velocity saturation is present. This means that scaling is more effective for devices biased in the weak and moderate inversion region than in strong inversion.

- Having no hot electron effects avoids the increase of the noise excess factor.

- The reduction of the bias voltages better accommodates the use of low supply voltages that are imposed by the scaling of UDSM technologies.

3. Double-Gate MOSFETs (DGMOSFETs) for Ultra-Low Power Subthreshold Circuit Design

3.1. Introduction of Double-Gate MOSFETs (DGMOSFETs)

- Nearly ideal subthreshold slope.

- Small intrinsic gate capacitance.

- Smaller junction capacitances.

- Better immunity to SCEs, although negligible for subthreshold operation.

- Reduced Random dopant fluctuations (RDF) due to undoped or lightly doped body and reduced carrier mobility degradation.

- Higher ION/IOFF ratio.

- Design flexibility at circuit level by symmetric/asymmetric with tied and independent gate options.

3.2. Comparison of Bulk CMOS and DGMOSFETs for Ultra-Low Power Subthreshold Circuit Design

3.2.1. Bulk CMOS and DGMOSFET Device Model Parameters

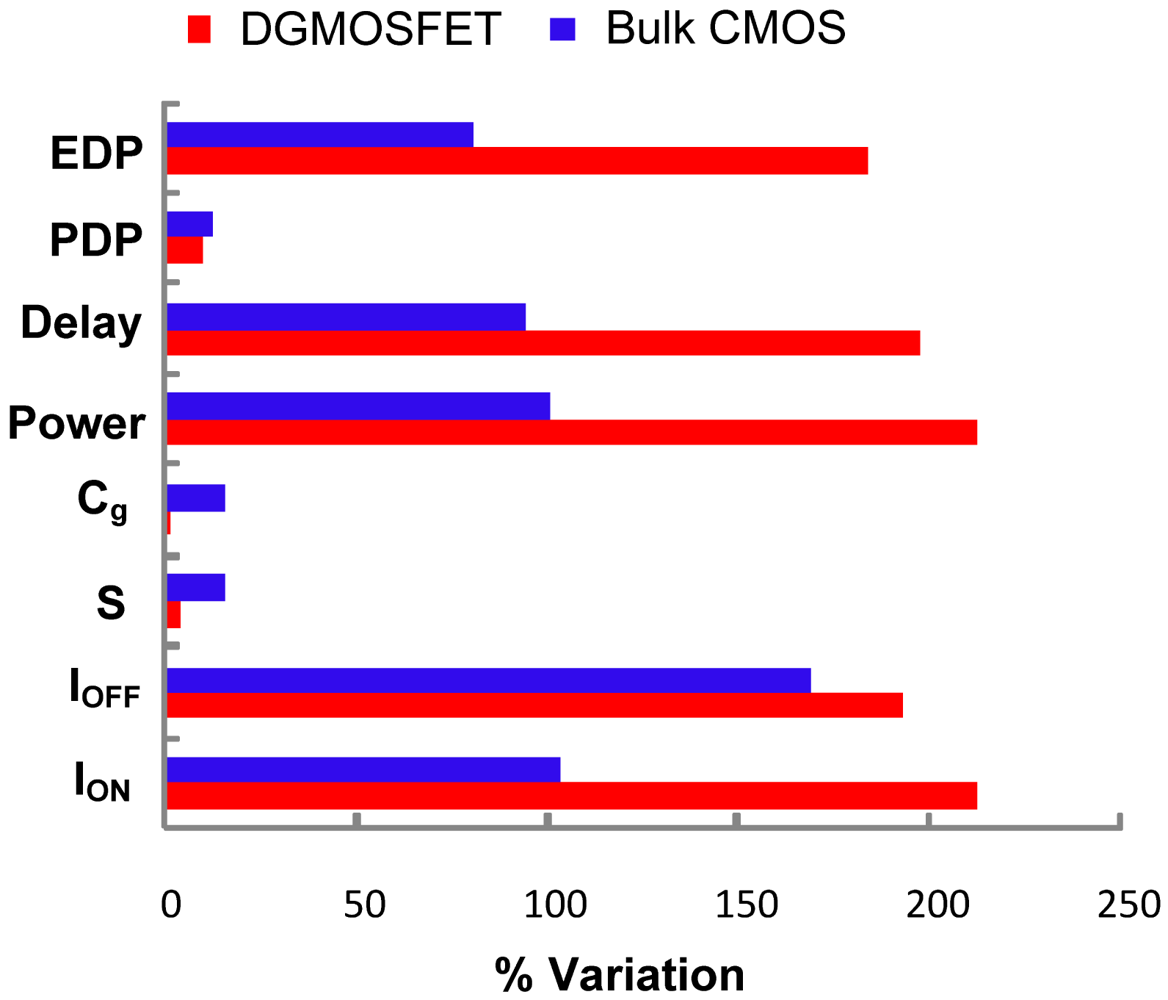

3.2.2. Comparison of Bulk CMOS and DGMOSFETs

4. Comparison of Various DGMOSFET Configurations for Ultra-Low Power Subthreshold Circuit Design

4.1. Introduction of Various DGMOSFET Configurations

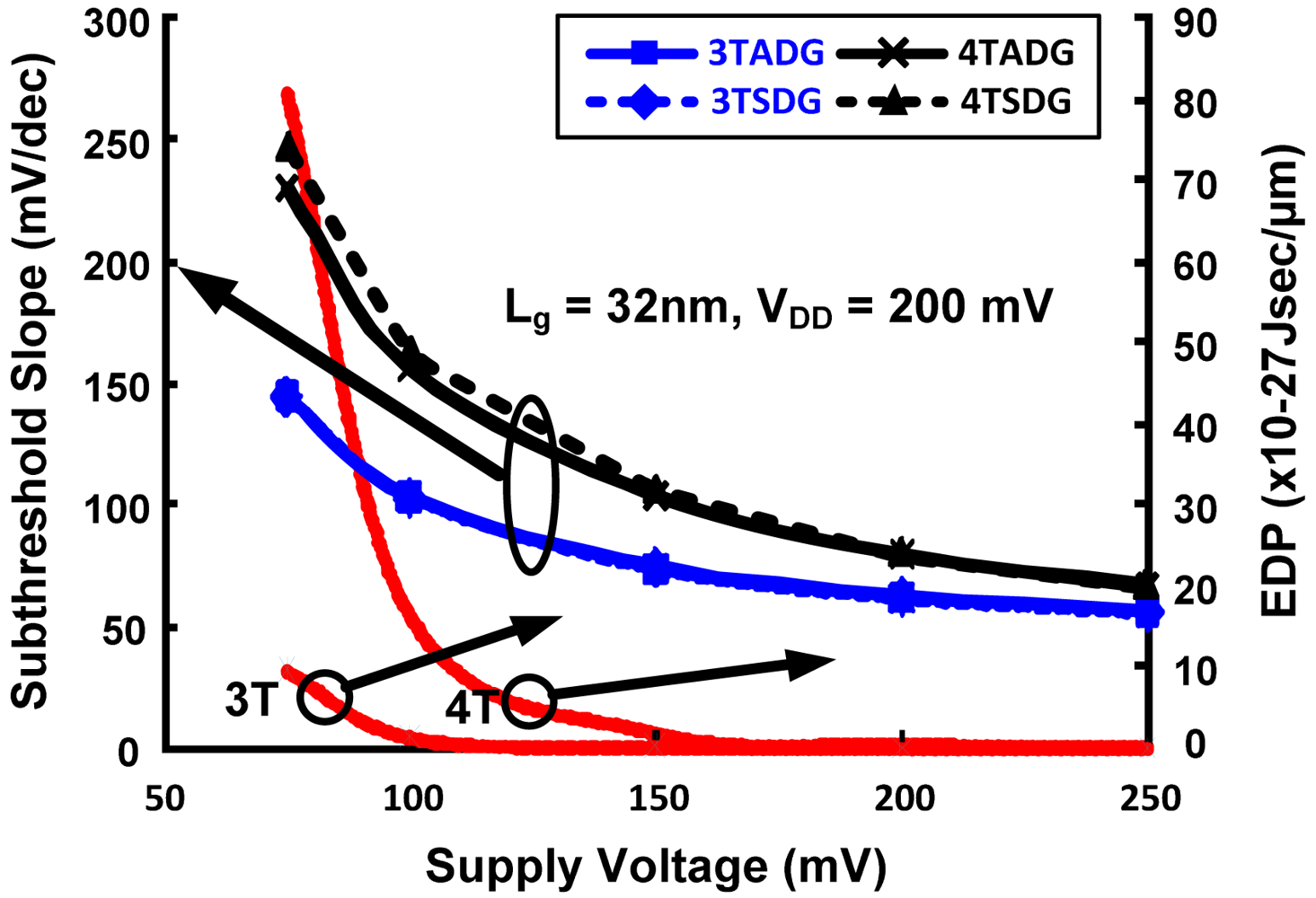

4.2. Comparison of Various DGMOSFET Configurations

4.3. Comparisons of Various DGMOSFET-Based Logic Families

5. Ultra-Low Power RFID Rectifiers with Various DGMOSFET Configurations

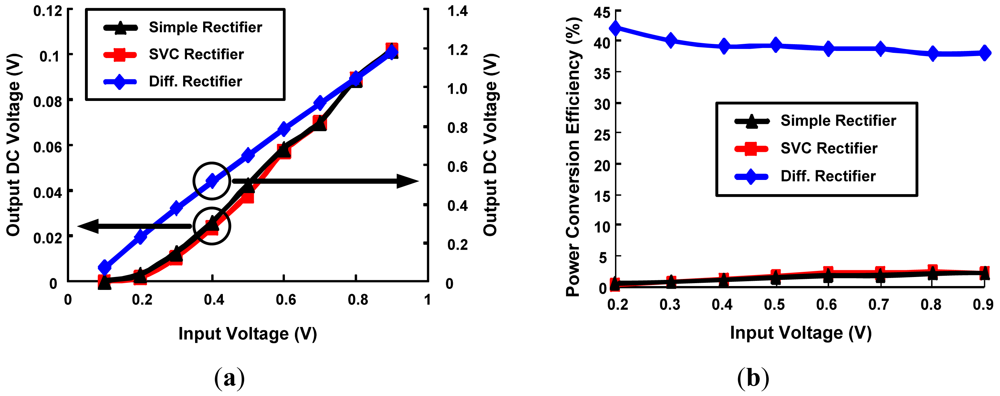

5.1. Various Rectifier Topologies Implemented with DGMOSFETs

5.1.1. Simple Rectifier

5.1.2. Self-Vth Cancellation (SVC) Rectifier

5.1.3. Differential Drive Rectifier

5.2. Comparison of Various RFID Rectifier Topologies Using DGMOSFETs

5.3. Effect of 3T/4T, Symmetric/Asymmetric DGMOSFET Features on Differential Drive Rectifier Topology

6. Conclusions

| Parameter | 32 nm Bulk CMOS | 32 nm DGNMOSFET | 32 nm DGPMOSFET |

|---|---|---|---|

| Leff(nm) | 22 | 22 | 22 |

| Tox(nm) | 1.53 | 1.4 | 1.4 |

| Nch(cm−3) | 3.3 × 1018 | 2 × 1016 | 2 × 1016 |

| Vth(V) | 0.46 | 0.29 | −0.25 |

| Vdd(V) | 0.2 | 0.2 | −0.2 |

| Hfin(nm) | NA | 13 | 13 |

| Tfin(nm) | NA | 8.6 | 8.6 |

| VDD = 0.2 V | Bulk CMOS | DGMOSFET | ||||

|---|---|---|---|---|---|---|

| P × 10−11 (W) | D × 10−9 (s) | PDP × 10−20 (J) | P × 10−9 (W) | D × 10−12 (s) | PDP × 10−20 (J) | |

| CMOS Inv | 2.6 | 1.9 | 5.1 | 1.4 | 10.5 | 1.5 |

| Pseudo NMOS Inv | 46 | 0.7 | 79 | 28 | 1.0 | 27.3 |

| 2 I/p NAND | 8.3 | 7.5 | 62.2 | 1.2 | 3.7 | 43.7 |

| 2 I/p NOR | 8.9 | 8.5 | 75.3 | 2.0 | 2.3 | 45 |

| 2 I/p AND | 17.3 | 47.6 | 823.5 | 1.9 | 9.7 | 181.3 |

| 2 I/p OR | 19.7 | 52.2 | 1029.3 | 2.7 | 4.3 | 117 |

| 2 I/p XOR | 28.4 | 122.6 | 3481.8 | 2.6 | 7.2 | 187.2 |

| 2 I/p XNOR | 32.8 | 216 | 7095.6 | 3.3 | 11.9 | 395.4 |

| Parameter | 3TSDG | 3TADG | 4TSDG | 4TADG |

|---|---|---|---|---|

| (Vfg = Vbg = Vdd, Tfox = Tbox = 1.4 nm) | (Vfg = Vbg = Vdd, Tfox = 1.4 nm, Tbox = 2.8 nm) | (Vfg = Vdd, Vbg = 0, Tfox = Tbox = 1.4 nm) | (Vfg = Vdd, Vbg = 0, Tfox = 1.4 nm, Tbox = 2.8 nm) | |

| ION (μA/μm) | 62.5 | 63.9 | 11.95 | 11.95 |

| IOFF (nA/μm) | 41.98 | 36.2 | 41.98 | 36.2 |

| ION/IOFF | 1495 | 1763 | 286 | 329.74 |

| gm (μS/μm) | 1289 | 1322 | 308.6 | 308.6 |

| Cg (af/μm) | 769.5 | 779.7 | 683 | 683 |

| Power (μW/μm) | 12.9 | 13 | 2.69 | 2.69 |

| Delay factor (ps) | 2.53 | 2.51 | 11.8 | 11.8 |

| PDP factor(aJ/μm) | 32.64 | 32.63 | 31.7 | 31.7 |

| EDP factor (aJ.ps/μm) | 82.6 | 81.9 | 374 | 374 |

| 3TSDG | 3TADG | |||||

|---|---|---|---|---|---|---|

| P 10−9 (w) | D 10−12 (s) | PDP 10−21 (J) | P 10−9 (w) | D 10−12(s) | PDP 10−21 (J) | |

| CMOS Inv | 0.72 | 1.637 | 1.178 | 0.621 | 1.55 | 0.962 |

| 2 I/p NAND | 1.18 | 3.7 | 4.366 | 1.02 | 3.26 | 3.325 |

| 2 I/p AND | 1.86 | 9.75 | 18.135 | 1.6 | 9 | 14.4 |

| 2 I/p NOR | 1.97 | 2.28 | 4.5 | 1.7 | 2.2 | 3.74 |

| 2 I/p OR | 2.72 | 4.3 | 11.7 | 2.35 | 4.15 | 9.75 |

| 2 I/p XOR | 2.6 | 7.2 | 18.72 | 2.24 | 6.85 | 15.34 |

| 2 I/p XNOR | 3.32 | 11.91 | 39.54 | 2.9 | 11.37 | 32.97 |

| Half adder | 6.5 | 9.1 | 59.2 | 5.64 | 8.7 | 49.1 |

| Full adder | 312 | 70 | 21840 | 312 | 69.6 | 21715 |

| 2 × 1 Mux | 0.88 | 2.8 | 2.5 | 0.76 | 2.6 | 2.0 |

| 4 × 1 Mux | 2 | 16.8 | 33.6 | 1.74 | 15.9 | 27.7 |

| 4TSDG | 4TADG | |||||

|---|---|---|---|---|---|---|

| P 10−9 (w) | D 10−9 (s) | PDP 10−18 (J) | P 10−9 (w) | D 10−9 (s) | PDP 10−18 (J) | |

| CMOS Inv | 68.23 | 2.2 | 150.1 | 67.9 | 2.2 | 149.38 |

| 2 I/p NAND | 136 | 2.3 | 312.8 | 135.3 | 2.3 | 311.2 |

| 2 I/p AND | 206 | 8.3 | 1709.8 | 205.8 | 8.27 | 1702 |

| 2 I/p NOR | 69 | 2.22 | 153.2 | 68.5 | 2.2 | 150.7 |

| 2 I/p OR | 139 | 4.2 | 584 | 138 | 4.2 | 579.6 |

| 2 I/p XOR | 185 | 4.8 | 888 | 185 | 4.72 | 873.2 |

| 2 I/p XNOR | 275 | 9.5 | 2612.5 | 275 | 9.4 | 2585 |

| Half adder | 341 | 108.3 | 36930 | 341 | 108.2 | 36896 |

| Full adder | 1017 | 660 | 671220 | 1017 | 655 | 666135 |

| 2 × 1 Mux | 68.7 | 39.1 | 2686 | 68.8 | 39 | 2683 |

| 4 × 1 Mux | 140 | 155 | 21700 | 140 | 152 | 21280 |

| Logic Style | 3TSDG | 3TADG | 4TSDG | ||||||

|---|---|---|---|---|---|---|---|---|---|

| P (nW) | D (ps) | PDP (10−21 J) | P (nW) | D (ps) | PDP (10−21 J) | P (nW) | D (ns) | PDP (10−18 J) | |

| Sub-static CMOS | 1.2 | 3.7 | 4.44 | 1.0 | 3.3 | 3.3 | 136 | 2.3 | 313 |

| Sub-pseudo NMOS | 253 | 1.13 | 286.3 | 258 | 1.16 | 299.3 | 242 | 1.7 | 411.4 |

| Sub-CPL | 1.72 | 21.3 | 36.6 | 1.76 | 22.4 | 39.4 | 155 | 54.5 | 8447 |

| Sub-Domino | 1.06 | 10.2 | 10.8 | 0.97 | 12.1 | 11.7 | 83.7 | 3 | 251 |

| Sub-DCVSL | 3.2 | 5.7 | 18.2 | 3.2 | 5.7 | 18.2 | 282 | 0.9 | 254 |

| Sub-DCVSPG | 3.4 | 54.9 | 186.7 | 2.9 | 54.9 | 159.2 | 202 | 47.6 | 9615 |

| RF Input (V) | 3T Min. Size | 3T Upsize | 4T Min. Size | 4T Upsize | ||||

|---|---|---|---|---|---|---|---|---|

| DC Output Level (V) | DC Power (μw) | DC Output Level (V) | DC Power (μw) | DC Output Level (V) | DC Power (μw) | DC Output Level (V) | DC Power (μw) | |

| 0.1 (small) | 0.07 | 0.5 | 0.12 | 1.5 | 0.063 | 0.4 | 0.08 | 0.7 |

| 0.9 (large) | 1.18 | 138.8 | 1.72 | 295.7 | 0.84 | 70.7 | 1.16 | 138.4 |

References

- Chen, C.; Sarrafzadeh, M. Simultaneous voltage scaling and gate sizing for low-power design. IEEE Trans. Circuits Syst. 2002, 49, 400–408. [Google Scholar]

- Kim, C.H.; Roy, K. Dynamic VTH Scaling Scheme for Active Leakage Power Reduction. Proceedings of the Design, Automation Test Europe Conference and Exhibition, Paris, France, 4–8 March 2002; pp. 163–167.

- Agarwal, A.; Li, H.; Roy, K. A single V low-leakage gated- ground cache for deep submicron. IEEE J. Solid-State Circuits 2003, 38, 319–328. [Google Scholar]

- Palumbo, G.; Pappalardo, F.; Sannella, S. Evaluation on Power Reduction Applying Gated Clock Approaches. Proceedings of the 2002 IEEE International Symposium on Circuits and Systems, New York, NY, USA, 2002; 4, pp. 85–88.

- Cao, Y.; Hu, C.; Huang, X.; Kahng, A.B.; Muddu, S.; Stroobandt, D.; Sylvester, D. Effects of global Interconnect Optimizations on Performance Estimation of deep Submicron Design. Proceedings of the IEEE/ACM International Conference on Computer Aided Design (ICCAD2000), San Jose, CA, USA, 5–9 November 2000; pp. 56–61.

- Katkoori, S.; Alupoaei, S. RT-level Interconnect Optimization in DSM Regime. Proceedings of the IEEE Computer Society Workshop VLSI, 2000, Orlando, FL, USA, 27–28 April 2000; pp. 143–148.

- Entrena, L.; Lopez, C.; Olias, E.; Millan, E.S.; Espejo, J.A. Logic Optimization of Unidirectional Circuits with Structural Methods. Proceedings of the Seventh International on-Line Testing Workshop, Taormina, Italy, 9–11 July 2001; pp. 43–47.

- Millan, E.S.; Entrena, L.; Espejo, J.A. On the Optimization Power of Redundancy Addition and Removal for Sequential Logic Optimization. Proceedings of the Euromicro Symposium on Digital Systems, Design, Warszawa, Poland, 4–6 September 2001; pp. 292–299.

- Ramirez, R.J. Variability-aware design of subthreshold devices. Master Thesis, Electrical and Computer Engineering Department, University of Waterloo, Waterloo, Canada, 2007. [Google Scholar]

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, UK, 1998. [Google Scholar]

- Vittoz, E.; Fellrath, J. CMOS analog integrated circuits based on weak inversion operation. IEEE J. Solid-State Circuits 1977, 12, 224–231. [Google Scholar]

- Ramesh, V.; Dasgupta, S.; Agarwal, R.P. SDG vs. ADG with Tied and Independent gate Options in the Subthreshold Logic for Ultra Low Power Applications. Proceedings of the 2nd International Workshop on Electron Devices and Semiconductor Technology (IEDST '09), Bombay, India, 1–2 June 2009.

- Soeleman, H.; Roy, K. Digital CMOS Logic Operation in the Sub-Threshold Region. Proceedings of the Tenth Great Lakes Symposium on VLSI, Chicago, IL, USA, March 2000; pp. 107–112.

- Ramesh, V.; Dasgupta, S.; Agarwal, R.P. Device and Circuit Co-Design Robustness Studies in the Sub-Threshold Logic for Ultra Low Power Applications for 32 nm CMOS. IEEE Trans. Electron Devices 2010, 57, 654–664. [Google Scholar]

- Wang, A.; Chandrakasan, A. A 180-mv subthreshold FFT Processor Using a Minimum Energy Design Methodology. IEEE J. Solid-State Circuits 2005, 40, 310–319. [Google Scholar]

- Ramesh, V.; Dasgupta, S.; Agarwal, R.P. Investigation of Robustness and Performance Comparisons of DG-FinFETs with Symmetric, Asymmetric, Tied and Independent gate options for Optimal Subthreshold Logic. Proceedings of the IEEE 4th International Conference on Computers & Devices for Communication (CODEC), Calcutta, India, 14–16 December 2009.

- Zhai, B.; Nazhandali, L.; Olson, J.; Reeves, A.; Minuth, M.; Helfand, R.; Pant, S.; Blaauw, D.; Austin, T. A 2.60pj/inst Subthreshold Sensor Processor for Optimal Energy Efficiency. Proceedings of the 2006 Symposium on VLSI Circuits, Honolulu, HI, USA, June 2006; pp. 154–155.

- Lee, T.H. The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed.; Cambridge University Press: Cambridge, UK, 1998. [Google Scholar]

- Wu, S.M.; Yang, J.R.; Liu, T.Y. A Transponder IC for Wireless Identification Systems. Proceedings of the 7th International Symposium on Personal, Indoor, and Mobile Communications (PIMRC '96), Taipei, Taiwan, 15–18 October 1996; 1, pp. 238–241.

- Masui, S.; Ishii, E.; Iwawaki, T.; Sugawara, Y.; Sawada, K. A 13.56-MHz CMOS RF Identification Transponder Integrated Circuit with a Dedicated CPU. Proceedings of the 1999 IEEE International Solid-State Circuits Conference (ISSCC '99), San Francisco, CA, USA, 15–17 February 1999; pp. 162–163.

- Rao, K.V.S.; Heinrich, H.; Martinez, R. High Performance UHF RFID Tags. Proceedings of the 3rd Workshop on Automatic Identification Advanced Technologies, Tarrytown, NY, USA, March 2002.

- Karthaus, U.; Fischer, M. Fully integrated passive UHF RFID transponder with 16.7 mu-W minimum RF input power. IEEE J. Solid-State Circuits 2003, 38, 1602–1608. [Google Scholar]

- Glidden, R.; Bockorick, C.; Cooper, S.; Diorio, C.; Dressler, D.; Gutnik, V.; Hagen, C.; Hara, D.; Hass, T.; Humes, T.; et al. Design of ultra-low-cost UHF RFID tags for supply chain applications. IEEE Commun. Mag. 2004, 42, 140–151. [Google Scholar]

- Vita, G.D.; Lannaccone, G. Design Criteria for the RF Section of Long Range Passive RFID systems. Proceedings of the Norchip Conference, Oslo, Norway, 8–9 November 2004; pp. 107–110.

- Curty, J.P.; Joehl, N.; Dehollain, C.; Declercq, M.J. Remotely powered addressable UHF RFID integrated system. IEEE J. Solid-State Circuits 2005, 40, 2193–2202. [Google Scholar]

- Kocer, F.; Flynn, M.P. A Long-Range RFID IC with On-Chip ADC in 0.25 μm CMOS. Proceedings of the 2005 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Long Beach, CA, USA, 12–14 June 2005; 12–14, pp. 361–364.

- Yeoh, W.G.; Choi, Y.B.; Tham, K.Y.; Diao, S.X.; Li, Y.S. A CMOS 2.45-GHz Radio Frequency Identification Tag IC with Read/Write Memory. Proceedings of the 2005 IEEE Radio Frequency integrated Circuits (RFIC) Symposium, Long Beach, CA, USA, 12–14 June 2005; pp. 365–368.

- Jamali, B.; Ranasinghe, D.C.; Cole, P.H. Analysis of UHF RFID CMOS rectifier structures and input impedance characteristics. Proc. SPIE 2005, 6035, 313–323. [Google Scholar]

- Umeda, T.; Yoshida, H.; Sekine, S.; Fujita, Y.; Suzuki, T.; Otaka, S. A 950-MHz rectifier circuit for sensor network tags with 10-m distance. IEEE J. Solid-State Circuits 2006, 40, 35–41. [Google Scholar]

- Kranti, A.; Armstrong, G.A. Nonclassical channel design in MOSFETs for improving OTA gain-bandwidth trade-off. IEEE Trans. Circuits Syst. I 2010, 57, 3048–3054. [Google Scholar]

- Kumar, A.; Tiwari, S. A Power-Performance Adaptive Low Voltage Analog Circuit Design Using Independently Controlled Double Gate CMOS Technology. Proceedings of the 2004 International Symposium on Circuits and Systems (ISCAS '04), Vancouver, Canada, 23–26 May 2004; pp. 197–200.

- Freitas, P.; Billio, G.; Lapuyade, H.; Begueret, J.B. Analog Design Considerations for Independently Driven Double Gate MOSfets and Their Application in a Low-Voltage OTA. Proceedings of the 14th IEEE International Conference on Electronics, Circuits and Systems, Marrakech, Morocco, 11–14 December 2007; pp. 198–201.

- Mohankumar, N.; Syamal, B.; Sarkar, C.K. Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs. IEEE Trans. Electron Devices 2010, 57, 82–86. [Google Scholar]

- Sekigawa, T.; Hayashi, Y. Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate. Solid-State Electron. 1984, 27, 827–828. [Google Scholar]

- Hisamoto, D.; Kaga, T.; Kawamoto, Y.; Takeda, E. A fully depleted lean channel transistor (DELTA)-a novel vertical ultra thin SOI MOSFET. IEEE Electron Device Lett. 1990, 11, 36–38. [Google Scholar]

- Colinge, J.P.; Gao, M.H.; Romano, A.; Maes, H.; Claeys, C. Silicon-on Insulator Gate-all-around Device. Proceedings of the 1990 IEEE SOS/SOI Technology Conference, Key West, FL, USA, 2–4 October 1990; pp. 137–138.

- Jurczak, M.; Skotnicki, T.; Paoli, M.; Tormen, B.; Martins, J.; Regolini, J.L.; Dutartre, D.; Ribot, P.; Lenoble, D.; Pantel, R.; et al. Silicon-on-Nothing (SON)-an innovative process for advanced CMOS. IEEE Trans. Electron Devices 2000, 47, 2179–2187. [Google Scholar]

- Harrison, S.; Coronel, P.; Leverd, F.; Cerutti, R.; Palla, R.; Delille, D.; Borel, S.; Jullian, S.; Pantel, R.; Descombes, S.; et al. Highly Performant Double Gate MOSFET Realized with SON Process. Proceedings of the IEEE International Electron Devices Meeting (IEDM '03), Washington, DC, USA, 8–10 December 2003; pp. 18.6.1–18.6.4.

- Pretet, J.; Monfray, S.; Cristoloveanu, S.; Skotnicki, T. Silicon-on-nothing MOSFETs: Performance, short-channel effects, and backgate coupling. IEEE Trans. Electron Devices 2004, 51, 240–245. [Google Scholar]

- Liu, Y.; Ishii, K.; Tsutsumi, T.; Masahara, M.; Suzuki, E. Ideal rectangular cross-section Si-Fin channel double-gate MOSFETs fabricated using orientation-dependent wet etching. IEEE Electron Device Lett. 2003, 24, 484–486. [Google Scholar]

- Hiramoto, T. Nano-scale silicon MOSFET Towards non-traditional and quantum devices. Proceedings of the IEEE International SOI Conference, Maui, HI, USA, October 2001; pp. 8–10.

- Jiao, Z.; Salama, A.T. A fully depleted delta channel SOI NMOSFET. Proc. Electro chem. Soc. 2001, 3, 403. [Google Scholar]

- Singh, N.; Agarwal, A.; Bera, L.K.; Liow, T.Y.; Yang, R.; Rustagi, S.C.; Tung, C.H.; Kumar, R.; Lo, G.Q.; Balasubramanian, N.; et al. High performance fully depleted silicon nanowire (diameter < 5 nm) gate-allaround CMOS devices. IEEE Electron Device Lett. 2006, 27, 383–385. [Google Scholar]

- Moselund, K.E.; Dainesi, P.; Declercq, M.; Bopp, M.; Coronel, P.; Skotnicki, T.; Ionescu, A.M. Compact gate-all-around silicon light modulator for ultra high speed operation. Sens. Actuators A 2006, 130–131, 220–227. [Google Scholar]

- Castellani-Coulie, K.; Munteanu, D.; Autran, J.L.; Ferlet-Cavrois, V.; Paillet, P.; Baggio, J. Investigation of 30 nm gate-all-around MOSFET sensitivity to heavy ions: A 3-D simulation study. IEEE Trans. Nucl. Sci. 2006, 53, 1950–1954. [Google Scholar]

- Lemme, M.C.; Mollenhauer, T.; Henschel, W.; Wahlbrink, T.; Baus, M.; Winkler, O.; Granzner, R.; Schwierz, F.; Spangenberg, B.; Kurz, H. Subthreshold behavior of triple-gate MOSFETs on SOI Material. Solid State Electronics 2004, 48, 529–534. [Google Scholar]

- Baie, X.; Colinge, J.P.; Bayot, V.; Grivei, E. Quantum-wire effects in thin and narrow SOI MOSFETs. Proceedings of the IEEE International SOI Conference, Tucson, AZ, USA; 1995; pp. 66–67. [Google Scholar]

- Colinge, J.P.; Baie, X.; Bayot, V.; Grivei, E. A silicon-on-insulator quantum wire. Solid-State Electron. 1996, 39, 49–51. [Google Scholar]

- Chau, R.; Doyle, B.; Kavalieros, J.; Barlage, D.; Murthy, A.; Doczy, M.; Arghavani, R.; Datta, S. Advanced Depleted-Substrate Transistors: Single-gate, Double-Gate and Tri-Gate. Proceedings of the 2002 International Conference on Solid State Devices and Materials (SSDM 2002), Nagoya, Japan, 17–19 September 2002; pp. 68–69.

- Doyle, B.S.; Datta, S.; Doczy, M.; Jin, B.; Kavalieros, J.; Linton, T.; Murthy, A.; Rios, R.; Chau, R. High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Device Lett. 2003, 24, 263–265. [Google Scholar]

- Miyano, S.; Hirose, M.; Masuoka, F. Numerical analysis of a cylindrical thin pillar transistor (CYNTHIA). IEEE Trans. Electron Devices 1992, 39, 1876–1881. [Google Scholar]

- Ohba, T.; Nakamura, H.; Sakuraba, H.; Masuoka, F. A novel tri-control gate surrounding gate transistor (TCG-SGT) nonvolatile memory cell for flash memory. Solid-State Electron. 2005, 50, 924–928. [Google Scholar]

- Nitayama, A.; Takato, H.; Okabe, N.; Sunouchi, K.; Hieda, K.; Horiguchi, F.; Masuoka, F. Multi-pillar surrounding gate transistor (M-SGT) for compact and high-speed circuits. IEEE Trans. Electron Devices 1991, 38, 579–583. [Google Scholar]

- Passi, V.; Olbrechts, B.; Raskin, J.P. Fabrication of a Quadruple Gate MOSFET in Silicon-on-Insulator Technology. Proceedings of the NATO Advanced Research Workshop on Nanoscaled Semiconductor-on-Insulator Structures and Devices, Big Yalta, Ukraine, 15–19 October 2006; pp. 11–12.

- Dufrene, B.; Akarvardar, K.; Cristoloveanu, S.; Blalock, B.J.; Gentil, P.; Kolawa, E.; Mojarradi, M.M. Investigation of the four-gate action in G4–FETs. IEEE Trans. Electron Devices 2004, 51, 1931–1935. [Google Scholar]

- Lee, H.; Yu, L.E.; Ryu, S.W.; Han, J.W.; Jeon, K.; Jang, D.Y.; Kim, K.H.; Lee, J.; Kim, J.H.; Jeon, S.C.; et al. Sub-5 nm All-Around Gate FinFET for Ultimate Scaling. Proceedings of the 2006 Symposium on VLSI Circuits, Honolulu, HI, USA, June 2006.

- Singh, N.; Lim, F.Y.; Fang, W.W.; Rustagi, S.C.; Bera, L.K.; Agarwal, A.; Tung, C.H.; Hoe, K.M.; Omampuliyur, S.R.; Tripathi, D.; et al. Ultra-narrow silicon nanowire gate-allaround CMOS device: Impact of diameter, channel-orientation and low temperature on device performance. Proceedings of the International Electron Devices Meeting (IEDM '06), San Francisco, CA, USA, 11–13 December 2006; pp. 1–4.

- Colinge, J.P.; Chandrakasan, A. FinFETs and Other Multi-Gate Transistors (Integrated Circuits and Systems); Springer: Berlin, Germany, 2008. [Google Scholar]

- Chang, L.; Choi, Y.K.; Ha, D.; Ranade, P.; Xiong, S.; Bokor, J.; Hu, C.; King, T.J. Extremely scaled silicon nano CMOS devices. Proc. IEEE 2003, 91, 1860–1873. [Google Scholar]

- Wong, H.S.P.; Frank, D.J.; Solomon, P.M. Device Design Considerations for Double-Gate, Ground-Plane, Single-Gated Ultra-Thin SOI MOSFET at the 25 nm Channel Length Generation. Proceedings of the International Electron Devices Meeting (IEDM '98), San Francisco, CA, USA, 6–9 December 1998; pp. 407–410.

- Nowak, E.J.; Aller, I.; Ludwig, T.; Kim, K.; Joshi, R.V.; Chuang, C.T.; Bernstein, K.; Puri, R. Turning silicon on its edge. IEEE Circuits Device Mag. 2004, 20, 20–31. [Google Scholar]

- Tang, S.H.; Chang, L.; Lindert, N.; Kyu, C.Y.; Lee, W.C.; Huang, X.; Subramanian, V.; Bokor, J.; King, T.J.; Hu, C. FinFET-a Quasi-Planar Double-Gate MOSFET. Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC 2001), San Francisco, CA, USA, 5–7 February 2001; pp. 118–119.

- Fried, D.; Nowak, E.; Kedzierski, J.; Dusterr, J.; Kornegay, K. A Fin-Type Independent-Double-Gate NFET. Proceedings of the 61st Device Research Conference, Salt Lake, UT, USA, 23–25 June 2003; pp. 45–46.

- Mathew, L.; Du, Y.; Thean, A.V.Y.; Sadd, M.; Vandooren, A.; Parker, C.; Stephens, T.; Mora, R.; Rai, R.; Zavala, M.; et al. CMOS vertical multiple independent gate field effect transistors (MIGFET). 2004, 187–188. [Google Scholar]

- Mukhopadhyay, S.; Mahmoodi, H.; Roy, K. Design of High Performance Sense Amplifier Using Independent Gate Control in Sub-50 nm Double-Gate MOSFET. Proceedings of the 6th International Symposium on Quality Electronic Design (ISQED 2005), San Jose, CA, USA, 21–23 March 2005; pp. 490–495.

- Mahmoodi, H.; Mukhopadhyay, S.; Roy, K. High performance and low power domino logic using independent gate control in double-gate SOI MOSFETs. Proceedings of the IEEE International SOI Conference, Charleston, SC, USA; 2004; pp. 67–68. [Google Scholar]

- Cakici, T.; Mahmoodi, H.; Mukhopadhyay, S.; Roy, K. Independent Gate Skewed Logic in Double-Gate SOI Technology. Proceedings of the 2005 IEEE International SOI Conference, Honolulu, HI, USA, 3–6 October 2005; pp. 83–84.

- Cakici, T.; Bansal, A.; Roy, K. A low power four transistor Schmitt Trigger for asymmetric double gate fully depleted SOI devices. Proceedings of the IEEE International SOI Conference, Newport Beach, CA, USA; 2003; pp. 21–22. [Google Scholar]

- International Technology Roadmap for Semiconductors. Available online: http://public.itrs.net/ (accessed on 29 June 2011).

- Kim, J.J.; Roy, K. Double gate-MOSFET sub-threshold circuit for ultralow power applications. IEEE Trans. Electron Devices 2004, 51, 1468–1474. [Google Scholar]

- Ramesh, V.; Dasgupta, S.; Agarwal, R.P. Robustness comparison of DG-FinFETs with symmetric, asymmetric, tied and independent gate options with circuit co-design for ultra low power subthreshold logic. Microelectron. J. 2010, 41, 195–211. [Google Scholar]

- Paul, B.; Bansal, A.; Roy, K. Underlap DGMOS for digital sub-threshold operation. IEEE Trans. Electron Devices 2006, 53, 910–913. [Google Scholar]

- Ramesh, V.; Dasgupta, S.; Agarwal, R.P. Robust and ultra low power subthreshold logic circuits with symmetric, asymmetric, 3T, 4T DGFinFETs. J. Low Power Electron. 2010, 6, 103–114. [Google Scholar]

- Feng, X.W.; Xie, W.Y. Analysis of subthreshold FinFET Circuits for ultra low power design. Proceedings of the IEEE International SOI Conference, Niagara Falls, NY, USA, 2006; pp. 91–92.

- Ramesh, V.; Dasgupta, S.; Agarwal, R.P. PVT variation sensitivity comparisons of nano scale CMOS and 3T-4T double gate FinFETs for robust and ultra low power subthreshold logic. J. IET Circuits Devices Syst. 2010, 4, 548–560. [Google Scholar]

- Roy, K.; Mahmoodi, H.; Mukhopadhyay, S.; Ananthan, H.; Bansal, A.; Cakici, T. Double-Gate SOI Devices for Low-Power and High-Performance Applications. Proceedings of the 19th International Conference on VLSI Design (VLSID 2006), Hyderabad, India, January 2006.

- Hanson, S.; Seok, M.; Sylvester, D.; Blaauw, D. Nanometer device scaling in subthreshold logic and SRAM. IEEE Trans. Electron Devices 2008, 55, 175–185. [Google Scholar]

- Predictive Technology Model (PTM). Available online: http://ptm.asu.edu/ (accessed on 29 June 2011).

- Zhao, W.; Cao, Y. Predictive technology model for nano-CMOS design exploration. J. Emerg. Technol. Comput. Syst. 2007, 3, 1–17. [Google Scholar]

- Umeda, T.; Yoshida, H.; Sekine, S.; Fujita, Y.; Suzuki, T.; Otaka, S. A 950-MHz rectifier circuit for sensor network tags with 10-m distance. IEEE J. Solid-State Circuits 2006, 41, 35–41. [Google Scholar]

- Nakamoto, H.; Yamazaki, D.; Yamamoto, T.; Kurata, H.; Yamada, S.; Mukaida, K.; Ninomiya, T.; Ohkawa, T.; Masui, S.; Gotoh, K. A passive UHF RF identification CMOS tag IC using ferroelectric RAM in 0.35-μm technology. IEEE J. Solid-State Circuits 2007, 42, 101–110. [Google Scholar]

- Kotani, K.; Ito, T. High Efficiency CMOS Rectifier Circuit with Self-Vth-Cancellation and Power Regulation Functions for UHF RFIDs. Proceedings of the IEEE Asian Solid-State Circuits Conference (ASSCC '07), 12–14 November 2007; pp. 119–122.

- Kotani, K.; Ito, T. Self-Vth-cancellation high-efficiency CMOS rectifier circuit for UHF RFIDs. IEICE Trans. Electron. 2009, E92-C, 153–160. [Google Scholar]

- Sasaki, A.; Kotani, K.; Ito, T. Differential-Drive CMOS Rectifier for UHF RFIDs with 66% PCE at 12 dBm Input. Proceedings of the IEEE Asian Solid-State Circuits Conference (ASSCC '08), Fukuoka, Japan, 3–5 November 2008; pp. 105–108.

© 2011 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Vaddi, R.; Agarwal, R.P.; Dasgupta, S.; Kim, T.T. Design and Analysis of Double-Gate MOSFETs for Ultra-Low Power Radio Frequency Identification (RFID): Device and Circuit Co-Design. J. Low Power Electron. Appl. 2011, 1, 277-302. https://doi.org/10.3390/jlpea1020277

Vaddi R, Agarwal RP, Dasgupta S, Kim TT. Design and Analysis of Double-Gate MOSFETs for Ultra-Low Power Radio Frequency Identification (RFID): Device and Circuit Co-Design. Journal of Low Power Electronics and Applications. 2011; 1(2):277-302. https://doi.org/10.3390/jlpea1020277

Chicago/Turabian StyleVaddi, Ramesh, Rajendra P. Agarwal, Sudeb Dasgupta, and Tony T. Kim. 2011. "Design and Analysis of Double-Gate MOSFETs for Ultra-Low Power Radio Frequency Identification (RFID): Device and Circuit Co-Design" Journal of Low Power Electronics and Applications 1, no. 2: 277-302. https://doi.org/10.3390/jlpea1020277