Analysis of Dynamic Differential Swing Limited Logic for Low-Power Secure Applications

Abstract

:1. Introduction

- have performances (speed and power) in the range of standard CMOS, with significant security improvement,

- achieve a security level similar to previously introduced DDL styles, with significant perfor- mance improvement.

- or according to their nature as random (due to random dopant fluctuation (RDF), line edge roughness (LER), etc.) , environmental (such as supply and temperature variations) and systematic (for example well proximity effects and wire thickness variation) [26].

2. Dynamic Differential Swing Limited Logic (DDSLL)

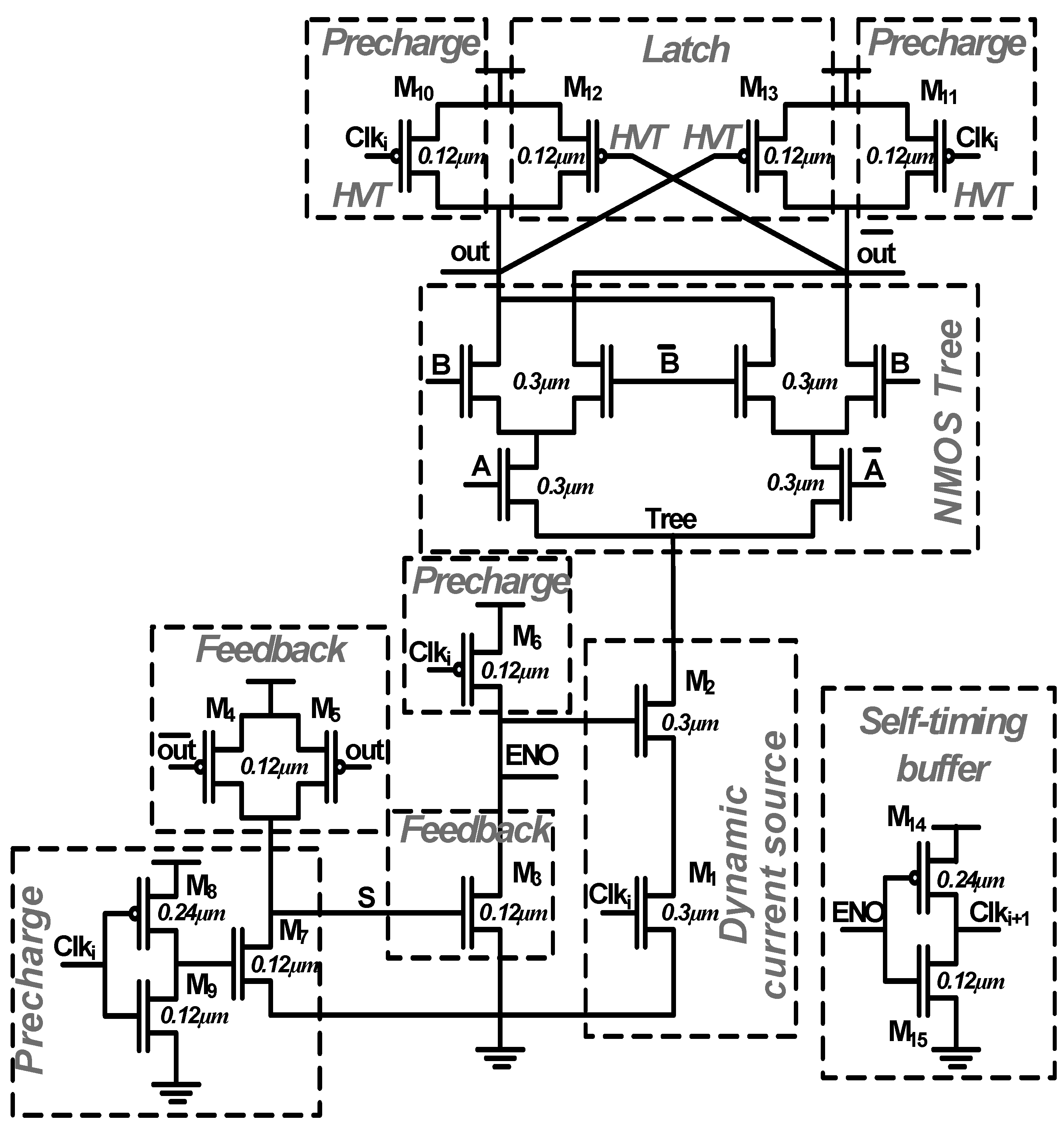

2.1. DDSLL Circuit Topology

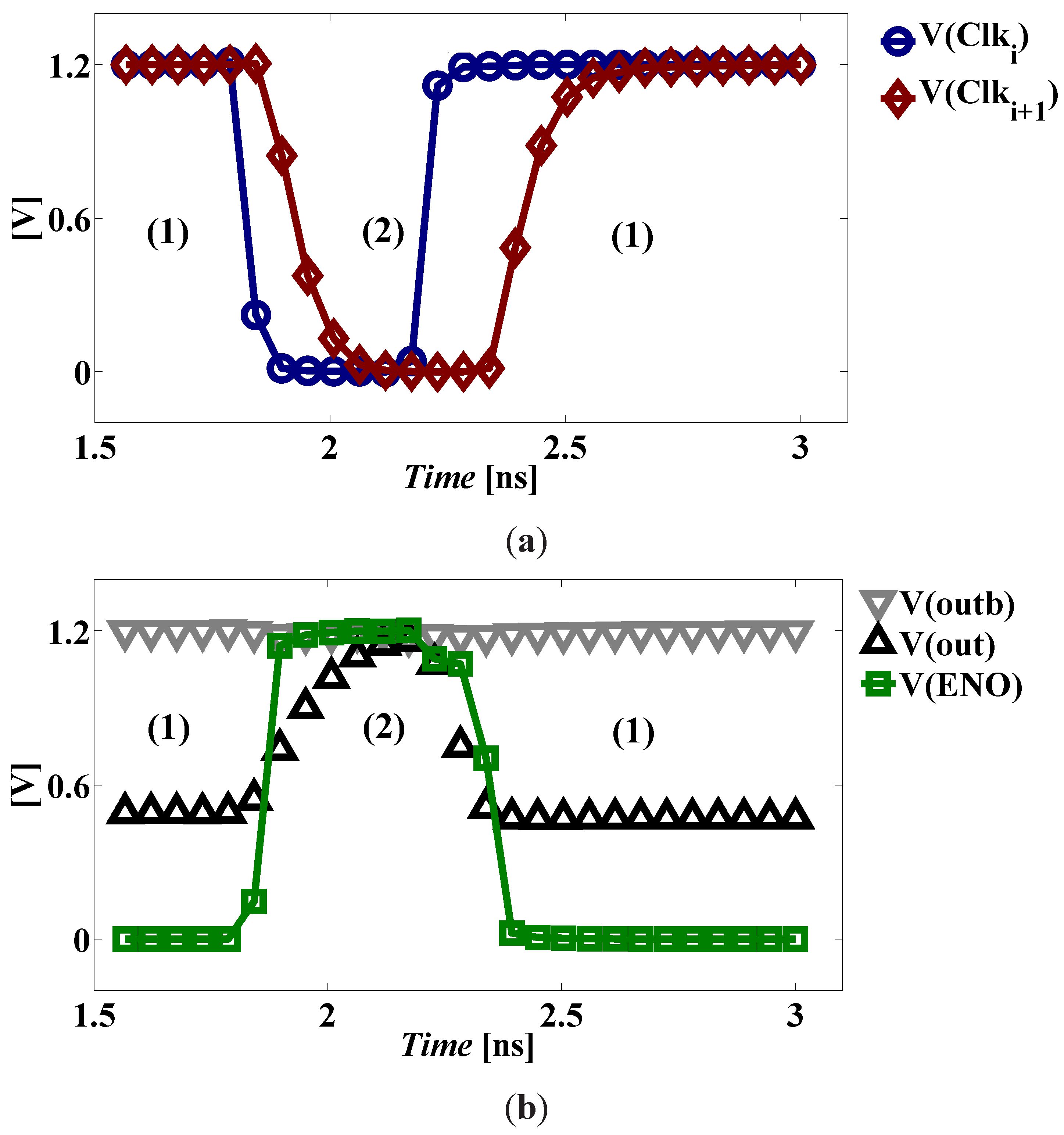

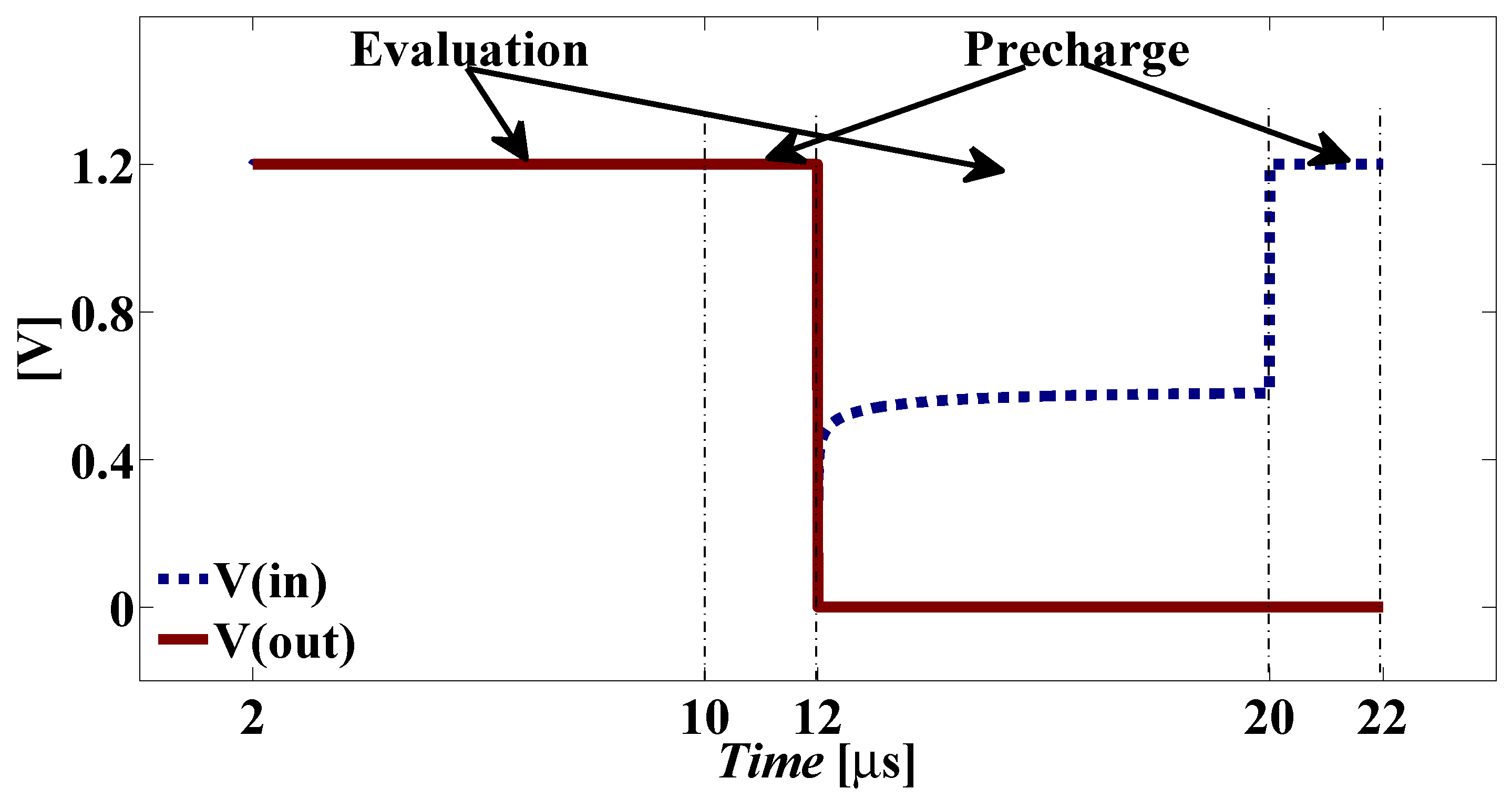

2.2. DDSLL Functional Operation

2.3. DDSLL Circuit Design

- The precharge, latch, feed-back circuits and the self-timing buffer are designed using minimum feature size transistors (W = 0.12 µm) to reduce the power consumption except for the PMOS transistors in the inverters of the precharge circuit and self-timing buffer (W = 0.24 µm) to maintain the duty cycle of the input clock.

- The dynamic current source uses wider transistors (W = 0.3 µm) in order to drive sufficient current from the NMOS tree during the evaluation period providing the desired output voltage swing.

- The NMOS tree is also designed with wider transistors (W = 0.3 µm) for two reasons; the first is to increase the output voltage swing and the second to reduce the effect of WID variability on the output voltage swing.

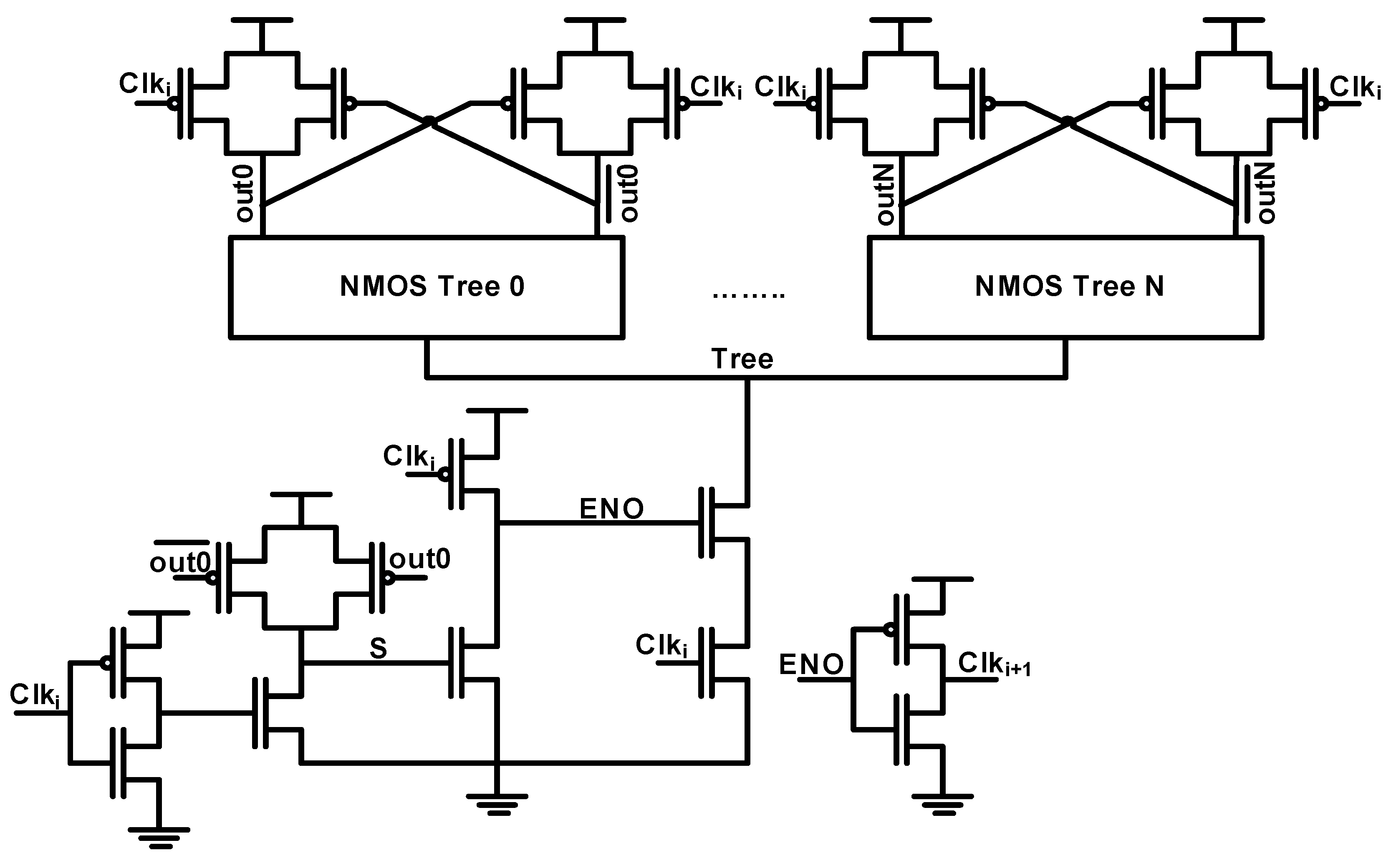

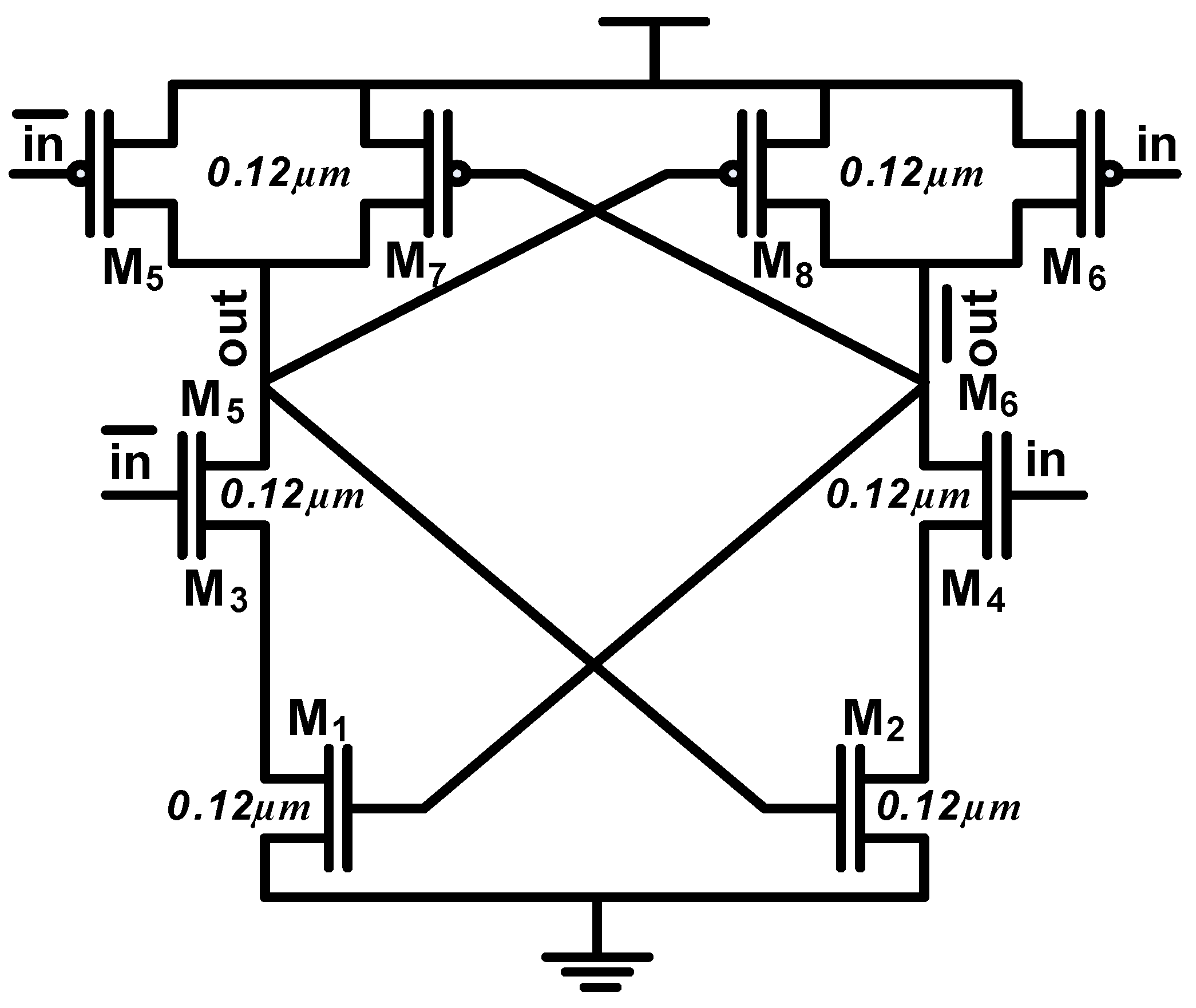

2.4. NMOS Trees Creation

- Both out and of each NMOS tree must be connected to the same number of parallel branches in order to have the same load.

- The number of series connected transistors in each out/ branch should not depend on the input of the implemented function [35].

- The layout of the NMOS tree should preserve the symmetry between out and branches and also balance the routes in order to match the interconnect capacitances [35].

2.5. Sharing Principle

2.6. Interface with Static CMOS Logic

3. Simulation Results of DDSLL and Other State-of-the-Art Logic Styles

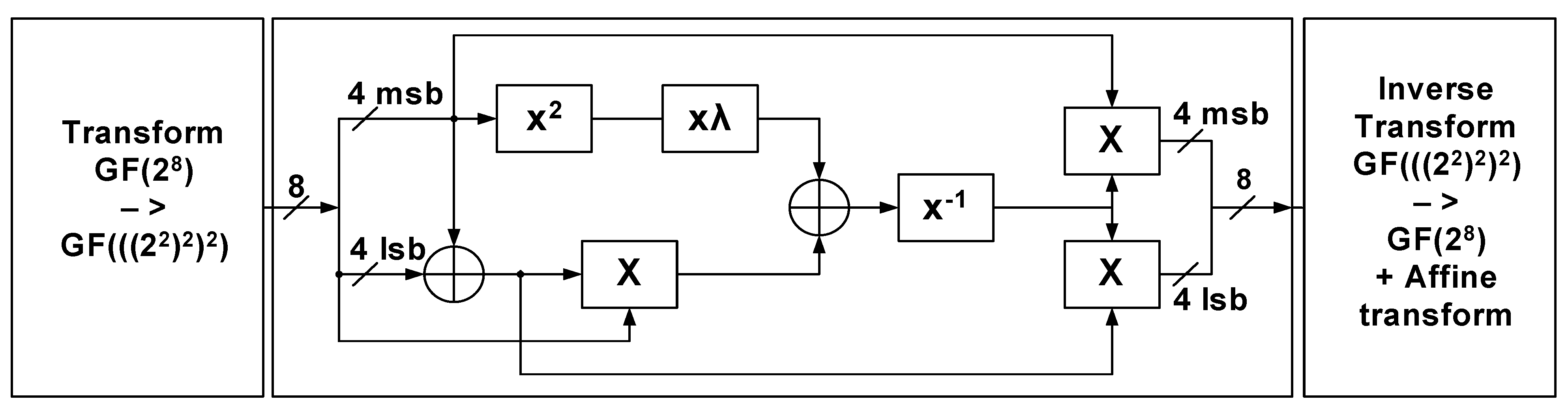

3.1. Case Study

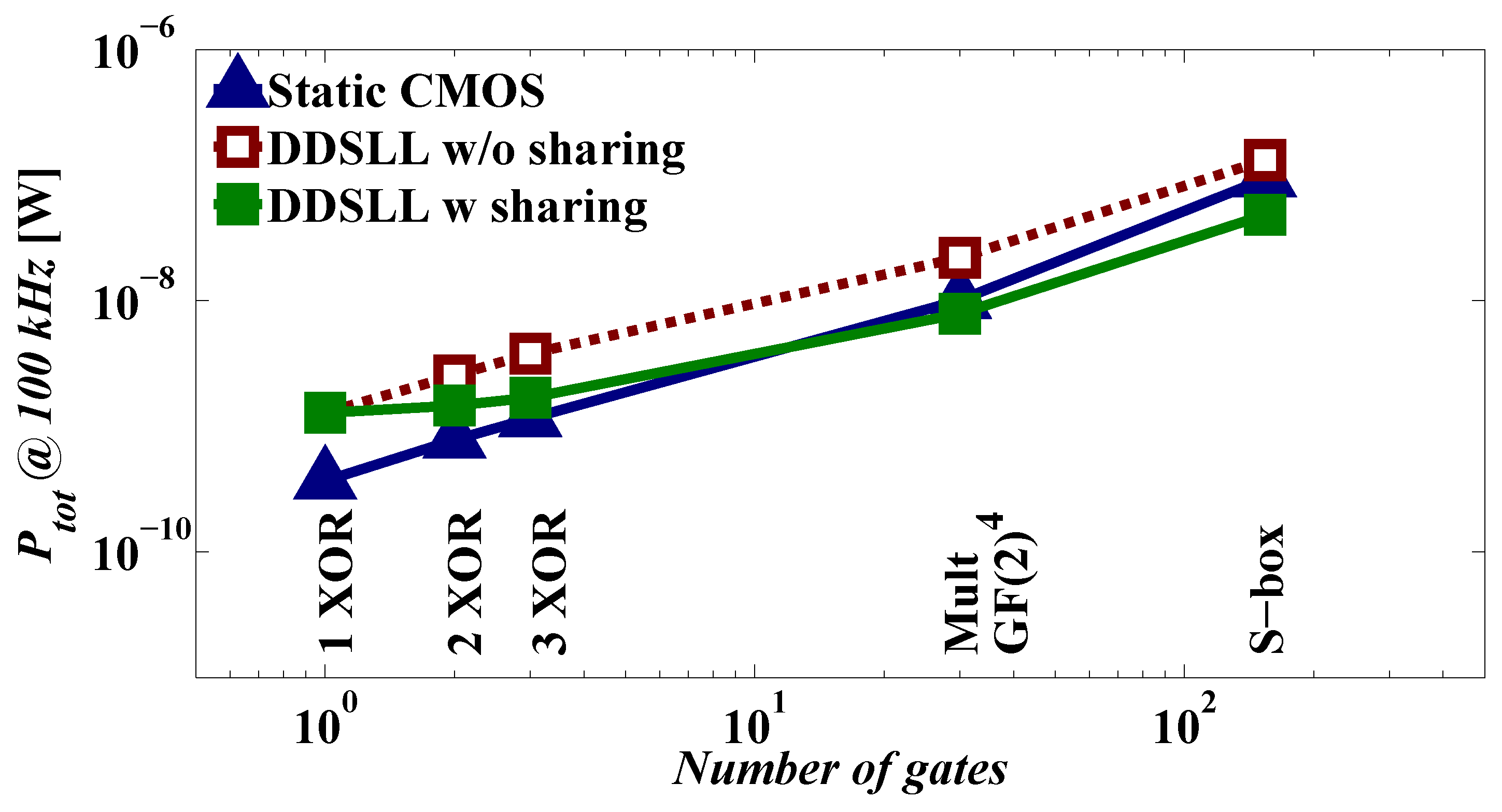

3.2. Effect of Sharing in Dynamic Differential Logic

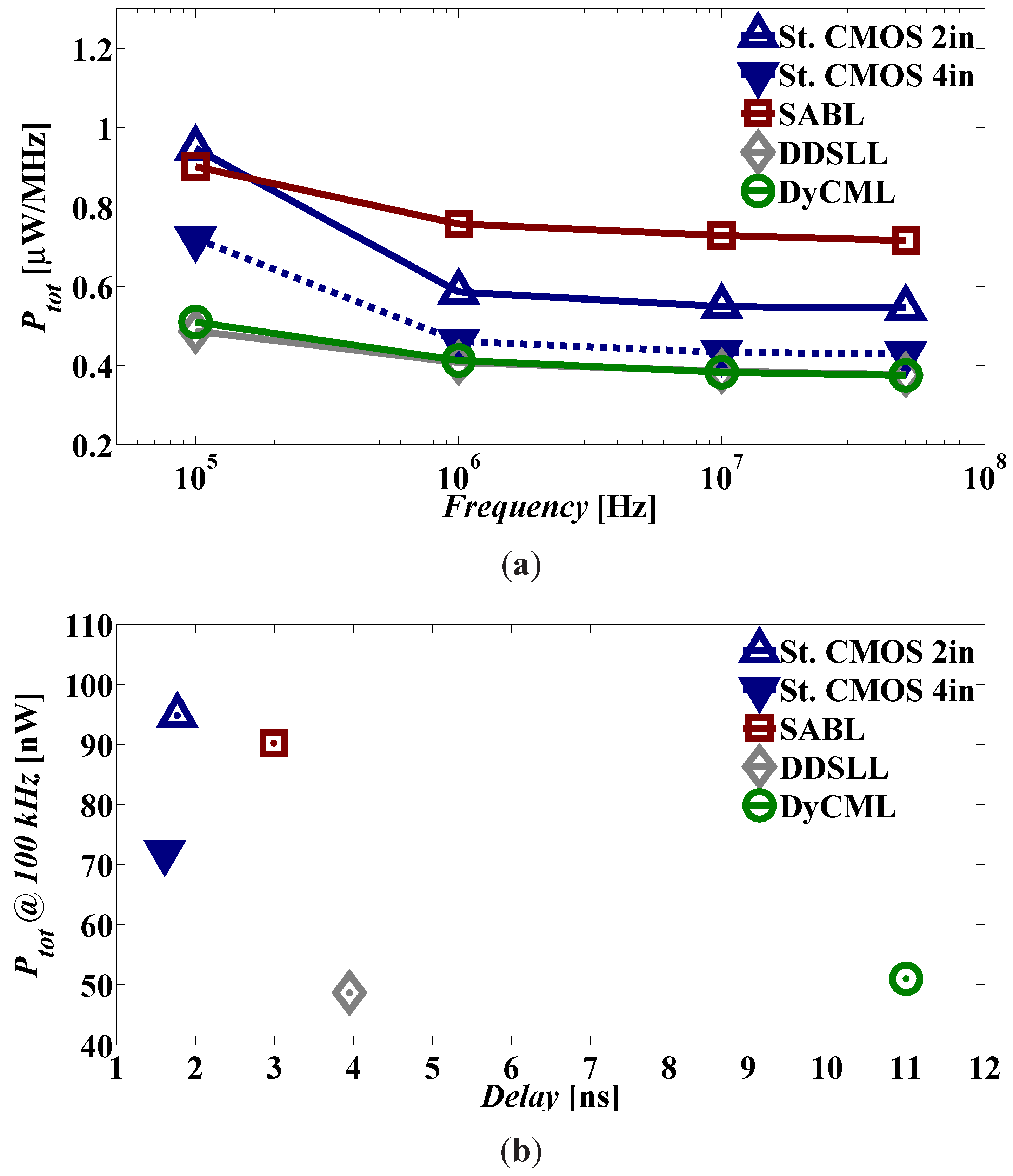

3.3. Power and Delay Comparison

3.4. Security Simulation Results

3.5. Effect of Routing Parasitics

3.6. Variability Effect on the Power Consumption of DDSLL and Static CMOS Styles

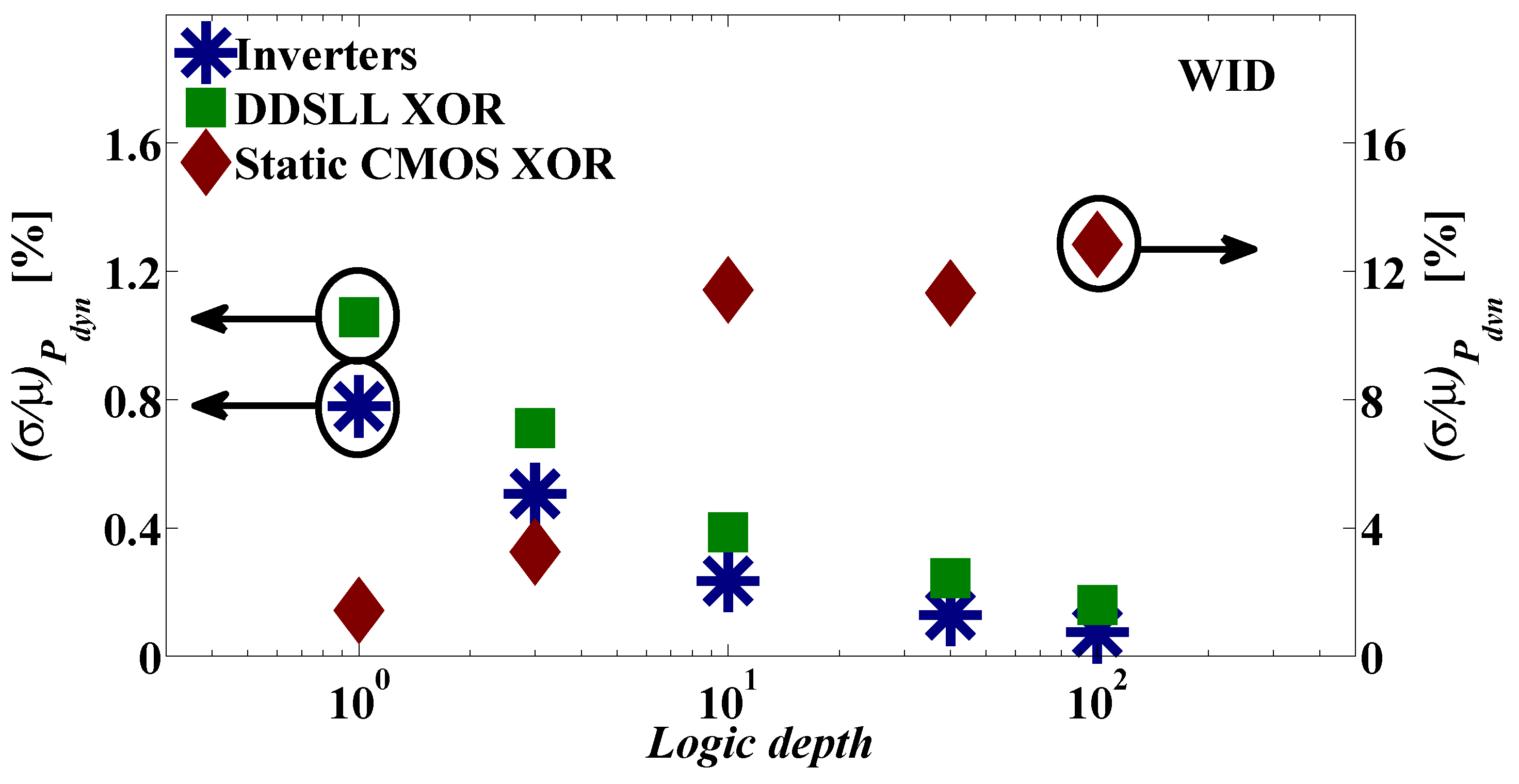

3.6.1. With-in-Die Variability

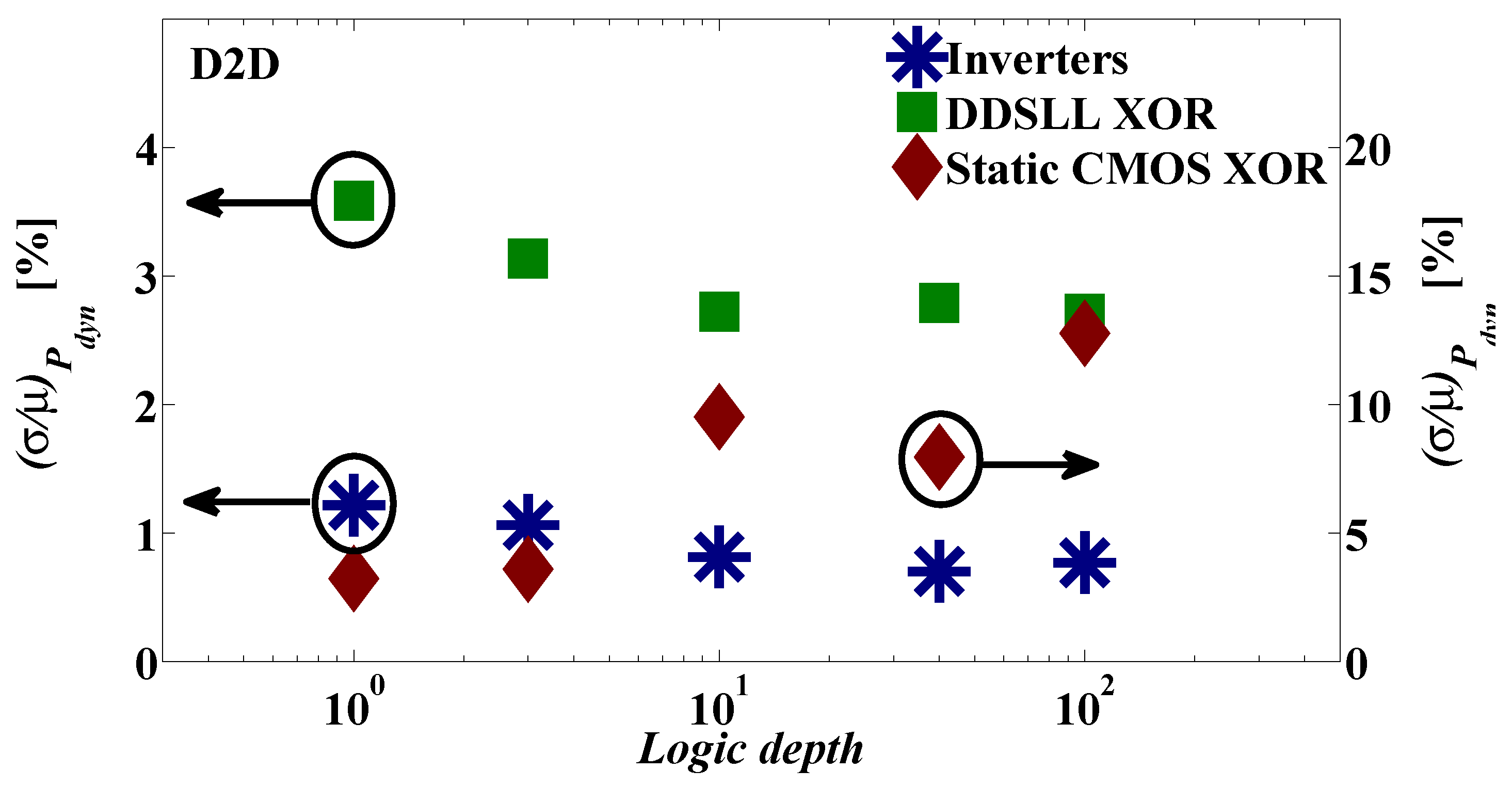

3.6.2. Die-to-Die Variability

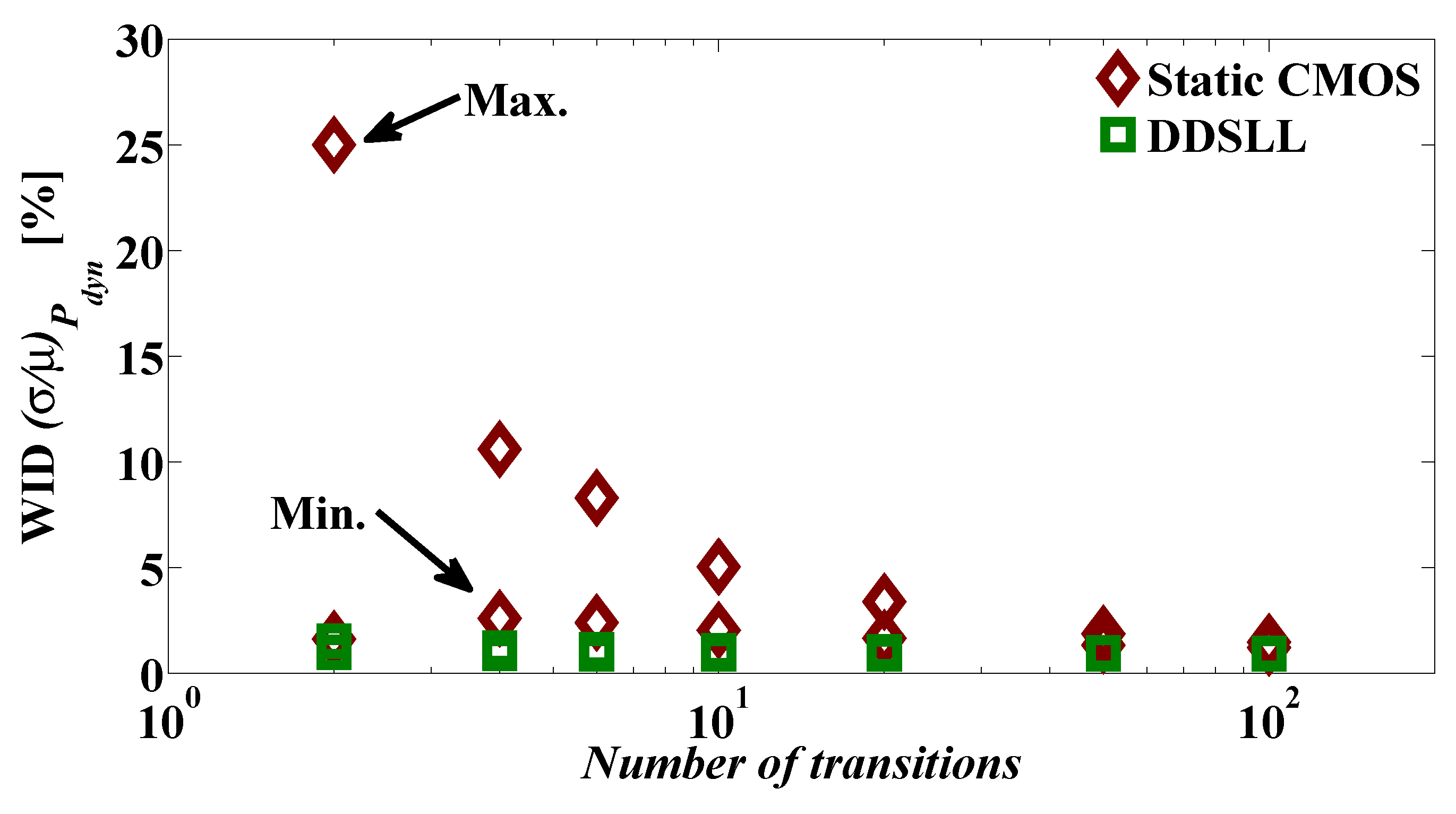

3.6.3. WID Variability Effect on S-Box

4. Measurement Results

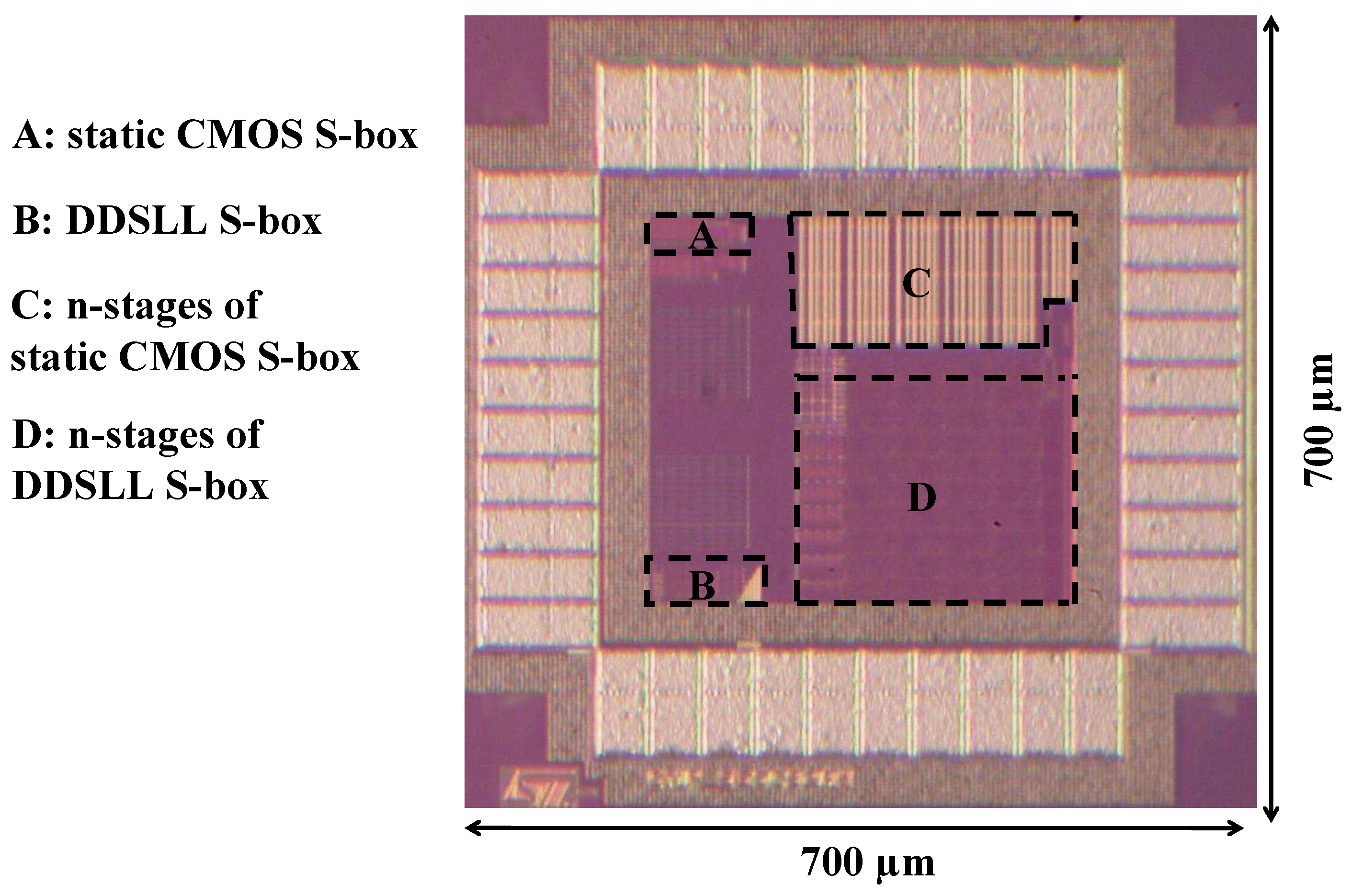

4.1. Test Chip Implementation

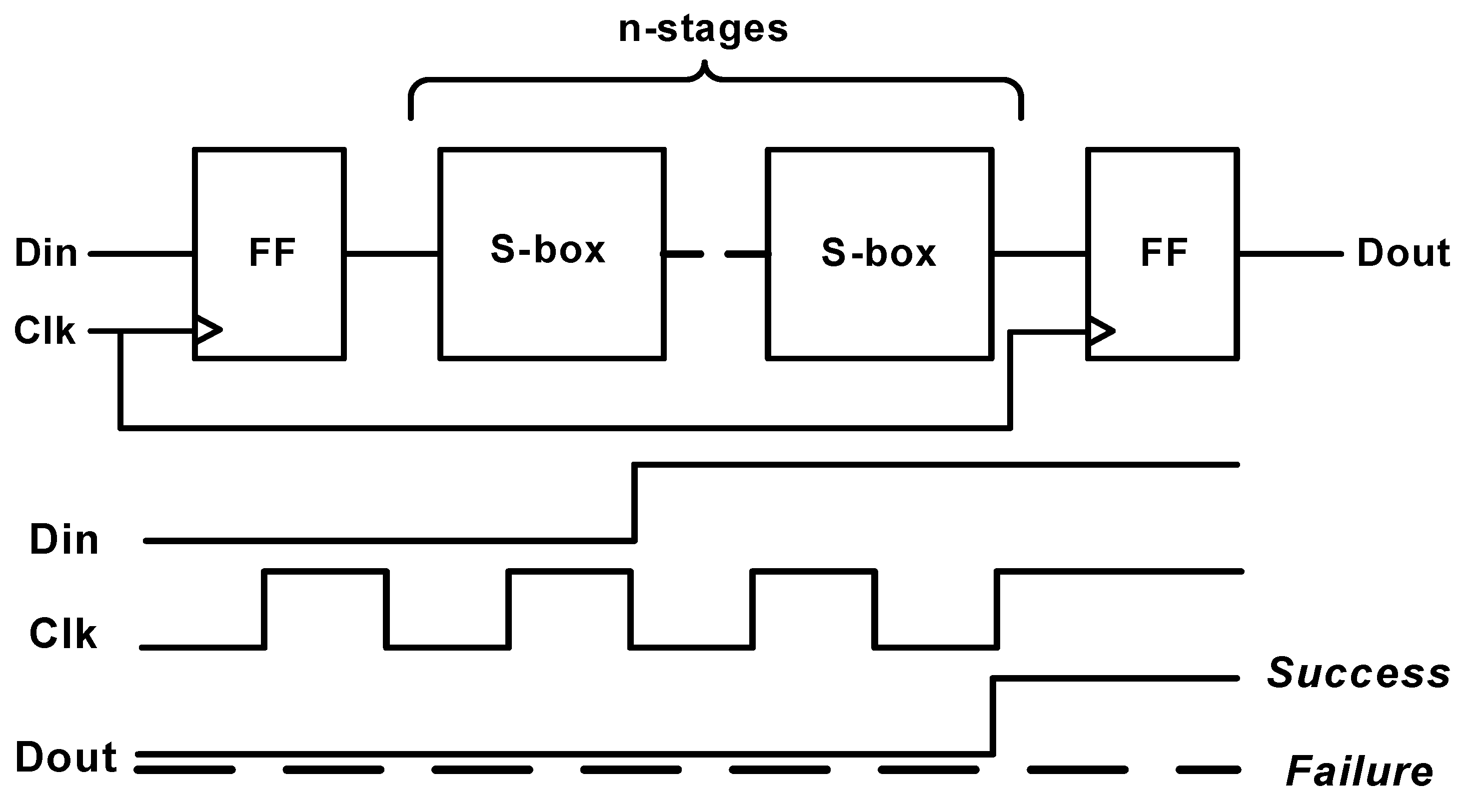

4.2. Measurement Setup

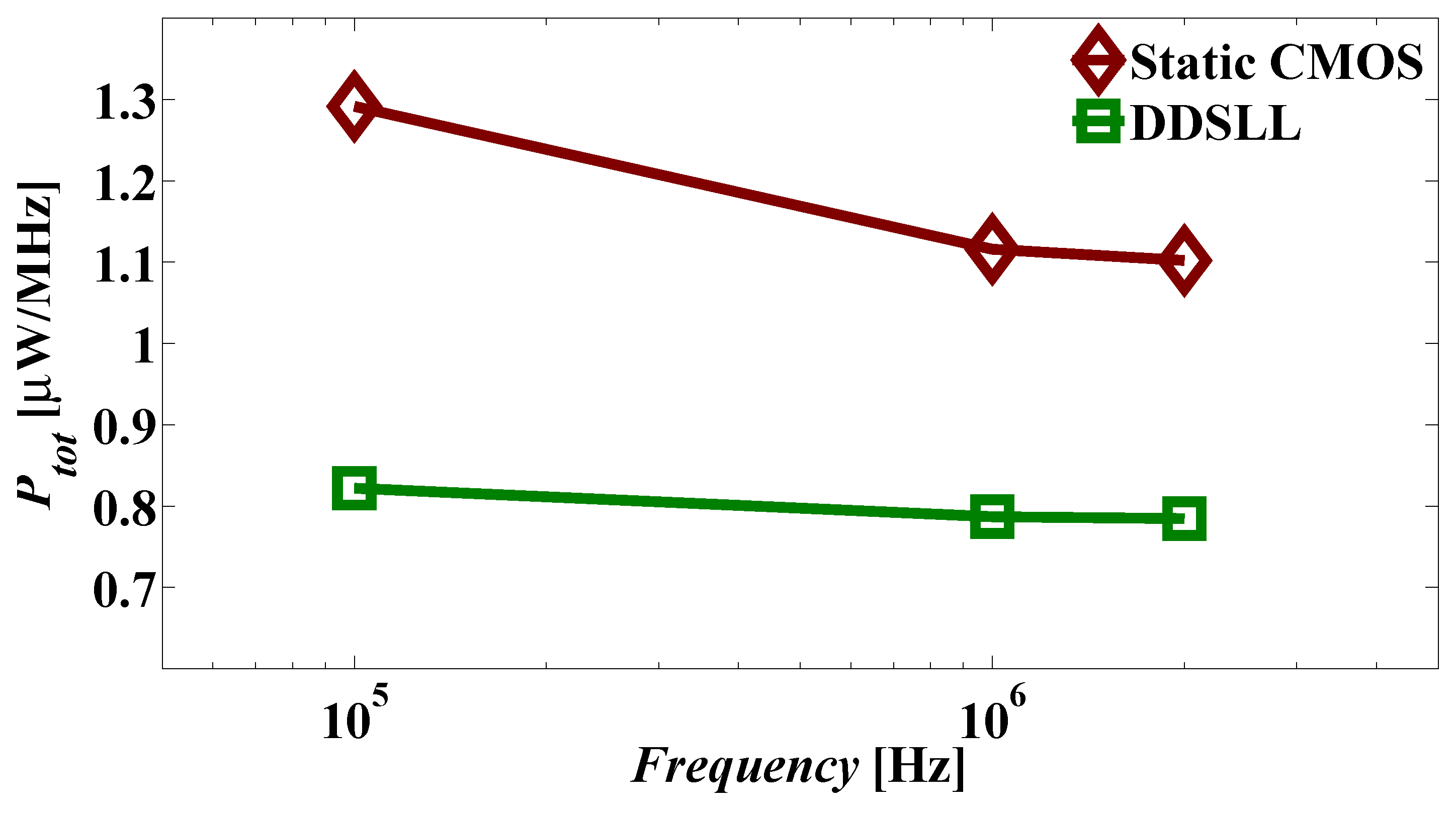

4.3. Power Consumption Measurement Results

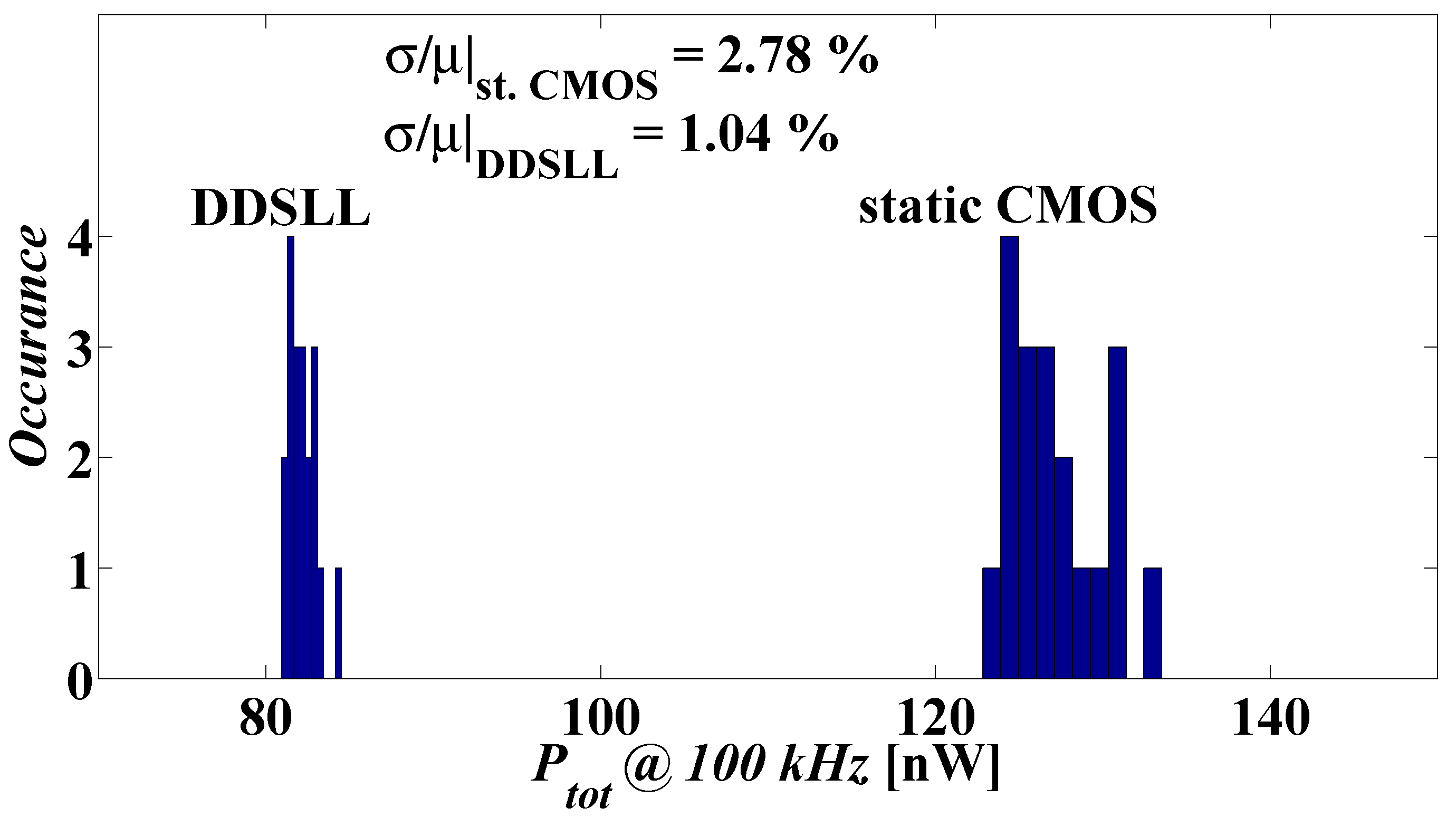

4.4. Variability Effect on Power Consumption Measurement Results

4.5. Delay Measurement Results

4.6. Security Results

5. Conclusions

Acknowledgments

References

- Roberti, M. A 5-cent breakthrough. Available online: http://www.rfidjournal.com (accessed on 16 March 2012).

- Umeda, T.; Yoshida, H.; Sekine, S.; Fujita, Y.; Suzuki, T.; Otaka, S. A 950-MHz rectifier circuit for sensor network tags with 10-m distance. IEEE J. Solid State Circuits 2006, 41, 35–41. [Google Scholar] [CrossRef]

- Hong, Y.; Chan, C.F.; Guo, J.; Ng, Y.S.; Shi, W.; Leung, L.K.; Leung, K.N.; Choy, C.S.; Pun, K.P. Design of Passive UHF RFID Tag in 130 nm CMOS Technology. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS ’08), Macao, China, 30 November–3 December 2008; pp. 1371–1374. [Google Scholar]

- Sony. RC-S801 Product Specification. Available online: http://www.sony.net/Products/felica/business/tech-support/data/fprcs8011.02.pdf (accessed on 16 March 2012).

- Infineon. Chip Card and Security: SLE 6636–SLE 6636E. Available online: http://www.infineon.com/dgdl/SPISLE66361008.pdf?folderId=db3a304328c6bd5c0128d5df208b014f&fileId=db3a304328c6bd5c0128d5e58c240150 (accessed on 1 October 2008).

- Feldhofer, M.; Dominikus, S.; Wolkerstorfer, J. Strong Authentication for RFID Systems Using the AES Algorithm. In Proceedings of the 6th International Workshop on Cryptographic Hardware and Embedded Systems (CHES ’04), Boston/Cambridge, MA, USA, 11–13 August 2004; pp. 357–370. [Google Scholar]

- Infineon. my-d® vicinity: SRF55V01P. Available online: http://www.infineon.com/dgdl/my-d+vicinityProductBrief2007-04.pdf?folderId=db3a30432662379201269d68cac1740f&fileId=db3a304328c6bd5c0128d63aa22a402e (accessed on 16 March 2012).

- ISO Standards. ISO/IEC 14443-3:2011. Identification cards—Contactless integrated circuit cards—Proximity cards—Part 3: Initialization and anticollision. Available online: http://www.iso.org/iso/isocatalogue/cataloguetc/cataloguedetail.htm?csnumber=50942 (accessed on 16 March 2012).

- Ricci, A.; Grisanti, M.; de Munari, I.; Ciampolini, P. Design of a 2 µW RFID Baseband Processor Featuring an AES Cryptography Primitive. In Proceedings of the 15th IEEE International Conference on Electronics, Circuits and Systems (ICECS ’08), Malta, 31 August–3 September 2008; pp. 376–379. [Google Scholar]

- Feldhofer, M.; Wolkerstorfer, J. Strong Crypto for RFID Tags—A Comparison of Low-Power Hardware Implementations. In Proceedings of the International Symposium on Circuits and Systems (ISCAS ’07), New Orleans, LA, USA, 20–27 May 2007; pp. 1839–1842. [Google Scholar]

- Mangard, S.; Oswald, E.; Popp, T. Power Analysis Attacks—Revealing the Secrets of Smart Cards; Springer: Berlin, Germany, 2007. [Google Scholar]

- Dziembowski, S.; Pietrzak, K. Leakage-Resilient Cryptography. In Proceedings of the 49th Annual IEEE Symposium on Foundations of Computer Science (FOCS ’09), Philadelphia, PA, USA, 26–28 October 2008; pp. I–XXIII, 1–337. [Google Scholar]

- Goubin, L.; Patarin, J. DES and Differential Power Analysis (The “Duplication” Method). In Proceedings of the 1st International Workshop on Cryptographic Hardware and Embedded Systems (CHES ’99), Worcester, MA, USA, August 1999; Springer-Verlag: London, UK, 1999; pp. 158–172. [Google Scholar]

- Tiri, K.; Akmal, M.; Verbauwhede, I. A Dynamic and Differential CMOS Logic with Signal Independent Power Consumption to Withstand Differential Power Analysis on Smart Cards. In Proceedings of the 28th European Solid-State Circuits Conference, (ESSCIRC ’02), Firenze, Italy, 24–26 September 2002; pp. 403–406. [Google Scholar]

- Tiri, K.; Verbauwhede, I. A Logic Level Design Methodology for a Secure DPA Resistant ASIC or FPGA Implementation. In Proceedings of the 2004 Design, Automation and Test in Europe Conference and Exposition (DATE ’04), Paris, France, 16–20 February 2004; pp. 246–251. [Google Scholar]

- Tiri, K.; Verbauwhede, I. Charge Recycling Sense Amplifier Based Logic: Securing Low Power Security ICs Against DPA [Differential Power Analysis]. In Proceeding of the 30th European Solid-State Circuits Conference, (ESSCIRC ’04), Leuven, Belgium, 21–23 September 2004; pp. 179–182. [Google Scholar]

- Allam, M.; Elmasry, M. Dynamic Current Mode Logic (DyCML): A new low-power high-performance logic style. IEEE J. Solid State Circuits 2001, 36, 550–558. [Google Scholar] [CrossRef]

- Yamashina, M.; Yamada, H. An MOS Current Mode Logic (MCML) Circuit for Low-Power Sub-GHz Processors. In Proceedings of the IEICE, October 1992; pp. 1181–1187. [Google Scholar]

- Hassoune, I.; Mace´, F.; Flandre, D.; Legat, J.D. Dynamic differential self-timed logic families for robust and low-power security ICs. VLSI J. Integr. 2007, 40, 355–364. [Google Scholar] [CrossRef]

- Hwang, D.; Tiri, K.; Hodjat, A.; Lai, B.C.; Yang, S.; Schaumont, P.; Verbauwhede, I. AES-based security coprocessor IC in 0.18 µm CMOS with resistance to differential power analysis side-channel attacks. IEEE J. Solid State Circuits 2006, 41, 781–792. [Google Scholar] [CrossRef]

- Mace, F.; Standaert, F.X.; Hassoune, I.; Quisquater, J.J.; Legat, J.D. A Dynamic Current Mode Logic to Counteract Power Analysis Attacks. In Proceedings of the 19th Conference on Design of Circuits and Integrated Systems (DCIS ’04), Bordeaux, France, 24–26 November 2004; pp. 186–191. [Google Scholar]

- Regazzoni, F.; Badel, S.; Eisenbarth, T.; Großscha¨dl, J.; Poschmann, A.; Toprak, Z.; Macchetti, M.; Pozzi, L.; Paar, C.; Leblebici, Y.; et al. A Simulation-Based Methodology for Evaluating DPA-Resistance of Cryptographic Functional Units with Application to CMOS and MCML Technologies. In Proceedings of the IEEE International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS IC ’07), Samos, Greece, 16–19 July 2007; pp. 209–214. [Google Scholar]

- Toprak, Z.; Leblebici, Y. Low-Power Current Mode Logic for Improved DPA-Resistance in Embedded Systems. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS ’05), Kobe, Japan, 23–26 May 2005; Volume 2, pp. 1059–1062. [Google Scholar]

- Renauld, M.; Standaert, F.X.; Veyrat-Charvillon, N.; Kamel, D.; Flandre, D. A Formal Study of Power Variability Issues and Side-Channel Attacks for Nanoscale Devices. In Proceedings of the 30th Annual International Conference on the Theory and Applications of Cryptographic Techniques (EUROCRYPT ’11), Tallinn, Estonia, 15–19 May 2011; pp. 109–128. [Google Scholar]

- Verma, N.; Kwong, J.; Chandrakasan, A. Nanometer MOSFET variation in minimum energy subthreshold circuits. IEEE Trans. Electron. Devices 2008, 55, 163–174. [Google Scholar] [CrossRef]

- Blaauw, D.; Chopra, K.; Srivastava, A.; Scheffer, L. Statistical timing analysis: From basic principles to state of the art. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2008, 27, 589–607. [Google Scholar] [CrossRef]

- Bol, D. Robust and energy-efficient ultra-low-voltage circuit design under timing constraints in 65/45 nm CMOS. J. Low Power Electron. Appl. 2011, 1, 1–19. [Google Scholar] [CrossRef]

- Kamel, D.; Hocquet, C.; Standaert, F.X.; Flandre, D.; Bol, D. Glitch-Induced Within-Die Variations of Dynamic Energy in Voltage-Scaled Nano-CMOS Circuits. In Proceedings of the 36th European Solid-State Circuits Conference (ESSCIRC ’10), Seville, Spain, 13–17 September 2010; pp. 518–521. [Google Scholar]

- Pang, L.T.; Nikolic, B. Measurements and analysis of process variability in 90 nm CMOS. IEEE J. Solid State Circuits 2009, 44, 1655–1663. [Google Scholar] [CrossRef]

- Standaert, F.X.; Malkin, T.G.; Yung, M. A Unified Framework for the Analysis of Side-Channel Key Recovery Attacks. In Proceedings of the 28th Annual International Conference on Advances in Cryptology: The Theory and Applications of Cryptographic Techniques (EUROCRYPT ’09), Cologne, Germany, 26–30 April 2009; Springer-Verlag: Berlin, Heidelberg, Germany, 2009; pp. 443–461. [Google Scholar]

- Renauld, M.; Kamel, D.; Standaert, F.X.; Flandre, D. Information Theoretic and Security Analysis of a 65-Nanometer DDSLL AES S-Box. In Proceedings of the Workshop on Cryptographic Hardware and Embedded Systems (CHES ’11), Nara, Japan, 28 September–1 October 2011; pp. 223–239. [Google Scholar]

- Chari, S.; Rao, J.R.; Rohatgi, P. Template Attacks. In Proceedings of the 4th International Workshop on Cryptographic Hardware and Embedded Systems (CHES ’02), Redwood Shores, CA, USA, 13–15 August 2002; pp. 13–28. [Google Scholar]

- Kamel, D.; Standaert, F.X.; Flandre, D. Scaling Trends of the AES S-Box Low Power Consumption in 130 and 65 nm CMOS Technology Nodes. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS ’09), Taipei, Taiwan, 24–17 May 2009; pp. 1385–1388. [Google Scholar]

- Hassoune, I.; Mace, F.; Flandre, D.; Legat, J.D. Low-swing current mode logic (LSCML): A new logic style for secure and robust smart cards against power analysis attacks. Microelectron. J. 2006, 37, 997–1006. [Google Scholar] [CrossRef]

- Giancane, L.; Marietti, P.; Olivieri, M.; Scotti, G.; Trifiletti, A. A New Dynamic Differential Logic Style as a Countermeasure to Power Analysis Attacks. In Proceedings of the 15th IEEE International Conference on Electronics, Circuits and Systems (ICECS ’08), Malta, 31 August–3 September 2008; pp. 364–367. [Google Scholar]

- Akers, S. Binary decision diagrams. IEEE Trans. Comput. 1978, C-27, 509–516. [Google Scholar] [CrossRef]

- Cortadella, J. Mapping BDDs Into DCVSL Gates; Technical report No. RR 95/04; UPC/DAC (Universitat Polite´cnica de Catalunya): Barcelona, Spain, 1995. [Google Scholar]

- Mace, F.; Standaert, F.X.; Quisquater, J.J.; Legat, J.D. A Design Methodology for Secured ICs Using Dynamic Current Mode Logic. Proceedings of 15th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS ’05), Leuven, Belgium, 20–23 September 2005; Paliouras, V., Ed.; Springer: Berlin, Germany, 2005; pp. 550–560. [Google Scholar]

- Tiri, K.; Verbauwhede, I. Place and Route for Secure Standard Cell Design. In Proceedings of the 6th Smart Card Research and Advanced Application IFIP Conference (CARDIS ’04), Toulouse, France, 22–27 August 2004; pp. 143–158. [Google Scholar]

- Tiri, K.; Hwang, D.; Hodjat, A.; Lai, B.C.; Yang, S.; Schaumont, P.; Verbauwhede, I. A side- channel leakage free coprocessor IC in 0. In 18/spl µm CMOS for embedded AES-based cryptographic and biometric processing. In Proceedings of the 42nd Design Automation Conference (DAC ’05), San Diego, CA, USA, 13–17 June 2005; pp. 222–227. [Google Scholar]

- Cannillo, F.; Toumazou, C. Nano-power subthreshold current-mode logic in sub-100 nm technologies. Electron. Lett. 2005, 41, 1268–1269. [Google Scholar] [CrossRef]

- Musicer, J.M.; Rabaey, J.M. MOS Current Mode Logic for Low Power, Low Noise CORDIC Computation in Mixed-Signal Environments. In Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED ’00), Rapallo, Italy, 25–27 July 2000; pp. 102–107. [Google Scholar]

- Tajalli, A.; Brauer, E.; Leblebici, Y.; Vittoz, E. Subthreshold Source-Coupled Logic Circuits for Ultra-Low-Power Applications. IEEE J. Solid State Circuits 2008, 43, 1699–1710. [Google Scholar] [CrossRef]

- Federal Information Processing Standards Publication (FIPS 197 Advanced Encryption Standard (AES)). November 2001. Available online: http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf (accessed on 16 March 2012).

- Mentens, N.; Batina, L.; Preneel, B.; Verbauwhede, I. A Systematic Evaluation of Compact Hardware Implementations for the Rijndael S-Box. In Proceedings of the 14th Annual RSA Conference—Cryptographer’s Track (CT-RSA ’05), San Francisco, CA, USA, 14–18 February 2005; pp. 323–333. [Google Scholar]

- Satoh, A.; Morioka, S.; Takano, K.; Munetoh, S. A Compact Rijndael Hardware Architecture with S-Box Optimization. In Proceedings of the 7th International Conference on the Theory and Application of Cryptology and Information Security (ASIACRYPT ’01), Gold Coast, Australia, 9–13 December 2001; pp. 239–254. [Google Scholar]

- Chandrakasan, A.; Sheng, S.; Brodersen, R. Low-power CMOS digital design. IEEE J. Solid State Circuits 1992, 27, 473–484. [Google Scholar] [CrossRef]

- Alioto, M.; Palumbo, G.; Pennisi, M. Understanding the Effect of Process Variations on the Delay of Static and Domino Logic. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2010, 18, 697–710. [Google Scholar] [CrossRef]

- Brown, A.; Asenov, A. Capacitance fluctuations in bulk MOSFETs due to random discrete dopants. J. Comput. Electron. 2008, 7, 115–118. [Google Scholar] [CrossRef]

| Circuit | 2-in static CMOS | 4-in static CMOS | SABL | DyCML | DDSLL |

|---|---|---|---|---|---|

| Logic gates | 138 XOR/XNOR, AND/NAND, INVs | 90 XOR/XNOR, AND/NAND, INVs, | 90 | 90 | 90 |

| complex 4-in functions | |||||

| Logic depth | 22 | 13 | 13 | 13 | 13 |

| Transistors | 1530 | 1099 | 1672 | 1241 | 1275 |

| Parameter | 2-in static CMOS | SABL | DyCML | DDSLL |

|---|---|---|---|---|

| PI | 5.323 | 3.498 | 1.922 | 2.656 |

| Parameter | static CMOS | DDSLL | ||||

|---|---|---|---|---|---|---|

| No | Typical | No | Typical | |||

| Crout | Crout | Crout | Crout | |||

| Pstat [nW] | 46.6 | − | ||||

| Pdyn@100 kHz [nW] | 54.2 | 107.9 | − | − | ||

| Ptot@100 kHz [nW] | 99.4 | 154.5 | 48.8 | 96.1 | ||

| Pdyn@13.56 MHz [nW] | 7, 365 | 14, 830 | − | − | ||

| Ptot@13.56 MHz [nW] | 7, 412 | 14, 877 | 5, 246 | 10, 856 | ||

| delay [ns] | 1.8 | 2.5 | 3.9 | 7.2 | ||

| Parameter | Static CMOS | DDSLL | ||

|---|---|---|---|---|

| Meas. | TT Sim. | Meas. | TT Sim. | |

| Pstat [nW] | 20.3 | 46.6 | ||

| Pdyn@100 kHz [nW] | 106.4 | 107.9 | ||

| Ptot@100 kHz [nW] | 126.8 | 154.5 | 82.2 | 96.1 |

| Logic style | Meas. (ns) | Sim. (ns) |

|---|---|---|

| static CMOS | 3.1 | 2.5 |

| DDSLL | 7.8 | 7.2 |

| Parameter | Static CMOS | DDSLL |

|---|---|---|

| PI | 2.120 | 0.689 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2012 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kamel, D.; Renauld, M.; Bol, D.; Standaert, F.-X.; Flandre, D. Analysis of Dynamic Differential Swing Limited Logic for Low-Power Secure Applications. J. Low Power Electron. Appl. 2012, 2, 98-126. https://doi.org/10.3390/jlpea2010098

Kamel D, Renauld M, Bol D, Standaert F-X, Flandre D. Analysis of Dynamic Differential Swing Limited Logic for Low-Power Secure Applications. Journal of Low Power Electronics and Applications. 2012; 2(1):98-126. https://doi.org/10.3390/jlpea2010098

Chicago/Turabian StyleKamel, Dina, Mathieu Renauld, David Bol, François-Xavier Standaert, and Denis Flandre. 2012. "Analysis of Dynamic Differential Swing Limited Logic for Low-Power Secure Applications" Journal of Low Power Electronics and Applications 2, no. 1: 98-126. https://doi.org/10.3390/jlpea2010098

APA StyleKamel, D., Renauld, M., Bol, D., Standaert, F.-X., & Flandre, D. (2012). Analysis of Dynamic Differential Swing Limited Logic for Low-Power Secure Applications. Journal of Low Power Electronics and Applications, 2(1), 98-126. https://doi.org/10.3390/jlpea2010098