Vacuum Inner Spacer to Improve Annealing Effect during Electro-Thermal Annealing of Nanosheet FETs

Abstract

:1. Introduction

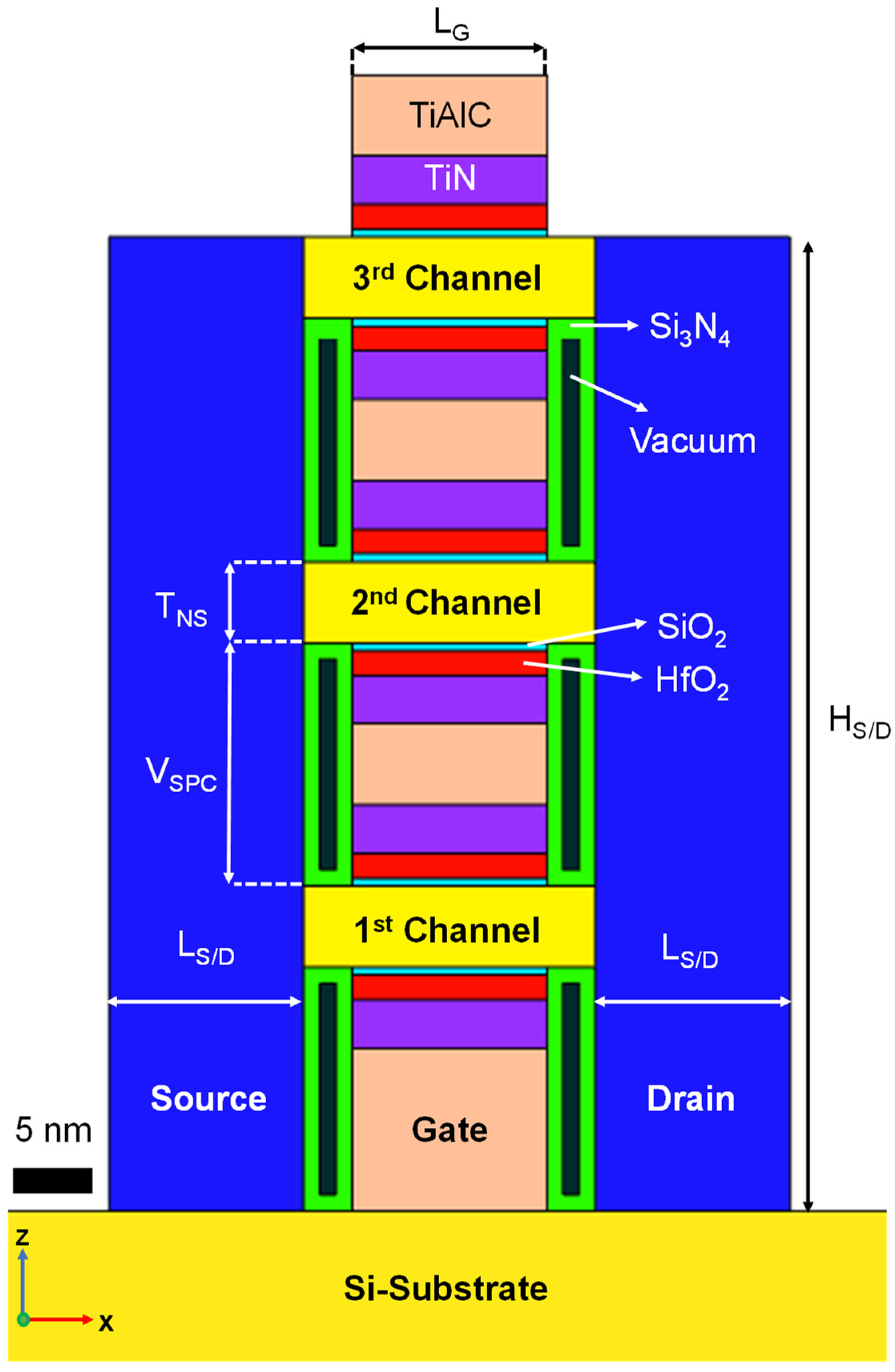

2. Device Structure and Simulation Methodology

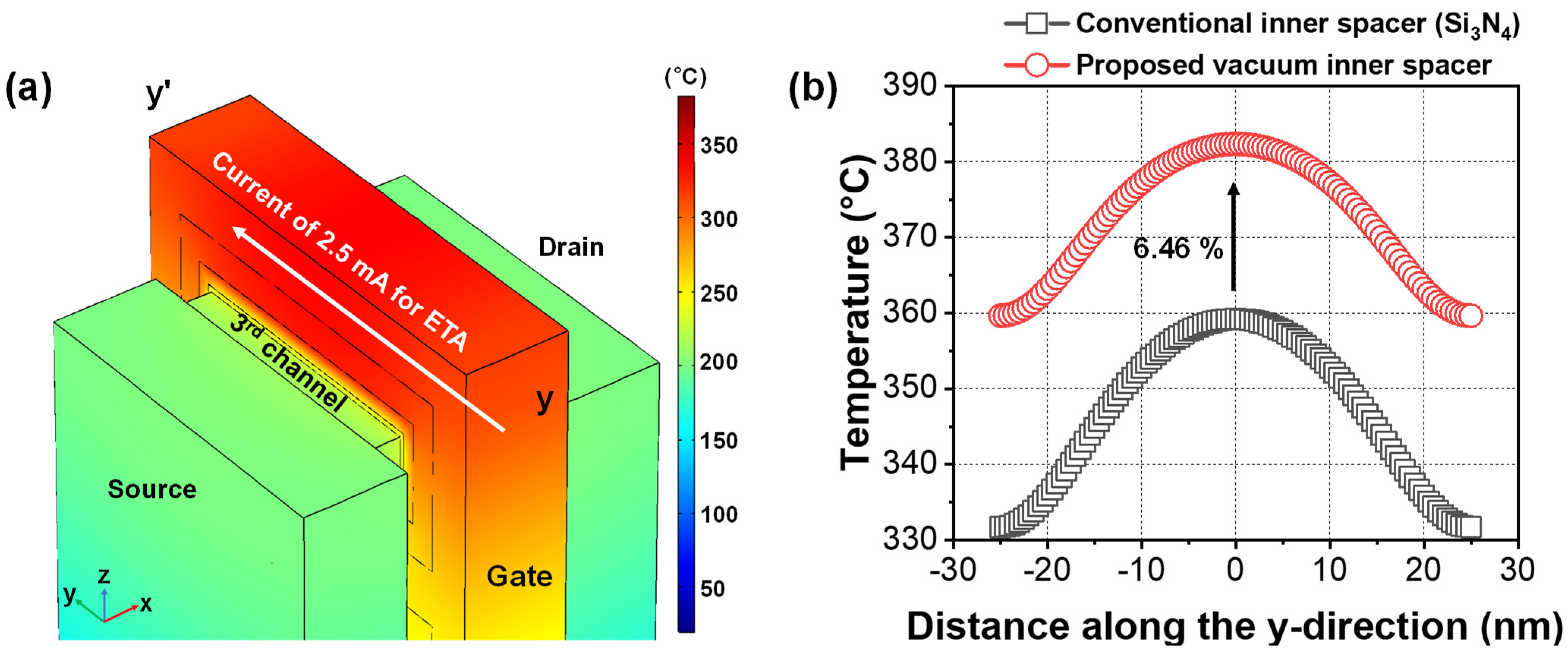

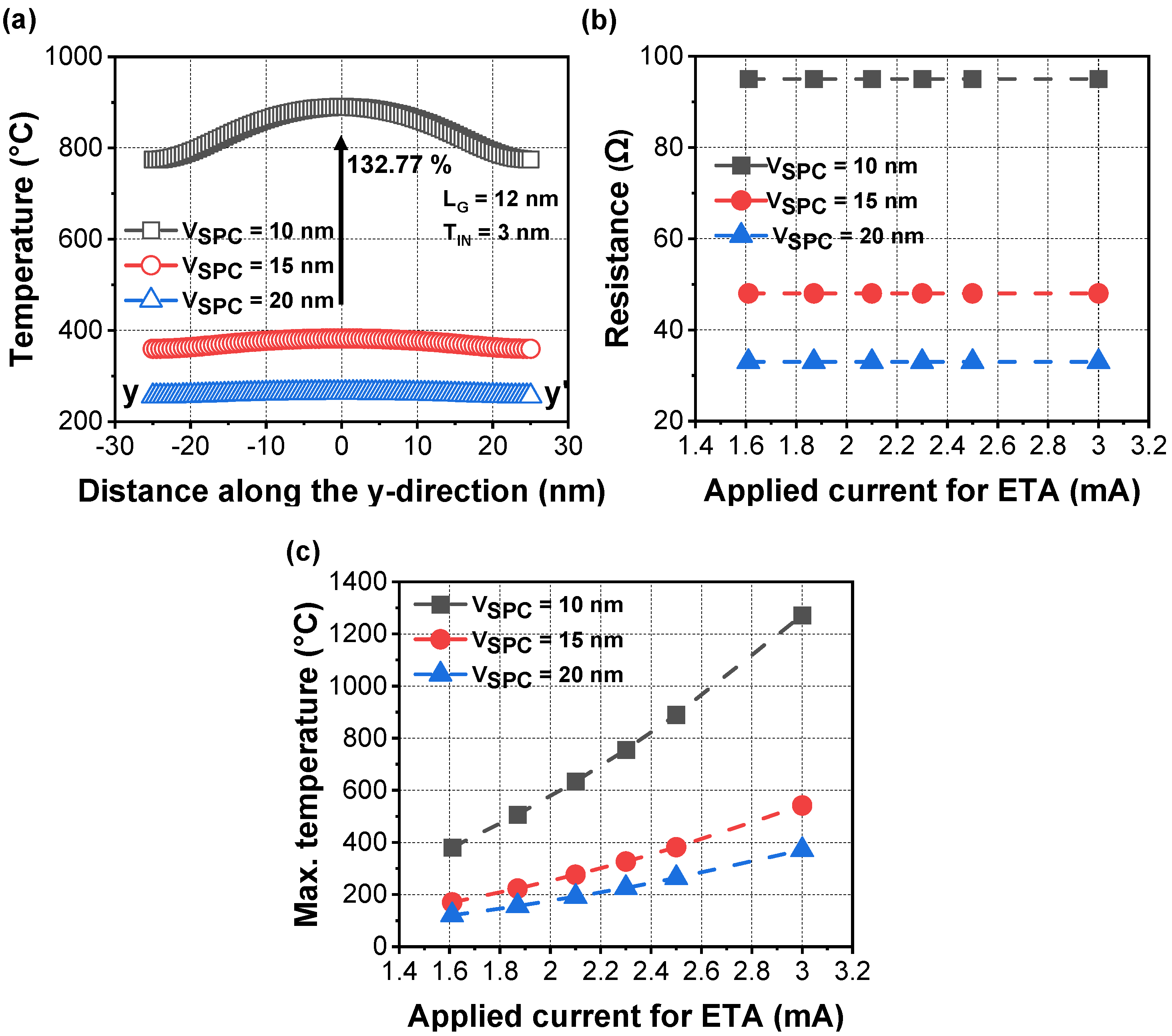

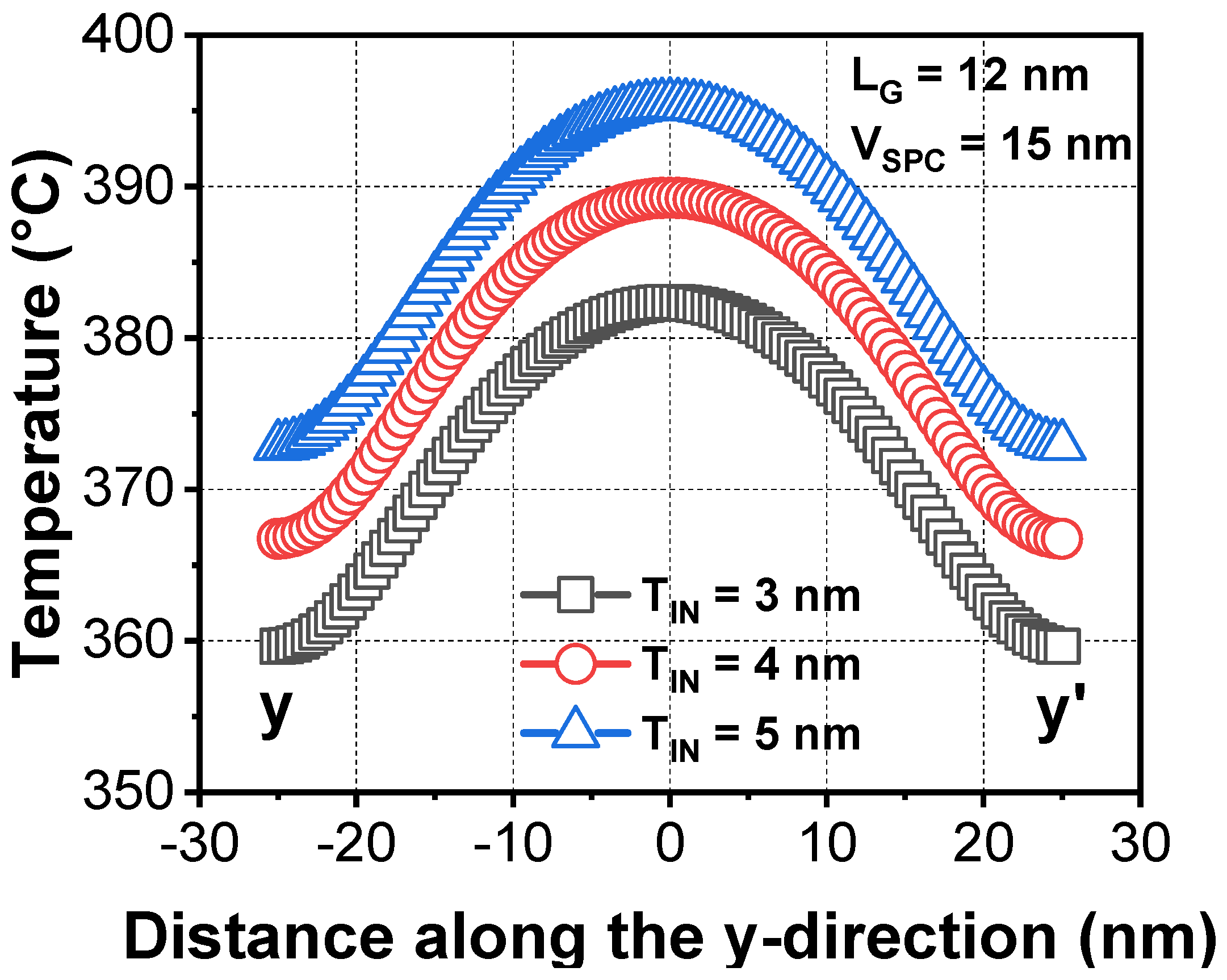

3. Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chaudhry, A.; Kumar, M.J. Controlling Short-Channel Effects in Deep-Submicron SOI MOSFETs for Improved Reliability: A Review. IEEE Trans. Device Mater. Reliab. 2004, 4, 99–109. [Google Scholar] [CrossRef] [Green Version]

- Shen, T.; Watanabe, K.; Zhou, H.; Belyansky, M.; Stuckert, E.; Zhang, J.; Greene, A.; Basker, V.; Wang, M. A new technique for evaluating stacked nanosheet inner spacer TDDB reliability. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020. [Google Scholar] [CrossRef]

- Sachid, A.B.; Chen, M.-C.; Hu, C. Bulk FinFET With Low-κ Spacers for Continued Scaling. IEEE Trans. Electron Devices 2017, 64, 1861–1864. [Google Scholar] [CrossRef]

- Singh, N.; Agarwal, A.; Bera, L.K.; Liow, T.Y.; Yang, R.; Tung, S.C.; Kumar, R.; Lo, G.Q.; Balasubramanian, N.; Kwong, D.-L. High-Performance Fully Depleted Silicon Nanowire (Diameter ≤ 5 nm) Gate-All-Around CMOS Devices. IEEE Electron Device Lett. 2006, 27, 383–386. [Google Scholar] [CrossRef]

- Auth, C.; Cappellani, A.; Chun, J.-S.; Dalis, A.; Davis, A.; Ghani, T.; Glass, G.; Glassman, T.; Harper, M.; Hattendorf, M.; et al. 45 nm High-k + Metal Gate Strain-Enhanced Transistors. In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008. [Google Scholar] [CrossRef]

- Ogura, S.; Tsang, P.J.; Walker, W.W.; Critchlow, D.L.; Shepard, J.F. Design and Characteristics of the Lightly Doped Drain-Source (LDD) Insulated Gate Field-Effect Transistor. IEEE J. Solid-State Circuits 1980, 15, 424–432. [Google Scholar] [CrossRef]

- Onishi, K.; Kang, C.S.; Choi, R.; Cho, H.-J.; Gopalan, S.; Nieh, R.E.; Krishnan, S.A.; Lee, J.C. Improvement of Surface Carrier Mobility of HfO2 MOSFETs by High-Temperature Forming Gas Annealing. IEEE Trans. Electron Devices 2003, 50, 384–390. [Google Scholar] [CrossRef]

- Park, J.-Y.; Moon, D.-I.; Lee, G.-B.; Choi, Y.-K. Curing of Aged Gate Dielectric by the Self-Heating Effect in MOSFETs. IEEE Trans. Electron Devices 2020, 67, 777–788. [Google Scholar] [CrossRef]

- Han, J.-K.; Park, J.-Y.; Kim, C.-K.; Kwon, J.H.; Kim, M.-S.; Hwang, B.-W.; Kim, D.-J.; Choi, K.C.; Choi, Y.-K. Electrothermal Annealing to Enhance the Electrical Performance of an Exfoliated MoS2 Field-Effect Transistor. IEEE Electron Device Lett. 2016, 39, 1532–1535. [Google Scholar] [CrossRef]

- Bae, H.; Lee, K.-S.; Ye, P.D.; Park, J.-Y. Current annealing to improve drain output performance of β-Ga2O3 field-effect transistor. Solid-State Electron. 2021, 185, 108134. [Google Scholar] [CrossRef]

- Cha, D.-W.; Park, J.-Y. Impact of Dielectrics in SOI FinFET for Lower Power Consumption in Punch-through Current-based Local Thermal Annealing. J. Semicond. Technol. Sci. 2021, 21, 222–228. [Google Scholar] [CrossRef]

- Kim, M.-K.; Choi, Y.-K.; Park, J.-Y. Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs. Micromachines 2022, 13, 124. [Google Scholar] [CrossRef]

- Lee, K.-S.; Park, J.-Y. Inner Spacer Engineering to Improve Mechanical Stability in Channel-Release Process of Nanosheet FETs. Electronics 2021, 10, 1395. [Google Scholar] [CrossRef]

- Xiang, J.; Li, T.; Wang, X.; Han, K.; Li, J.; Zhao, C. Understanding the Role of TiN Barrier Layer on Electrical Performance of MOS Device with ALD-TiN/ALD-TiAlC Metal Gate Stacks TiN 0nm TiN 1nm TiN 2nm TiN 3nm. ESC J. Solid State Sci. Technol. 2016, 5, 327–329. [Google Scholar] [CrossRef]

- Chiang, C.K.; Pai, H.; Lin, J.L.; Chang, J.K.; Lee, M.Y.; Hsieh, E.R.; Li, K.S.; Luo, G.L.; Cheng, O.; Chung, S.S. FinFET Plus: A Scalable FinFET Architecture with 3D Air-Gap and Air-Spacer Toward the 3nm Generation and Beyond. In Proceedings of the 2021 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Hsinchu, Taiwan, 19–22 April 2021. [Google Scholar] [CrossRef]

- Ko, H.; Kim, J.; Kang, M.; Shin, H. Investigation and Analysis of Dual-k Spacer with Different Materials and Spacer Lengths for Nanowire-FET Performance. Solid-State Electron. 2017, 136, 68–74. [Google Scholar] [CrossRef]

- Kim, S.; Cho, W.; Kim, J.; Lee, B.; Park, S. Air-Gap Application and Simulation Results for Low Capacitance in 60nm NAND Flash Memory. In Proceedings of the 22nd IEEE Non-Volatile Semiconductor Memory Workshop, Monterey, CA, USA, 26–30 August 2007. [Google Scholar] [CrossRef]

- Sachid, A.B.; Huang, Y.-M.; Chen, Y.-J.; Chen, C.-C.; Lu, D.D.; Chen, M.-C.; Hu, C. FinFET With Encased Air-Gap Spacers for High-Performance and Low-Energy Circuits. IEEE Electron Device Lett. 2016, 38, 16–19. [Google Scholar] [CrossRef]

- Pundir, Y.P.; Bisht, A.; Saha, R.; Pal, P.K. Air-spacers as analog-performance booster for 5nm-node N-channel nanosheet transistor. Semicond. Sci. Technol. 2021, 36, 10. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the IEEE 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar] [CrossRef]

- Abe, S.; Miyazawa, Y.; Nakajima, Y.; Hanajiri, T.; Toyabe, T.; Sugano, T. Suppression of DIBL in deca-nano SOI MOSFETs by controlling permittivity and thickness of BOX layers. In Proceedings of the 2009 10th International Conference on Ultimate Integration of Silicon, Aachen, Germany, 18–20 March 2009. [Google Scholar] [CrossRef]

- Cai, L.; Chen, W.; Du, G.; Zhang, X.; Liu, X. Layout Design Correlated with Self-Heating Effect in Stacked Nanosheet Transistors. IEEE Trans. Electron Devices 2018, 65, 2647–2653. [Google Scholar] [CrossRef]

- Sachid, A.B.; Lin, H.-Y.; Hu, C. Nanowire FET With Corner Spacer for High-Performance, Energy-Efficient Applications. IEEE Trans. Electron Devices 2017, 64, 5181–5187. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, Y.; Bakir, M.S. Thermal Design and Constraints for Heterogeneous Integrated Chip Stacks and Isolation Technology Using Air Gap and Thermal Bridge. IEEE Trans. Compon. Packag. Manuf. Technol. 2014, 4, 1914–1924. [Google Scholar] [CrossRef]

- Park, J.-Y.; Moon, D.-I.; Seol, M.-L.; Kim, C.-K.; Jeon, C.-H.; Bae, H.; Bang, T.; Choi, Y.-K. Self-Curable Gate-All-Around MOSFETs Using Electrical Annealing to Repair Degradation Induced from Hot-Carrier Injection. IEEE Trans. Electron Devices 2016, 63, 910–915. [Google Scholar] [CrossRef]

- Lee, K.-S.; Park, J.-Y. N-Type Nanosheet FETs without Ground Plane Region for Process Simplification. Micromachines 2022, 13, 432. [Google Scholar] [CrossRef]

- Ota, K.; Saitoh, M.; Tanaka, C.; Numata, T. Experimental Study of Self-Heating Effects in Trigate Nanowire MOSFETs Considering Device Geometry. IEEE Trans. Electron Devices 2012, 59, 3239–3242. [Google Scholar] [CrossRef]

| Parameters | Materials | Values |

|---|---|---|

| Gate length, LG | TiAlC | 12 nm [20] |

| Channel width, WNS | Si | 30 nm [13] |

| Nanosheet thickness, TNS | Si | 5 nm [13] |

| Inner spacer thickness, TIN | Si3N4 | 3 nm [13] |

| Nanosheet-to-nanosheet vertical space, VSPC | - | 15 nm |

| Gate dielectric | SiO2/HfO2 | 1/3 nm |

| Source/drain length, LS/D | Si | 12 nm [13] |

| Source/drain height, HS/D | Si | 60 nm |

| Vacuum dielectric | Vacuum | 1 nm |

| Material | Relative Permittivity | Thermal Conductivity (W/mK) | Electrical Conductivity (S/m) |

|---|---|---|---|

| Si | 11.90 [21] | Si substrate 140 [22] | 7.68 × 10−3 |

| Channels 18 [22] | 7.68 × 10−3 | ||

| Source/drain 38 [22] | 5 × 105 | ||

| Si3N4 | 7.50 [23] | 3.2 | 1 × 10−8 |

| SiO2 | 3.90 [21] | 1.4 | 1 × 10−17 |

| HfO2 | 22 | 1.06 | 1 × 10−14 |

| TiAlC | 1 | 46 | 2. × 106 |

| Vacuum | 1 [21,23] | 0.024 [24] | 1 × 10−15 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, D.-H.; Lee, K.-S.; Park, J.-Y. Vacuum Inner Spacer to Improve Annealing Effect during Electro-Thermal Annealing of Nanosheet FETs. Micromachines 2022, 13, 987. https://doi.org/10.3390/mi13070987

Wang D-H, Lee K-S, Park J-Y. Vacuum Inner Spacer to Improve Annealing Effect during Electro-Thermal Annealing of Nanosheet FETs. Micromachines. 2022; 13(7):987. https://doi.org/10.3390/mi13070987

Chicago/Turabian StyleWang, Dong-Hyun, Khwang-Sun Lee, and Jun-Young Park. 2022. "Vacuum Inner Spacer to Improve Annealing Effect during Electro-Thermal Annealing of Nanosheet FETs" Micromachines 13, no. 7: 987. https://doi.org/10.3390/mi13070987

APA StyleWang, D.-H., Lee, K.-S., & Park, J.-Y. (2022). Vacuum Inner Spacer to Improve Annealing Effect during Electro-Thermal Annealing of Nanosheet FETs. Micromachines, 13(7), 987. https://doi.org/10.3390/mi13070987