Practical Submodule Capacitor Sizing for Modular Multilevel Converter Considering Grid Faults

Abstract

:1. Introduction

2. Steady-State Analysis of SM Capacitor Voltage

3. Transient SM Capacitor Voltage during Grid Faults

3.1. System Dynamics and Control Schemes

3.2. Grid Fault SM Voltage Estimation

4. Design Consideration of SM Capacitors

4.1. Energy Storage Requirement

4.2. SM Ripple Voltage Requirement

4.3. Transient SM Voltage Constraint

4.4. ESR, Thermal Resistance, and Lifetime Assessment

5. SM Capacitor Selection

5.1. SM Capacitance Selection

5.2. Rated Voltage Selection

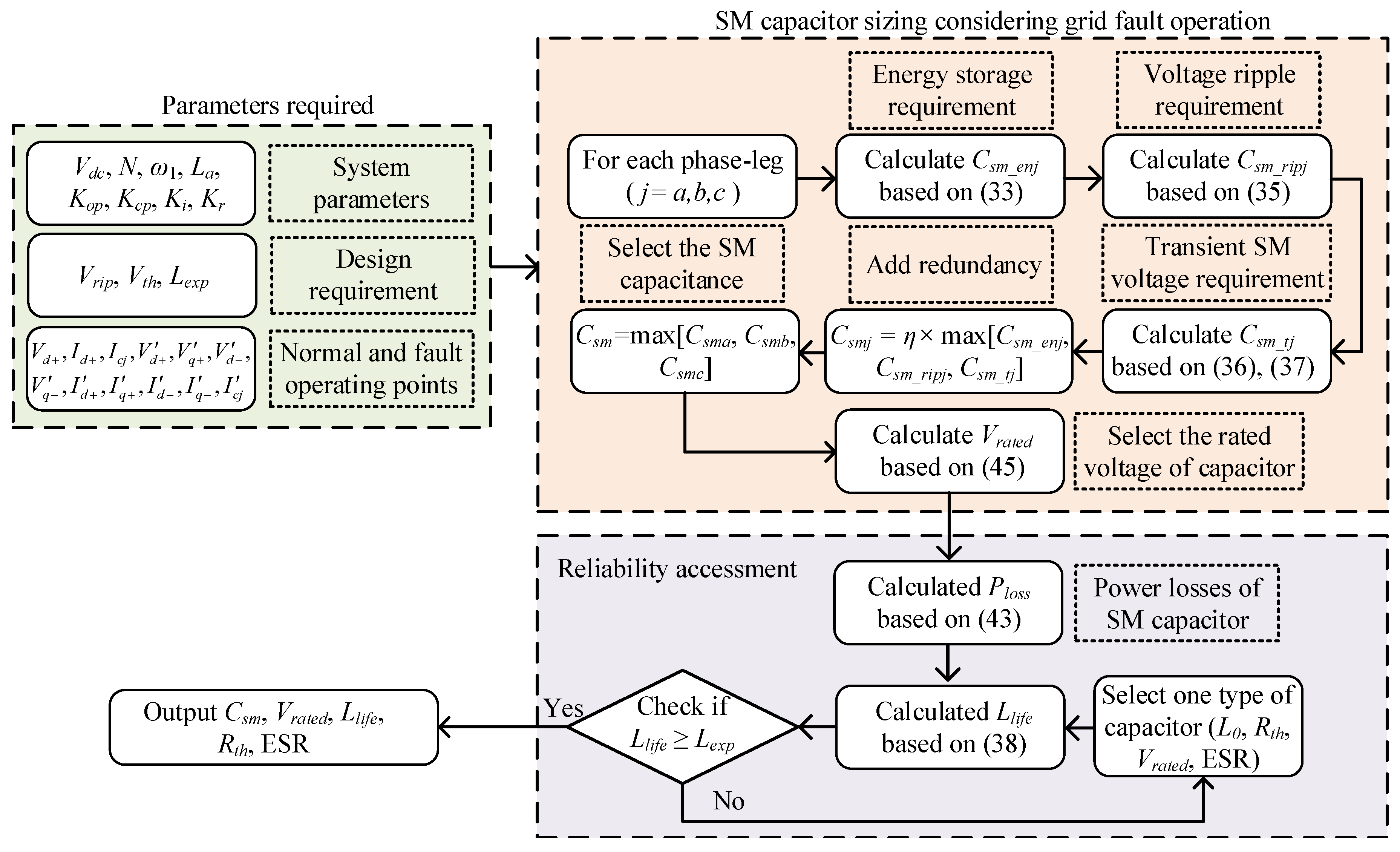

5.3. Design Flowchart

6. Case Study

6.1. Design Example

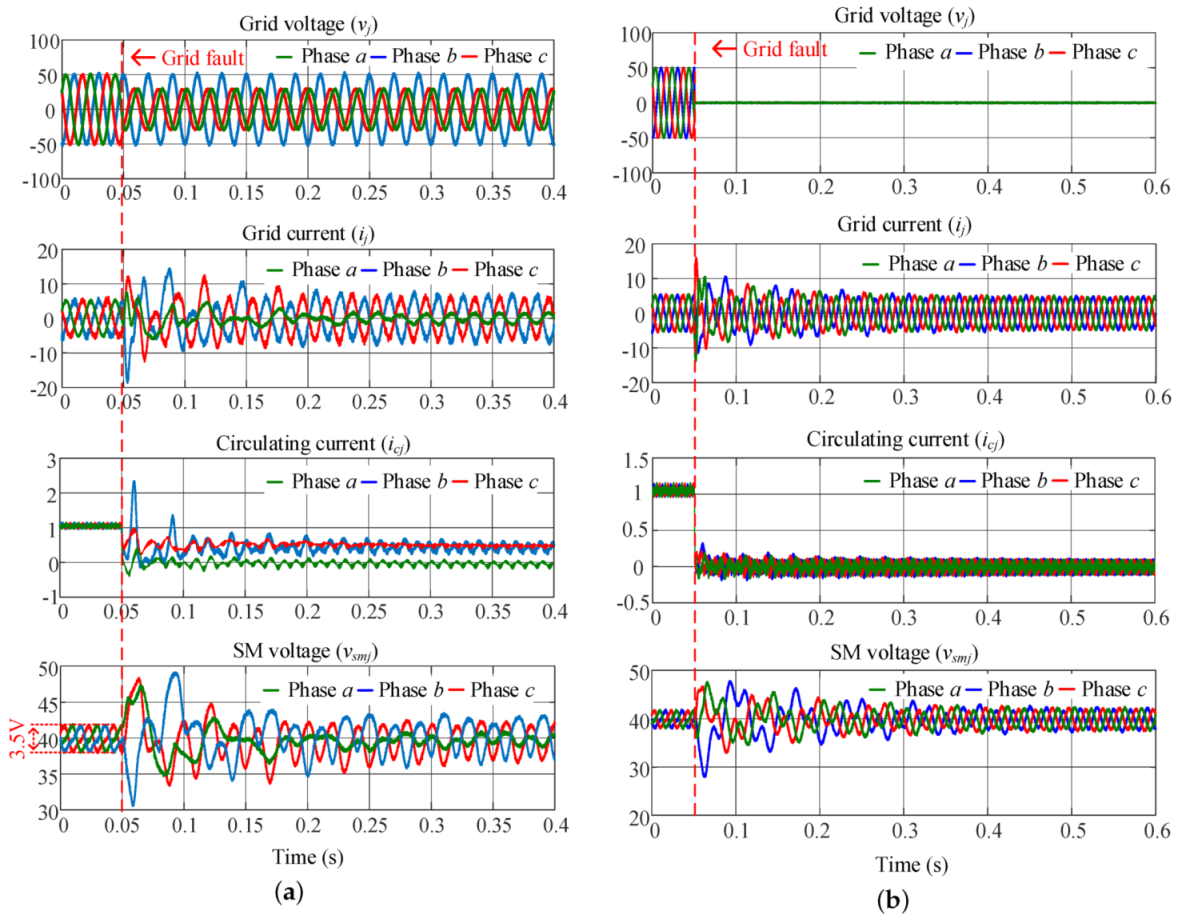

6.2. Experimental Verification

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Pang, H.; Wei, X. Research on Key Technology and Equipment for Zhangbei 500kV DC Grid. In Proceedings of the International Power Electronics Conference (ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 2343–2351. [Google Scholar]

- Ou, K.; Rao, H.; Cai, Z.; Guo, H.; Lin, X.; Guan, L.; Maguire, T.; Warkentin, B.; Chen, Y. MMC-HVDC Simulation and Testing Based on Real-Time Digital Simulator and Physical Control System. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 1109–1116. [Google Scholar]

- ABB Solusion. Available online: https://new.abb.com/systems/hvdc/hvdc-light (accessed on 20 May 2020).

- Akagi, H. Classification, Terminology, and Application of the Modular Multilevel Cascade Converter (MMCC). IEEE Trans. Power Electron. 2011, 26, 3119–3130. [Google Scholar] [CrossRef]

- Dekka, A.; Wu, B.; Fuentes, R.L.; Perez, M.; Zargari, N.R. Evolution of Topologies, Modeling, Control Schemes, and Applications of Modular Multilevel Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1631–1656. [Google Scholar] [CrossRef]

- Perez, M.A.; Bernet, S.; Rodriguez, J.; Kouro, S.; Lizana, R. Circuit Topologies, Modeling, Control Schemes, and Applications of Modular Multilevel Converters. IEEE Trans. Power Electron. 2015, 30, 4–17. [Google Scholar] [CrossRef]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G.D. Modular Multilevel Converters for HVDC Applications: Review on Converter Cells and Functionalities. IEEE Trans. Power Electron. 2015, 30, 18–36. [Google Scholar] [CrossRef]

- Debnath, S.; Qin, J.; Bahrani, B.; Saeedifard, M.; Barbosa, P. Operation, Control, and Applications of the Modular Multilevel Converter: A Review. IEEE Trans. Power Electron. 2015, 30, 37–53. [Google Scholar] [CrossRef]

- Ilves, K.; Antonopoulos, A.; Norrga, S.; Nee, H. Steady-State Analysis of Interaction Between Harmonic Components of Arm and Line Quantities of Modular Multilevel Converters. IEEE Trans. Power Electron. 2012, 27, 57–68. [Google Scholar] [CrossRef]

- Iov, F.; Hansen, A.D.; Sorensen, P.; Cutululis, N.A. Mapping of Grid Faults and Grid Codes; Tech. Rep. Riso-R-1617 (EN); Riso National Laboratory, Technical University of Denmark: Roskilde, Denmark, 2007. [Google Scholar]

- VDN—Transmission Code 2003; Network and System Rules of the German Transmission System Operators: Berlin, Germany, 2003.

- Hydro-Quebec Technical Information. Available online: http://www.hydroquebec.com/transenergie/fr/commerce/pdf/exigence_raccordement_fev_09_en.pdf (accessed on 20 May 2020).

- Shi, X.; Wang, Z.; Liu, B.; Liu, Y.; Tolbert, L.M.; Wang, F. Characteristic Investigation and Control of a Modular Multilevel Converter-Based HVDC System Under Single-Line-to-Ground Fault Conditions. IEEE Trans. Power Electron. 2015, 30, 408–421. [Google Scholar] [CrossRef]

- Li, J.; Konstantinou, G.; Wickramasinghe, H.R.; Pou, J. Operation and Control Methods of Modular Multilevel Converters in Unbalanced AC Grids: A Review. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1258–1271. [Google Scholar] [CrossRef]

- Li, G.; Liang, J.; Ma, F.; Ugalde-Loo, C.E.; Liang, H. Analysis of Single-Phase-to-Ground Faults at the Valve-Side of HB-MMCs in HVDC Systems. IEEE Trans. Ind. Electron. 2019, 66, 2444–2453. [Google Scholar] [CrossRef]

- Nademi, H.; Norum, L. Analytical circuit oriented modelling and performance assessment of modular multilevel converter. IET Power Electron. 2015, 8, 1625–1635. [Google Scholar] [CrossRef]

- Ilves, K.; Norrga, S.; Harnefors, L.; Nee, H. On Energy Storage Requirements in Modular Multilevel Converters. IEEE Trans. Power Electron. 2014, 29, 77–88. [Google Scholar] [CrossRef]

- Bärnklau, H.; Gensior, A.; Bernet, S. Submodule Capacitor Dimensioning for Modular Multilevel Converters. IEEE Trans. Ind. Appl. 2014, 50, 1915–1923. [Google Scholar] [CrossRef]

- Merlin, M.M.C.; Green, T.C. Cell capacitor sizing in multilevel converters: Cases of the modular multilevel converter and alternate arm converter. IET Power Electron. 2015, 8, 350–360. [Google Scholar] [CrossRef]

- Tang, Y.; Ran, L.; Alatise, O.; Mawby, P. Capacitor Selection for Modular Multilevel Converter. IEEE Trans. Ind. Appl. 2016, 52, 3279–3293. [Google Scholar] [CrossRef]

- Guan, M.; Xu, Z. Modeling and Control of a Modular Multilevel Converter-Based HVDC System Under Unbalanced Grid Conditions. IEEE Trans. Power Electron. 2012, 27, 4858–4867. [Google Scholar] [CrossRef]

- Shi, X.; Wang, Z.; Liu, B.; Li, Y.; Tolbert, L.M.; Wang, F. Steady-State Modeling of Modular Multilevel Converter Under Unbalanced Grid Conditions. IEEE Trans. Power Electron. 2017, 32, 7306–7324. [Google Scholar] [CrossRef]

- Li, J.; Konstantinou, G.; Wickramasinghe, H.R.; Pou, J.; Wu, X.; Jin, X. Impact of Circulating Current Control in Capacitor Voltage Ripples of Modular Multilevel Converters Under Grid Imbalances. IEEE Trans. Power Deliv. 2018, 33, 1257–1267. [Google Scholar] [CrossRef]

- Zhao, C.; Lei, M.; Hu, Y.; Li, Z.; Gao, F.; Wang, P.; Li, Y. Energy Storage Requirement Optimization of Hybrid Modular Multilevel Converter With Circulating Current Injection. IEEE Trans. Ind. Electron. 2019, 66, 6637–6648. [Google Scholar] [CrossRef]

- Li, B.; Zhang, Y.; Wang, G.; Sun, W.; Xu, D.; Wang, W. A Modified Modular Multilevel Converter With Reduced Capacitor Voltage Fluctuation. IEEE Trans. Ind. Electron. 2015, 62, 6108–6119. [Google Scholar] [CrossRef]

- Tu, Q.; Xu, Z.; Chang, Y.; Guan, L. Suppressing DC Voltage Ripples of MMC-HVDC Under Unbalanced Grid Conditions. IEEE Trans. Power Deliv. 2012, 27, 1332–1338. [Google Scholar] [CrossRef]

- Picas, R.; Ceballos, S.; Pou, J.; Zaragoza, J.; Konstantinou, G.; Agelidis, V.G. Closed-Loop Discontinuous Modulation Technique for Capacitor Voltage Ripples and Switching Losses Reduction in Modular Multilevel Converters. IEEE Trans. Power Electron. 2015, 30, 4714–4725. [Google Scholar] [CrossRef] [Green Version]

- Kong, Z.; Huang, X.; Wang, Z.; Xiong, J.; Zhang, K. Active Power Decoupling for Submodules of a Modular Multilevel Converter. IEEE Trans. Power Electron. 2018, 33, 125–136. [Google Scholar] [CrossRef]

- Yin, Z.; Yang, Y.; Wang, H. Transient Voltage Stress Modeling for Submodules of Modular Multilevel Converters under Grid Voltage Sags. In Proceedings of the International Power Electronics Conference (ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 1021–1026. [Google Scholar]

- Yin, Z.; Qiu, H.; Yang, Y.; Tang, Y.; Wang, H. Impact of the Circulating Current Control on Transient Submodule Voltage Stresses for Grid-Tied Modular Multilevel Converters During Grid Faults. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 1–6. [Google Scholar]

- Guo, X.; Liu, W.; Zhang, X.; Sun, X.; Lu, Z.; Guerrero, J.M. Flexible Control Strategy for Grid-Connected Inverter Under Unbalanced Grid Faults Without PLL. IEEE Trans. Power Electron. 2015, 30, 1773–1778. [Google Scholar] [CrossRef] [Green Version]

- Jamshidifar, A.; Jovcic, D. Small-Signal Dynamic DQ Model of Modular Multilevel Converter for System Studies. IEEE Trans. Power Deliv. 2016, 31, 191–199. [Google Scholar] [CrossRef] [Green Version]

- Siemaszko, D.; Antonopoulos, A.; Ilves, K.; Vasiladiotis, M.; Ängquist, L.; Nee, H. Evaluation of control and modulation methods for modular multilevel converters. In Proceedings of the International Power Electronics Conference (ECCE ASIA), Sapporo, Japan, 21–24 June 2010; pp. 746–753. [Google Scholar]

- Deng, F.; Zhu, R.; Liu, D.; Wang, Y.; Wang, H.; Chen, Z.; Cheng, M. Protection Scheme for Modular Multilevel Converters Under Diode Open-Circuit Faults. IEEE Trans. Power Electron. 2018, 33, 2866–2877. [Google Scholar] [CrossRef] [Green Version]

- Wang, H.; Blaabjerg, F. Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef] [Green Version]

- AVX Medium Power Film Capacitors datasheet. Available online: http://datasheets.avx.com/ffli.pdf (accessed on 20 May 2020).

- Marzoughi, A.; Burgos, R.; Boroyevich, D.; Xue, Y. Steady-state analysis of voltages and currents in modular multilevel converter based on average model. In Proceedings of the Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 3522–3528. [Google Scholar]

- Soliman, H.; Wang, H.; Blaabjerg, F. A Review of the Condition Monitoring of Capacitors in Power Electronic Converters. IEEE Trans. Ind. Appl. 2016, 52, 4976–4989. [Google Scholar] [CrossRef]

- Vishay Technical Information. Available online: https://www.vishay.com/docs/26033/gentechinfofilm.pdf (accessed on 20 May 2020).

- Sharifabadi, K.; Harnefors, L.; Nee, H.P.; Norrga, S.; Teodorescu, R. Design, Control and Application of Modular Multilevel Converters for HVDC Transmission Systems; Wiley-IEEE Press: Piscataway, NJ, USA, 2016. [Google Scholar]

| Normal Operation Point | Grid Fault Operation Point |

|---|---|

| = | = |

| = 0 | = |

| = 0 | = |

| = 0 | = |

| = | = |

| = 0 | = |

| = 0 | = |

| = 0 | = |

| = | = |

| System Parameters | |

|---|---|

| SM number in each arm (N) | 3 |

| Arm Inductance (La) | 5 mH |

| Grid frequency | 50 Hz |

| Switching frequency | 8 kHz |

| DC-bus voltage | 120 V |

| Kop | 10 |

| Ki | 60 |

| Kcp | 5 |

| Kr | 35 |

| Design Requirement | |

| Peak-to-peak SM voltage ripple (Vrip) | 4 V |

| Maximum SM voltage threshold (Vth) | 50 V |

| Capacitance redundancy factor () | 1.2 |

| Normal Operation Point | |

|---|---|

| Grid voltage | = 50 V |

| Grid current injection | = 5 A; = 0 |

| Circulating current reference | = 0.417 A |

| Single-Line-to-Ground Condition | |

| Grid voltage | = 33.5 V |

| = 16.5 V | |

| Grid current injection | = 1.67 A |

| = 2.875 A | |

| = 0; = −3.5 A | |

| Three-Phase Short-Circuit Condition | |

| Grid voltage | = 0; = 0 |

| Grid current injection | = 0; = 4.5 A |

| = 0; = 0 | |

| Part Number | UBY2A681MHL |

|---|---|

| Capacitance | 680 F |

| ESR | 28 m at 50 Hz; 14 m at 100 Hz |

| Thermal resistance | 1.5 C/W |

| Reference lifetime | 3000 h at 125 C, 20–50 V |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yin, Z.; Qiu, H.; Yang, Y.; Tang, Y.; Wang, H. Practical Submodule Capacitor Sizing for Modular Multilevel Converter Considering Grid Faults. Appl. Sci. 2020, 10, 3550. https://doi.org/10.3390/app10103550

Yin Z, Qiu H, Yang Y, Tang Y, Wang H. Practical Submodule Capacitor Sizing for Modular Multilevel Converter Considering Grid Faults. Applied Sciences. 2020; 10(10):3550. https://doi.org/10.3390/app10103550

Chicago/Turabian StyleYin, Zhijian, Huan Qiu, Yongheng Yang, Yi Tang, and Huai Wang. 2020. "Practical Submodule Capacitor Sizing for Modular Multilevel Converter Considering Grid Faults" Applied Sciences 10, no. 10: 3550. https://doi.org/10.3390/app10103550