Common-Mode Voltage Analysis and Reduction for the Quasi-Z-Source Inverter with a Split Inductor

Abstract

1. Introduction

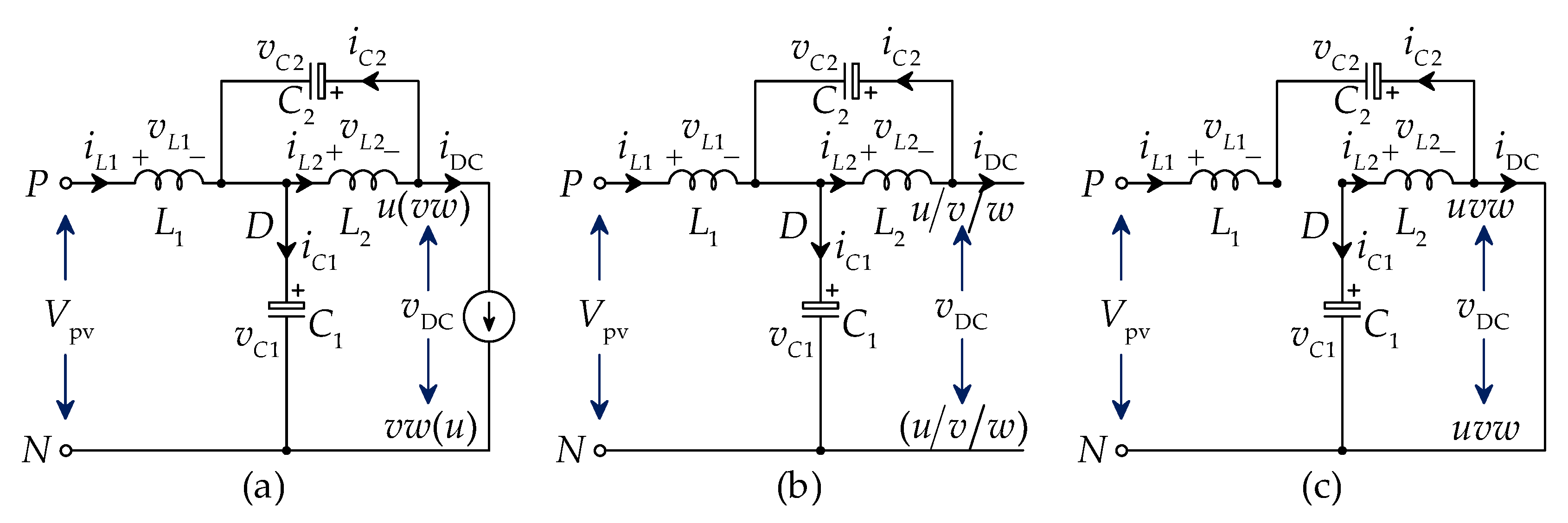

2. CMV Analysis in Different Operational States for the qZSI

2.1. CMV during the Active State

2.2. CMV during the Null State

2.3. CMV during the Shoot-Through State

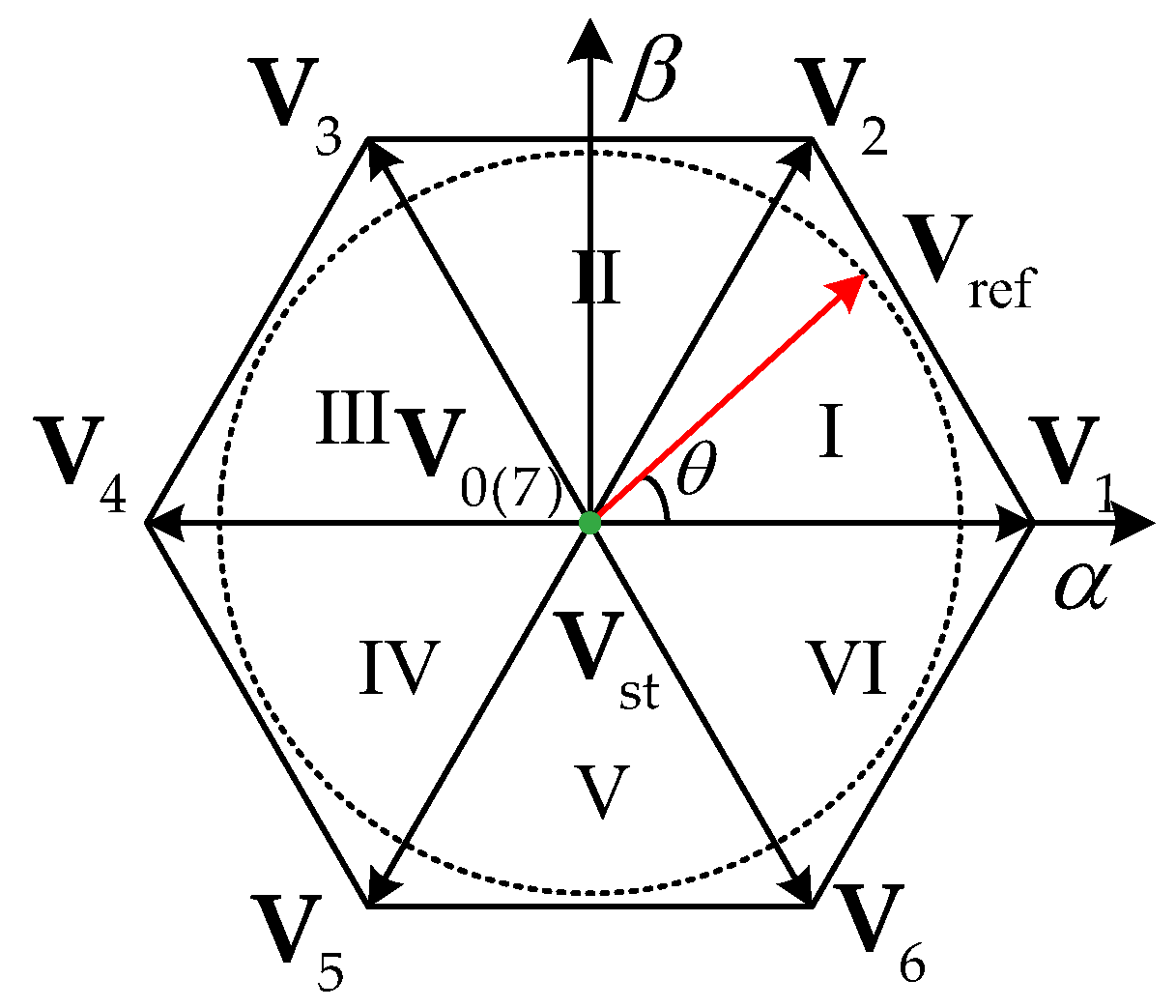

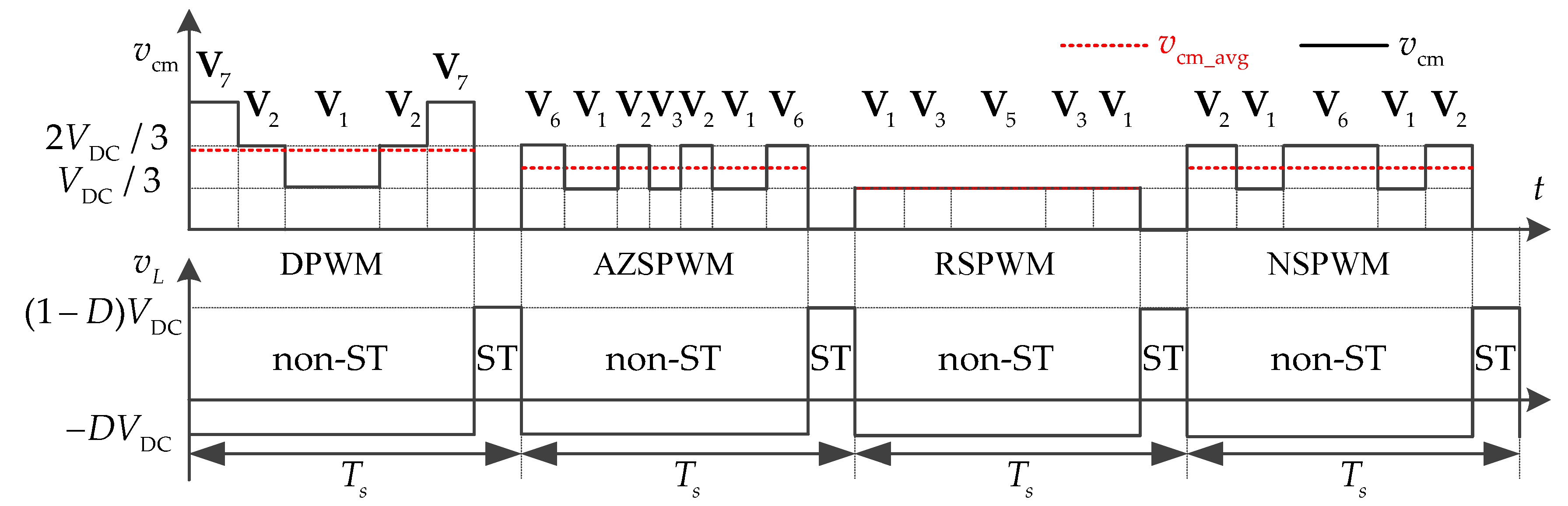

3. CMV Reduction Strategies for the VSI

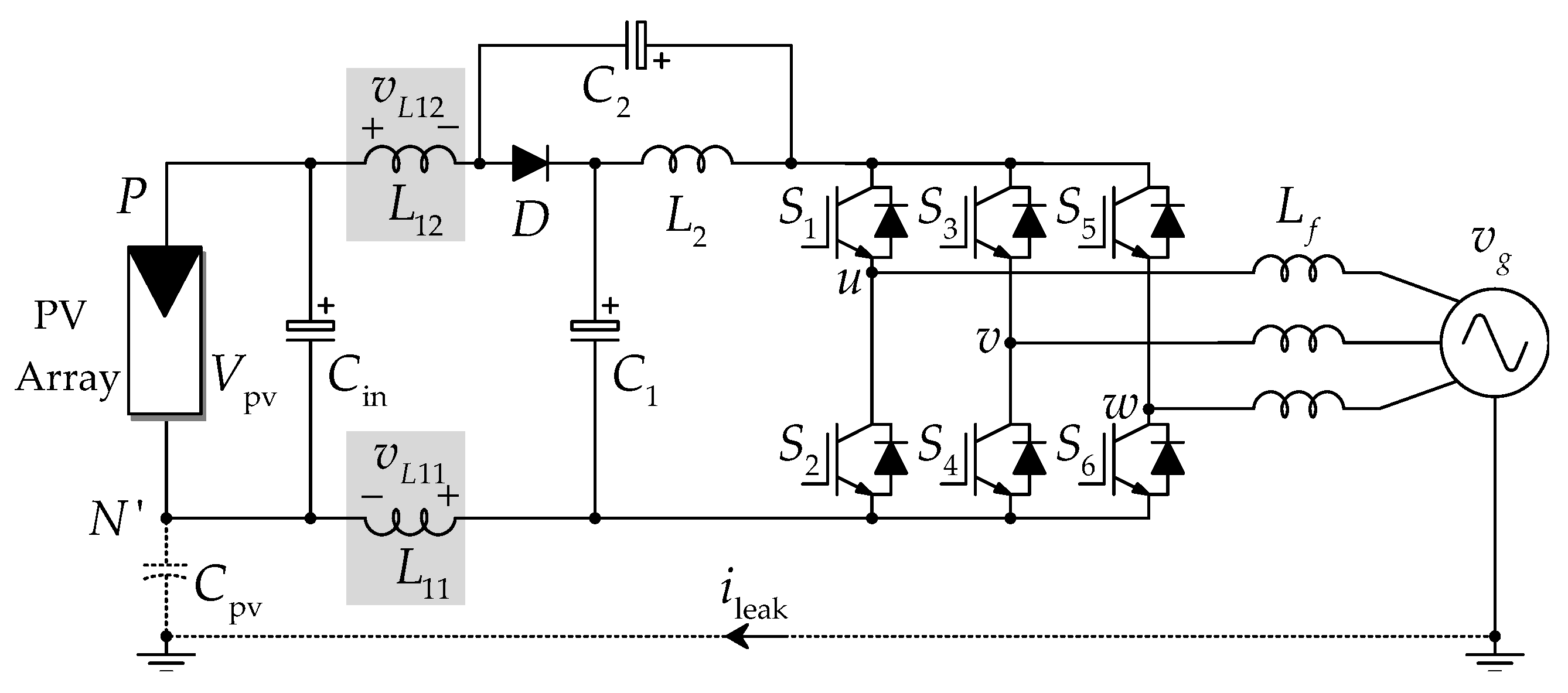

4. Modified qZSI for CMV Reduction

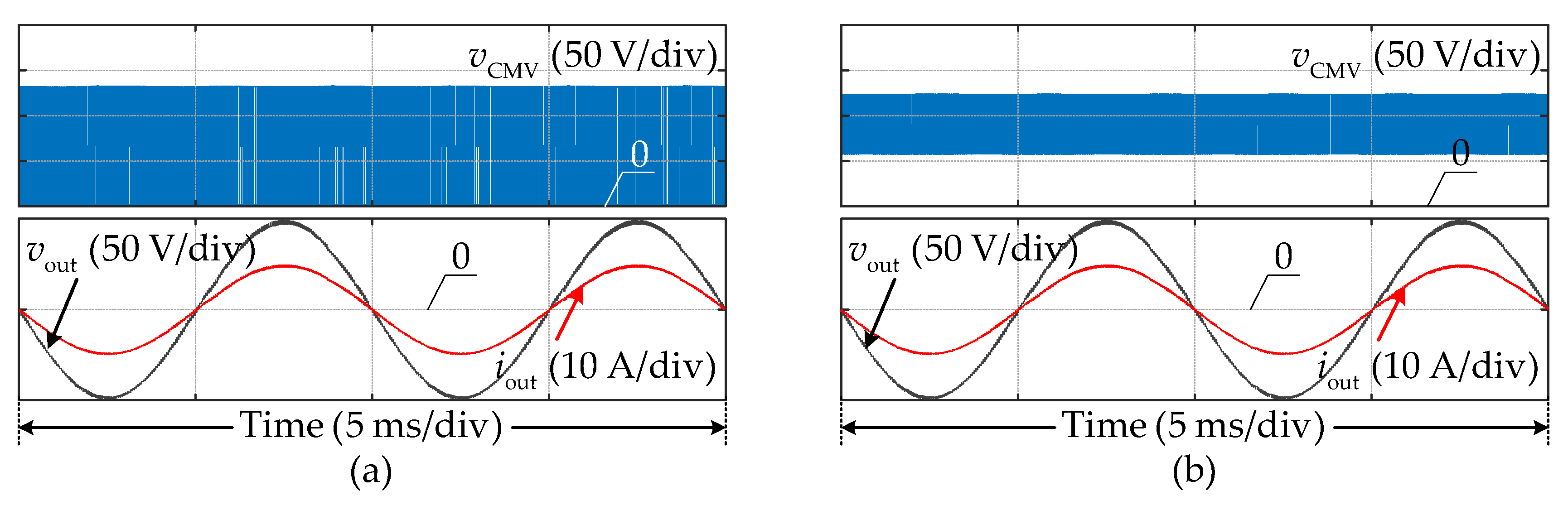

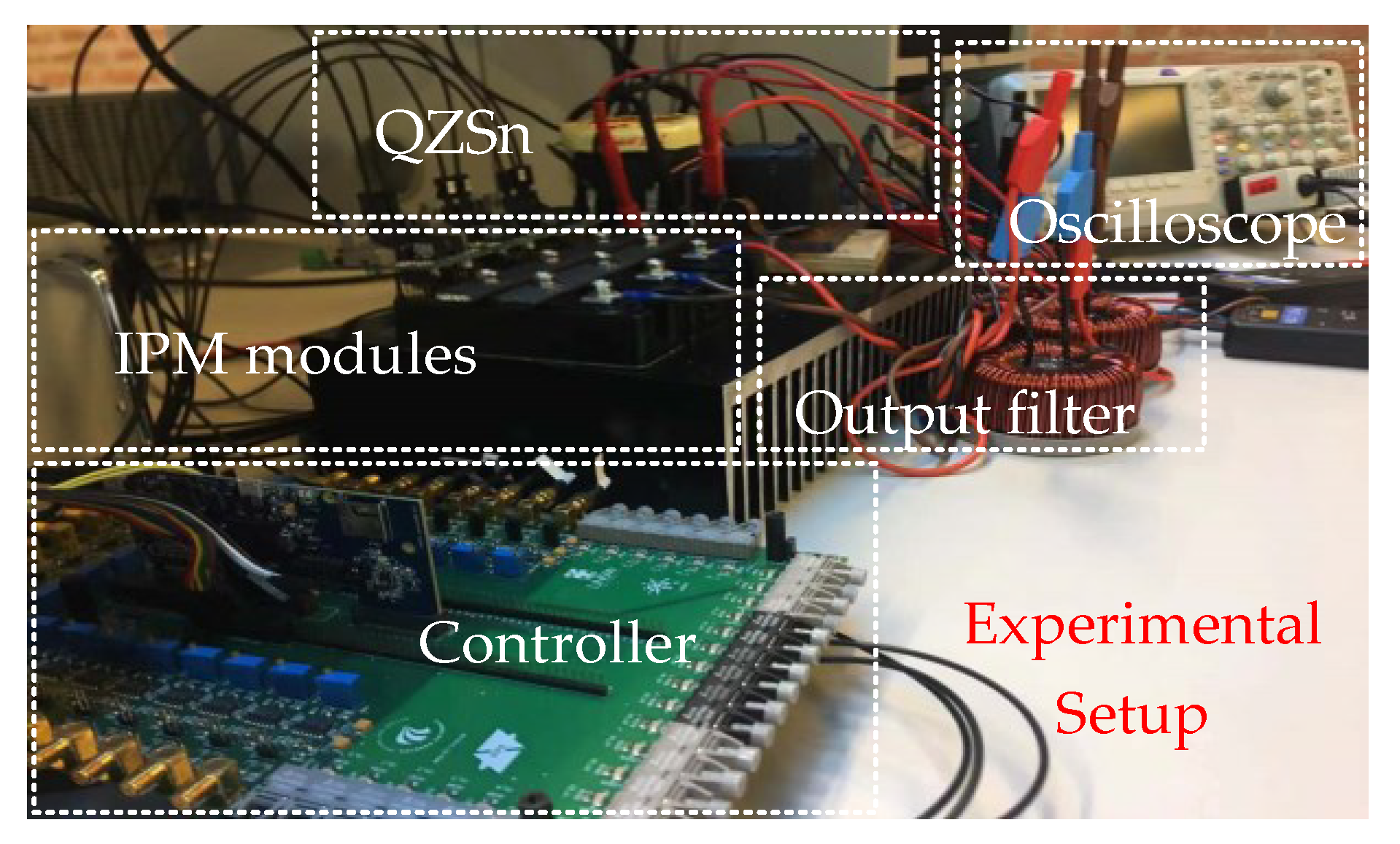

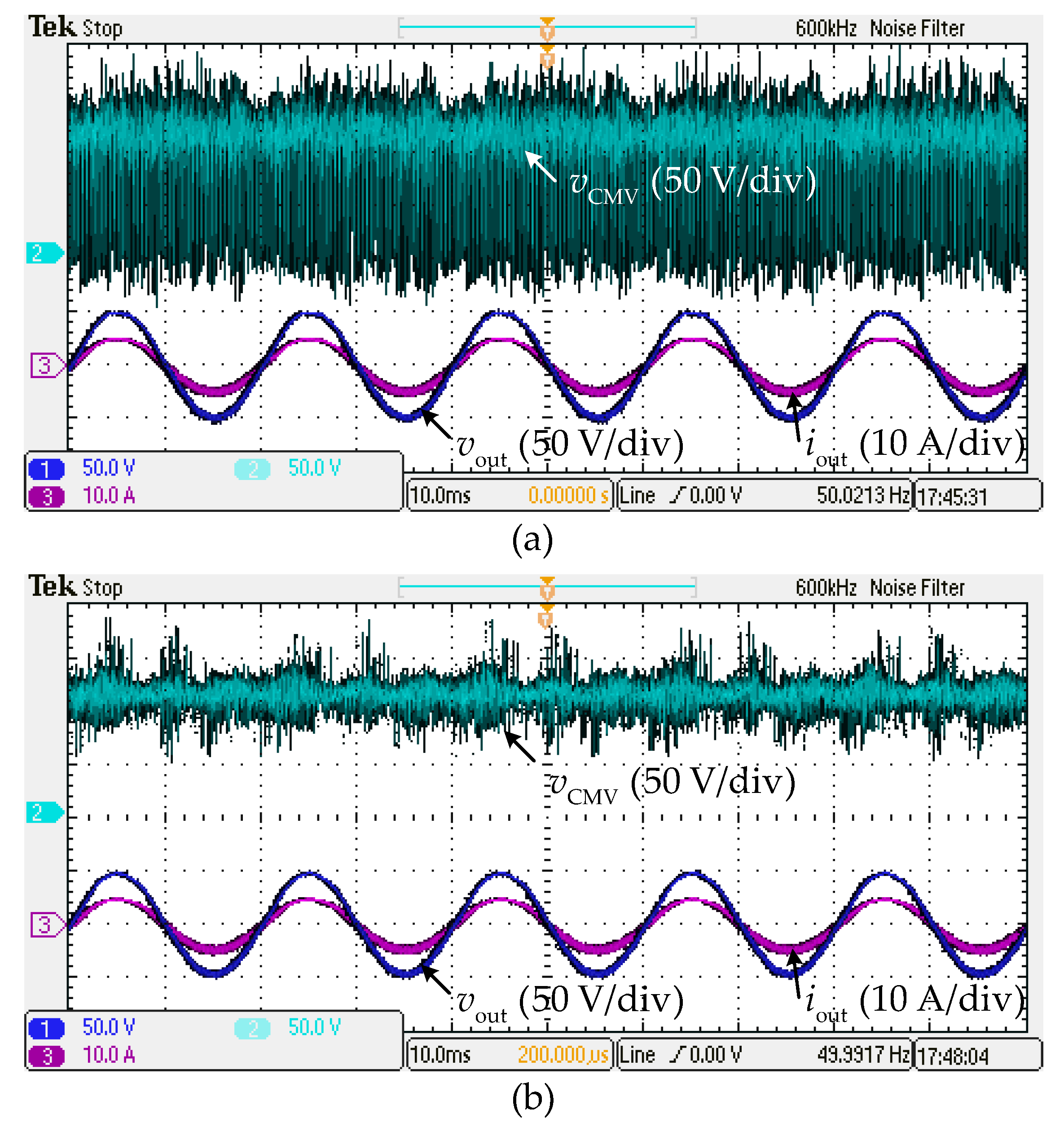

5. Simulation and Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kerekes, T.; Koutroulis, E.; Sera, D.; Teodorescu, R.; Katsanevakis, M. An Optimization Method for Designing Large PV Plants. IEEE J. Photovolt. 2013, 3, 814–822. [Google Scholar] [CrossRef]

- Cacciato, M.; Consoli, A.; Scarcella, G.; Testa, A. Reduction of Common-Mode Currents in PWM Inverter Motor Drives. IEEE Trans. Ind. Appl. 1999, 35, 469–476. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Liserre, M.; Klumpner, C.; Sumner, M. Evaluation of Three-Phase Transformerless Photovoltaic Inverter Topologies. IEEE Trans. Power Electron. 2009, 24, 2202–2211. [Google Scholar] [CrossRef]

- Bradaschia, F.; Cavalcanti, M.C.; Ferraz, P.E.P.; Azevedo, G.M.S.; Neves, F.A.S.; dos Santos, E.C. Stability Analysis of Reduced Leakage Current Modulation Techniques for Z-Source Inverters in Transformerless Photovoltaic Applications. In Proceedings of the ECCE, Delft, The Netherlands, 25–27 August 2011; pp. 2268–2275. [Google Scholar]

- Tang, Y.; Yao, W.; Loh, P.C.; Blaabjerg, F. Highly Reliable Transformerless Photovoltaic Inverters With Leakage Current and Pulsating Power Elimination. IEEE Trans. Ind. Electron. 2016, 63, 1016–1026. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S. Leakage Current Analytical Model and Application in Single-Phase Transformerless Photovoltaic Grid-Connected Inverter. IEEE Trans. Electromagn. Compat. 2010, 52, 902–913. [Google Scholar] [CrossRef]

- Yang, B.; Li, W.; Gu, Y.; Cui, W.; He, X. Improved Transformerless Inverter with Common-Mode Leakage Current Elimination for a Photovoltaic Grid-Connected Power System. IEEE Trans. Power Electron. 2012, 27, 752–762. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Rodriguez, P.; Vazquez, G.; Aldabas, E. A New High-Efficiency Single-Phase Transformerless PV Inverter Topology. IEEE Trans. Ind. Electron. 2011, 58, 184–191. [Google Scholar] [CrossRef]

- Zhou, Y.; Huang, W.; Zhao, P.; Zhao, J. A Transformerless Grid-Connected Photovoltaic System Based on the Coupled Inductor Single-Stage Boost Three-Phase Inverter. IEEE Trans. Power Electron. 2014, 29, 1041–1046. [Google Scholar] [CrossRef]

- Liu, W.; Yang, Y.; Kerekes, T. Modified Quasi-Z-Source Inverter with Model Predictive Control for Constant Common-Mode Voltage. In Proceedings of the ICPE-ECCE Asia, Busan, Korea, 27–30 May 2019; pp. 1–6. [Google Scholar]

- Hava, A.M.; Ün, E. A High-Performance PWM Algorithm for Common-Mode Voltage Reduction in Three-Phase Voltage Source Inverters. IEEE Trans. Power Electron. 2011, 26, 1998–2008. [Google Scholar] [CrossRef]

- Hou, C.C.; Shih, C.C.; Cheng, P.T.; Hava, A.M. Common-Mode Voltage Reduction Pulsewidth Modulation Techniques for Three-Phase Grid-Connected Converters. IEEE Trans. Power Electron. 2013, 28, 1971–1979. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Liserre, M. Common Mode Voltage in Case of Transformerless PV Inverters Connected to the Grid. In Proceedings of the ISIE, Cambridge, UK, 30 June–2 July 2008; IEEE: Cambridge, UK, 2008; pp. 2390–2395. [Google Scholar]

- Buticchi, G.; Barater, D.; Lorenzani, E.; Franceschini, G. Digital Control of Actual Grid-Connected Converters for Ground Leakage Current Reduction in PV Transformerless Systems. IEEE Trans. Ind. Inform. 2012, 8, 563–572. [Google Scholar] [CrossRef]

- Hoseini, S.K.; Sheikholeslami, A.; Adabi, J. Predictive Modulation Schemes to Reduce Common-Mode Voltage in Three-Phase Inverters-Fed AC Drive Systems. IET Power Electron. 2014, 7, 840–849. [Google Scholar] [CrossRef]

- Rojas, C.A.; Aguirre, M.; Kouro, S.; Geyer, T.; Gutierrez, E. Leakage Current Mitigation in Photovoltaic String Inverter Using Predictive Control With Fixed Average Switching Frequency. IEEE Trans. Ind. Electron. 2017, 64, 9344–9354. [Google Scholar] [CrossRef]

- Kakosimos, P.; Abu-Rub, H. Predictive Control of a Grid-Tied Cascaded Full-Bridge NPC Inverter for Reducing High-Frequency Common-Mode Voltage Components. IEEE Trans. Ind. Inform. 2018, 14, 2385–2394. [Google Scholar] [CrossRef]

- Wang, X.; Zou, J.; Ma, L.; Zhao, J.; Xie, C.; Li, K.; Meng, L.; Guerrero, J.M. Model Predictive Control Methods of Leakage Current Elimination for a Three-Level T-Type Transformerless PV Inverter. IET Power Electron. 2018, 11, 1492–1498. [Google Scholar] [CrossRef]

- Mun, S.k.; Kwak, S. Reducing Common-Mode Voltage of Three-Phase VSIs Using the Predictive Current Control Method Based on Reference Voltage. J. Power Electron. 2015, 15, 712–720. [Google Scholar] [CrossRef]

- Anderson, J.; Peng, F.Z. Four Quasi-Z-Source Inverters. In Proceedings of the PESC, Rhodes, Greece, 15–19 June 2008; pp. 2743–2749. [Google Scholar]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E. Impedance-Source Networks for Electric Power Conversion Part I: A Topological Review. IEEE Trans. Power Electron. 2015, 30, 699–716. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E.; Yang, S. Impedance-Source Networks for Electric Power Conversion Part II: Review of Control and Modulation Techniques. IEEE Trans. Power Electron. 2015, 30, 1887–1906. [Google Scholar] [CrossRef]

- Liu, W.; Yuan, J.; Yang, Y.; Kerekes, T. Modeling and Control of Single-Phase Quasi-Z-Source Inverters. In Proceedings of the IECON, Washington, DC, USA, 21–23 October 2018; pp. 3737–3742. [Google Scholar]

- Liu, W.; Yang, Y.; Kerekes, T. Characteristic Analysis of the Grid-Connected Impedance-Source Inverter for PV Applications. In Proceedings of the PEDG, Xi’an, China, 3–6 June 2019; pp. 874–880. [Google Scholar]

- Guo, X.; Zhou, J.; He, R.; Jia, X.; Rojas, C.A. Leakage Current Attenuation of a Three-Phase Cascaded Inverter for Transformerless Grid-Connected PV Systems. IEEE Trans. Ind. Electron. 2018, 65, 676–686. [Google Scholar] [CrossRef]

- Noroozi, N.; Zolghadri, M.R.; Yaghoubi, M. Comparison of Common-Mode Voltage in Three-Phase Quasi-Z-Source Inverters Using Different Shoot-through Implementation Methods. In Proceedings of the CPE-POWERENG, Doha, Qatar, 10–12 April 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–6. [Google Scholar]

- Noroozi, N.; Zolghadri, M.R. Three-Phase Quasi-Z-Source Inverter with Constant Common-Mode Voltage for Photovoltaic Application. IEEE Trans. Ind. Electron. 2018, 65, 4790–4798. [Google Scholar] [CrossRef]

- Guo, X.; Yang, Y.; Wang, B.; Blaabjerg, F. Leakage Current Reduction of Three-Phase Z-Source Three-Level Four-Leg Inverter for Transformerless PV System. IEEE Trans. Power Electron. 2019, 34, 6299–6308. [Google Scholar] [CrossRef]

- Guo, X.; Yang, Y.; He, R.; Wang, B.; Blaabjerg, F. Transformerless Z-Source Four-Leg PV Inverter With Leakage Current Reduction. IEEE Trans. Power Electron. 2019, 34, 4343–4352. [Google Scholar] [CrossRef]

- Meraj, M.; Rahman, S.; Iqbal, A.; Ben–Brahim, L. Common Mode Voltage Reduction in A Singlephase Quasi Z-Source Inverter for Transformerless Grid-Connected Solar PV Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 7, 1352–1363. [Google Scholar] [CrossRef]

- Liu, W.; Yang, Y.; Kerekes, T.; Blaabjerg, F. Generalized Space Vector Modulation for Ripple Current Reduction in Quasi-Z-Source Inverters. IEEE Trans. Power Electron. 2021, 36, 1730–1741. [Google Scholar] [CrossRef]

- Kayiranga, T.; Li, H.; Lin, X.; Shi, Y.; Li, H. Abnormal Operation State Analysis and Control of Asymmetric Impedance Network-Based Quasi-Z-Source PV Inverter (AIN-qZSI). IEEE Trans. Power Electron. 2016, 31, 7642–7650. [Google Scholar] [CrossRef]

- Bradaschia, F.; Cavalcanti, M.C.; Ferraz, P.E.P.; Neves, F.A.S.; dos Santos, E.C.; da Silva, J.H.G.M. Modulation for Three-Phase Transformerless Z-Source Inverter to Reduce Leakage Currents in Photovoltaic Systems. IEEE Trans. Ind. Electron. 2011, 58, 5385–5395. [Google Scholar] [CrossRef]

| Vectors | CMV Values |

|---|---|

| , , (odd vectors) | |

| , , (even vectors) | |

| (zero vector) | |

| (zero vector) | 0 |

| (shoot-through vectors) | 0 |

| Parameters | Symbol | Values |

|---|---|---|

| Input voltage | 160 V | |

| qZSI inductors | , | 700 H |

| qZSI inductor resistance | 0.05 | |

| qZSI capacitors | , | 200 F |

| qZSI capacitor resistance | 0.05 | |

| Output filter | 1.8 mH | |

| Switching frequency | 10 kHz | |

| Shoot-through duty ratio | 0.1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, W.; Yang, Y.; Kerekes, T.; Liivik, E.; Vinnikov, D.; Blaabjerg, F. Common-Mode Voltage Analysis and Reduction for the Quasi-Z-Source Inverter with a Split Inductor. Appl. Sci. 2020, 10, 8713. https://doi.org/10.3390/app10238713

Liu W, Yang Y, Kerekes T, Liivik E, Vinnikov D, Blaabjerg F. Common-Mode Voltage Analysis and Reduction for the Quasi-Z-Source Inverter with a Split Inductor. Applied Sciences. 2020; 10(23):8713. https://doi.org/10.3390/app10238713

Chicago/Turabian StyleLiu, Wenjie, Yongheng Yang, Tamas Kerekes, Elizaveta Liivik, Dmitri Vinnikov, and Frede Blaabjerg. 2020. "Common-Mode Voltage Analysis and Reduction for the Quasi-Z-Source Inverter with a Split Inductor" Applied Sciences 10, no. 23: 8713. https://doi.org/10.3390/app10238713

APA StyleLiu, W., Yang, Y., Kerekes, T., Liivik, E., Vinnikov, D., & Blaabjerg, F. (2020). Common-Mode Voltage Analysis and Reduction for the Quasi-Z-Source Inverter with a Split Inductor. Applied Sciences, 10(23), 8713. https://doi.org/10.3390/app10238713