Electrical Coupling of Monolithic 3D Inverters (M3INVs): MOSFET and Junctionless FET

Abstract

:1. Introduction

2. Structure and Simulation Method

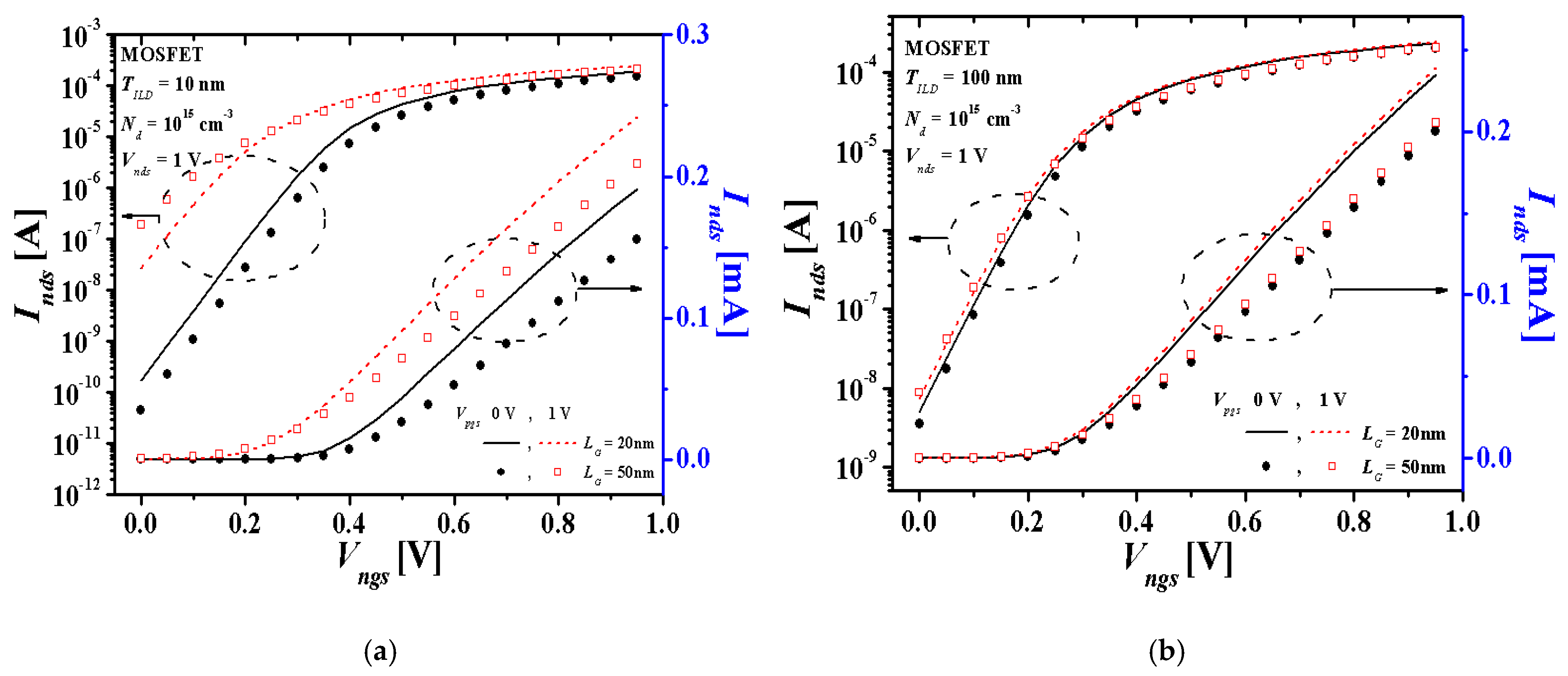

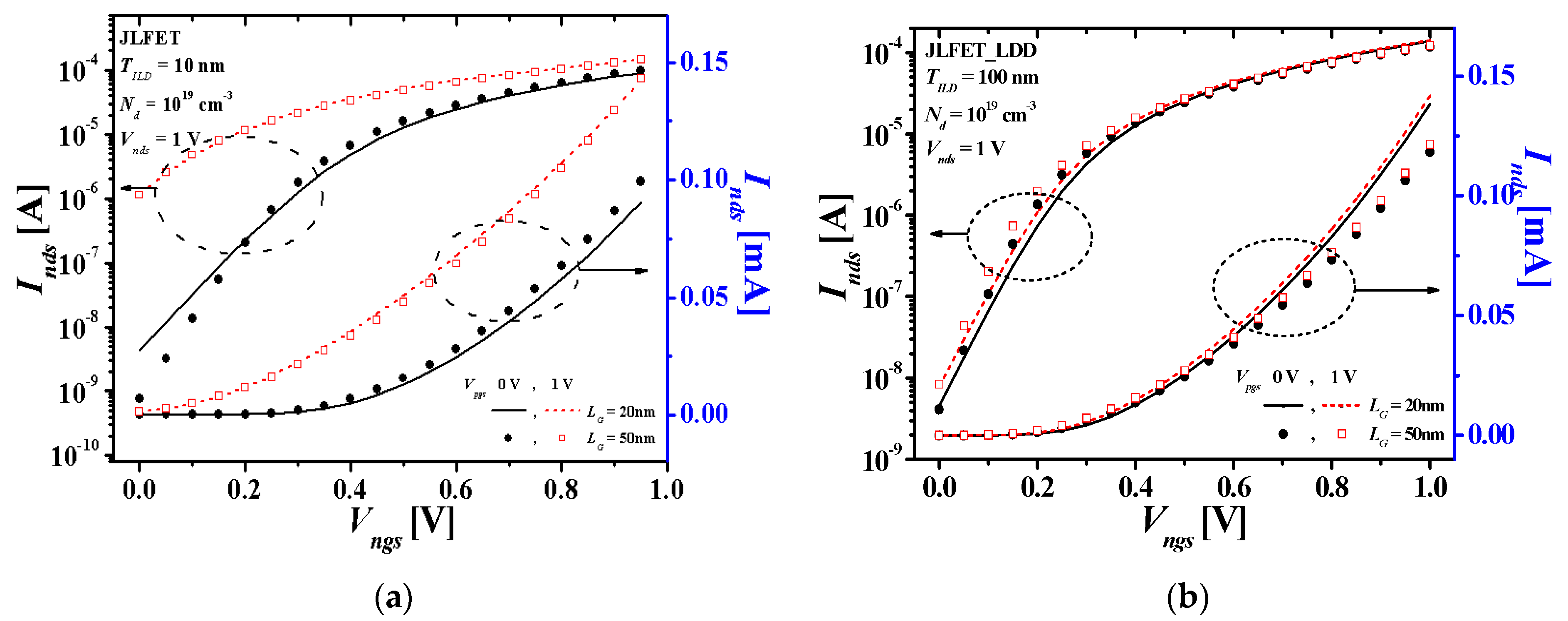

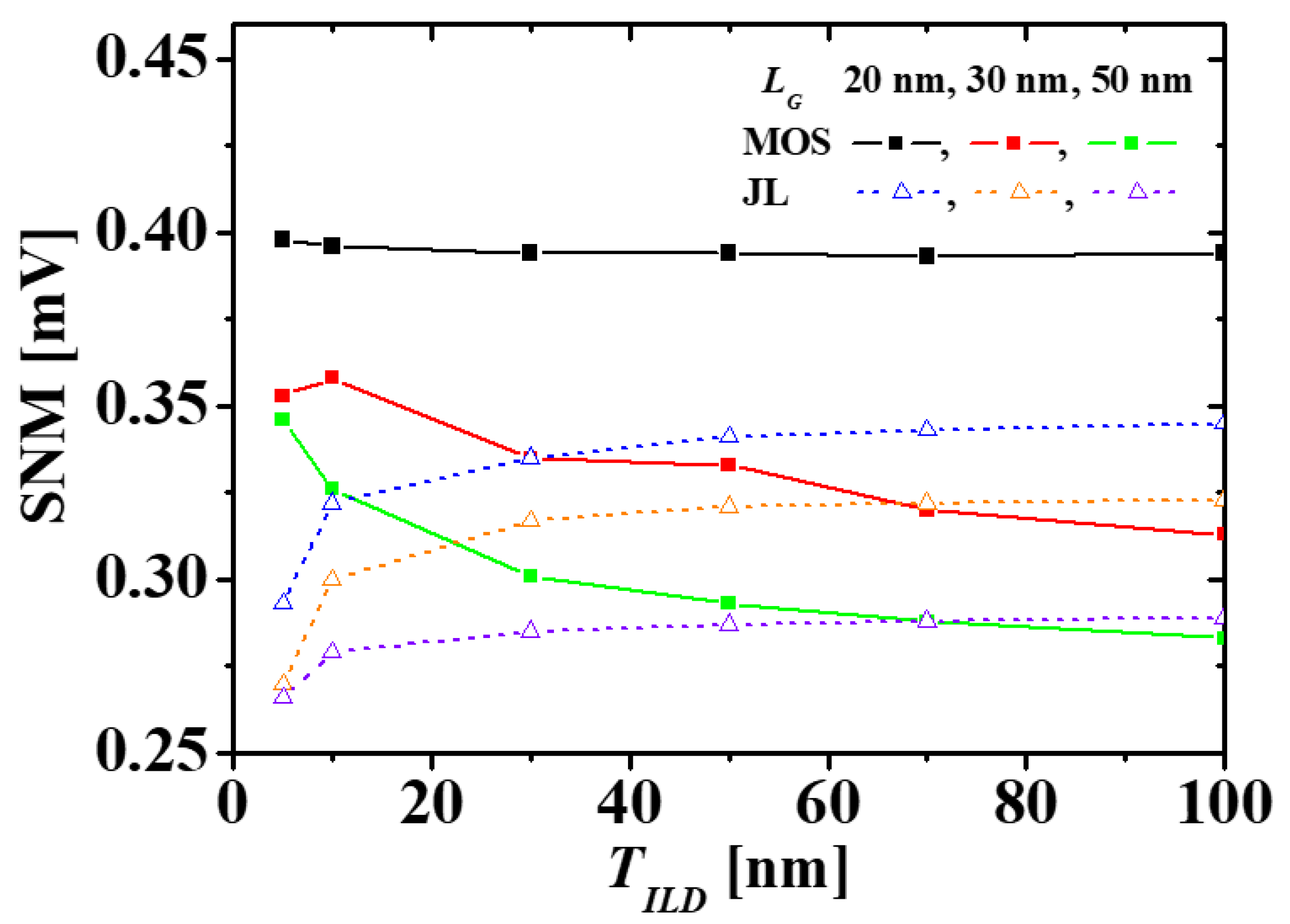

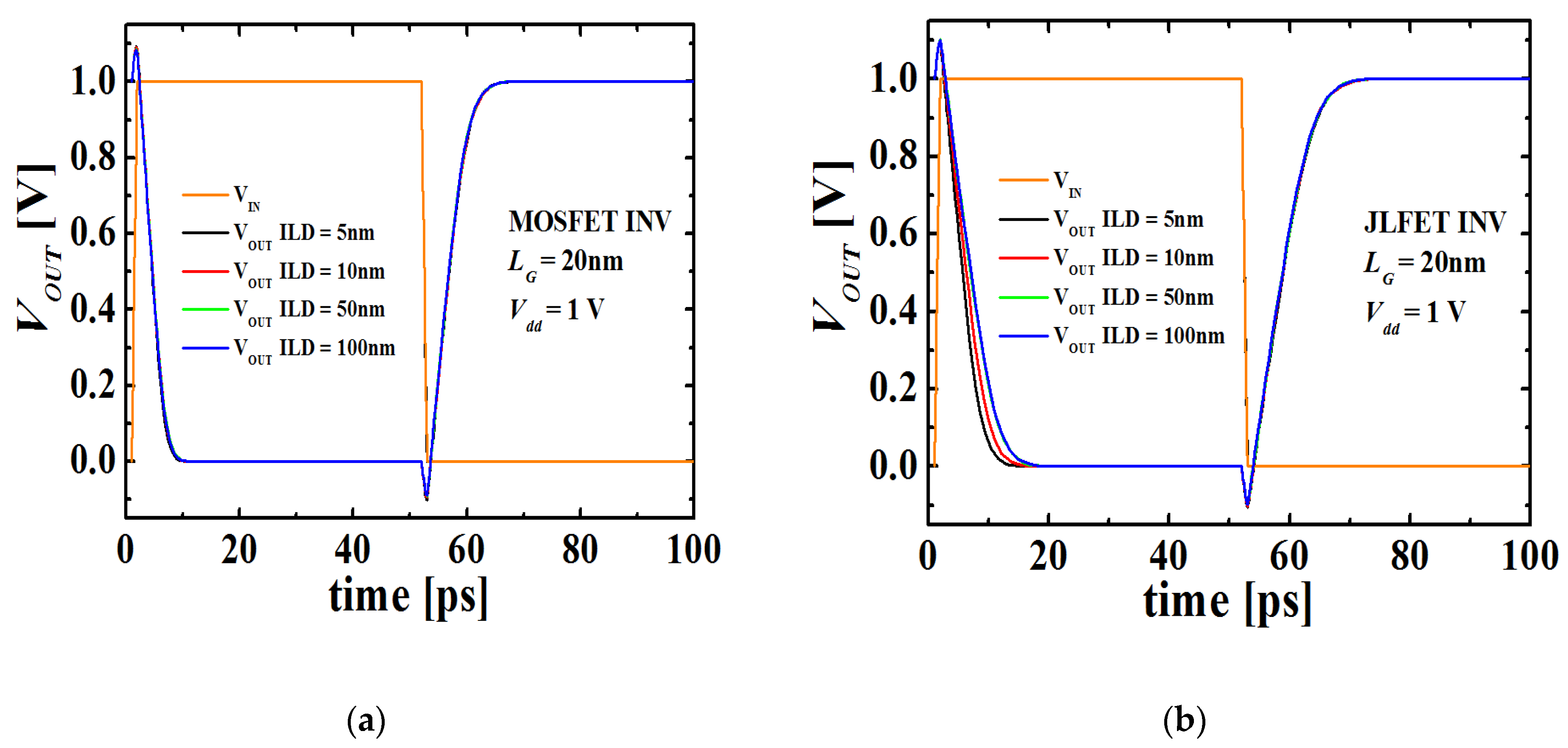

3. DC/AC Characteristics

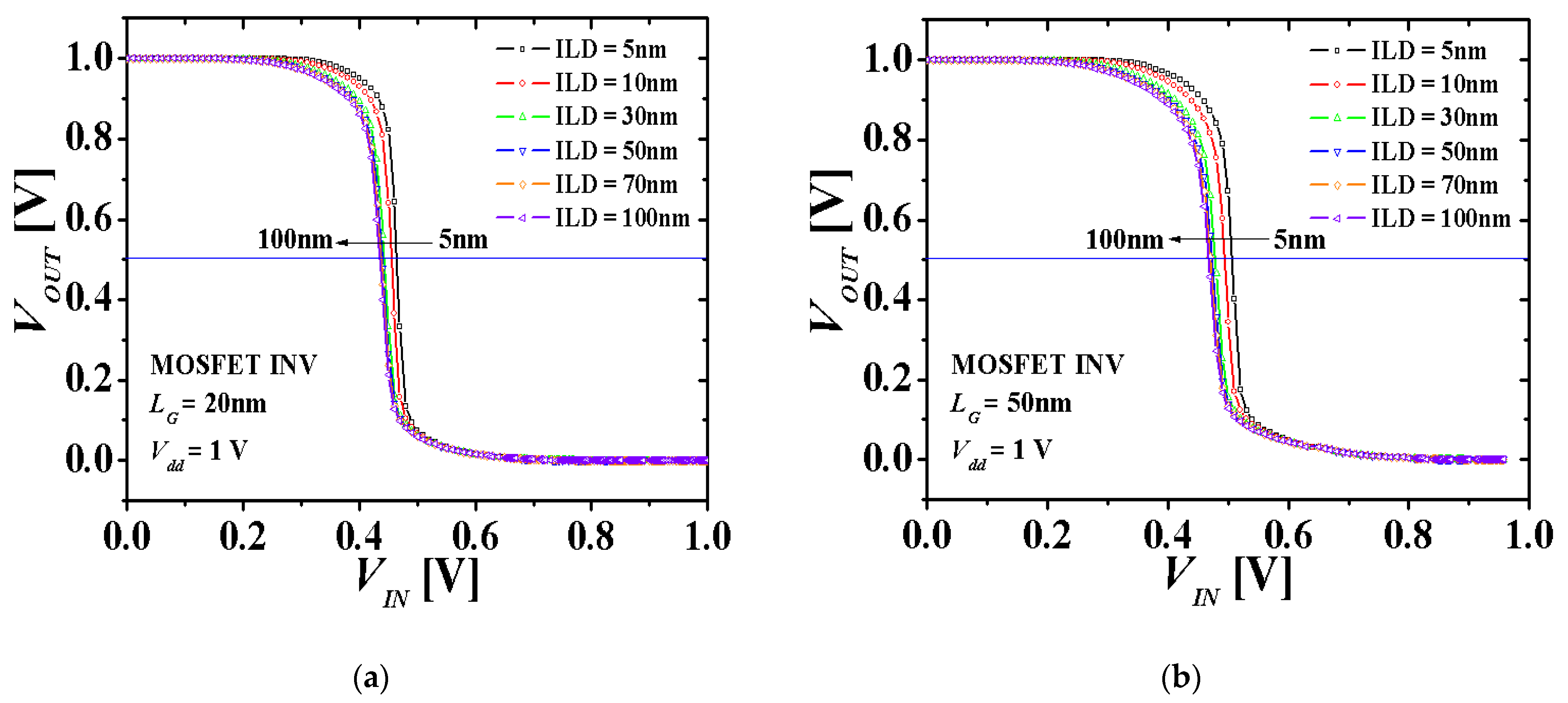

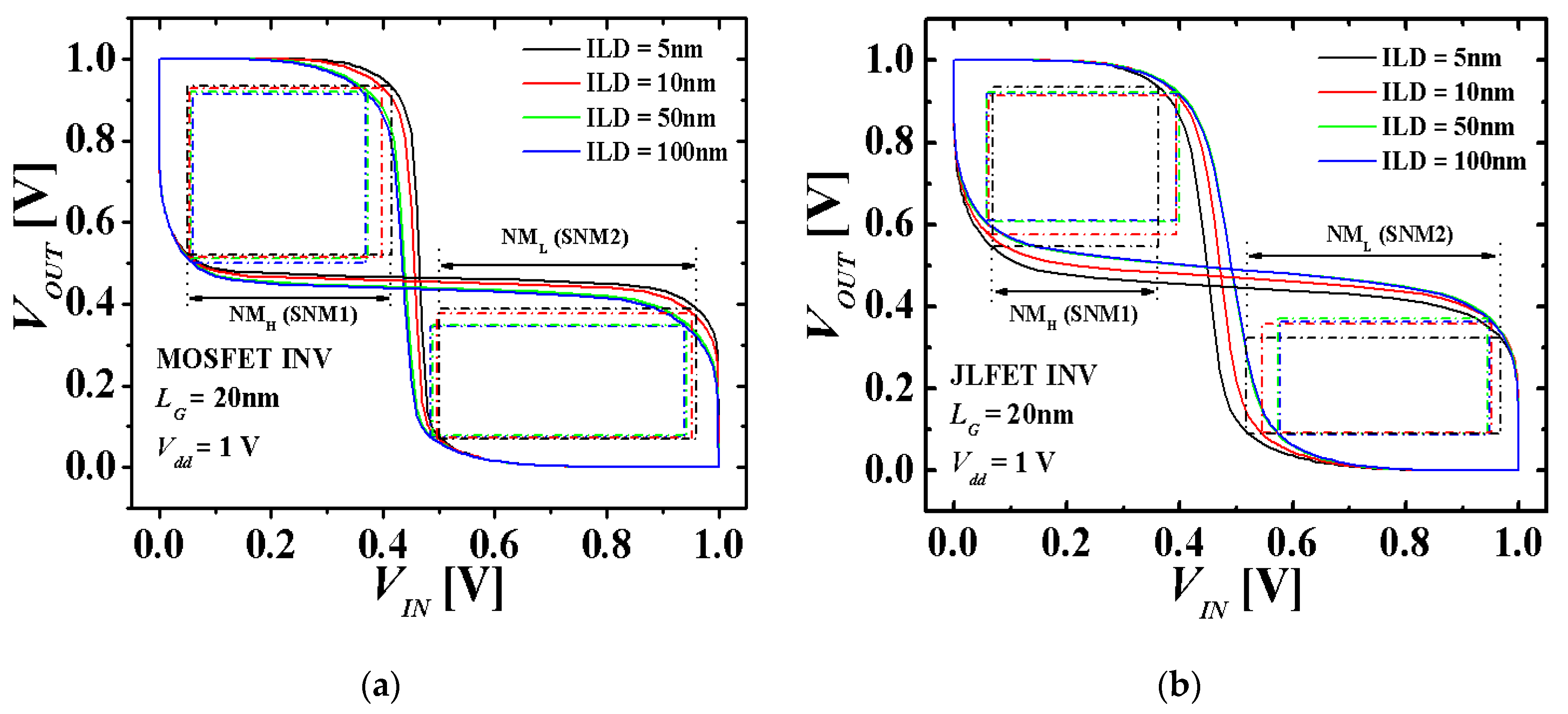

4. Inverter Characteristics

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Thompson, S.; Parthasarathy, S. Moore’s law: The future of Si microelectronics. Mater. Today 2006, 9, 20–25. [Google Scholar] [CrossRef]

- Iwai, H. Future of nano CMOS technology. Solid State Electron. 2018, 112, 56–67. [Google Scholar] [CrossRef]

- Schuegraf, K.; Abraham, M.C.; Naik, M.; Thakur, R. Semiconductor Logic Technology Innovation to Achieve Sub-10 nm Manufacturing. IEEE J. Electron Devices Soc. 2013, 1, 66–75. [Google Scholar] [CrossRef]

- Claverlier, L.; Deguet, C.; Di Cioccio, L.; Augendre, E.; Brugere, A.; Gueguen, P.; Le Tiec, Y.; Moriceau, H.; Rabarot, M.; Signamarcheix, T.; et al. Engineered substrates for future More Moore and More than Moore integrated devices. In Proceedings of the 2010 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 2.6.1–2.6.4. [Google Scholar] [CrossRef]

- Batude, P.; Ernst, T.; Arcamone, J.; Arndt, G.; Coudrain, P.; Gaillardon, P.-E. 3-D Sequential Integration: A key enabling technology for heterogeneous co-integration of new function with CMOS. IEEE J. Emerg. Sel. Top. Circuits Syst. 2012, 2, 714–722. [Google Scholar] [CrossRef]

- Li, S.K. Bringing 3D ICs to aerospace: Needs for design tools and methodologies. J. Lnf. Commun. Converg. Eng. 2017, 15, 117–122. [Google Scholar] [CrossRef]

- Nayak, D.K.; Banna, S.; Sarnal, S.K.; Lim, S.K. Power, performance, and cost comparisons of monolithic 3D ICs and TSV-based 3D ICs. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–2. [Google Scholar] [CrossRef]

- Coudrain, P.; Batude, P.; Gagnard, X.; Leyris, C.; Ricq, S.; Vinet, M.; Pouydebasque, A.; Moussy, N.; Cazaux, Y.; Giffard, B.; et al. Setting up 3D Sequential Integration for Back-Illuminated CMOS Image Sensors with Highly Miniaturized Pixels with low temperature Fully Depleted SOI transistors. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Batude, P.; Jaud, M.-A.; Thomas, O.; Clavellier, L.; Pouydebasque, A.; Vinet, M.; Deleonibus, S.; Amara, A. 3D CMOS Integration: Introduction of Dynamic coupling and Application to Compact and Robust 4T SRAM. In Proceedings of the 2008 IEEE International Conference on Integrated Circuit Design and Technology and Tutorial, Austin, TX, USA, 2–4 June 2008; pp. 281–284. [Google Scholar] [CrossRef]

- Colinge, J.-P. Junctionless transistors. In Proceedings of the 2012 IEEE International Meeting for Future of Electron Devices, Kansai, Osaka, Japan, 9–11 May 2012; pp. 1–2. [Google Scholar] [CrossRef]

- Migita, S.; Morita, Y.; Masahara, M.; Ota, H. Electrical performances of junctionless-FETs at the scaling limit (LCH = 3 nm). In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 8.6.1–8.6.4. [Google Scholar] [CrossRef]

- Sung, P.-J.; Chang, C.-Y.; Chen, L.-Y.; Kao, K.-H.; Su, C.-J.; Liao, T.-H.; Fang, C.-C.; Wang, C.-J.; Hong, T.-C.; Jao, C.-Y.; et al. Voltage Transfer Characteristic Matching by Different Nanosheet Layer Numbers of Vertically Stacked Junctionless CMOS Inverter for SoP/3D-ICs applications. In Proceedings of the 2010 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 21.4.1–21.4.4. [Google Scholar] [CrossRef]

- Ahn, T.J.; Perumal, R.; Lim, S.K.; Yu, Y.S. Parameter Extraction and Power/Performance Analysis of Monolithic 3-D Inverter (M3INV). IEEE Trans. Electron Devices 2019, 66, 1006–1011. [Google Scholar] [CrossRef]

- Yu, Y.S.; Panth, S.; Lim, S.K. Electrical Coupling of Monolithic 3-D Inverters. IEEE Trans. Electron Devices 2016, 63, 3346–3349. [Google Scholar] [CrossRef]

- Wang, J.-H.; Chen, Y.-N.; Su, P.; Chuang, C.-T. Exploration and evaluation of hybrid TFET-MOSFET monolithic 3D SRAMs considering interlayer coupling. In Proceedings of the 2016 International Conference on IC Design and Technology (ICICDT), Ho Chi Minh City, Vietnam, 27–29 June 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Colinge, J.P.; Lee, C.W.; Afzalian, A.; Akhavan, N.D.; Yan, R.; Ferain, I.; Razavi, P.; O’Neill, B.; Blake, A.; White, M.; et al. Nanowire transistors without junctions. Nat. Nanotechnol. 2010, 5, 225–229. [Google Scholar] [CrossRef] [PubMed]

- Silvaco Int. ATLAS ver. 5. 20. 2. R Manual; Silvaco Int.: Santa Clara, CA, USA, 2015. [Google Scholar]

- Park, C.-H.; Ko, M.-D.; Kim, K.-H.; Baek, R.-H.; Sohn, C.-W.; Baek, C.K.; Park, S.; Deen, M.J.; Jeong, Y.-H.; Lee, J.-S. Electrical characteristics of 20-nm junctionless Si nanowire transistors. Solid State Electron. 2012, 73, 7–10. [Google Scholar] [CrossRef]

- Hsieh, D.-R.; Lin, J.-Y.; Chao, T.-S. High-Performance Pi-Gate Poly-Si Junctionless and Inversion Mode FET. IEEE Trans. Electron Devices 2016, 63, 4179–4184. [Google Scholar] [CrossRef]

- Parihar, M.S.; Liu, F.; Navarro, C.; Barraud, S.; Bawedin, M.; Ionica, I.; Kranti, A.; Cristoloveanu, S. Back-gate effects and mobility characterization in junctionless transistor. Solid State Electron. 2016, 125, 154–160. [Google Scholar] [CrossRef]

- Eminente, S.; Cristoloveanu, S.; Clerc, R.; Ohata, A.; Ghibaudo, G. Ultra-thin fully-depleted SOI MOSFETs: Special charge properties and coupling effects. Solid State Electron. 2007, 51, 239–244. [Google Scholar] [CrossRef]

- Noel, J.-P.; Thomas, O.; Jaud, M.-A.; Weber, O.; Poiroux, T.; Fenouillet-Beranger, C.; Rivallin, P.; Scheiblin, P.; Andrieu, F.; Vinet, M.; et al. Multi-VT UTBB FDSOI Device Architectures for Low-Power CMOS Circuit. IEEE Trans. Electron Devices 2011, 58, 2473–2482. [Google Scholar] [CrossRef]

| Symbols | Description | Value/Unit |

|---|---|---|

| Cngng | Total gate capacitance of the top transistor | F |

| ΔVCngng | Difference of Vngss at maximum dCngng/dVngs of the top transistor at between Vpgs = 0 and 1 V | F |

| ΔVgm | Difference of Vngss at maximum gm of the top transistor at between Vpgs = 0 and 1 V | S |

| ΔVth | Difference of Vths of the top transistor at between Vpgs = 0 and 1 V | V |

| εox | Oxide dielectric constant | 3.9 |

| εsi | Silicon dielectric constant | 11.8 |

| εILD | ILD dielectric constant | 3.9 |

| gm | Transconductance (gm = dInds/dVngs or dIpds/dVpgs) | S |

| Inds/Ipds | Drain-source currents of top/bottom transistors | A |

| Lc | Contact length | 50 nm |

| LG | Gate length | 20/30/50 nm |

| LLDD | Lightly-doped drain length | 10 nm |

| TBOX | Buried-oxide thickness | 30 nm |

| Tc | Contact thickness | 6 nm |

| Tg | Gate thickness | 30 nm |

| TILD | ILD thickness | variable |

| Tox | Gate-oxide thickness | 0.9/1/1.1 nm |

| Tsi | Silicon-channel thickness | 6 nm |

| Tsub | Silicon substrate thickness | 50 nm |

| Tsw | Sidewall thickness | 31 nm |

| VIN | Input voltage of M3INV | V |

| Vm | Switching threshold voltage of the M3INV | V |

| Vngs/Vpgs | Gate-source voltages of top/bottom transistors | V |

| Vnds/Vpds | Drain-source voltages of top/bottom transistors | V |

| VOUT | Output voltage of M3INV | V |

| Vsub | Substrate voltage | V |

| Vth | Threshold voltage * of the top transistor | V |

| LG | 20 nm | 30 nm | 50 nm | ||||

|---|---|---|---|---|---|---|---|

| TILD | MOS Delay [ps] | JL Delay [ps] | MOS Delay [ps] | JL Delay [ps] | MOS Delay [ps] | JL Delay [ps] | |

| 5 nm | 4.42 | 4.18 | 4.56 | 4.58 | 6.56 | 5.84 | |

| 10 nm | 4.39 | 4.82 | 4.52 | 5.21 | 6.5 | 6.42 | |

| 30 nm | 4.37 | 5.43 | 4.49 | 5.57 | 6.43 | 6.93 | |

| 50 nm | 4.36 | 5.52 | 4.48 | 5.7 | 6.42 | 7.01 | |

| 70 nm | 4.35 | 5.55 | 4.47 | 5.72 | 6.41 | 7.06 | |

| 100 nm | 4.34 | 5.57 | 4.46 | 5.74 | 6.4 | 7.1 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahn, T.J.; Yu, Y.S. Electrical Coupling of Monolithic 3D Inverters (M3INVs): MOSFET and Junctionless FET. Appl. Sci. 2021, 11, 277. https://doi.org/10.3390/app11010277

Ahn TJ, Yu YS. Electrical Coupling of Monolithic 3D Inverters (M3INVs): MOSFET and Junctionless FET. Applied Sciences. 2021; 11(1):277. https://doi.org/10.3390/app11010277

Chicago/Turabian StyleAhn, Tae Jun, and Yun Seop Yu. 2021. "Electrical Coupling of Monolithic 3D Inverters (M3INVs): MOSFET and Junctionless FET" Applied Sciences 11, no. 1: 277. https://doi.org/10.3390/app11010277