Current-Feedback Instrumentation Amplifier Using Dual-Chopper Fill-In Technique

Abstract

:1. Introduction

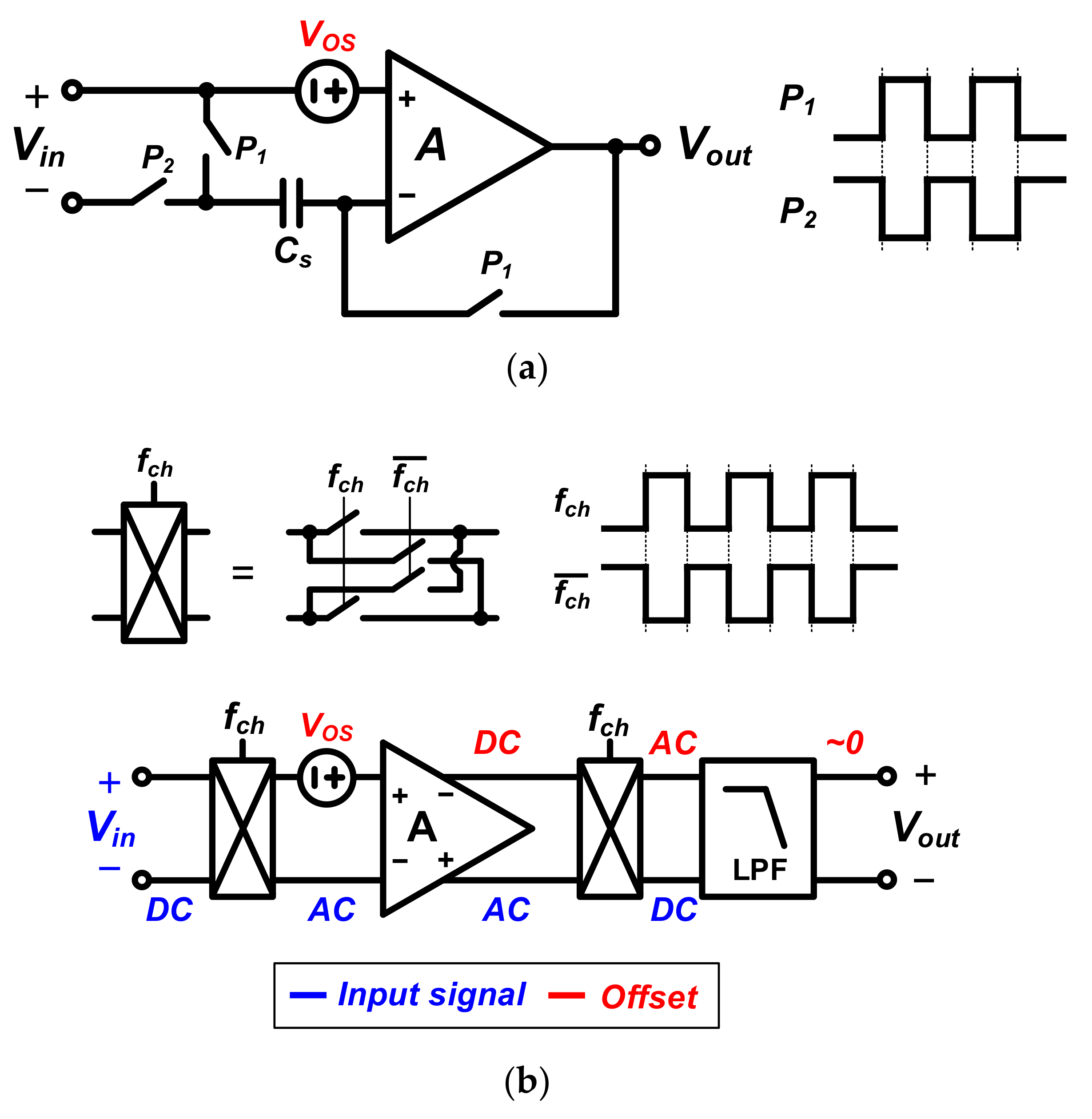

2. Proposed Chopper Fill-In Instrumentation Amplifier

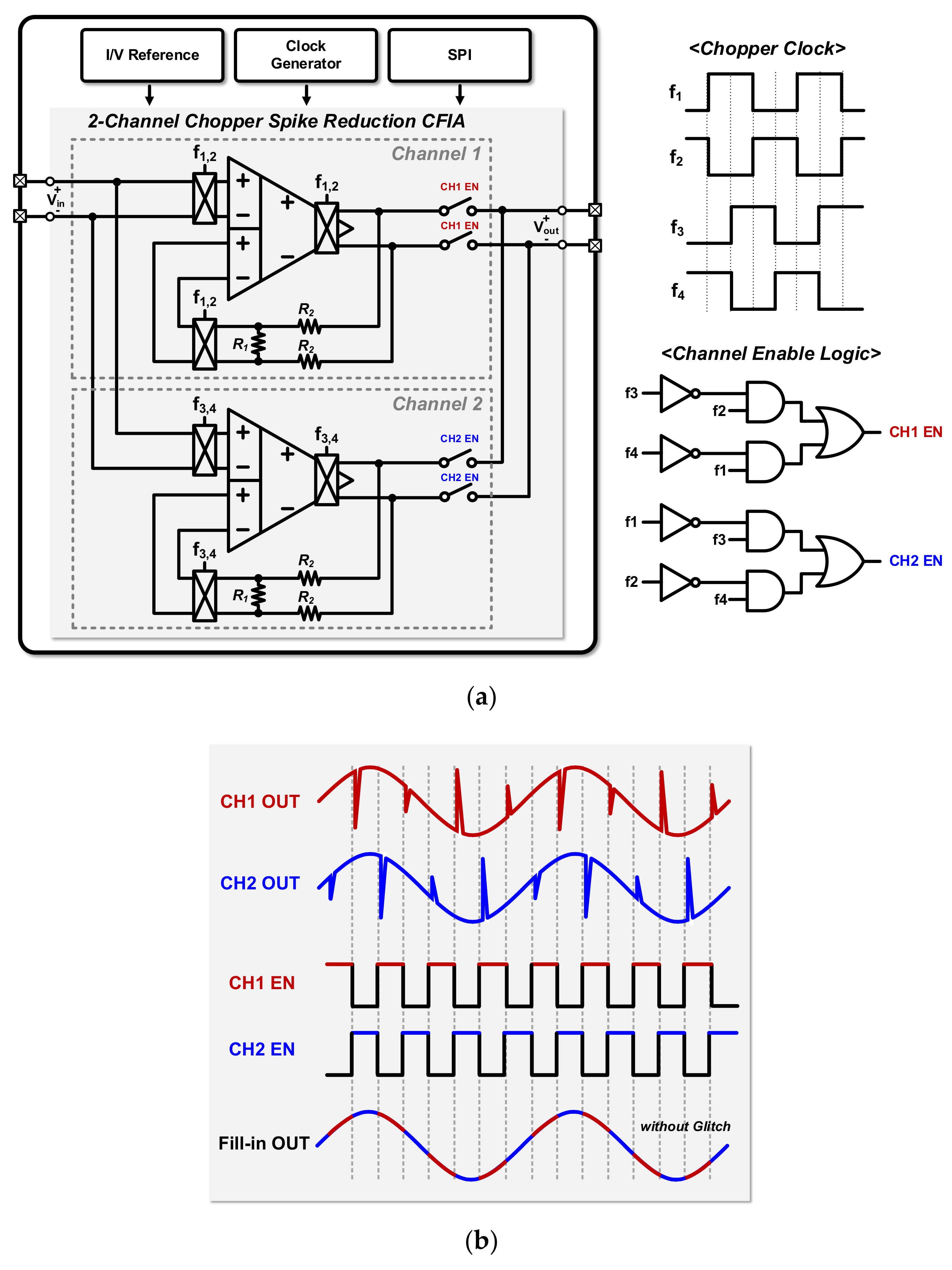

2.1. Top Architecture and Fill-In Technique of the Proposed CFIA

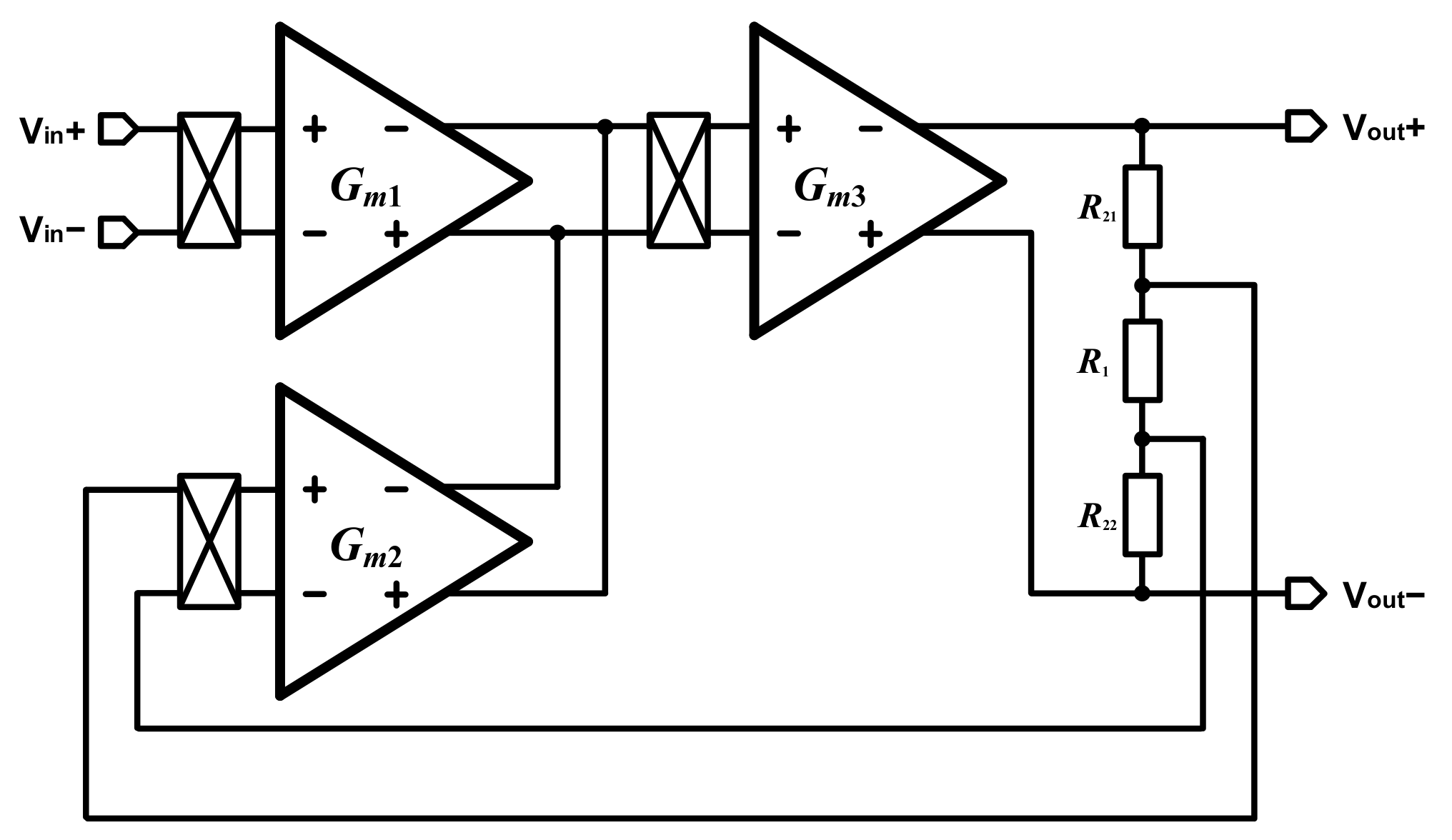

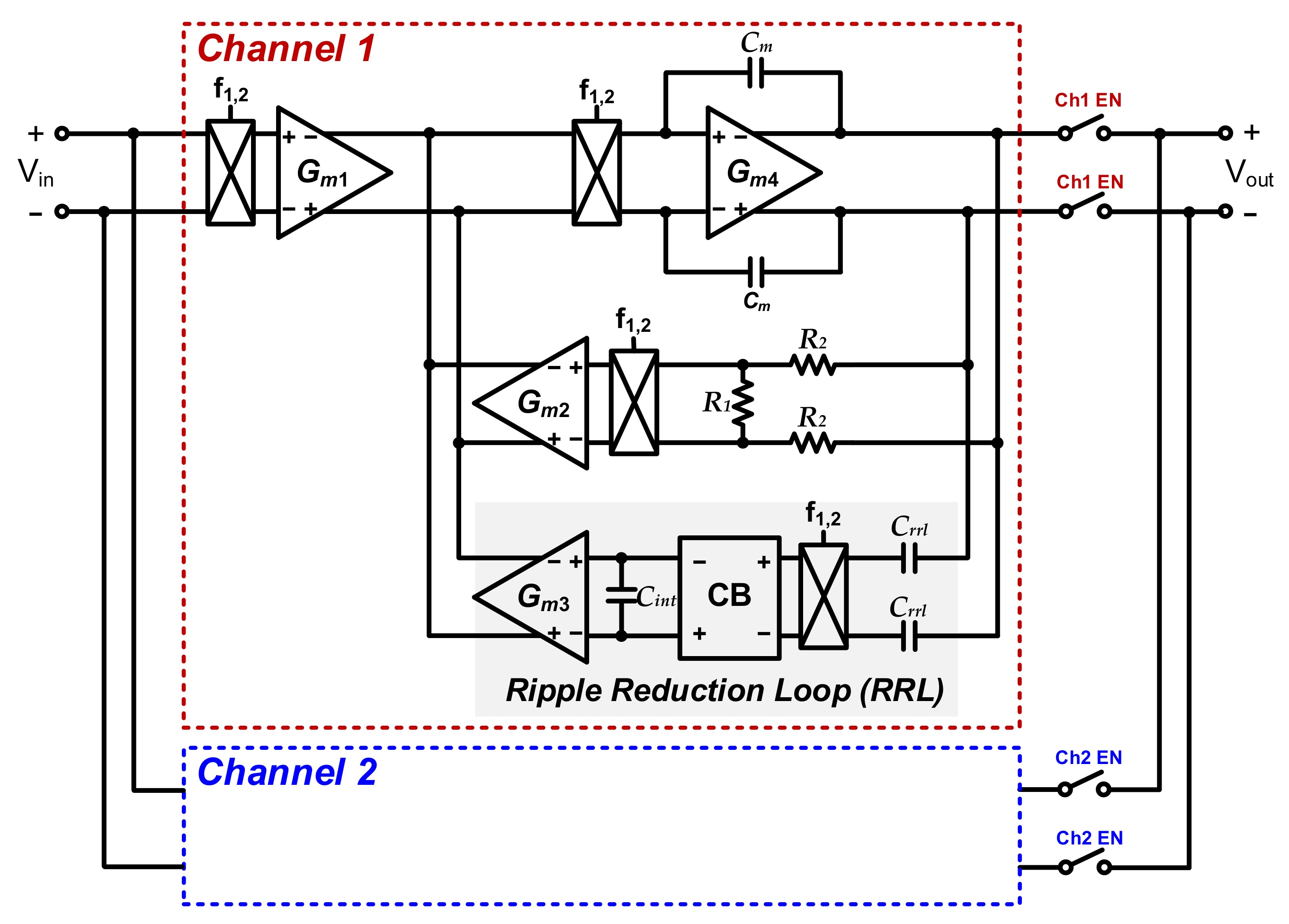

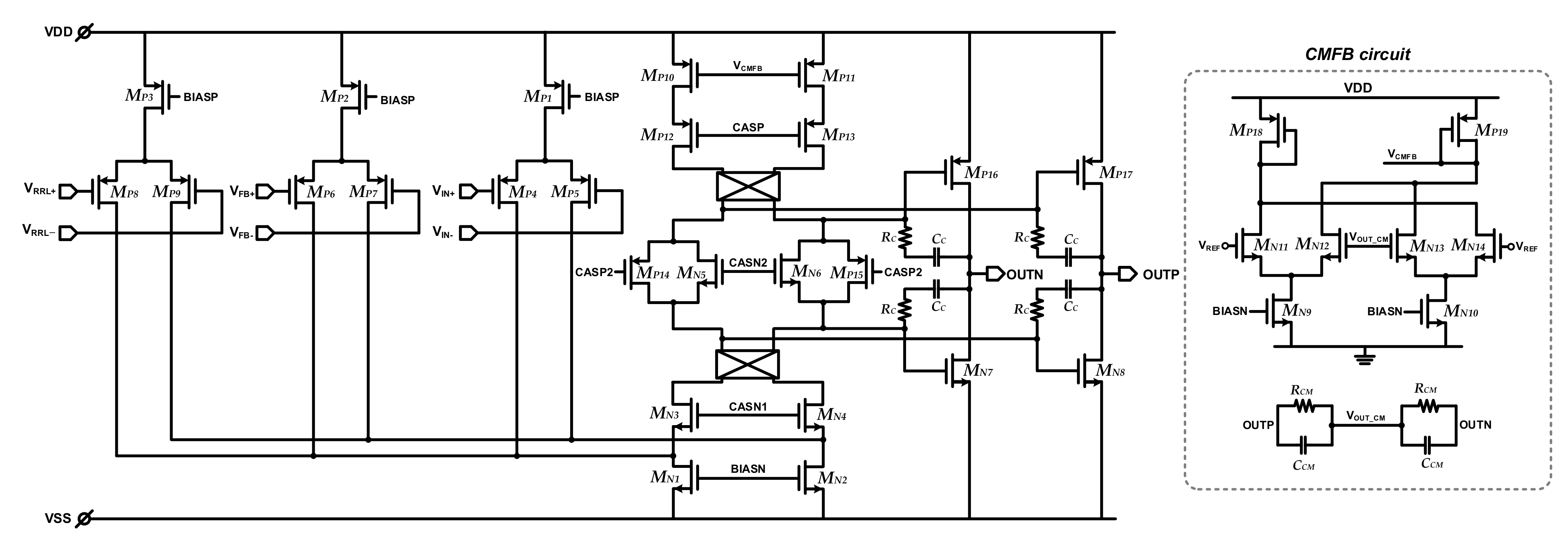

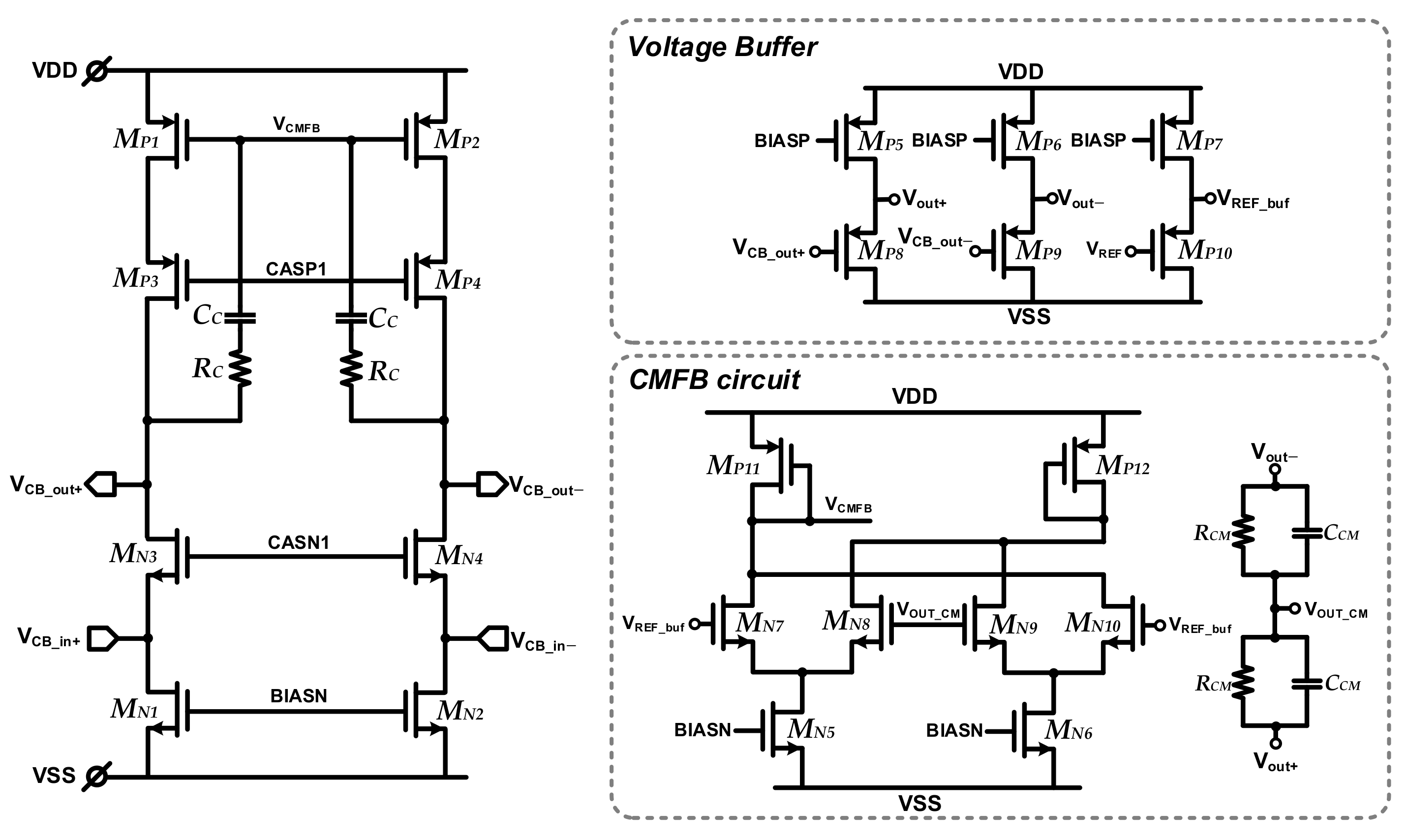

2.2. Configuration of the CFIA and RRL

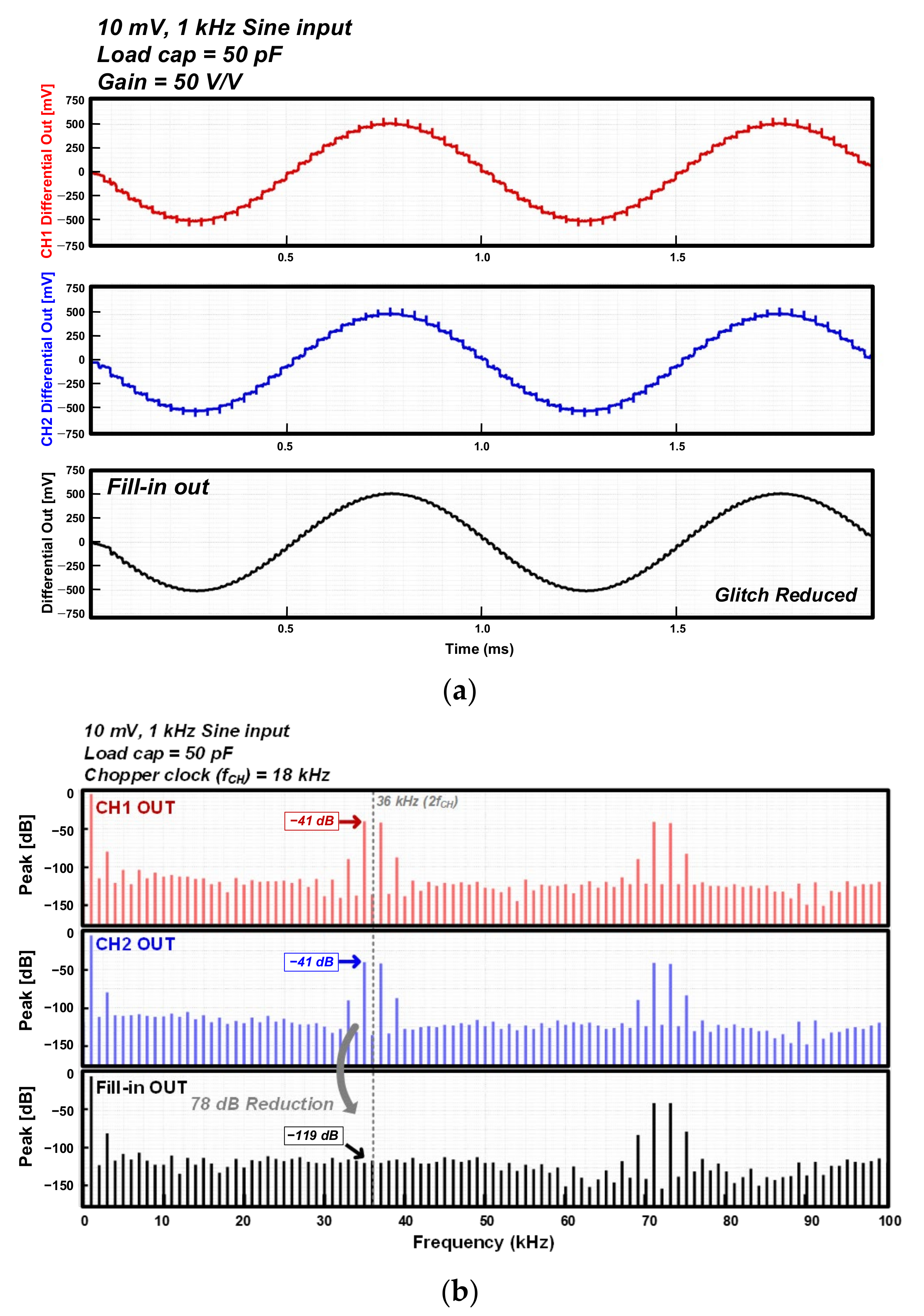

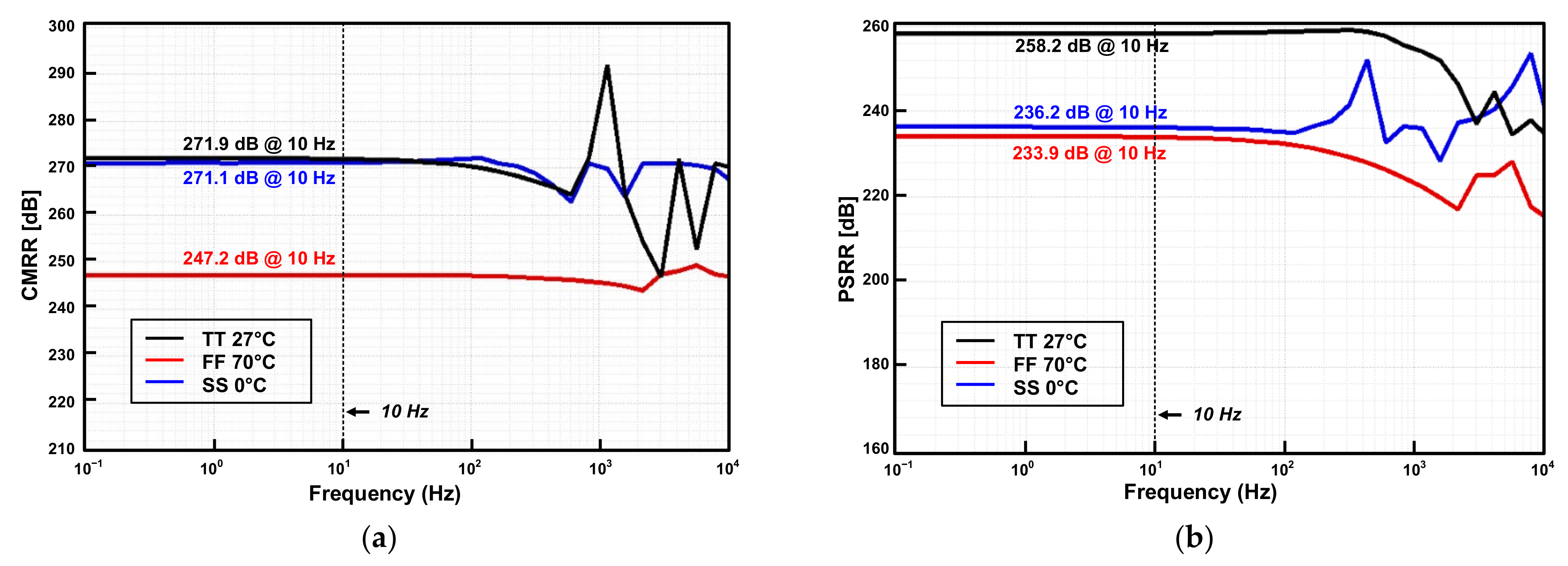

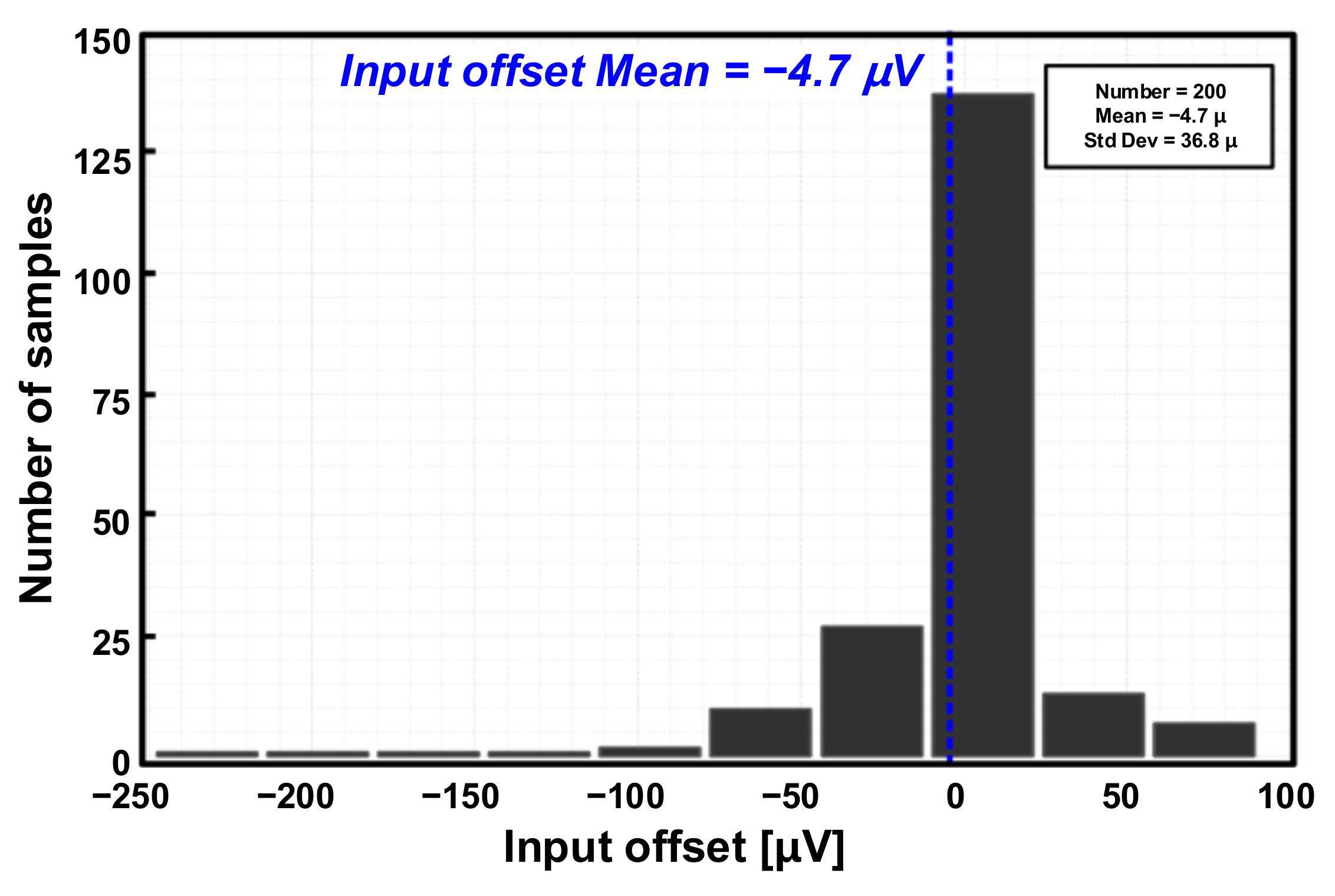

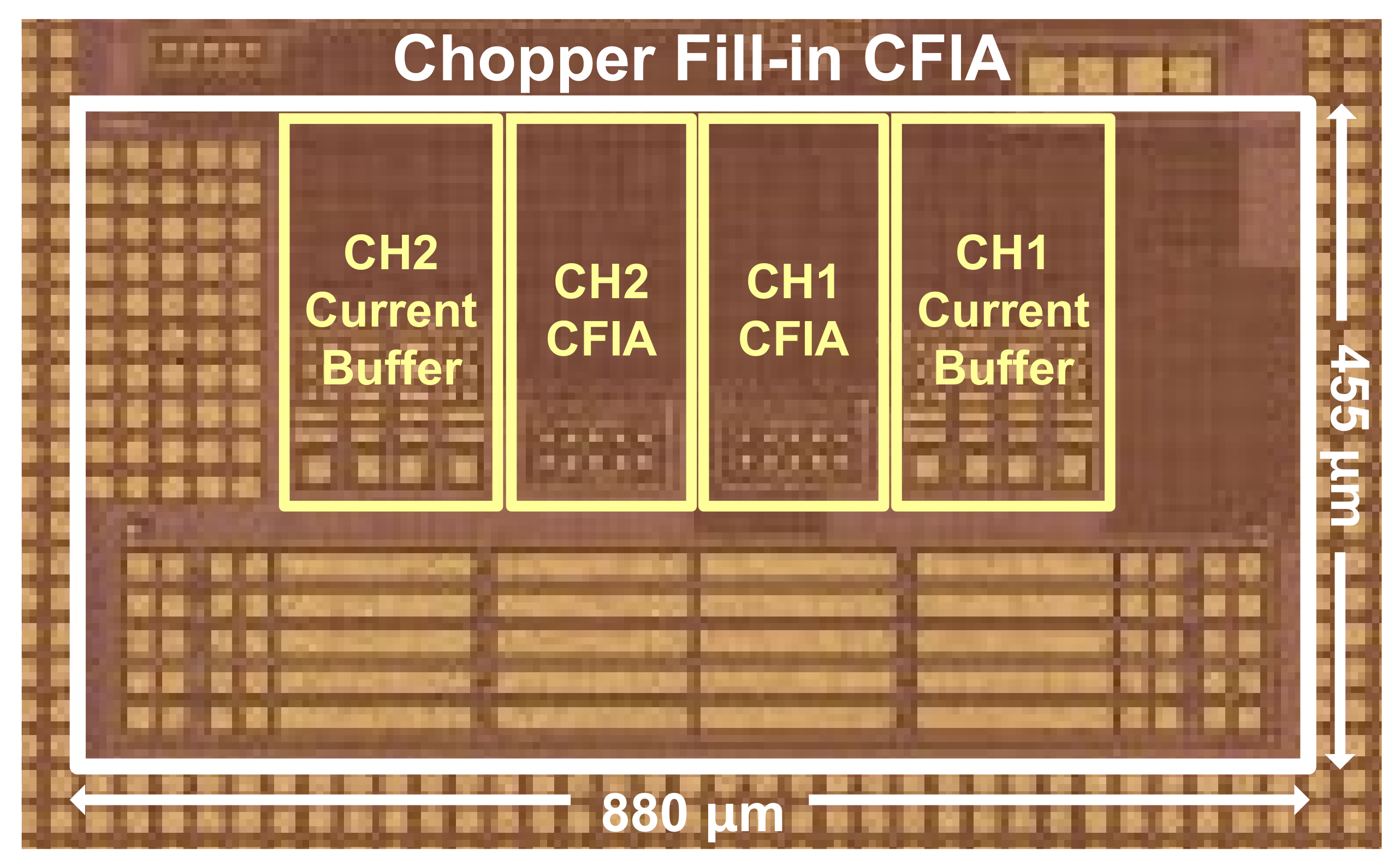

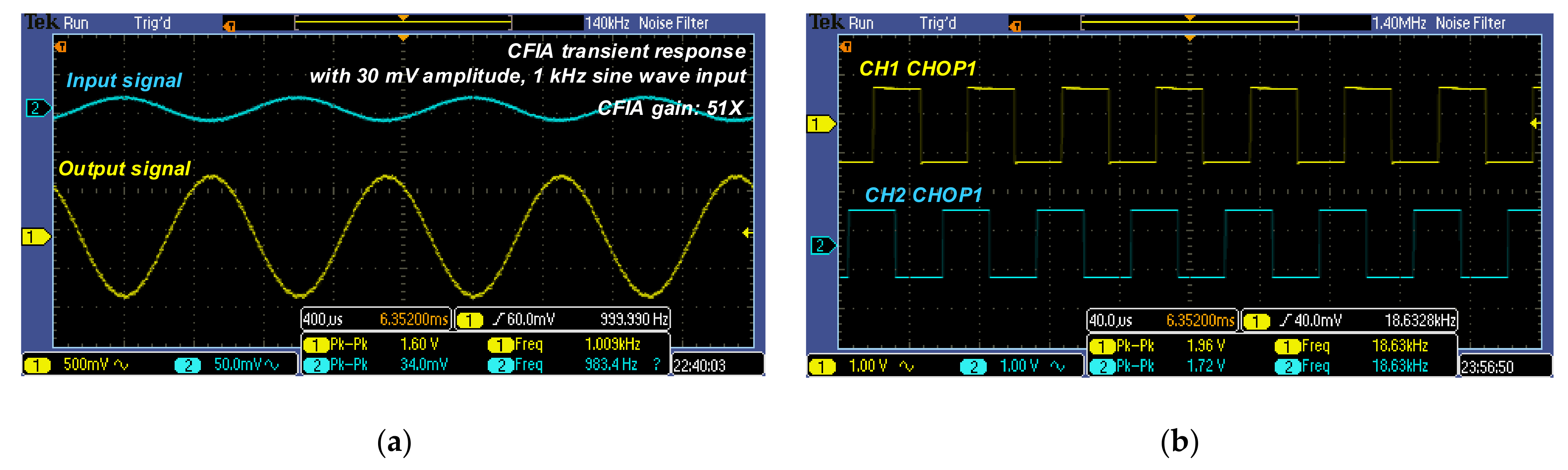

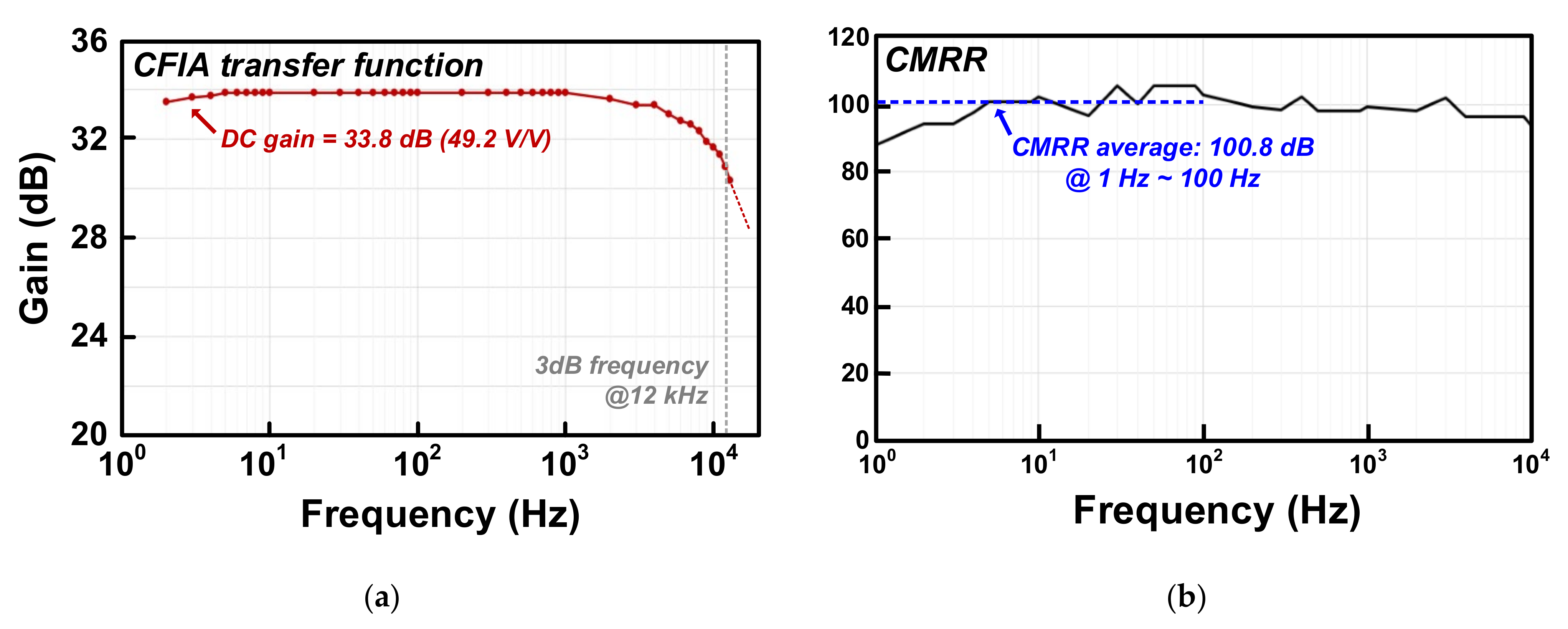

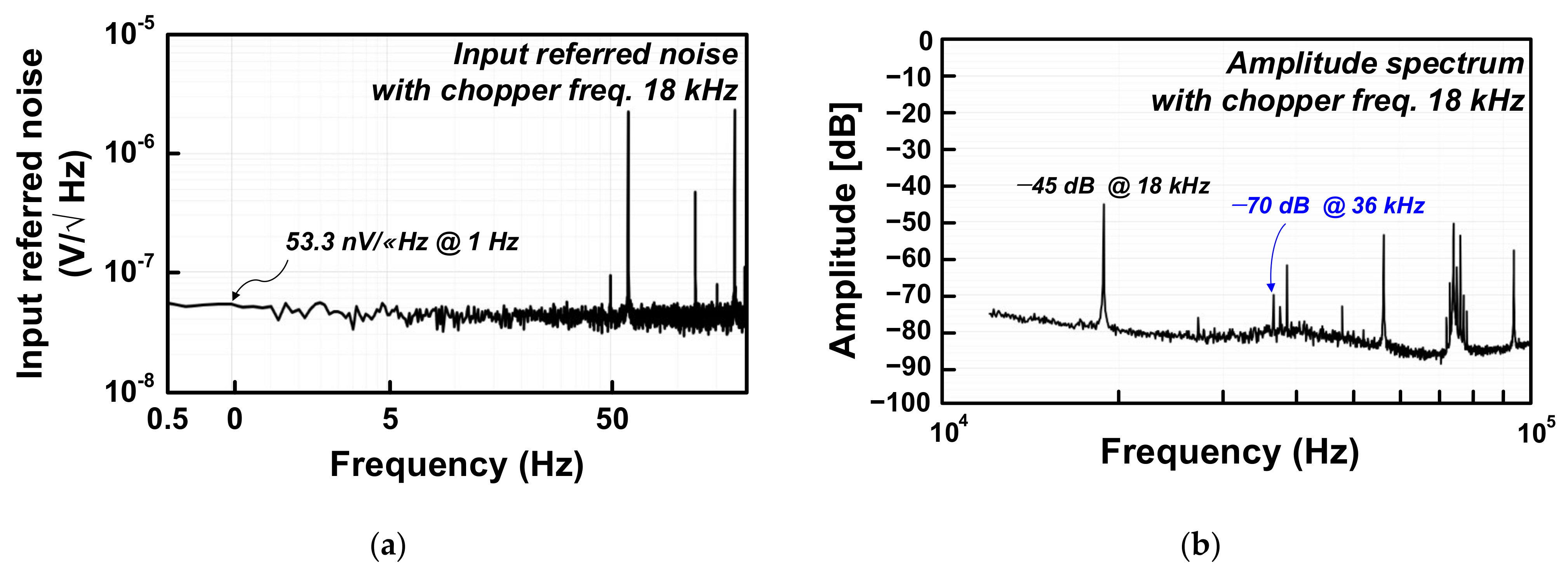

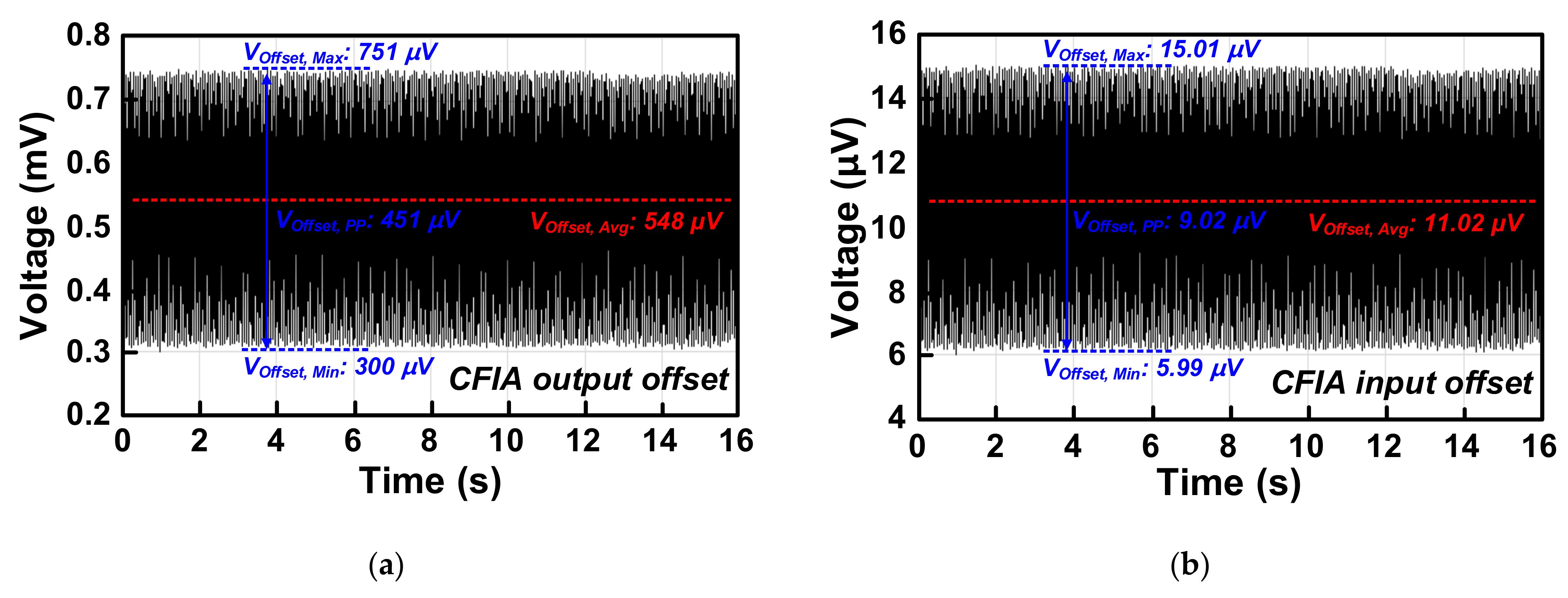

3. Measurement Results

4. Conclusions and Discussion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| CFIA | current-feedback instrumentation amplifier |

| IMD | intermodulation distortion |

| IA | instrumentation amplifier |

| AFE | analog front end |

| CMRR | common-mode rejection ratio |

| DOC | dynamic offset compensation |

| AZ | auto-zeroing |

| OTA | operational transconductance amplifier |

| LPF | low-frequency filter |

| RRL | ripple reduction loop |

| CMFB | common-mode feedback |

| PSRR | power supply rejection ratio |

| GBW | gain bandwidth |

| NEF | noise efficiency factor |

References

- Ong, G.T.; Chan, P.K. A Power-Aware Chopper-Stabilized Instrumentation Amplifier for Resistive Wheatstone Bridge Sensors. IEEE Trans. Intrum. Meas. 2014, 63, 2253–2263. [Google Scholar] [CrossRef]

- Ahmad, M.; Malik, S.; Dewan, S.; Bose, A.K.; Maddipatla, D.; Narakathu, B.B.; Atashbar, M.Z.; Baghini, M.S. An auto-calibrated resistive measurement system with low noise instrumentation ASIC. IEEE J. Solid-State Circuits 2020, 55, 3036–3050. [Google Scholar] [CrossRef]

- Sharma, B.P.; Mehra, R. Design of CMOS instrumentation amplifier with improved gain & CMRR for low power sensor applications. In Proceedings of the 2016 2nd International Conference on Next Generation Computing Technologies (NGCT), IEEE Conference, Dehradun, India, 14–16 October 2016. [Google Scholar]

- Pertijs, M.A.P.; Kindt, W.J. A 140 dB-CMRR Current-Feedback Instrumentation Amplifier Employing Ping-Pong Auto-Zeroing and Chopping. IEEE J. Solid-State Circuits 2010, 45, 2044–2056. [Google Scholar] [CrossRef]

- Archanaa, M.; Balamurugan, K. Analysis of thermal noise and noise reduction in CMOS device. In Proceedings of the 2014 International Conference on Green Computing Communication and Electrical Engineering (ICGCCEE), IEEE Conference, Coimbatore, India, 6–8 March 2014. [Google Scholar]

- Witte, J.F.; Huijising, J.H.; Makinwa, K.A.A. A Chopper and Auto-Zero Offset-Stabilized CMOS Instrumentation Amplifier. In Proceedings of the 2009 Proceedings of the 2009 Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2009. [Google Scholar]

- Rooijers, T.; Karmakar, S.; Kusuda, Y.; Huijising, J.H.; Makinwa, K.A.A. A Fill-In Technique for Robust IMD Suppression in Chopper Amplifiers. IEEE J. Solid-State Circuits 2021, 56, 3583–3592. [Google Scholar] [CrossRef]

- Vejdani, P.; Nabki, F. Dual-Path and Dual-Chopper Amplifier Signal Conditioning Circuit with Improved SNR and Ultra-Low Power Consumption for MEMS. IEEE Trans Circuit Syst I Regul Pap IEEE T Circuits-I 2019, 66, 2253–2262. [Google Scholar] [CrossRef]

- Yoo, M.; Kwon, Y.; Kim, H.; Choi, G.; Nam, K.; Ko, H. Low-Noise Resistive Bridge Sensor Analog Front-End Using Chopper-Stabilized Multipath Current Feedback Instrumentation Amplifier and Automatic Offset Cancellation Loop. IEEE Access 2022, 10, 12385–12394. [Google Scholar] [CrossRef]

- Choi, G.; Heo, H.; You, D.; Kim, H.; Nam, K.; Yoo, M.; Lee, S.; Ko, H. A Low-Power, Low-Noise, Resistive-Bridge Microsensor Readout Circuit with Chopper-Stabilized Recycling Folded Cascode Instrumentation Amplifier. Appl. Sci. 2021, 11, 7982. [Google Scholar] [CrossRef]

- Kwon, Y.; Kim, H.; Kim, J.; Han, K.; You, D.; Heo, H.; Cho, D.; Ko, H. Fully Differential Chopper-Stabilized Multipath Current-Feedback Instrumentation Amplifier with R-2R DAC Offset Adjustment for Resistive Bridge Sensors. Appl. Sci. 2020, 10, 63. [Google Scholar] [CrossRef] [Green Version]

| Transistor | Size (W/L) (µm) | Transistor | Size (W/L) (µm) |

|---|---|---|---|

| MP1, MP2 | 18/3.2 | MN1, MN2 | 13.6/10 |

| MP3 | 6/3.2 | MN3, MN4 | 5.6/4 |

| MP4–MP9 | 80/0.5 | MN5, MN6 | 2/14 |

| MP10, MP11 | 26/3 | MN7, MN8 | 2/1 |

| MP12, MP13 | 10/1 | MN9, MN10 | 2/5 |

| MP14, MP15 | 4/9 | NM11–MN14 | 12/2 |

| MP16, MP17 | 8/1 | ||

| MP18, MP19 | 20/2 |

| Component | Value |

|---|---|

| CC | 412 fF |

| RC | 134 kΩ |

| RCM | 2.3 MΩ |

| CCM | 206 fF |

| Transistor | Size (W/L) (µm) | Transistor | Size (W/L) (µm) |

|---|---|---|---|

| MP1, MP2 | 12/3 | MN1, MN2 | 2.4/14 |

| MP3, MP4 | 12/3 | MN3, MN4 | 3/4 |

| MP5–MP7 | 1/4 | MN5, MN6 | 1/8 |

| MP8–MP10 | 2/2 | MN7–MN10 | 4/2 |

| MP11, MP12 | 7/3 |

| Component | Value |

|---|---|

| CC | 1.2 pF |

| RC | 11.2 kΩ |

| RCM | 224 kΩ |

| CCM | 1.6 pF |

| Transistor | Noise Source | Total Noise (%) |

|---|---|---|

| MN1, MN2 (Figure 7) | Thermal | 23.74 |

| MP10, MP11 (Figure 7) | Thermal | 9.26 |

| MN6, MN7, MN8, MN9 (Figure 7) | Thermal | 6.84 |

| R1 (Figure 6) | Flicker | 3.8 |

| This Work | [9] | [10] | [11] | [4] | |

|---|---|---|---|---|---|

| Architecture | CFIA | CFIA | CFIA | CFIA | CFIA |

| Dynamic technique | chopping + fill-in + RRL | Multipath +chopper stabilization +RRL | RFC + chopping | Multipath + chopper stabilization +RRL | Auto-zeroing + chopping + ping-pong |

| Technology (µm) | 0.18 | 0.18 | 0.18 | 0.18 | 0.5 |

| Supply voltage (V) | 1.8 | 3.3 | 1.8 | 1.8 | 3.0~5.0 |

| Current consumption (µA) | 29 | 123 | 2.23 | 169 | 1700 |

| Power consumption (mW) | 52.2 | 405.9 | 4.014 | 304.2 | 5100~8500 |

| Active area (mm2) | 1.28 | 1.28 | 0.536 | 1.4 | 2.5 |

| Gain bandwidth (Hz) | 420 k | 1.92 M | 580 k | 59.2 k | 800 k |

| Input-referred noise (nV/√Hz) | 53.3 @1 Hz 24.7 (integrated) | 10 | 86.6 | 18.3 | 27 |

| CMRR (dB) | 108.8 | >100 | 176.6 | 162 | 142 |

| PSRR (dB) | 105.3 | >90 | 119 | 112 | 138 |

| Offset (V) | 11 μ | 1 μ | - | - | 2.8 μ |

| NEF * | 4.4 | 4.3 | 4.94 | 14.2 | 13.5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, G.; Nam, K.; Yoo, M.; Kang, S.; Jin, B.; Kim, K.; Son, H.; Ko, H. Current-Feedback Instrumentation Amplifier Using Dual-Chopper Fill-In Technique. Appl. Sci. 2022, 12, 10471. https://doi.org/10.3390/app122010471

Choi G, Nam K, Yoo M, Kang S, Jin B, Kim K, Son H, Ko H. Current-Feedback Instrumentation Amplifier Using Dual-Chopper Fill-In Technique. Applied Sciences. 2022; 12(20):10471. https://doi.org/10.3390/app122010471

Chicago/Turabian StyleChoi, Gyuri, Kyeongsik Nam, Mookyoung Yoo, Sanggyun Kang, Byeongkwan Jin, Kyounghwan Kim, Hyeoktae Son, and Hyoungho Ko. 2022. "Current-Feedback Instrumentation Amplifier Using Dual-Chopper Fill-In Technique" Applied Sciences 12, no. 20: 10471. https://doi.org/10.3390/app122010471

APA StyleChoi, G., Nam, K., Yoo, M., Kang, S., Jin, B., Kim, K., Son, H., & Ko, H. (2022). Current-Feedback Instrumentation Amplifier Using Dual-Chopper Fill-In Technique. Applied Sciences, 12(20), 10471. https://doi.org/10.3390/app122010471