Systematic Analysis of Spacer and Gate Length Scaling on Memory Characteristics in 3D NAND Flash Memory

Abstract

1. Introduction

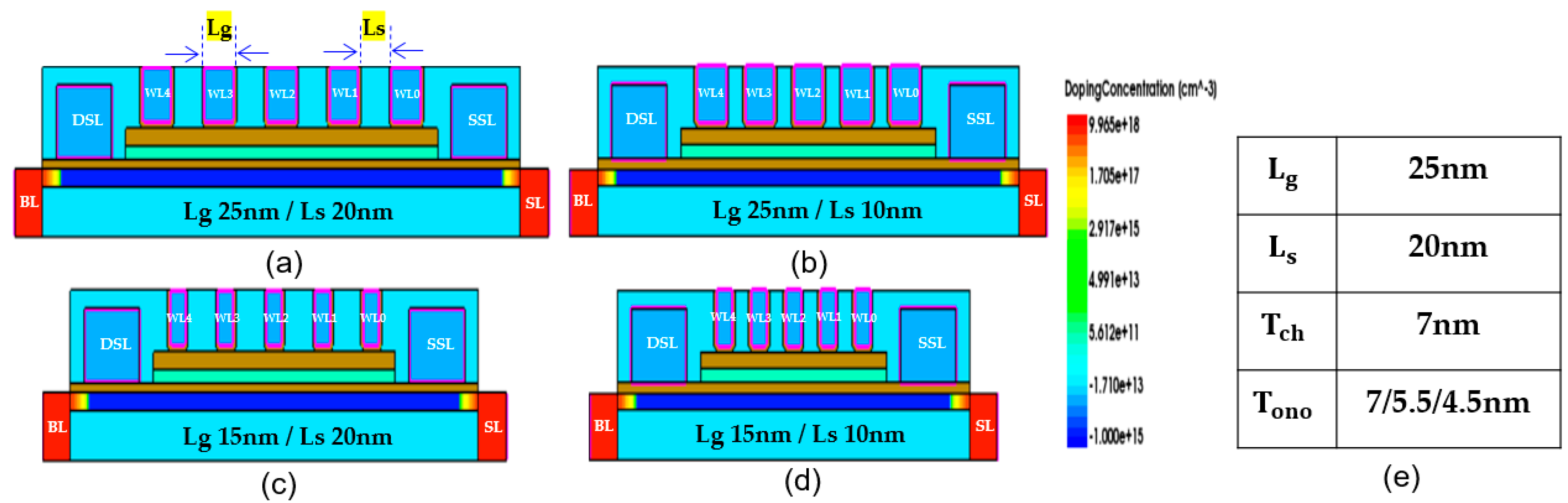

2. Simulation Set-Up

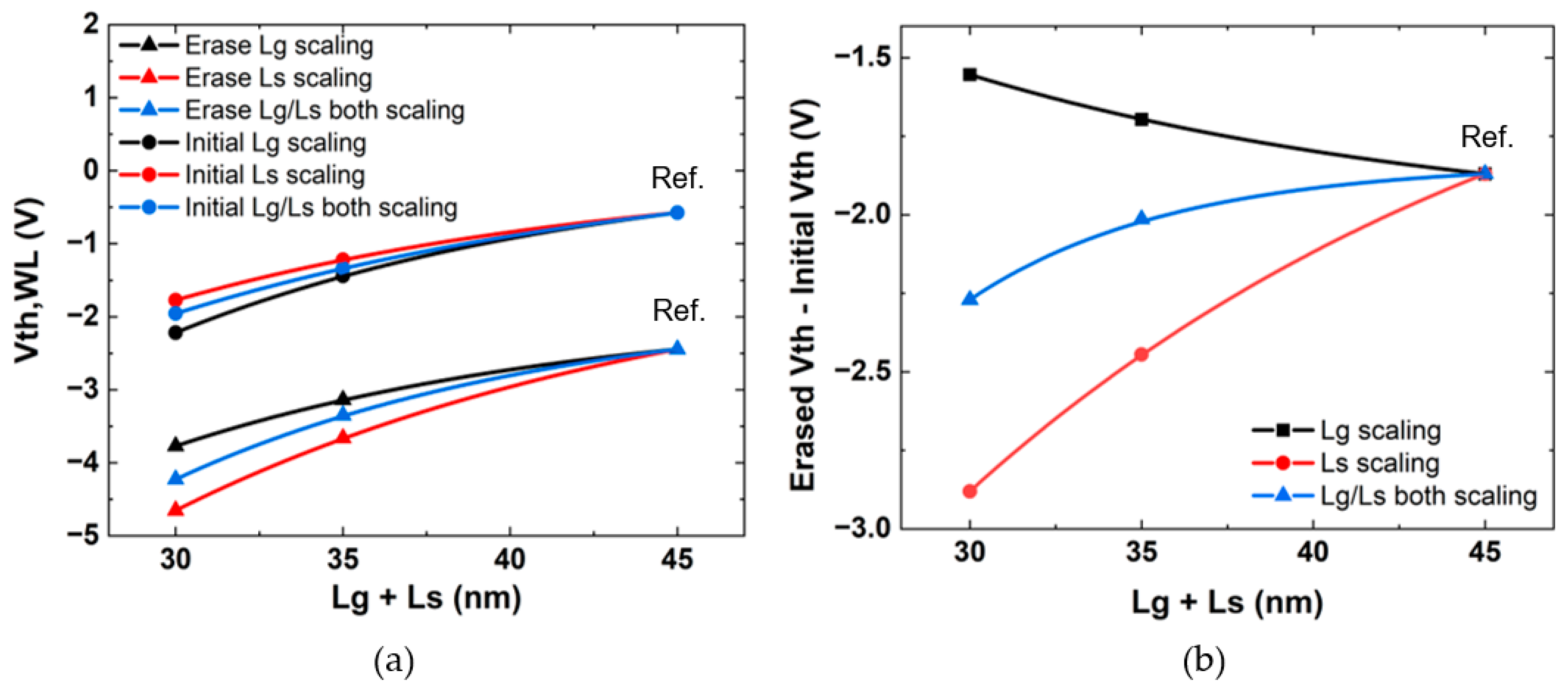

3. Analysis of Program and Erase Window

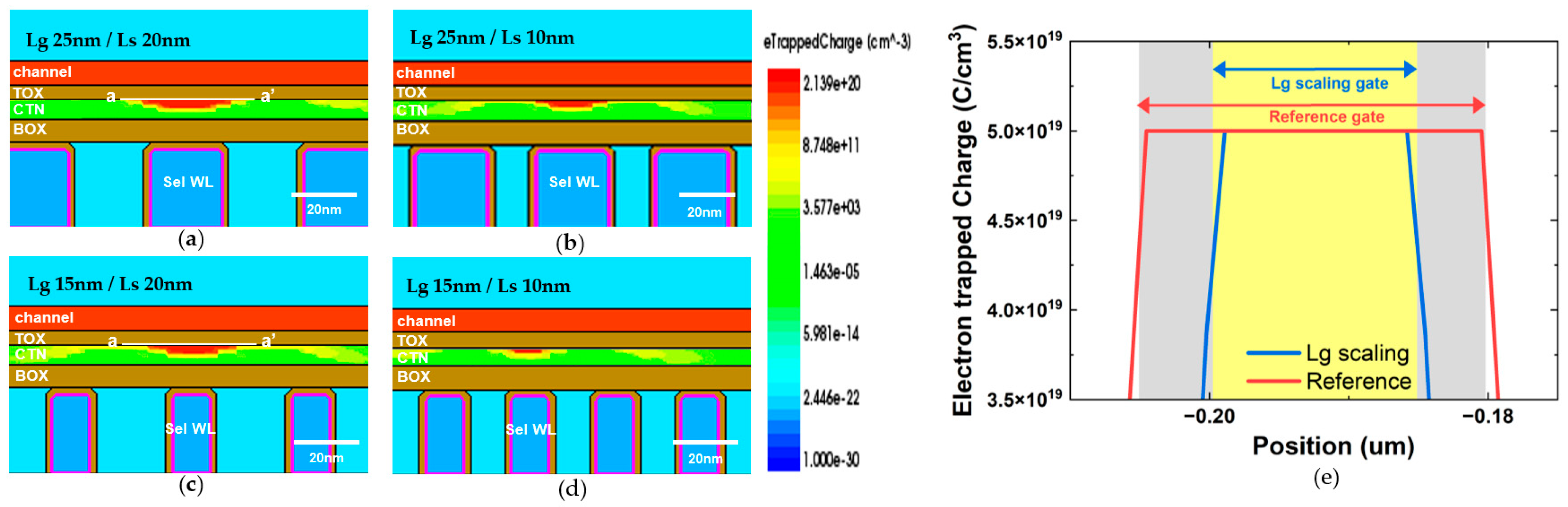

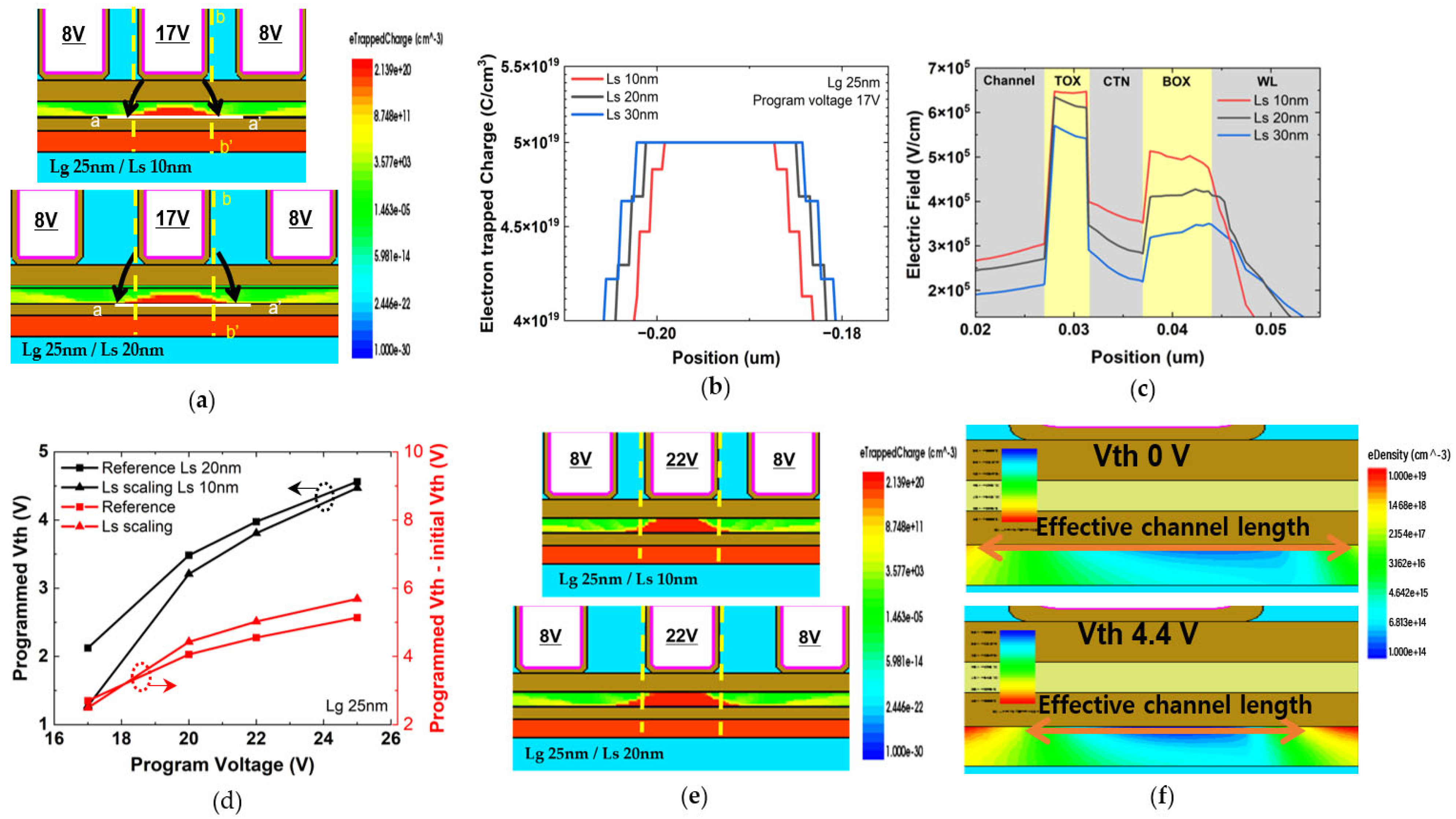

3.1. Program Window Effect

3.2. Erase Window Effect

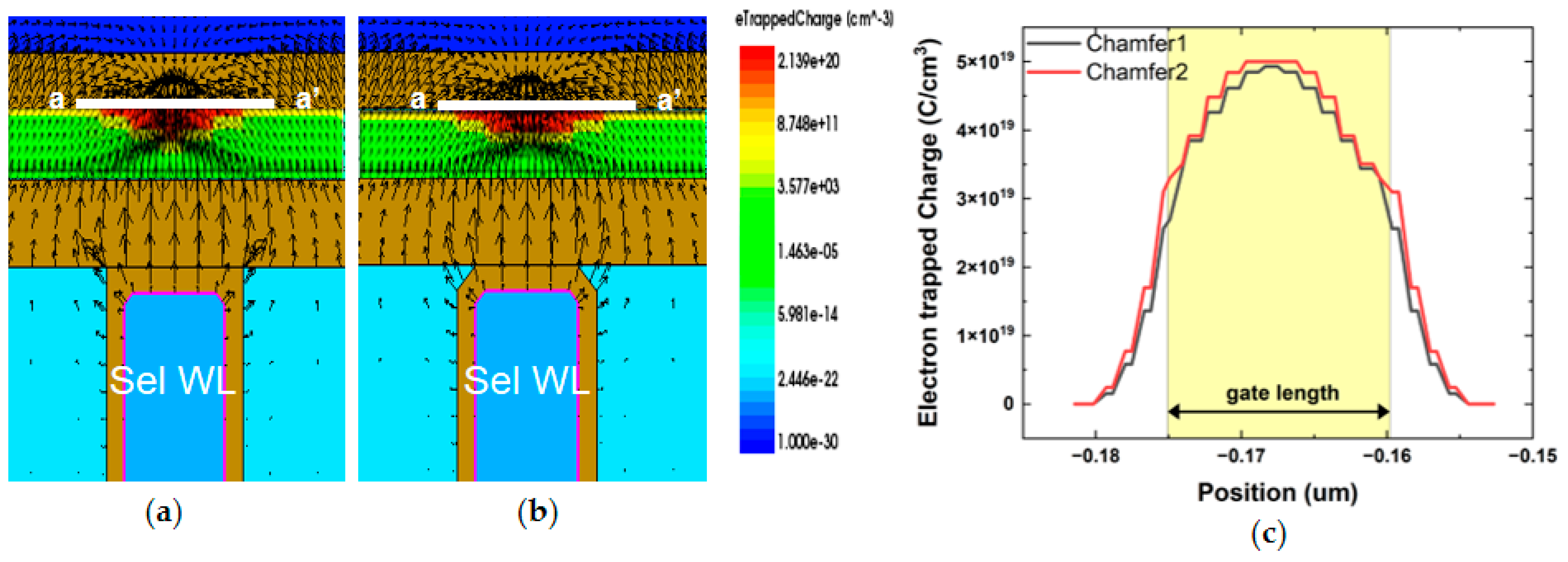

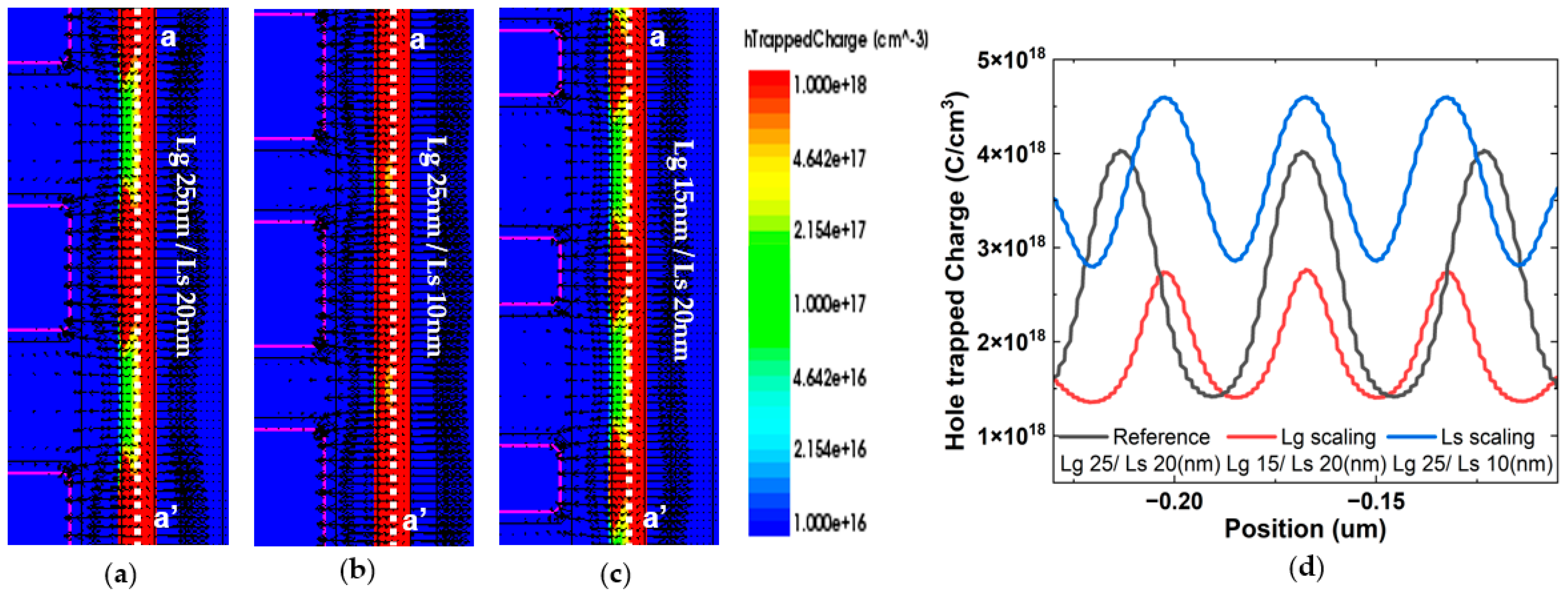

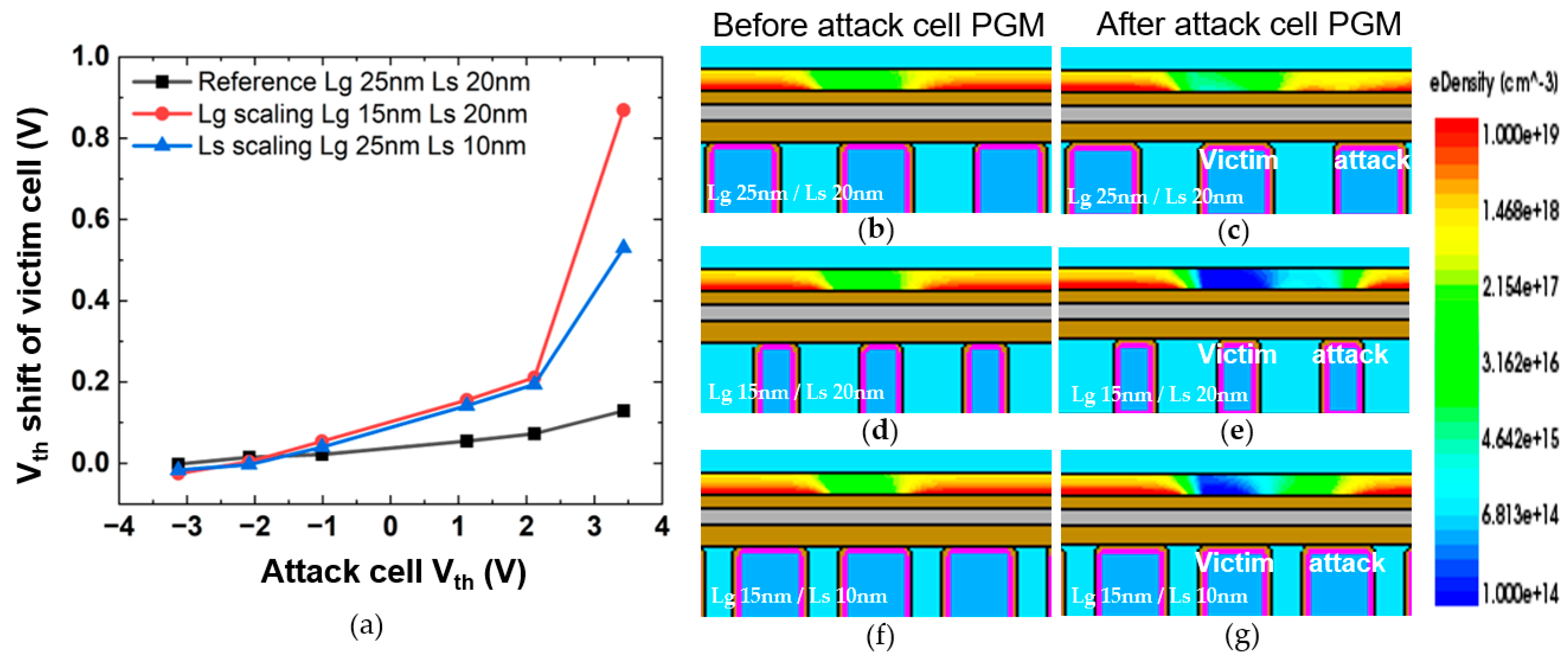

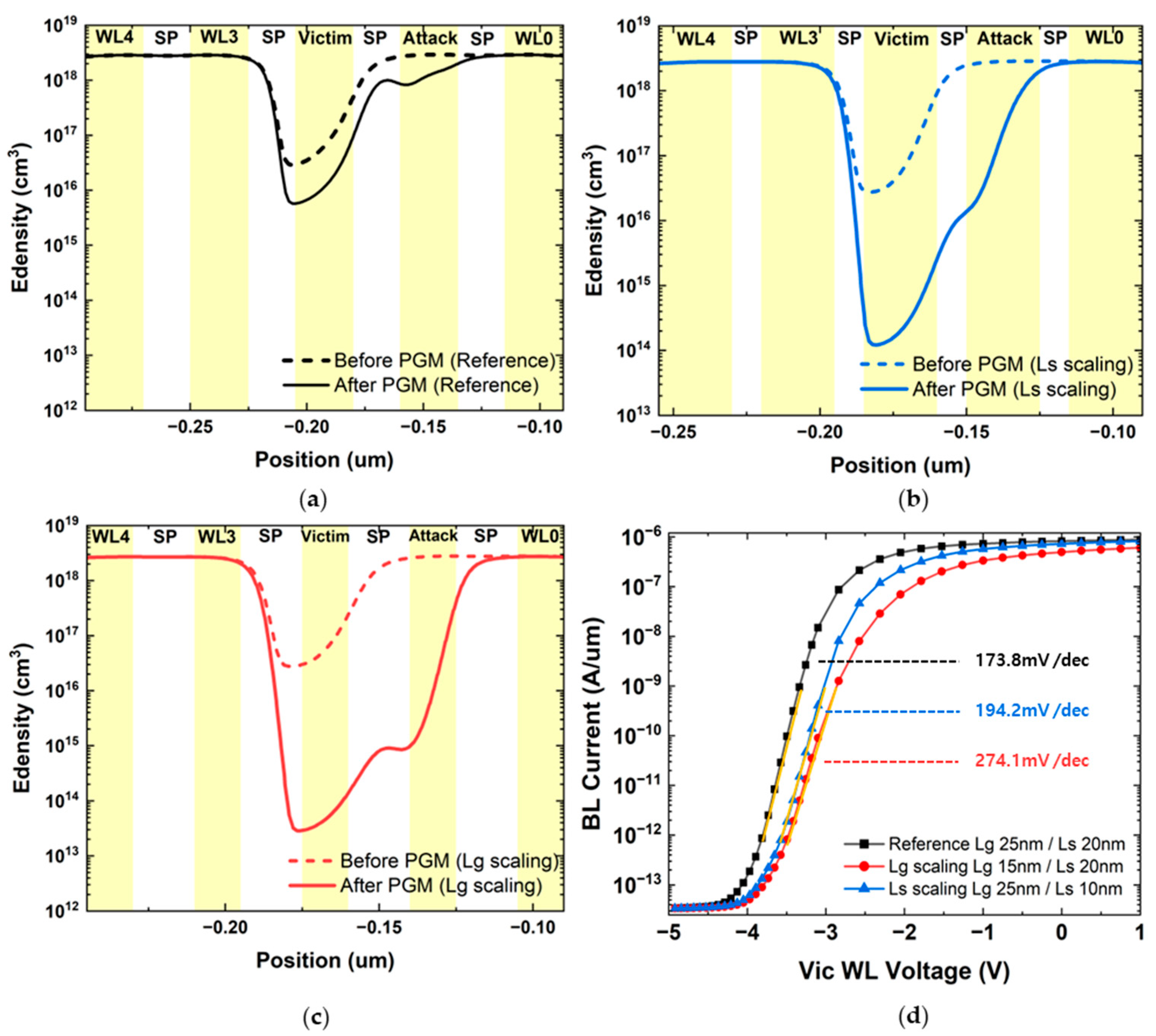

4. Investigation of Z-Interference

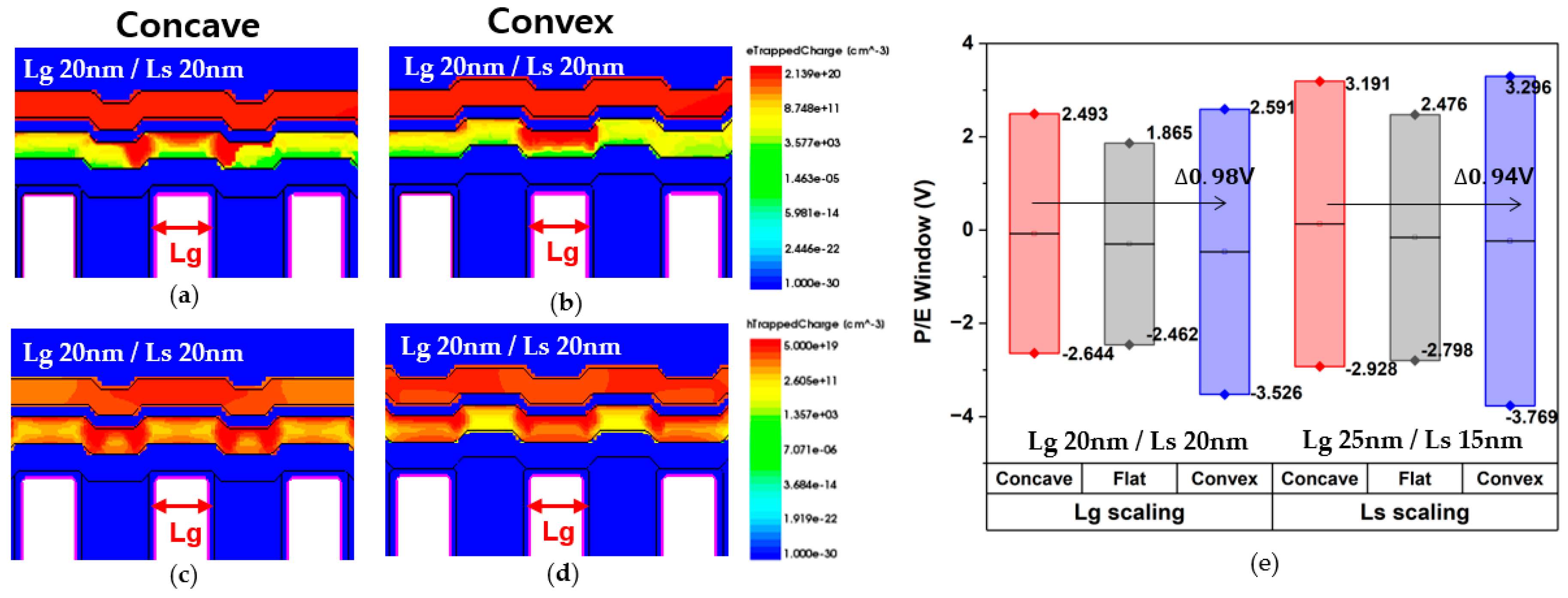

5. The Effect of Concave and Convex Structures

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Jun, H.; Cho, J.; Lee, K.; Son, H.-Y.; Kim, K.; Jin, H.; Kim, K. Hbm (high bandwidth memory) dram technology and architecture. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

- Park, K.-T.; Han, J.-M.; Kim, D.; Nam, S.; Choi, K.; Kim, M.-S.; Kwak, P.; Lee, D.; Choi, Y.-H.; Kang, K.-M.; et al. 19.5 Three-dimensional 128Gb MLC vertical NAND Flash-memory with 24-WL stacked layers and 50MB/s high-speed programming. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Goda, A.; Parat, K. Scaling directions for 2D and 3D NAND cells. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 2.1.1–2.1.4. [Google Scholar]

- Spinelli, A.; Compagnoni, C.; Lacaita, A. Reliability of NAND Flash Memories: Planar Cells and Emerging Issues in 3D Devices. Computers 2017, 6, 16. [Google Scholar] [CrossRef]

- Goda, A. 3-D NAND technology achievements and future scaling perspectives. IEEE Trans. Electron Devices 2020, 67, 1373–1381. [Google Scholar] [CrossRef]

- Alsmeier, J.; Higashitani, M.; Paak, S.S.; Sivaram, S. Past and Future of 3D Flash. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020. [Google Scholar]

- Nam, K.; Park, C.; Yoon, J.-S.; Jang, H.; Park, M.S.; Sim, J.; Baek, R.-H. Origin of incremental step pulse programming (ISPP) slope degradation in charge trap nitride based multi-layer 3D NAND flash. Solid-State Electron. 2021, 175, 107930. [Google Scholar] [CrossRef]

- Chen, W.-C.; Lue, H.-T.; Hsiao, Y.-H.; Hsu, T.-H.; Lin, X.-W.; Lu, C.-Y. Charge storage efficiency (CSE) effect in modeling the incremental step pulse programming (ISPP) in charge-trapping 3D NAND flash devices. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [Google Scholar]

- Sim, J.-M.; Kang, M.; Song, Y.-H. A Novel Program Operation Scheme with Negative Bias in 3-D NAND Flash Memory. IEEE Trans. Electron Devices 2021, 68, 6112–6117. [Google Scholar] [CrossRef]

- Chang, Y.-W.; Wu, G.-W.; Yang, I.-C.; Huang, Y.-H.; Lee, Y.-J.; Chen, K.-F.; Chen, Y.-J.; Lu, T.-C.; Chen, K.-C.; Lu, C.-Y. Deteriorated Non-Linear Interference in 3D NAND Cell with Word-Line Pitch Scaling Due to the Incapability to Turn on Non-Gate-Controlled Region. IEEE Electron Device Lett. 2023, 44, 1837–1840. [Google Scholar] [CrossRef]

- Kim, Y.; Hong, S.K.; Park, J.K. Optimizing Confined Nitride Trap Layers for Improved Z-Interference in 3D NAND Flash Memory. Electronics 2024, 13, 1020. [Google Scholar] [CrossRef]

- Rachidi, S.; Arreghini, A.; Verreck, D.; Donadio, G.; Banerjee, K.; Katcko, K.; Oniki, Y.; Rosmeulen, M. At the Extreme of 3D-NAND Scaling: 25 nm Z-Pitch with 10 nm Word Line Cells. In Proceedings of the 2022 IEEE International Memory Workshop (IMW), Dresden, Germany, 15–18 May 2022; pp. 1–4. [Google Scholar]

- Kim, C.; Kim, D.H.; Jeong, W.; Kim, H.J.; Park, I.H.; Park, H.W.; Lee, J.; Park, J.; Ahn, Y.L.; Lee, J.Y.; et al. A 512Gb 3b/cell 64-Stacked WL 3D V-NAND Flash Memory. IEEE J. Solid-State Circuits 2017, 53, 124–133. [Google Scholar] [CrossRef]

- Kim, S.; Shin, H. Analysis of the Effect of Residual Holes on Lateral Migration During the Retention Operation in 3-D NAND Flash Memory. IEEE Trans. Electron Devices 2021, 68, 6094–6099. [Google Scholar] [CrossRef]

- Chaudhry, A.; Kumar, M.J. Controlling short-channel effects in deep-submicron SOI MOSFETs for improved reliability: A review. IEEE Trans. Device Mater. Reliab. 2004, 4, 99–109. [Google Scholar] [CrossRef]

- Park, S.; Lee, J.; Jang, J.; Lim, J.K.; Kim, H.; Shim, J.J.; Yu, M.-t.; Kang, J.-K.; Ahn, S.J.; Song, J. Highly-reliable cell characteristics with 128-layer single-stack 3D-NAND flash memory. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Song, J.; Sim, J.-M.; Kim, B.; Song, Y.-H. Concave and Convex Structures for Advanced 3-D NAND Flash Memory Technology. IEEE Trans. Electron Devices 2024, 71, 2810–2814. [Google Scholar] [CrossRef]

| Program | Erase | Read | |

|---|---|---|---|

| Selected cell | 17~18 V | 0 V | −5 V~5 V |

| Unselected cell | 5.5 V | 0 V | 5.5 V |

| BL | 0 V | 20 V | 0.5 V |

| DSL | 3.3 V | Floating | 3.3 V |

| SSL | 0 V | Floating | 3.3 V |

| SL | 2 V | 20 V | 0 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, H.Y.; Hong, S.K.; Park, J.K. Systematic Analysis of Spacer and Gate Length Scaling on Memory Characteristics in 3D NAND Flash Memory. Appl. Sci. 2024, 14, 6689. https://doi.org/10.3390/app14156689

Bae HY, Hong SK, Park JK. Systematic Analysis of Spacer and Gate Length Scaling on Memory Characteristics in 3D NAND Flash Memory. Applied Sciences. 2024; 14(15):6689. https://doi.org/10.3390/app14156689

Chicago/Turabian StyleBae, Hee Young, Seul Ki Hong, and Jong Kyung Park. 2024. "Systematic Analysis of Spacer and Gate Length Scaling on Memory Characteristics in 3D NAND Flash Memory" Applied Sciences 14, no. 15: 6689. https://doi.org/10.3390/app14156689

APA StyleBae, H. Y., Hong, S. K., & Park, J. K. (2024). Systematic Analysis of Spacer and Gate Length Scaling on Memory Characteristics in 3D NAND Flash Memory. Applied Sciences, 14(15), 6689. https://doi.org/10.3390/app14156689