Silicon Surface Nanostructuration with Symmetric Cathode Configurations for Photonic Devices

Abstract

:1. Introduction

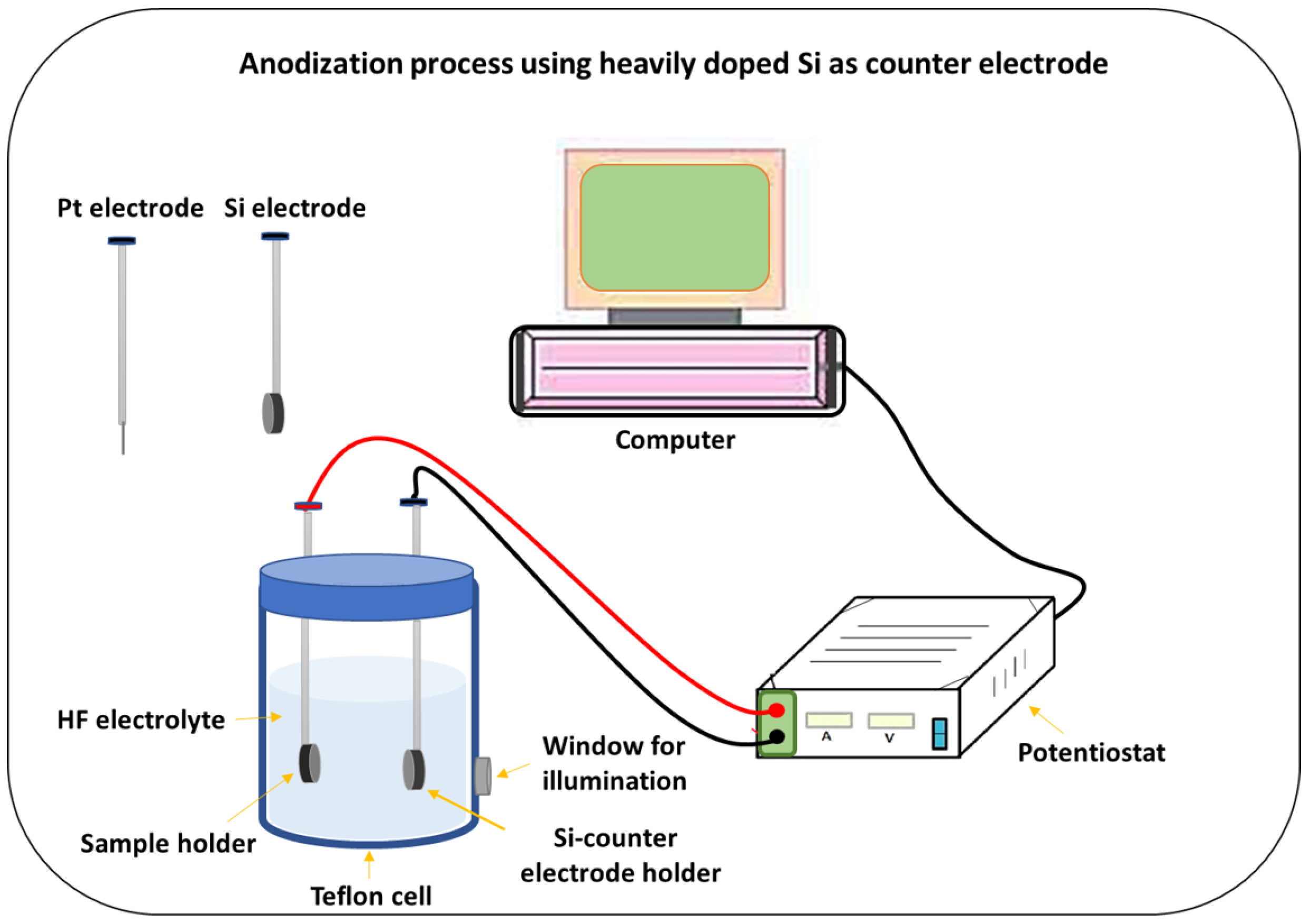

2. Materials and Methods

3. Results and Discussion

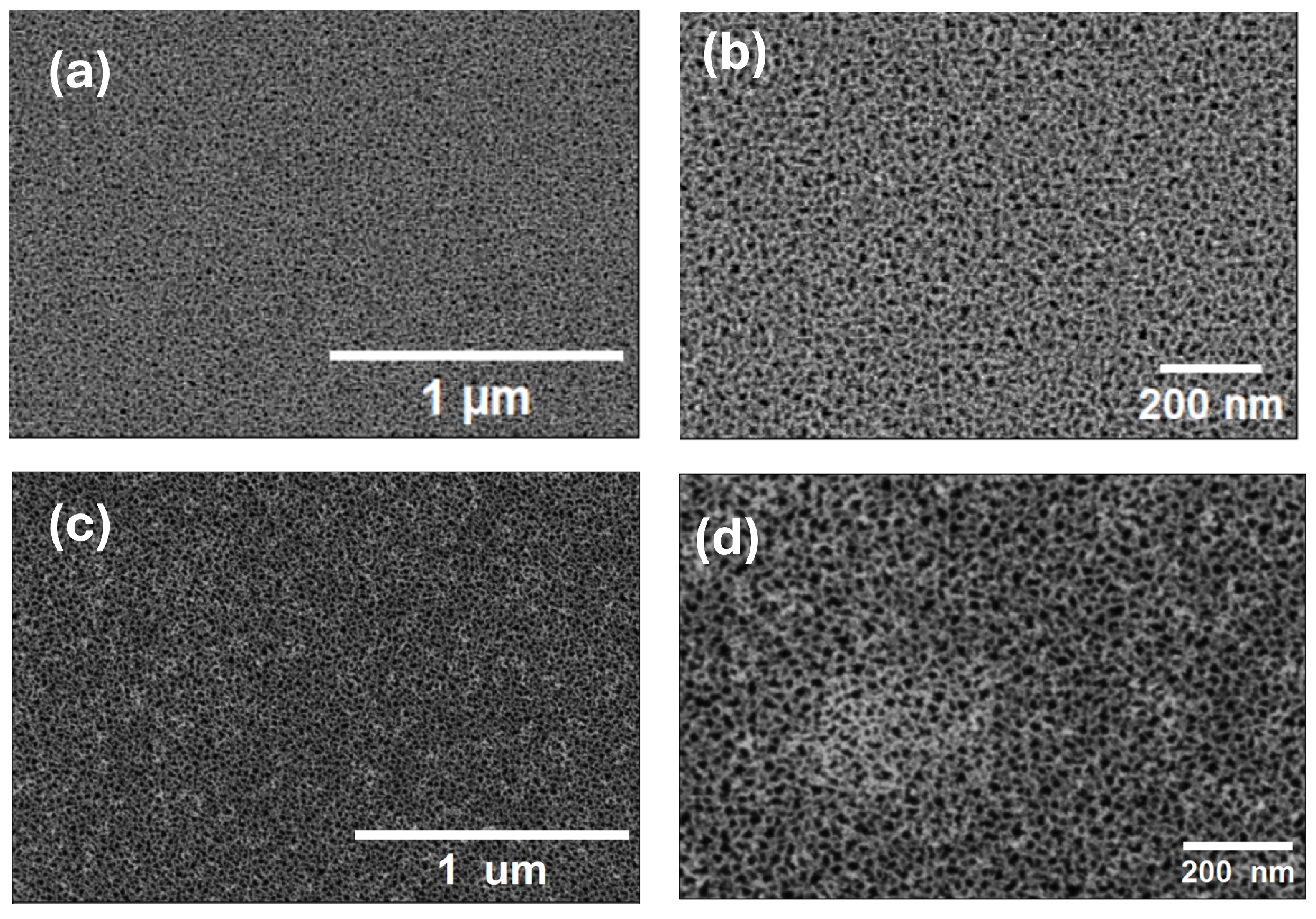

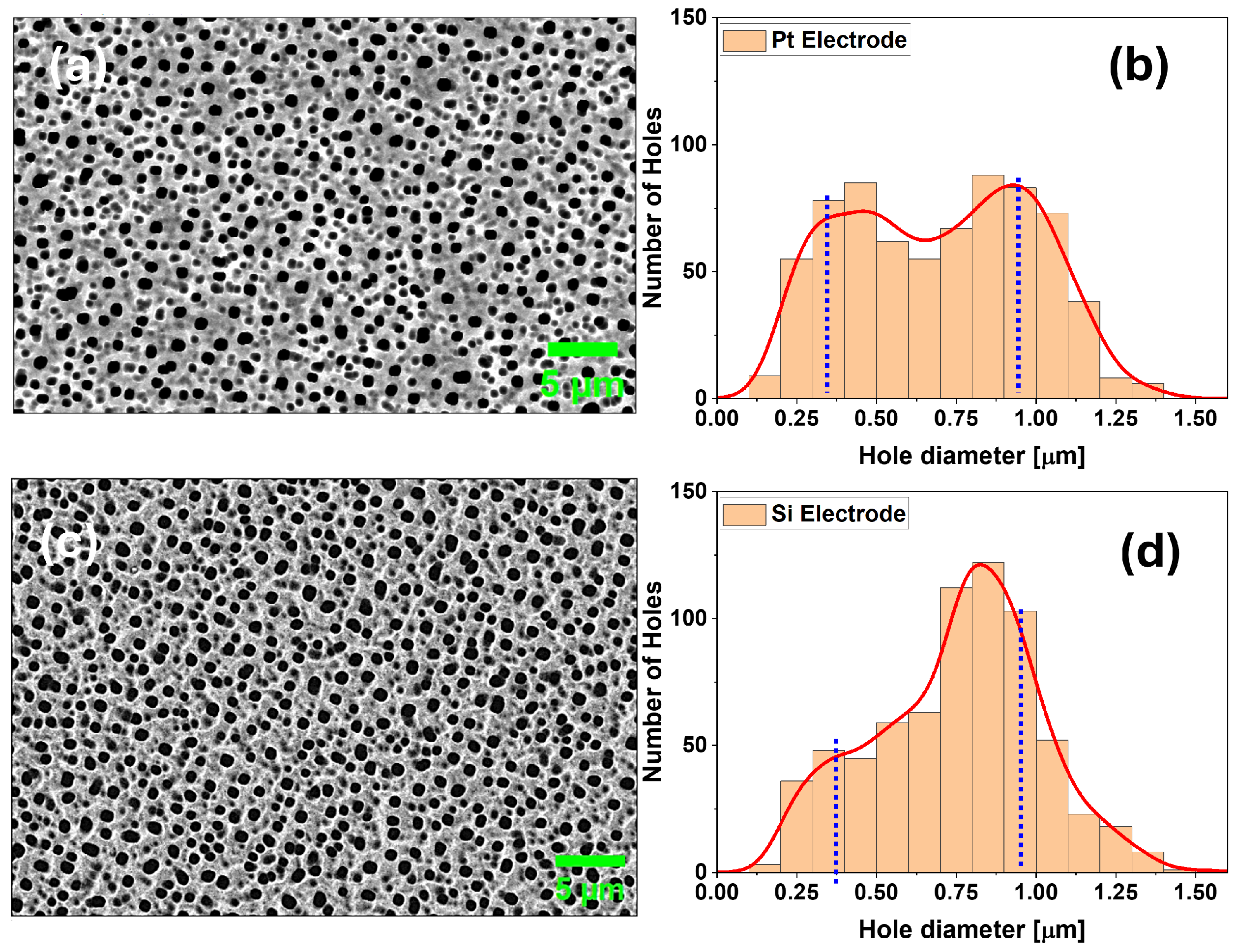

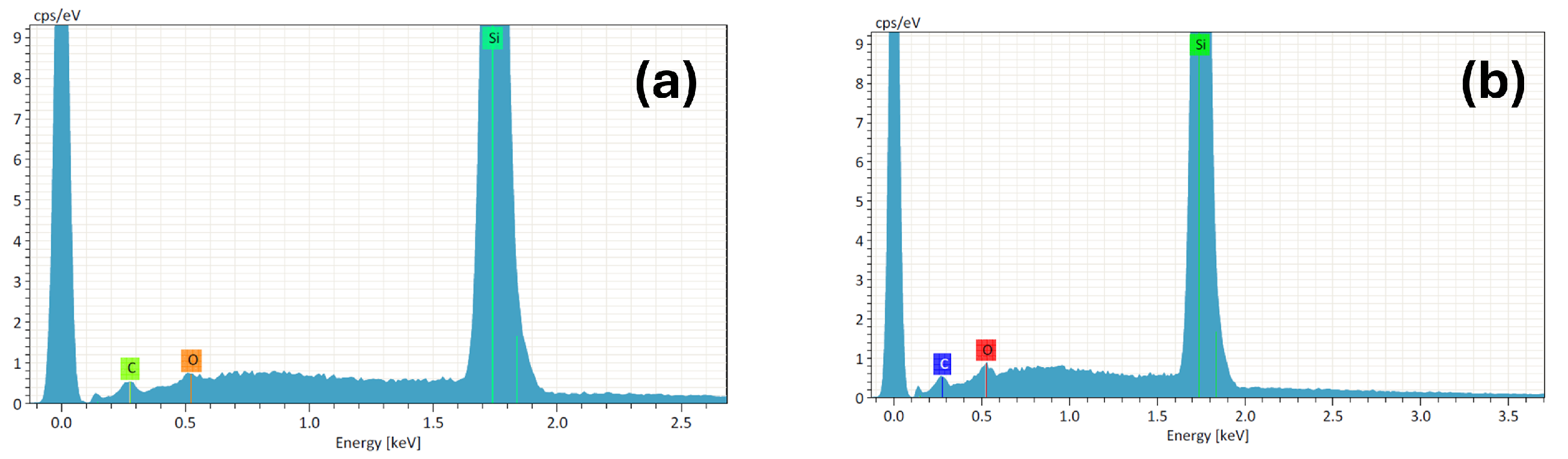

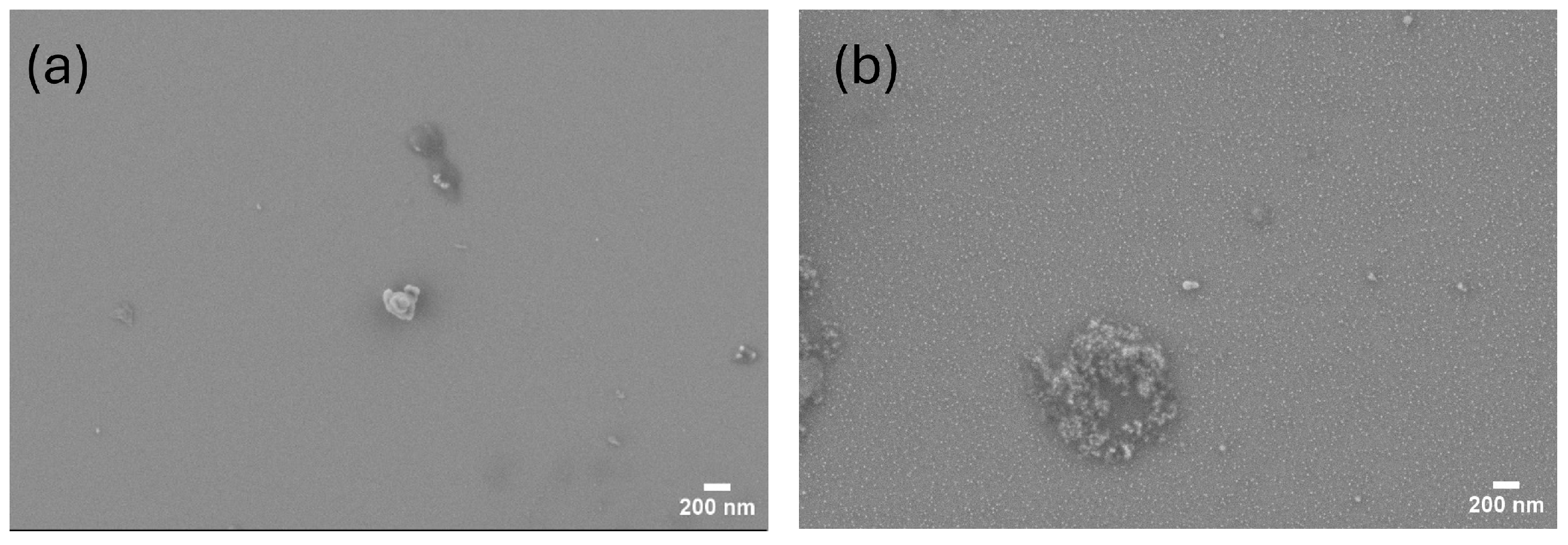

3.1. Morphology

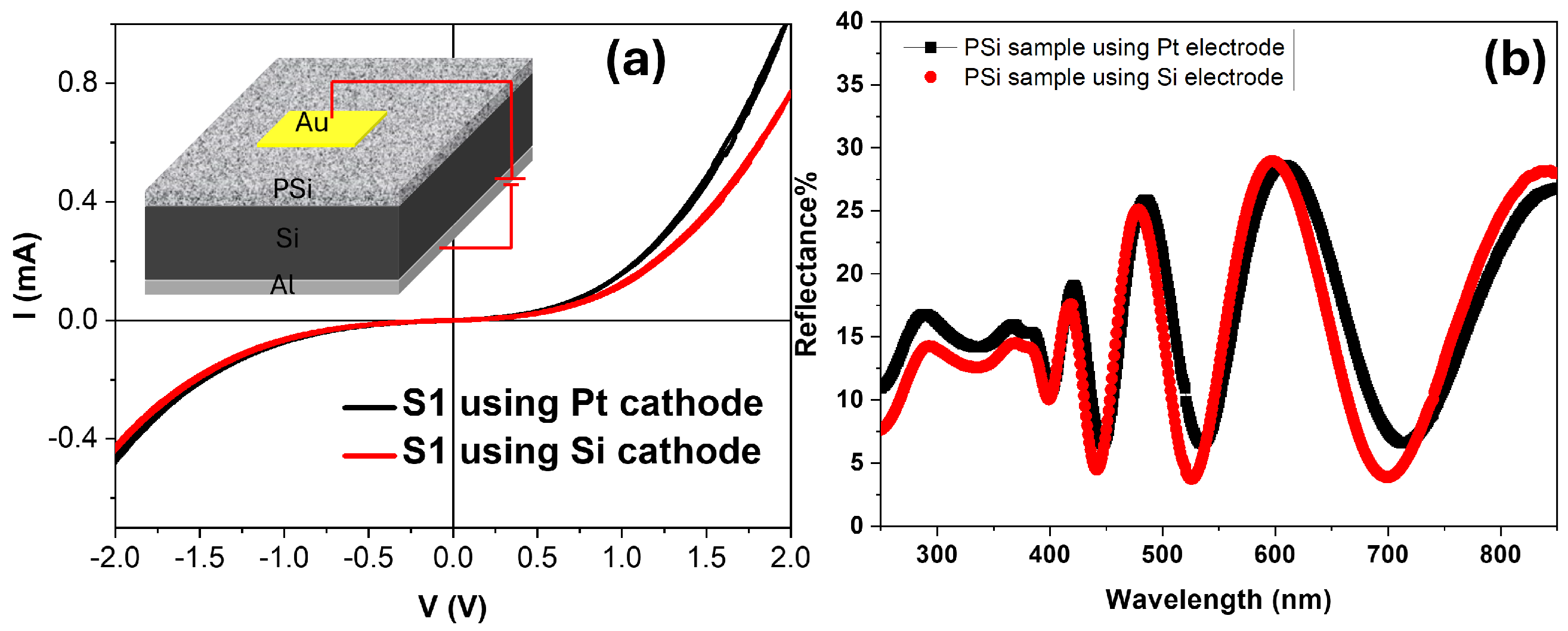

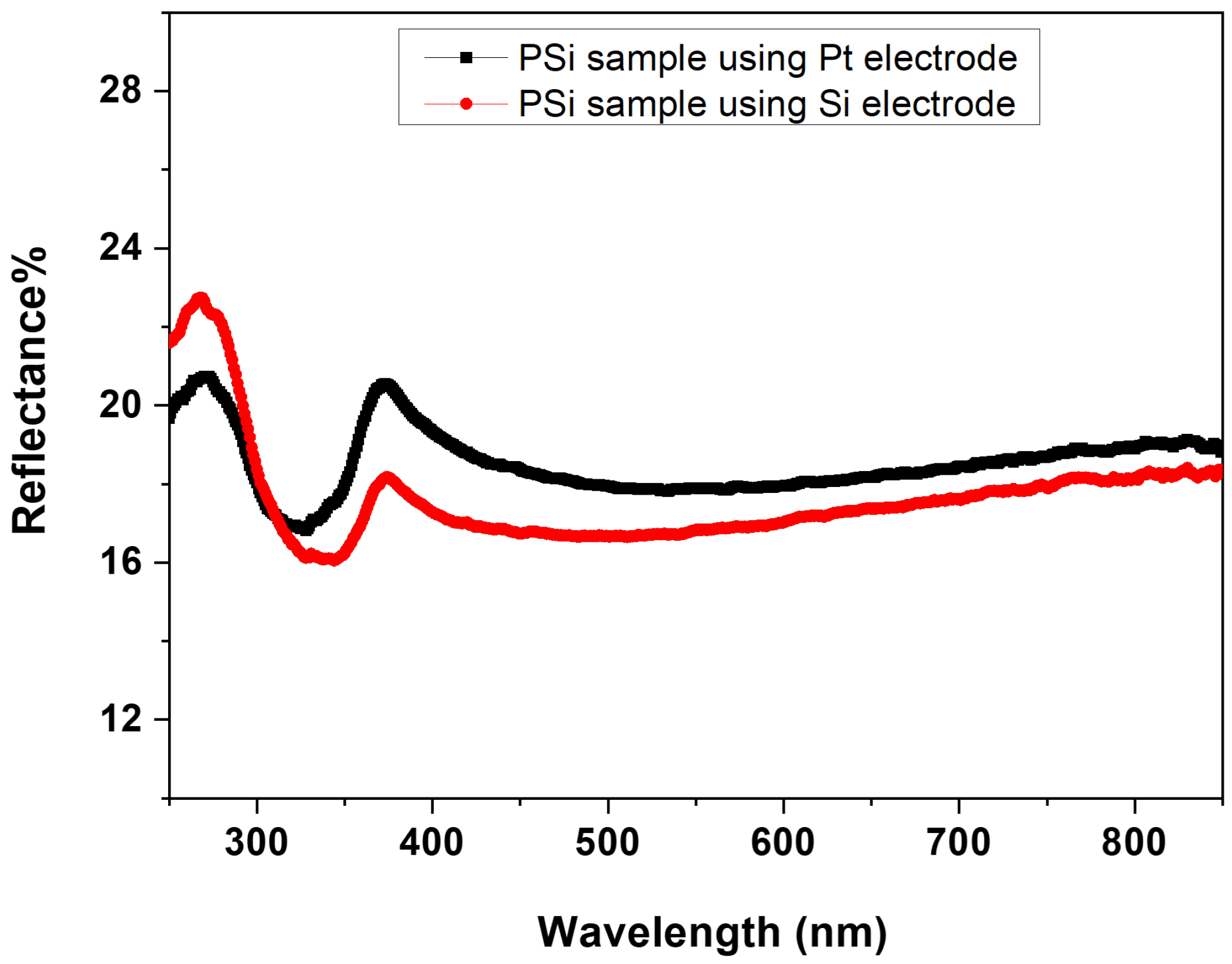

3.2. Optical and Electrical Properties

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Vercauteren, R.; Scheen, G.; Raskin, J.P.; Francis, L.A. Porous silicon membranes and their applications: Recent advances. Sens. Actuators A Phys. 2021, 318, 112486. [Google Scholar] [CrossRef]

- Ramadan, R.; Manso-Silván, M.; Martín-Palma, R.J. Hybrid porous silicon/silver nanostructures for the development of enhanced photovoltaic devices. J. Mater. Sci. 2020, 55, 5458–5470. [Google Scholar] [CrossRef]

- Korotcenkov, G. Porous Silicon: From Formation to Application: Formation and Properties; CRC Press: Boca Raton, FL, USA, 2016; Volume 1. [Google Scholar]

- Pérez, E.X. Design, Fabrication and Characterization of Porous Silicon Multilayer Optical Devices; Universitat Rovira i Virgili: Tarragona, Spain, 2008. [Google Scholar]

- Mortezaali, A.; Sani, S.R.; Jooni, F.J. Correlation between porosity of porous silicon and optoelectronic properties. J. Non-Oxide Glas. 2009, 1, 293–299. [Google Scholar]

- Harraz, F.A. Porous silicon chemical sensors and biosensors: A review. Sens. Actuators B Chem. 2014, 202, 897–912. [Google Scholar] [CrossRef]

- Ozdemir, S.; Gole, J.L. The potential of porous silicon gas sensors. Curr. Opin. Solid State Mater. Sci. 2007, 11, 92–100. [Google Scholar] [CrossRef]

- Zaky, Z.A.; Al-Dossari, M.; Hendy, A.S.; Zayed, M.; Aly, A.H. Gamma radiation detector using Cantor quasi-periodic photonic crystal based on porous silicon doped with polymer. Int. J. Mod. Phys. B 2024, 38, 2450409. [Google Scholar] [CrossRef]

- Villanueva, J.L.; Huanca, D.R.; Oliveira, A.F. Thickness and porosity characterization in porous silicon photonic crystals: The etch-stop effect. Mater. Chem. Phys. 2023, 307, 128070. [Google Scholar] [CrossRef]

- Huanca, D.R. Optical and structural characterization of one-dimensional porous silicon photonic crystals made in single and double electrochemical cells: Study on the back contact effect. Mater. Sci. Eng. B 2023, 297, 116733. [Google Scholar] [CrossRef]

- Fletcher, J.; Dell, J.; Parish, G.; Keating, A. Achieving Low Propagation Loss and Small-Index-Contrast Carbonized Porous Silicon Waveguides Using Direct Laser Writing. Adv. Photonics Res. 2024, 2400055. [Google Scholar] [CrossRef]

- Ali, A.; Hussain, M.S.; Almufarij, R.S.; Ali, M.Y.; Alharbe, L.G.; Somaily, H.; Shokralla, E.A.; Alrefaee, S.H.; Ashfaq, A.; Abd-Elwahed, A. Enhancing light trapping efficiency: Germanium-coated porous silicon structures for optimal antireflection performance. Ceram. Int. 2024, 50, 19424–19428. [Google Scholar] [CrossRef]

- Rahmouni, S.; Boubekri, H.; Bendjeffal, H.; Mamine, H.; Boukhenoufa, N.; Tifouti, I.; Mariane, B.; Nasri, N.; Zighed, L.; Chtourou, R. The Temperature Effect on the Photoluminescence of Porous Silicon Films Obtained from an N-Type Silicon Substrate. Silicon 2024, 16, 4253–4261. [Google Scholar] [CrossRef]

- Hu, S.; Bao, P.; Cao, Y.; Zhao, Z.; Chang, K.; Su, N.; Zhao, X.; Wang, H. Giant lateral photovoltaic effect in Ag/porous silicon/Si structure for high-performance near-infrared detection. Nano Energy 2024, 120, 109167. [Google Scholar] [CrossRef]

- Naderi, N.; Ahmad, H. Performance stability of porous silicon solar cells using reduced graphene oxide for applications in harsh environments. Opt. Commun. 2024, 559, 130422. [Google Scholar] [CrossRef]

- Arafat, M.Y.; Islam, M.A.; Mahmood, A.W.B.; Abdullah, F.; Nur-E-Alam, M.; Kiong, T.S.; Amin, N. Fabrication of black silicon via metal-assisted chemical etching—A review. Sustainability 2021, 13, 10766. [Google Scholar] [CrossRef]

- Pratiwi, N.D.; Handayani, M.; Suryana, R.; Nakatsuka, O. Fabrication of porous silicon using photolithography and reactive ion etching (RIE). Mater. Today: Proc. 2019, 13, 92–96. [Google Scholar] [CrossRef]

- Zhou, P.; Jiang, Z.; Li, Y.; Xiao, P.; Wu, F. Sulphur-template method for facile manufacturing porous silicon electrodes with enhanced electrochemical performance. Chin. Chem. Lett. 2024, 35, 109467. [Google Scholar] [CrossRef]

- Cao, D.T.; Anh, C.T.; Ngan, L.T.Q. Vertical-aligned silicon nanowire arrays with strong photoluminescence fabricated by metal-assisted electrochemical etching. J. Nanoelectron. Optoelectron. 2020, 15, 127–135. [Google Scholar] [CrossRef]

- Kolasinski, K.W. Silicon nanostructures from electroless electrochemical etching. Curr. Opin. Solid State Mater. Sci. 2005, 9, 73–83. [Google Scholar] [CrossRef]

- Searson, P.; Macaulay, J.; Prokes, S. The formation, morphology, and optical properties of porous silicon structures. J. Electrochem. Soc. 1992, 139, 3373. [Google Scholar] [CrossRef]

- Uhlir Jr, A. Electrolytic shaping of germanium and silicon. Bell Syst. Tech. J. 1956, 35, 333–347. [Google Scholar] [CrossRef]

- Kumar, P.; Huber, P. Effect of etching parameter on pore size and porosity of electrochemically formed nanoporous silicon. J. Nanomater. 2007, 2007, 089718. [Google Scholar] [CrossRef]

- Korotcenkov, G.; Cho, B. Silicon porosification: State of the art. Crit. Rev. Solid State Mater. Sci. 2010, 35, 153–260. [Google Scholar] [CrossRef]

- Husairi, F.; Rouhi, J.; Eswar, K.; Zainurul, A.; Rusop, M.; Abdullah, S. Electrochemical impedance spectroscopy analysis of porous silicon prepared by photo-electrochemical etching: Current density effect. Appl. Phys. A 2014, 116, 2119–2124. [Google Scholar] [CrossRef]

- Barillaro, G.; Nannini, A.; Piotto, M. Electrochemical etching in HF solution for silicon micromachining. Sens. Actuators A Phys. 2002, 102, 195–201. [Google Scholar] [CrossRef]

- Sharma, S.N.; Sharma, R.; Lakshmikumar, S. Role of an electrolyte and substrate on the stability of porous silicon. Phys. E Low-Dimens. Syst. Nanostructures 2005, 28, 264–272. [Google Scholar] [CrossRef]

- Sailor, M.J. Porous Silicon in Practice: Preparation, Characterization and Applications; John Wiley & Sons: Hoboken, NJ, USA, 2012. [Google Scholar]

- Santos, A.; Kumeria, T. Electrochemical etching methods for producing porous silicon. Electrochem. Eng. Nanoporous Mater. Methods Prop. Appl. 2015, 20, 1–36. [Google Scholar]

- Ashruf, C.; French, P.; Bressers, P.; Kelly, J. Galvanic porous silicon formation without external contacts. Sens. Actuators A Phys. 1999, 74, 118–122. [Google Scholar] [CrossRef]

- Behzad, K.; Yunus, W.M.M.; Talib, Z.A.; Zakaria, A.; Bahrami, A. Effect of preparation parameters on physical, thermal and optical properties of n-type porous silicon. Int. J. Electrochem. Sci. 2012, 7, 8266–8275. [Google Scholar] [CrossRef]

- Zare, M.; Shokrollahi, A.; Seraji, F.E. Effect of fabrication parameters on morphological and optical properties of highly doped p-porous silicon. Appl. Surf. Sci. 2011, 257, 9507–9514. [Google Scholar] [CrossRef]

- Xu, J.; Liu, S.; Yang, Y.; Li, J.; Tian, C.; Guo, L.; Zhang, S.; Liu, Y.; Zhong, Z. Preparation of porous silicon by electrochemical etching methods and its morphological and optical properties. Int. J. Electrochem. Sci. 2019, 14, 5188–5199. [Google Scholar] [CrossRef]

- Jakubowicz, J. Nanoporous silicon fabricated at different illumination and electrochemical conditions. Superlattices Microstruct. 2007, 41, 205–215. [Google Scholar] [CrossRef]

- Watanabe, Y.; Arita, Y.; Yokoyama, T.; Igarashi, Y. Formation and properties of porous silicon and its application. J. Electrochem. Soc. 1975, 122, 1351. [Google Scholar] [CrossRef]

- ARahim, F.; Ahmed, M.; Razali, N.; Radzali, R.; Mahmood, A.; Hamzah, I.; Noorsal, E. Investigation of Light Trapping from Porous Silicon Surface for the Enhancement of Silicon Solar Cell Performance. Acta Phys. Pol. A 2019, 135, 637–642. [Google Scholar]

- Nelson, J.A. The Physics of Solar Cells; World Scientific Publishing Company: Singapore, 2003. [Google Scholar]

- Martín-Palma, R.J.; McAtee, P.D.; Ramadan, R.; Lakhtakia, A. Hybrid nanostructured porous silicon-silver layers for wideband optical absorption. Sci. Rep. 2019, 9, 7291. [Google Scholar] [CrossRef] [PubMed]

- Ramadan, R.; Martín-Palma, R.J. Electrical characterization of MIS Schottky barrier diodes based on nanostructured porous silicon and silver nanoparticles with applications in solar cells. Energies 2020, 13, 2165. [Google Scholar] [CrossRef]

- Carrillo, F.S.; García-Salgado, G.; Villanueva, M.S. Optical, Morphological, and Structural Properties of Tablets Obtained from Porous Silicon. Silicon 2022, 14, 7685–7691. [Google Scholar] [CrossRef]

- Martín-Palma, R.; Pascual, L.; Herrero, P.; Martínez-Duart, J. Monte Carlo determination of crystallite size of porous silicon from x-ray line broadening. Appl. Phys. Lett. 2005, 87, 211906. [Google Scholar] [CrossRef]

- Martın-Palma, R.; Pascual, L.; Herrero, P.; Martınez-Duart, J. Direct determination of grain sizes, lattice parameters, and mismatch of porous silicon. Appl. Phys. Lett. 2002, 81, 25–27. [Google Scholar] [CrossRef]

- Ramadan, R.; Martín-Palma, R.J. Precise calculation of the optical constants of self-standing nanoporous silicon layers. Silicon 2023, 15, 4391–4395. [Google Scholar] [CrossRef]

- Theiß, W. Optical properties of porous silicon. Surf. Sci. Rep. 1997, 29, 91–192. [Google Scholar] [CrossRef]

- Ramadan, R.; Torres-Costa, V.; Martín-Palma, R.J. Self-powered broadband hybrid organic–inorganic photodetectors based on PEDOT: PSS and silicon micro-nanostructures. J. Mater. Chem. C 2021, 9, 4682–4694. [Google Scholar] [CrossRef]

- Saarinen, J.J.; Weiss, S.M.; Fauchet, P.M.; Sipe, J. Optical sensor based on resonant porous silicon structures. Opt. Express 2005, 13, 3754–3764. [Google Scholar] [CrossRef] [PubMed]

- Lank, N.O.; Kall, M.; Antosiewicz, T.J. Electromagnetic energy distribution in resonant quasi porous silicon nanostructures. ACS Photonics 2019, 6, 1706–1714. [Google Scholar] [CrossRef]

- Sohn, H. Refractive index of porous silicon. In Handbook of Porous Silicon; Springer Nature: Berlin, Germany, 2014; pp. 231–243. [Google Scholar]

- Villatoro, J.; Finazzi, V.; Badenes, G.; Pruneri, V. Highly sensitive sensors based on photonic crystal fiber modal interferometers. J. Sensors 2009, 2009, 747803. [Google Scholar] [CrossRef]

- Kinoshita, S.; Yoshioka, S.; Miyazaki, J. Physics of structural colors. Rep. Prog. Phys. 2008, 71, 076401. [Google Scholar] [CrossRef]

| Substrate Resistivity () | Etching Solution | J (mA/cm2) | t (s) |

|---|---|---|---|

| S1 = 0.01–0.02 ·cm | HF 48%: ETOH 99% (1:2) | 80 | 14 |

| S2 = 0.8–2 ·cm | HF 48%: ETOH 99% (1:2) | 20 | 100 |

| S3 = 25–30 ·cm | HF 48%: DMF 98% (1:6) | 20 | 200 |

| Samples-S1 | I0 (mA) | n | Rs (k) | Rsh (k) |

|---|---|---|---|---|

| using Pt cathode | 4.80 × 10−4 | 5.44 | 1.0 | 42.38 |

| using Si cathode | 2.15 × 10−4 | 4.79 | 1.08 | 42.82 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramadan, R.; Elshorbagy, M.H.; Martín-Palma, R.J. Silicon Surface Nanostructuration with Symmetric Cathode Configurations for Photonic Devices. Appl. Sci. 2024, 14, 8635. https://doi.org/10.3390/app14198635

Ramadan R, Elshorbagy MH, Martín-Palma RJ. Silicon Surface Nanostructuration with Symmetric Cathode Configurations for Photonic Devices. Applied Sciences. 2024; 14(19):8635. https://doi.org/10.3390/app14198635

Chicago/Turabian StyleRamadan, Rehab, Mahmoud Hamdy Elshorbagy, and Raúl J. Martín-Palma. 2024. "Silicon Surface Nanostructuration with Symmetric Cathode Configurations for Photonic Devices" Applied Sciences 14, no. 19: 8635. https://doi.org/10.3390/app14198635