A Broadband Millimeter-Wave 5G Low Noise Amplifier Design in 22 nm Fully Depleted Silicon-on-Insulator (FD-SOI) CMOS

Abstract

:1. Introduction

2. LNA Design Methodology

2.1. 22 nm FD-SOI CMOS Technology

2.2. Device Selection

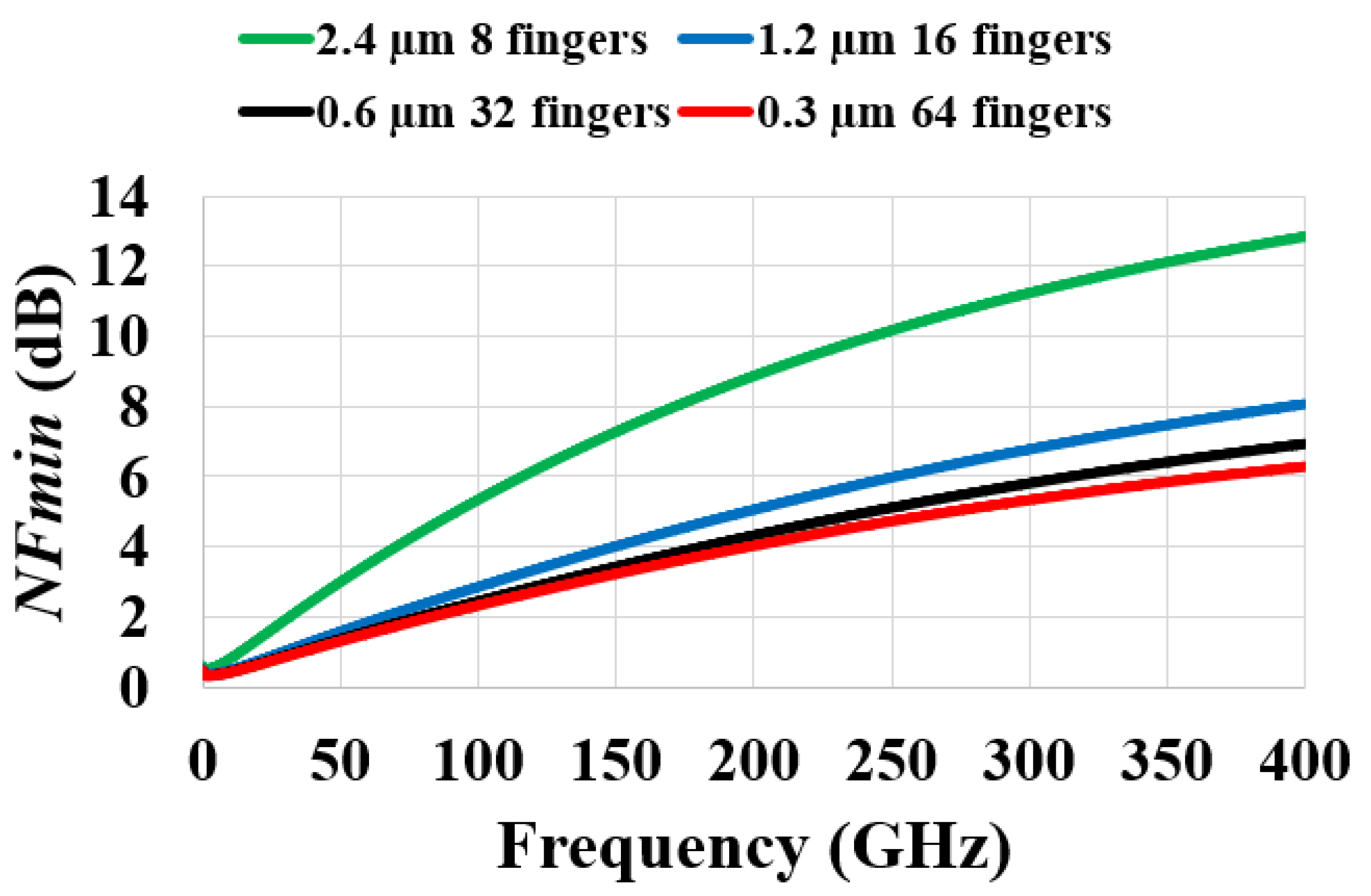

2.2.1. Finger Width and Number of Fingers

2.2.2. Contact Poly Pitch (CPP)

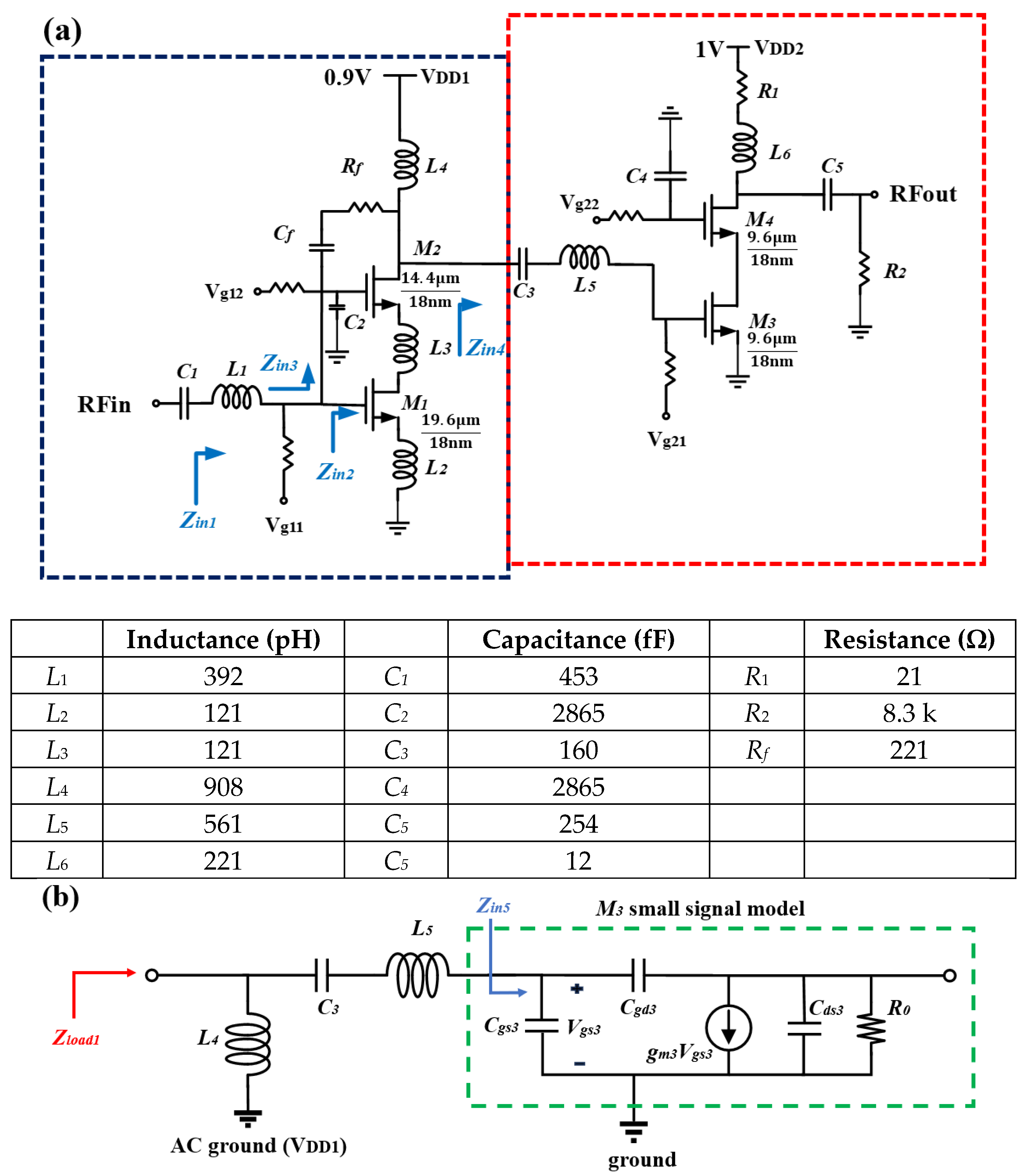

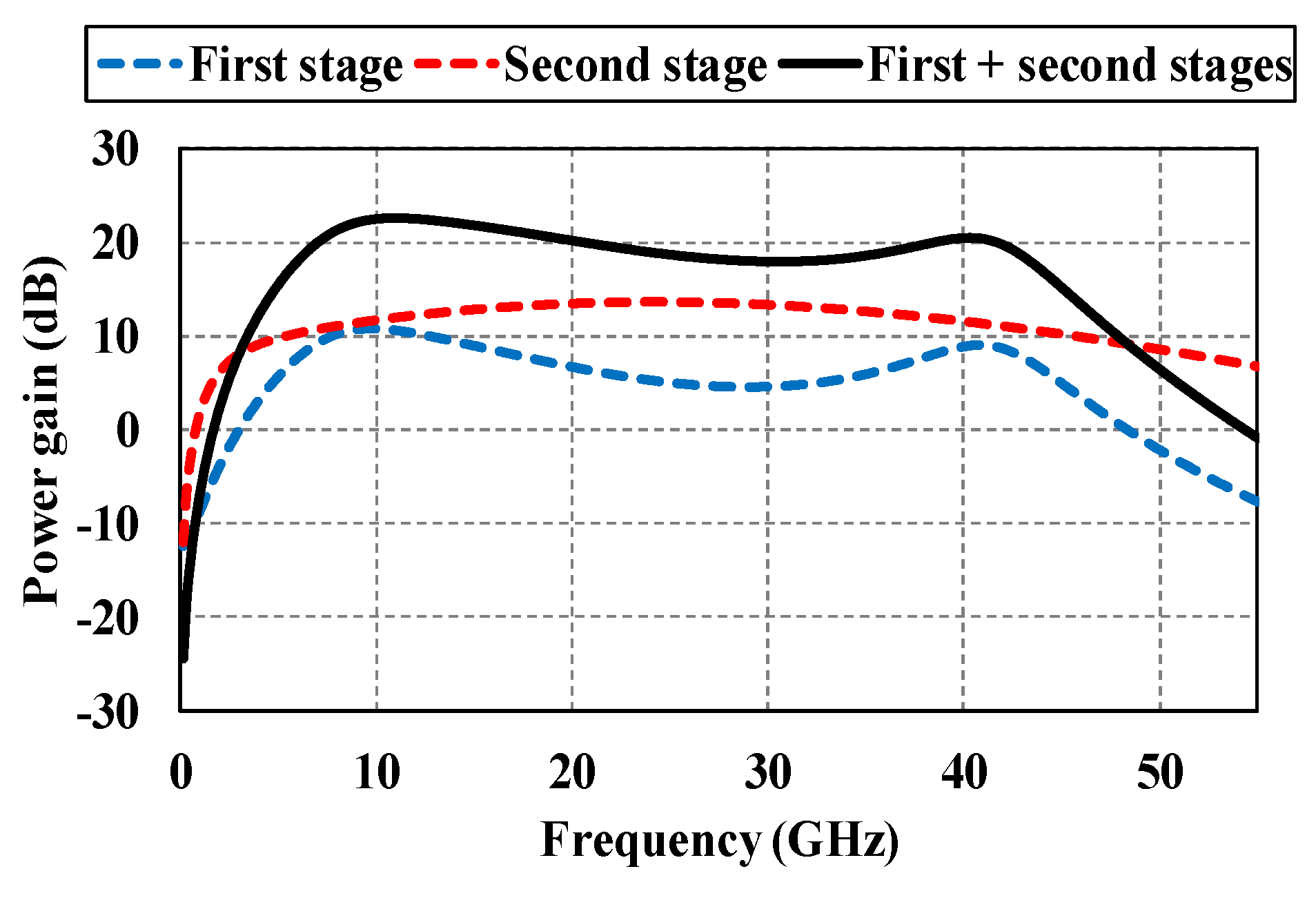

2.3. Two-Stage Gain Compensation

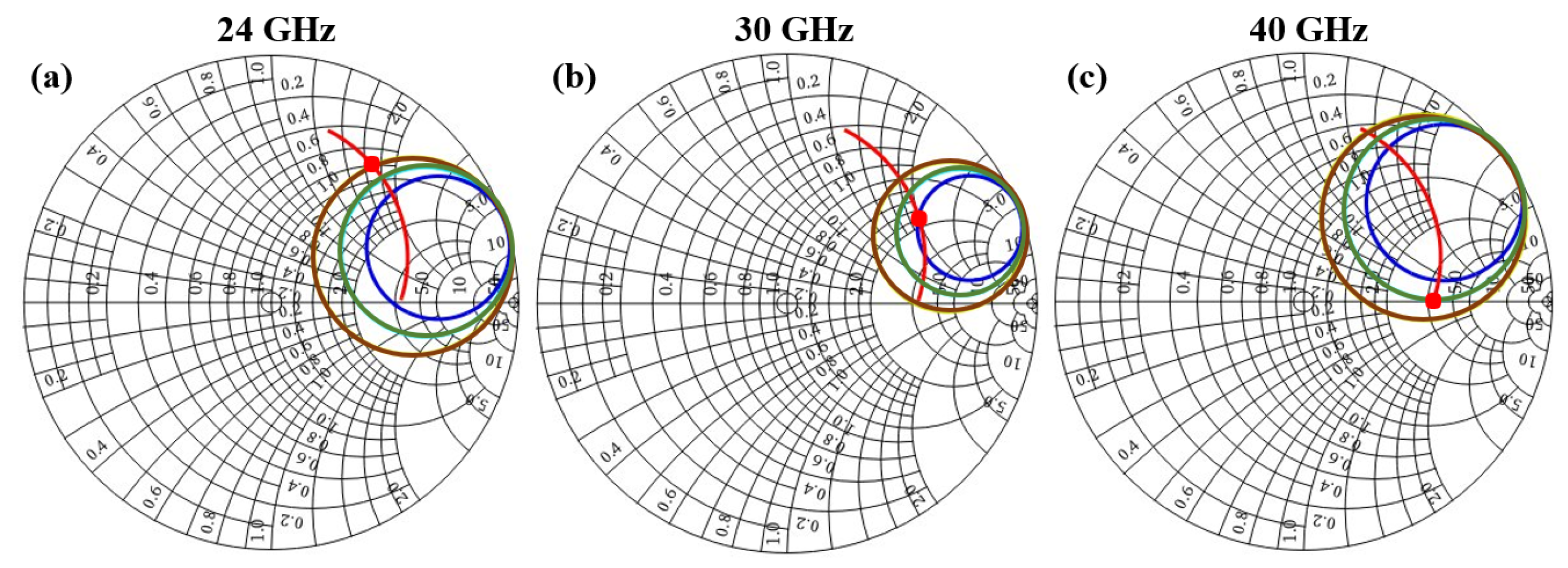

2.4. Resistive Feedback Network for Improved Input Matching and Broadband Gain Response

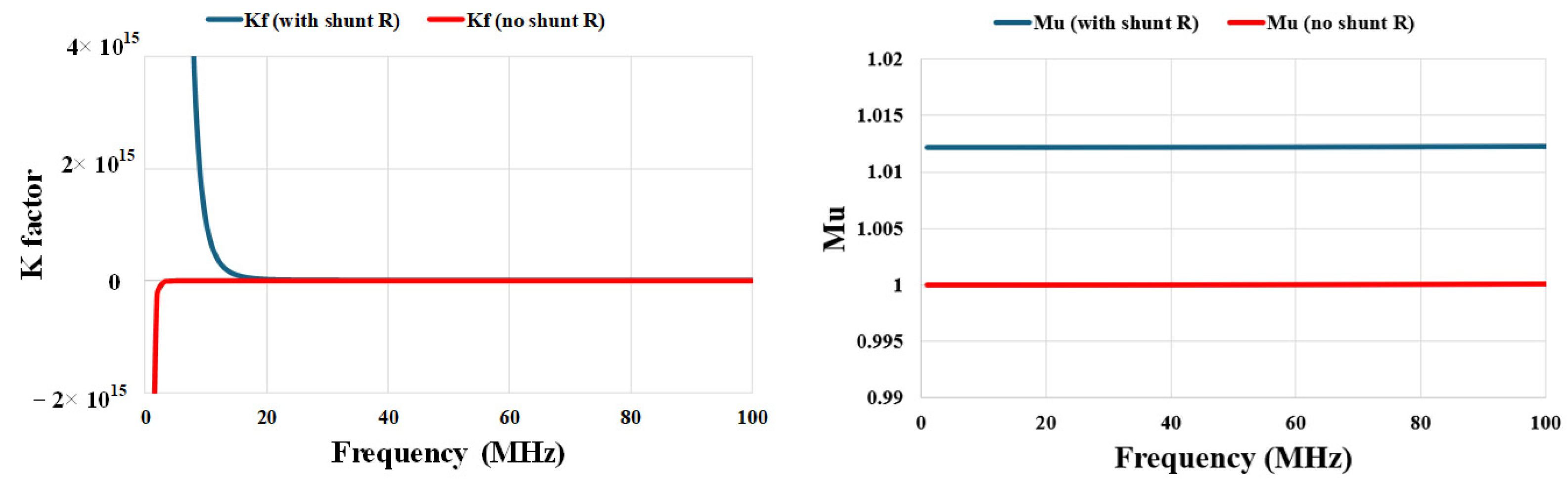

3. Layout and More PEX and EM Simulation Results

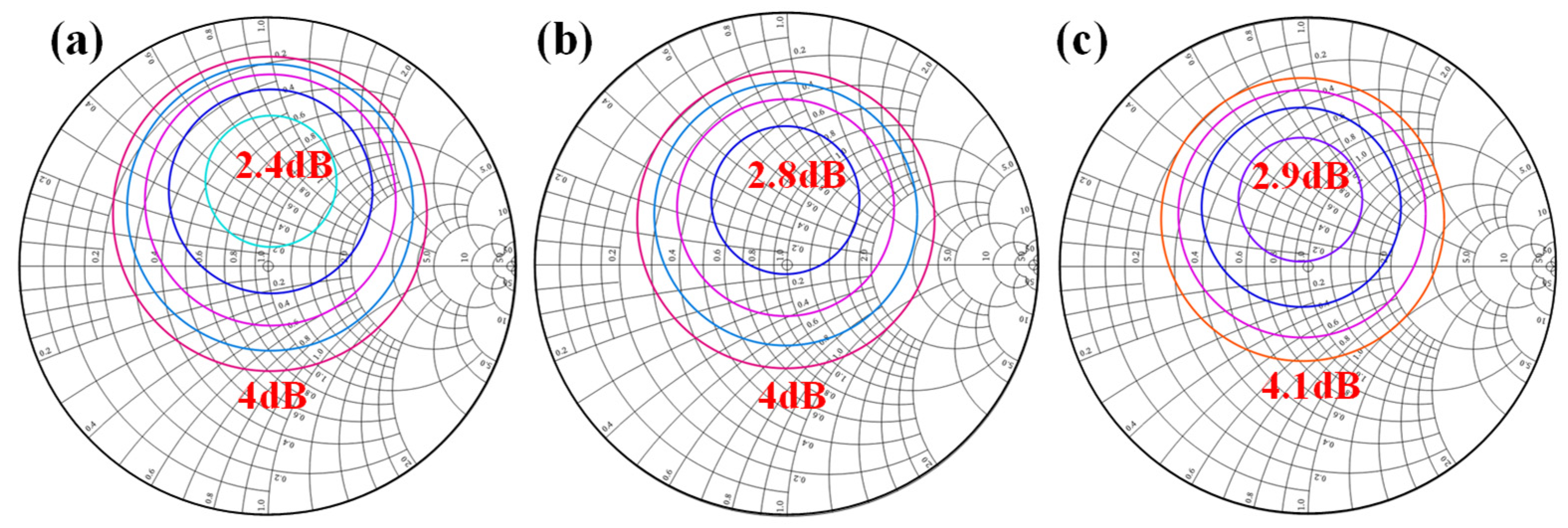

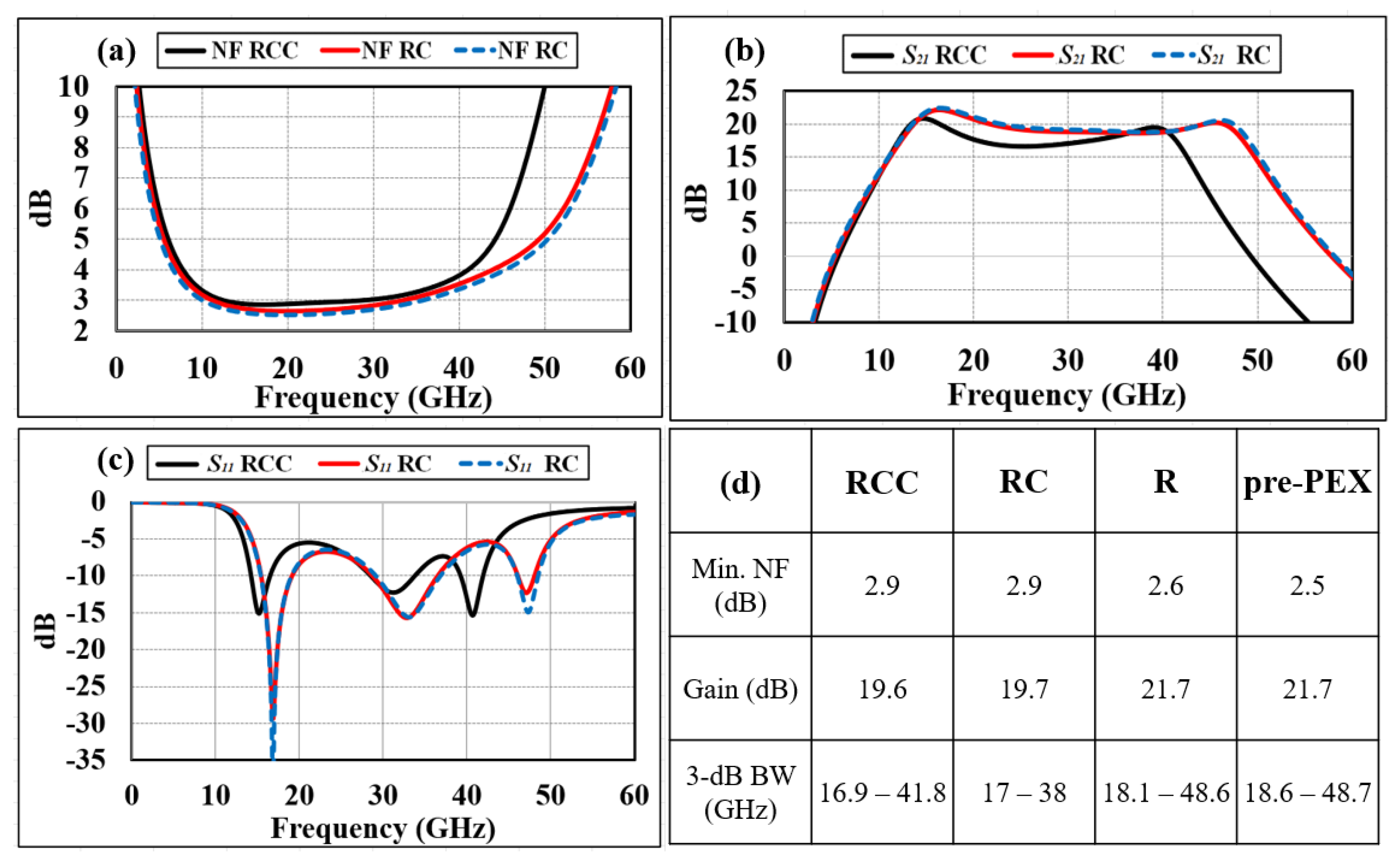

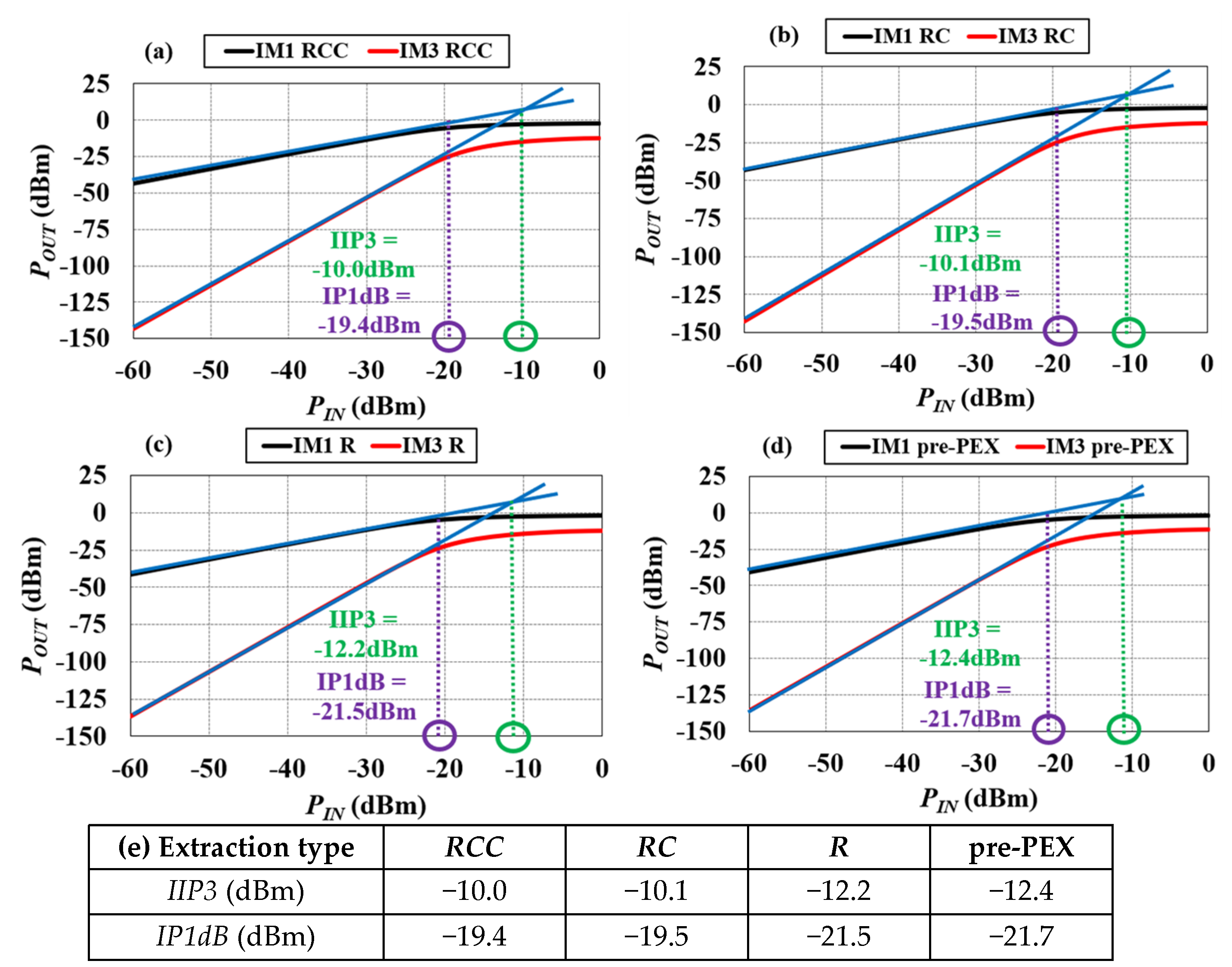

3.1. Comparison of PEX vs. Pre-PEX Simulated Results

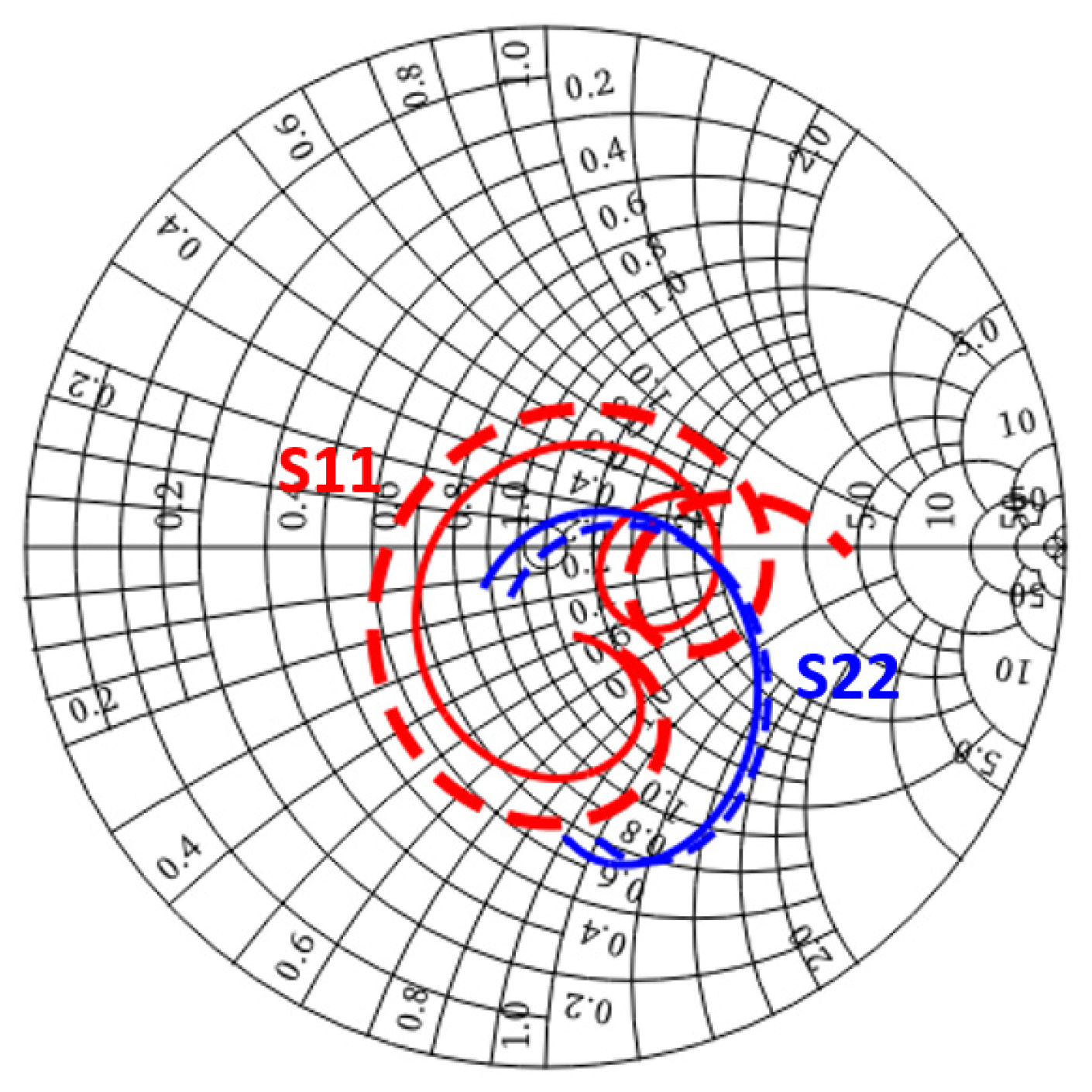

3.2. EM Simulated Results vs. PEX RCC

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- El-Aassar, O.; Rebeiz, G.M. Design of Low-Power Sub-2.4 dB Mean NF 5G LNAs Using Forward Body Bias in 22 nm FDSOI. IEEE Trans. Microw. Theory Tech. 2020, 68, 4445–4454. [Google Scholar] [CrossRef]

- Hu, Y.; Chi, T. A 27–46-GHz Low-Noise Amplifier with Dual-Resonant Input Matching and a Transformer-Based Broadband Output Network. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 725–728. [Google Scholar] [CrossRef]

- Wang, R.; Li, C.; Zhang, J.; Yin, S.; Zhu, W.; Wang, Y. A 18–44 GHz Low Noise Amplifier with Input Matching and Bandwidth Extension Techniques. IEEE Microw. Wirel. Compon. Lett. 2022, 32, 1083–1086. [Google Scholar] [CrossRef]

- Gao, L.; Rebeiz, G.M. A 24-43 GHz LNA with 3.1-3.7 dB Noise Figure and Embedded 3-Pole Elliptic High-Pass Response for 5G Applications in 22 nm FDSOI. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 239–242. [Google Scholar]

- Cui, B.; Long, J.R. A 1.7-dB Minimum NF, 22–32-GHz Low-Noise Feedback Amplifier with Multistage Noise Matching in 22-nm FD-SOI CMOS. IEEE J. Solid State Circuits 2020, 55, 1239–1248. [Google Scholar] [CrossRef]

- Radpour, M.; Belostotski, L. An LNA with Input Power Match from 6.1 to 38.6 GHz, the Noise-Figure Minimum of 1.9 dB, and Employing Back Gate for Matching. In Proceedings of the 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Denver, CO, USA, 19 June 2022; pp. 235–238. [Google Scholar]

- Zhang, C.; Zhang, F.; Syed, S.; Otto, M.; Bellaouar, A. A Low Noise Figure 28GHz LNA in 22nm FDSOI Technology. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 207–210. [Google Scholar]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice-Hall: New York, NY, USA, 2012; pp. 58–60. [Google Scholar]

- Chauhan, V.; Floyd, B. A 24–44 GHz UWB LNA for 5G Cellular Frequency Bands. In Proceedings of the 2018 11th Global Symposium on Millimeter Waves (GSMM), Boulder, CO, USA, 22–24 May 2018; pp. 1–3. [Google Scholar]

- Lie, D.Y.C.; Mayeda, J.C.; Lopez, J. RF Hardware Design for 5G mm-Wave and 6G Revolutions: Challenges and Opportunities. In Proceedings of the 8th IEEE International Conference on Consumer Electronics (ICCE-TW), Penghu, Taiwan, 15–17 September 2021. [Google Scholar]

- Ong, S.N.; Lehmann, S.; Chow, W.H.; Zhang, C.; Schippel, C.; Chan, L.H.K.; Andee, Y.; Hauschildt, M.; Tan, K.K.S.; Watts, J.; et al. A 22nm FDSOI Technology Optimized for RF/mmWave Applications. In Proceedings of the 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 72–75. [Google Scholar]

- Mayeda, J.C.; Lie, D.Y.C.; Lopez, J. Design of Broadband Highly Efficient Linear Power Amplifiers for mm-Wave 5G in 22nm FDSOI and 40 nm GaN/SiC. Electronics 2022, 11, 683. [Google Scholar] [CrossRef]

- Mayeda, J.C.; Tsay, J.; Lie, D.Y.C.; Lopez, J. Effective AM-PM Cancellation with Body Bias for 5G CMOS Power Amplifier Design in 22nm FD-SOI. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–4. [Google Scholar]

- Kane, O.; Lucci, L.; Scheiblin, P.; Lepilliet, S.; Danneville, F. RF characterization and small signal extraction on 22 nm CMOS fully-depleted SOI technology. In Proceedings of the 2019 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Grenoble, France, 1–3 April 2019; pp. 1–4. [Google Scholar]

- Wang, X.; Li, Z.; Li, Z. A 1.46-1.96dB-NF 2.1-5.2-GHz Wideband Passive Balun LNA in 22-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 3378–3382. [Google Scholar]

- Lee, T.H. The Design of CMOS Radio-Frequency Integrated Circuits, 2nd ed.; Cambridge University Press: New York, NY, USA, 2004; pp. 376–380. [Google Scholar]

- Kim, C.-W.; Kang, M.-S.; Anh, P.T.; Kim, H.-T.; Lee, S.-G. An Ultra-Wideband CMOS Low Noise Amplifier for 3-5GHz UWB System. IEEE J. Solid State Circuits 2005, 40, 544–547. [Google Scholar]

- Dunn, J.M.; Kapur, S.; Long, D. EMX: Overcoming Silicon Chip EM Simulation Challenges for Passive Circuit Analysis and Model Development. In Proceedings of the 2021 International Applied Computational Electromagnetics Society Symposium (ACES), Hamilton, ON, Canada, 1–5 August 2021; pp. 1–4. [Google Scholar]

- Pozar, D.M. Microwave Engineering, 4th ed.; John Wiley & Sons Inc.: Hoboken, NJ, USA, 2012; p. 567. [Google Scholar]

- Zhang, H.; Sánchez-Sinencio, E. Linearization Techniques for CMOS Low Noise Amplifiers: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 22–36. [Google Scholar] [CrossRef]

| W/L | 8 µm/18 nm | 16 µm/18 nm | 32 µm/18 nm | 64 µm/18 nm |

| CPP | 1x/2x | 1x/2x | 1x/2x | 1x/2x |

| NFmin @ 28 GHz (dB) | 0.691/0.636 | 0.839/0.709 | 1.175/0.866 | 1.926/1.168 |

| fMAX (GHz) | 303/309 | 253/273 | 182/222 | 139/188 |

| fT (GHz) | 349/344 | 371/372 | 381/386 | 386/391 |

| This Work (EM) | This Work (RCC) | [2] MWCL ‘21 | [3] MWCL ‘22 | [4] RFIC ‘19 | [5] JSSC ‘20 | [1] TMTT ‘20 | [6] RFIC ‘22 | [7] RFIC ‘19 | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Technology | 22 nm FDSOI | 45 nm RFSOI | 65 nm CMOS | 22 nm FDSOI | 22 nm FDSOI | 22 nm FDSOI | 22 nm FDSOI | 22 nm FDSOI | ||||

| Topology | 2-stage CAS | 2-stage CAS | 2-stage CS + 1 stage CAS | 3-stage CAS | 1-stage CS + 1stage CAS with CS source-gate FB | 1-stage CS | 2-stage CS | 2-stage CAS | 2-stage CS + buffer | 1-stage CAS | ||

| S21 3 dB BW (GHz) | 17.8–42.4 | 16.9–41.8 | 25.5–50 | 18–44 | 24–43 | 19–36 | 20–36 | 21.6–32.8 | 19.5–29 | 23–27 | 6.1–26.2 | 23–40 |

| FBW (%) | 81.7 | 84.8 | 64.9 | 83.9 | 56.7 | 61.8 | 57.1 | 41.2 | 39.6 | 16 | 124.5 | 54.0 |

| VDD (V) | 0.9/1 | 1.3 | 1 | 1/1.6 | 1.05 | 1.05 | 0.8/1.6 | 0.4/0.8 | 0.8/1.6 | 0.8/0.4 | 1.3 | |

| Max S21 (dB) | 18.3 | 19.6 | 21.2 | 19.5 | 23 | 21.5 | 17.9 | 7.8/10.2 | 16.9/20.1 | 23.2/28.5 | 15.6 | 12.6 |

| NF (dB) | 2.9–4.9 | 2.9–4.1 | 2.4–4.2 | 2.6–3.5 (20–43 GHz) | 3.1–3.7 | 1.7–2.2 | 2.1–2.9 | 2.65/2.2 # | 2.18/2.08 # | 2.38/2.25 # | 1.9-2.9 | 1.35 |

| IP1dB (dBm) | −17.9 (@ 28 GHz) | −19.4 (@ 28 GHz) | −20.6 * (@ 39 GHz) | −23 to −18.5 | −20.4 to −27 | −23 * (@ 22 GHz) | −24 * (@ 22 GHz) | −3 (@ 28 GHz) | −10.2 (@ 28 GHz) | −21 (@ 26 GHz) | −13 (@ 20 GHz) | −7.9 (@ 28 GHz) |

| IIP3 (dBm) | −8.5 | −10.0 | −11.0 | −13.4 to −8.9 * | −13.2 to −19 | −13.4 (@ 22 GHz) | −14.4 (@ 22 GHz) | 7.5 (@ 28 GHz) | 2.6 (@ 28 GHz) | −10.4 (@ 26 GHz) | −3.6 (@ 20 GHz) | 1.4 (@ 28 GHz) |

| Power (mW) | 15.8 | 25.5 | 17 | 20.5 | 17.3 | 5.6 | 6/15 | 3.2/9.6 | 5.5/20 | 7.8 | 13 | |

| Core area (mm2) | 0.24 | 0.38 | 0.16 | 0.21 | 0.05 | 0.05 | 0.12 | 0.19 | 0.19 | 0.03 | 0.12 | |

| FOM | 18.9 | 21.7 | 19.7 | 23.0 | 20.8 | 26.3 | 29.2 | 14.7/11.2 | 30.2/23.8 | 25.3/17.8 | 26.4 | 23.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ouyang, L.-W.; Mayeda, J.C.; Sweeney, C.; Lie, D.Y.C.; Lopez, J. A Broadband Millimeter-Wave 5G Low Noise Amplifier Design in 22 nm Fully Depleted Silicon-on-Insulator (FD-SOI) CMOS. Appl. Sci. 2024, 14, 3080. https://doi.org/10.3390/app14073080

Ouyang L-W, Mayeda JC, Sweeney C, Lie DYC, Lopez J. A Broadband Millimeter-Wave 5G Low Noise Amplifier Design in 22 nm Fully Depleted Silicon-on-Insulator (FD-SOI) CMOS. Applied Sciences. 2024; 14(7):3080. https://doi.org/10.3390/app14073080

Chicago/Turabian StyleOuyang, Liang-Wei, Jill C. Mayeda, Clint Sweeney, Donald Y. C. Lie, and Jerry Lopez. 2024. "A Broadband Millimeter-Wave 5G Low Noise Amplifier Design in 22 nm Fully Depleted Silicon-on-Insulator (FD-SOI) CMOS" Applied Sciences 14, no. 7: 3080. https://doi.org/10.3390/app14073080

APA StyleOuyang, L.-W., Mayeda, J. C., Sweeney, C., Lie, D. Y. C., & Lopez, J. (2024). A Broadband Millimeter-Wave 5G Low Noise Amplifier Design in 22 nm Fully Depleted Silicon-on-Insulator (FD-SOI) CMOS. Applied Sciences, 14(7), 3080. https://doi.org/10.3390/app14073080