Characterization of Trap States in AlGaN/GaN MIS-High-Electron-Mobility Transistors under Semi-on-State Stress

Abstract

1. Introduction

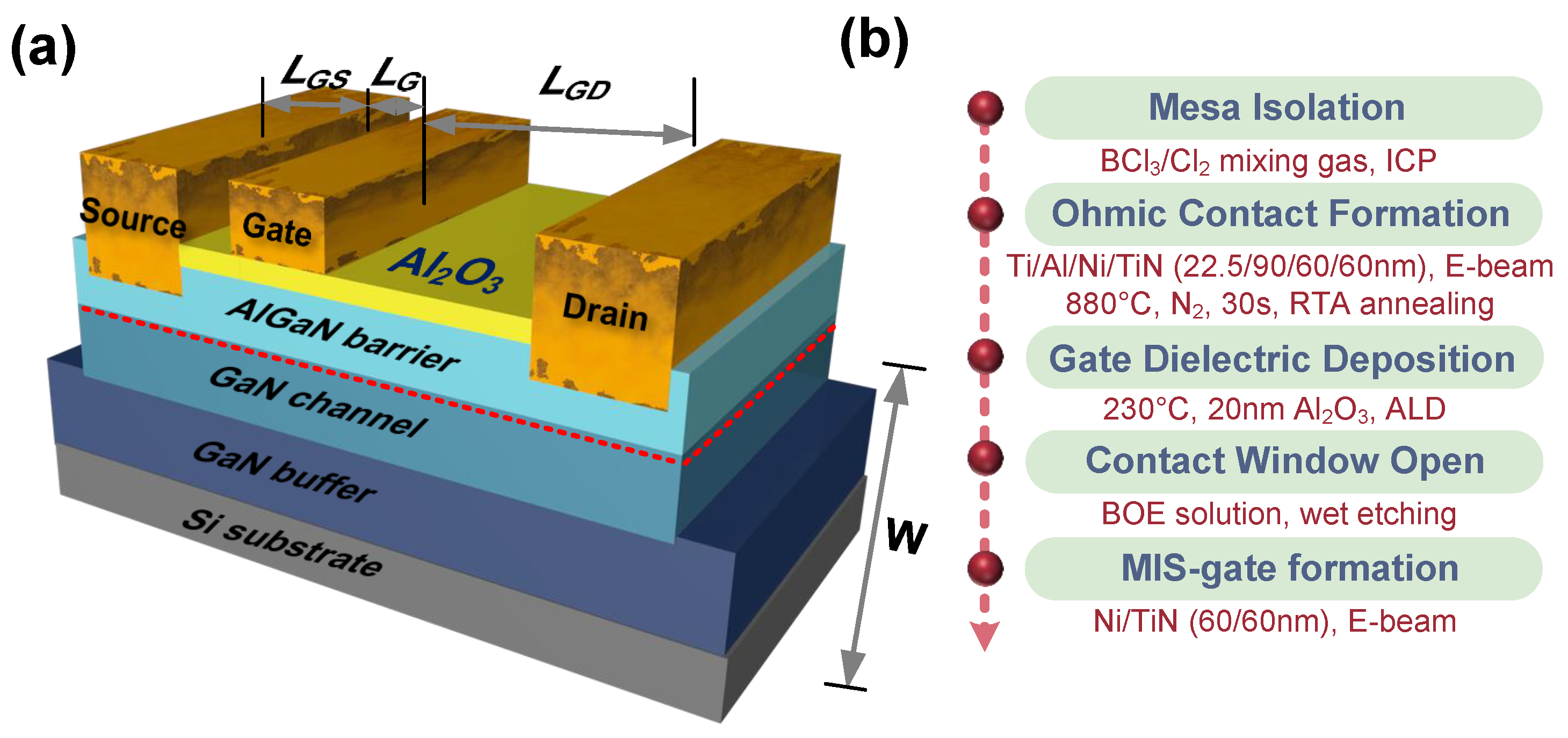

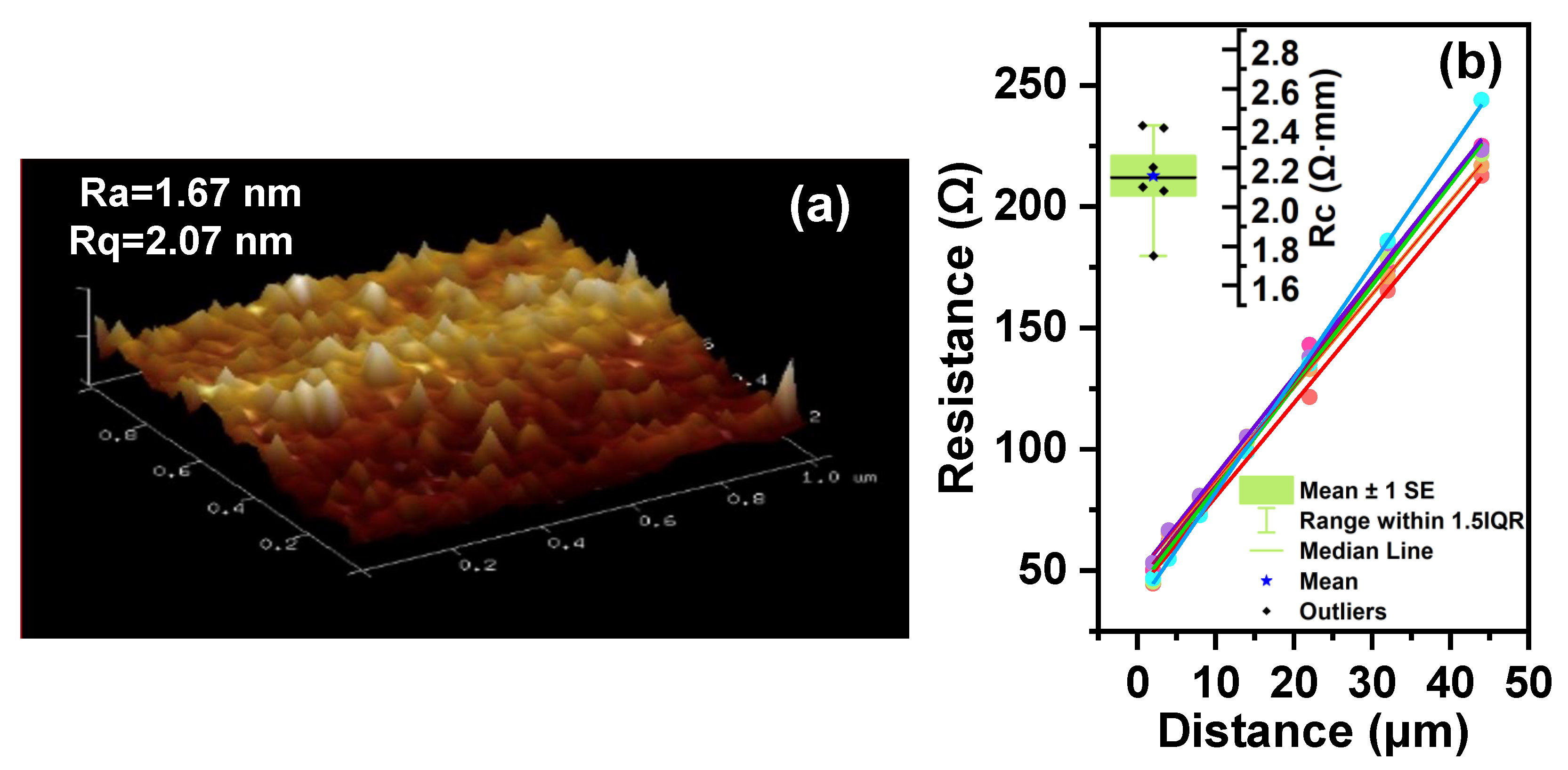

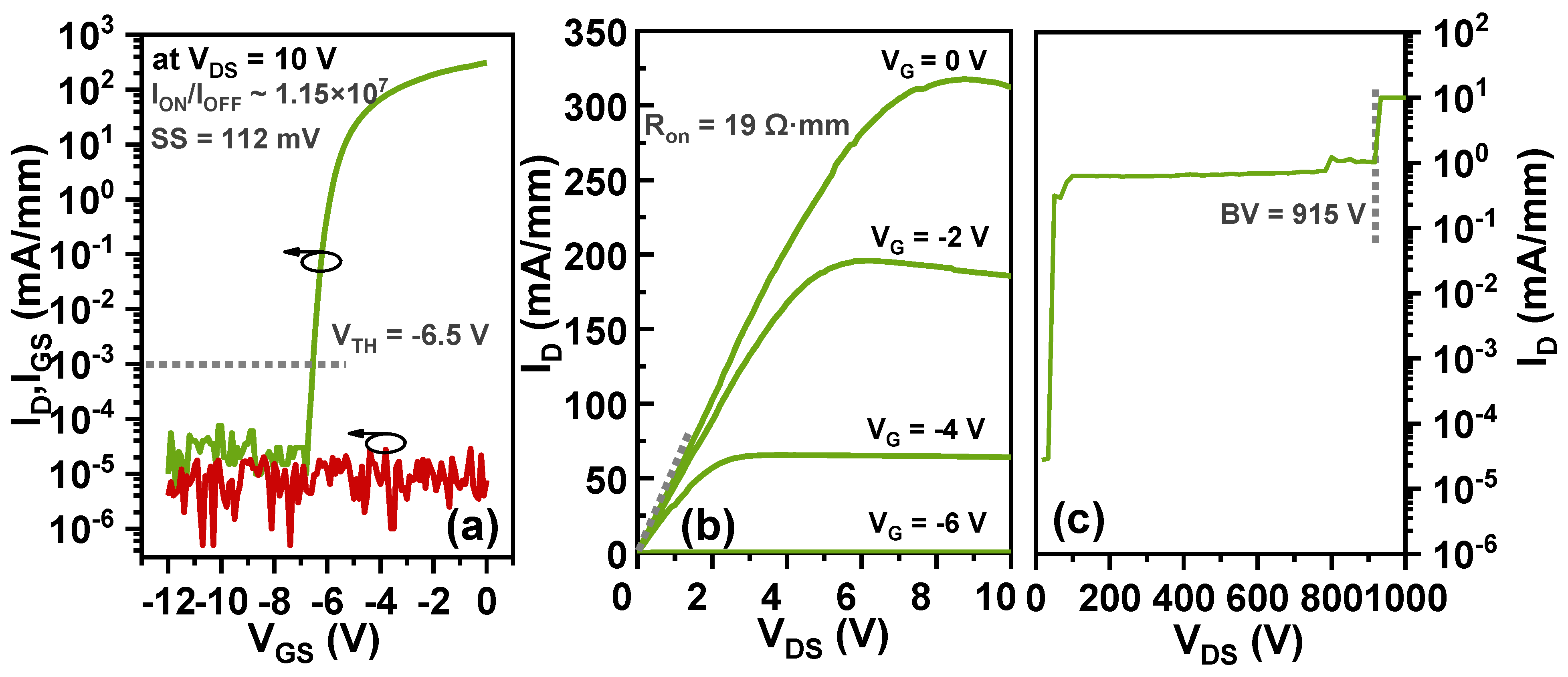

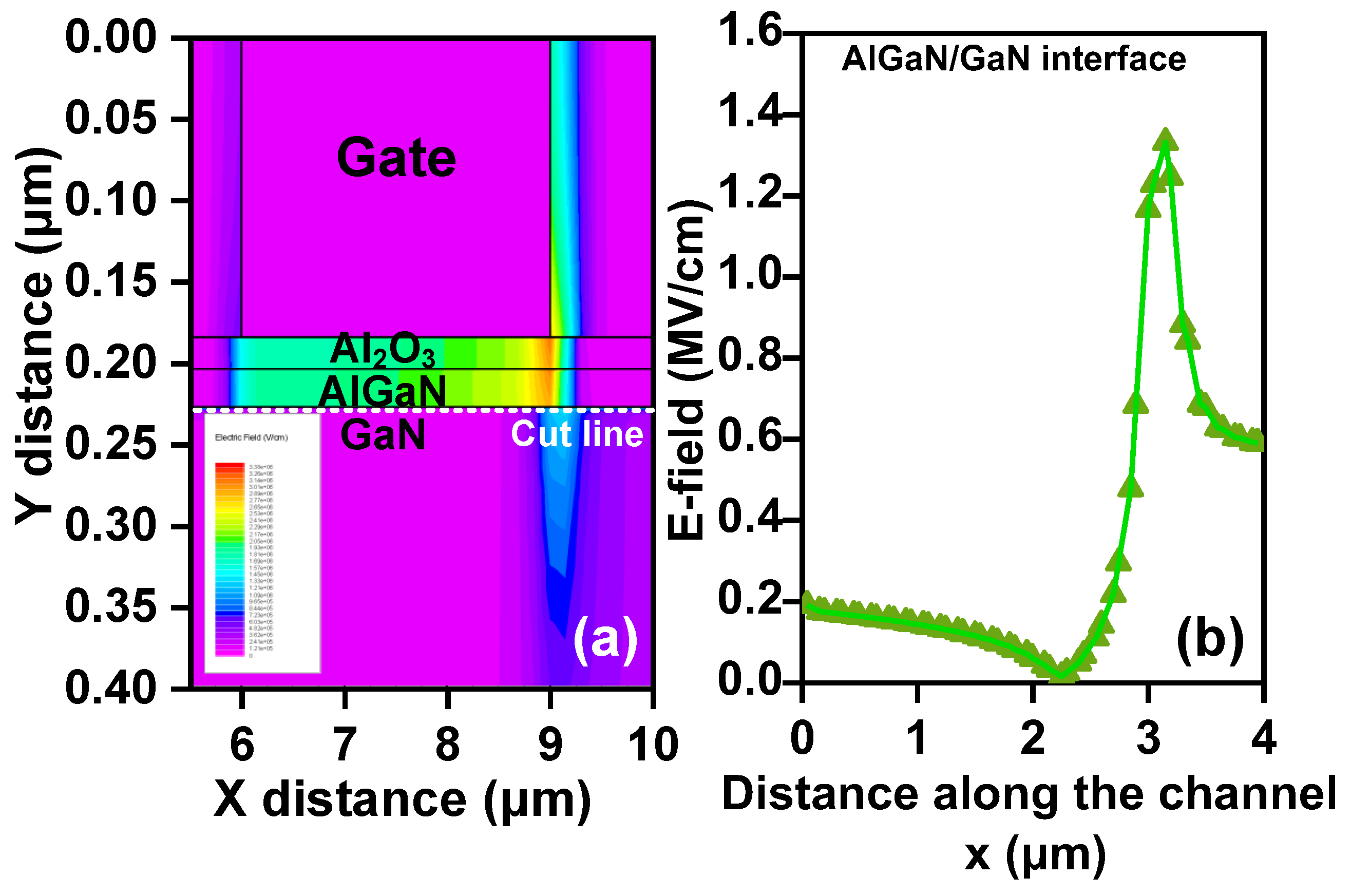

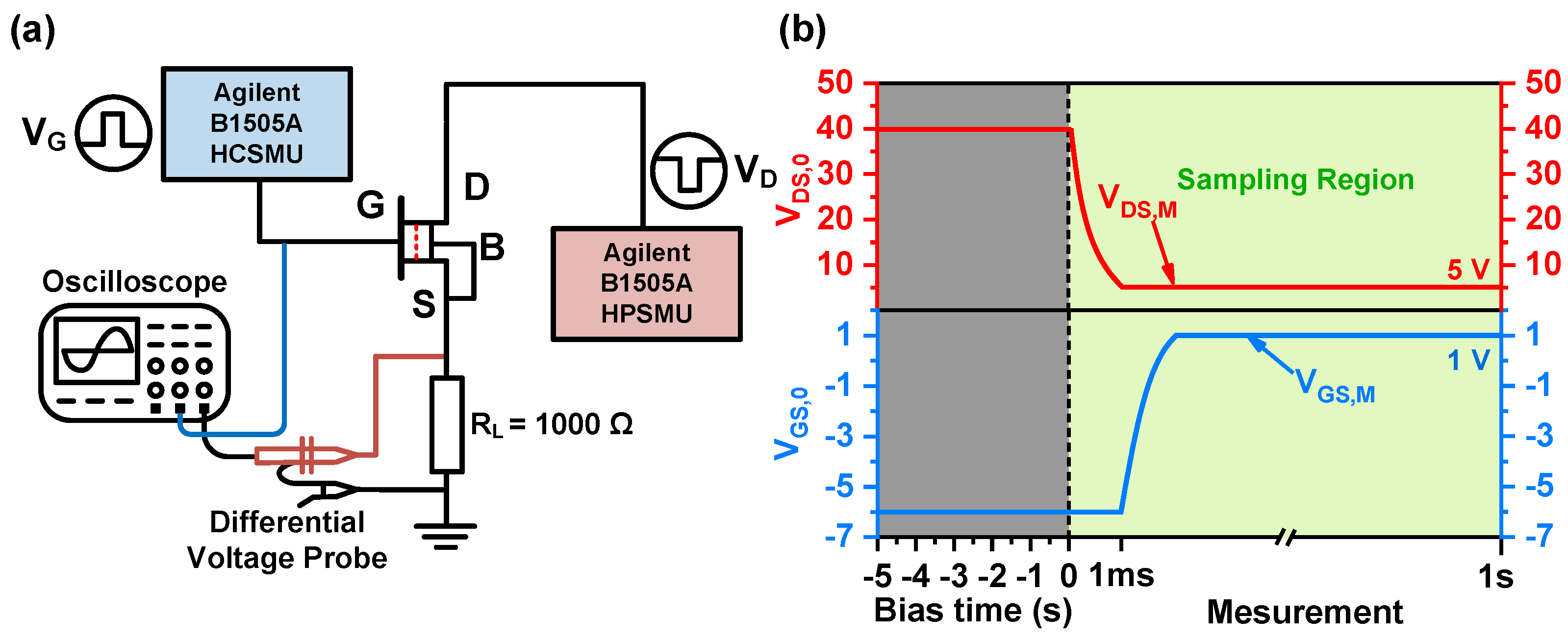

2. Device Fabrication and Characterization

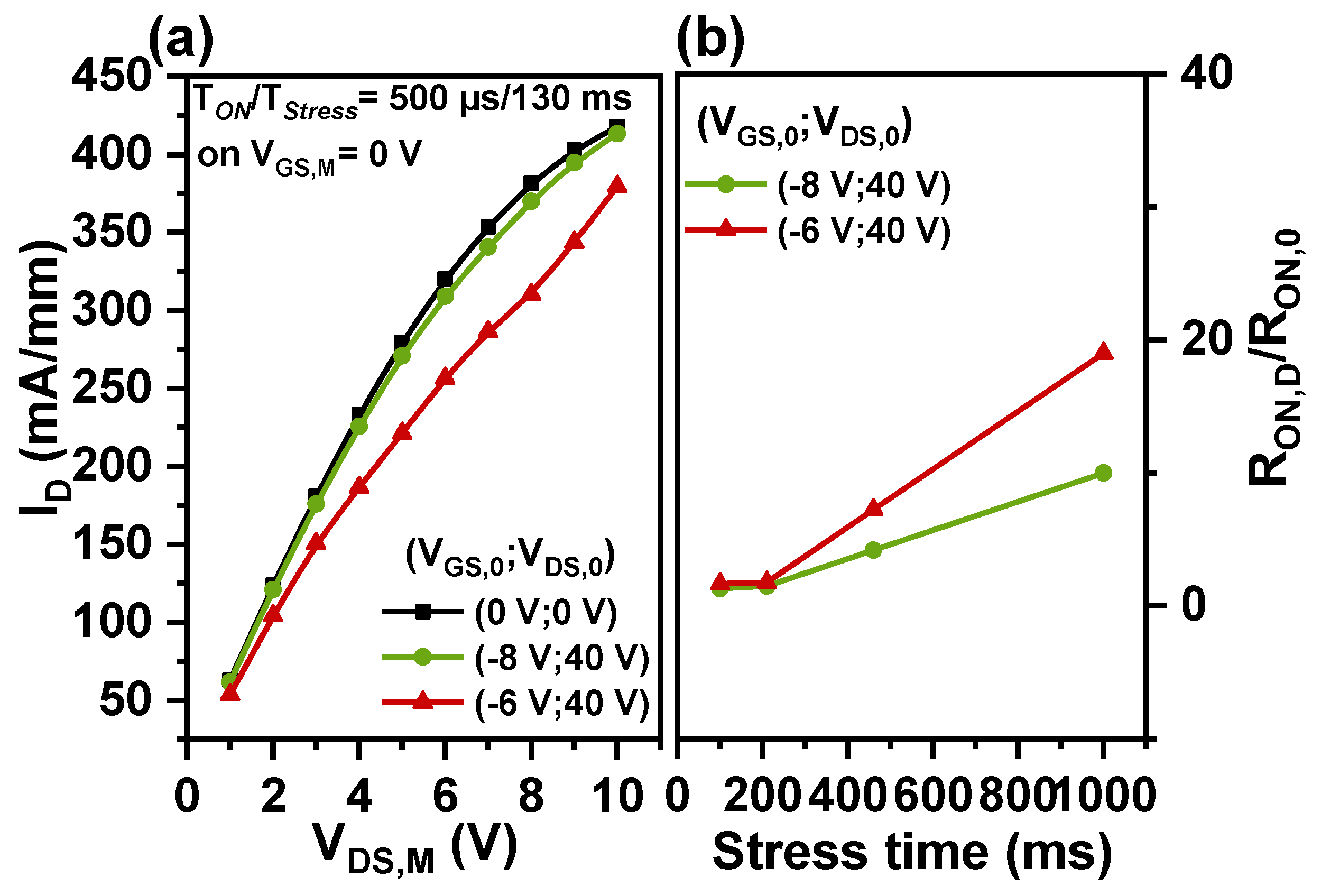

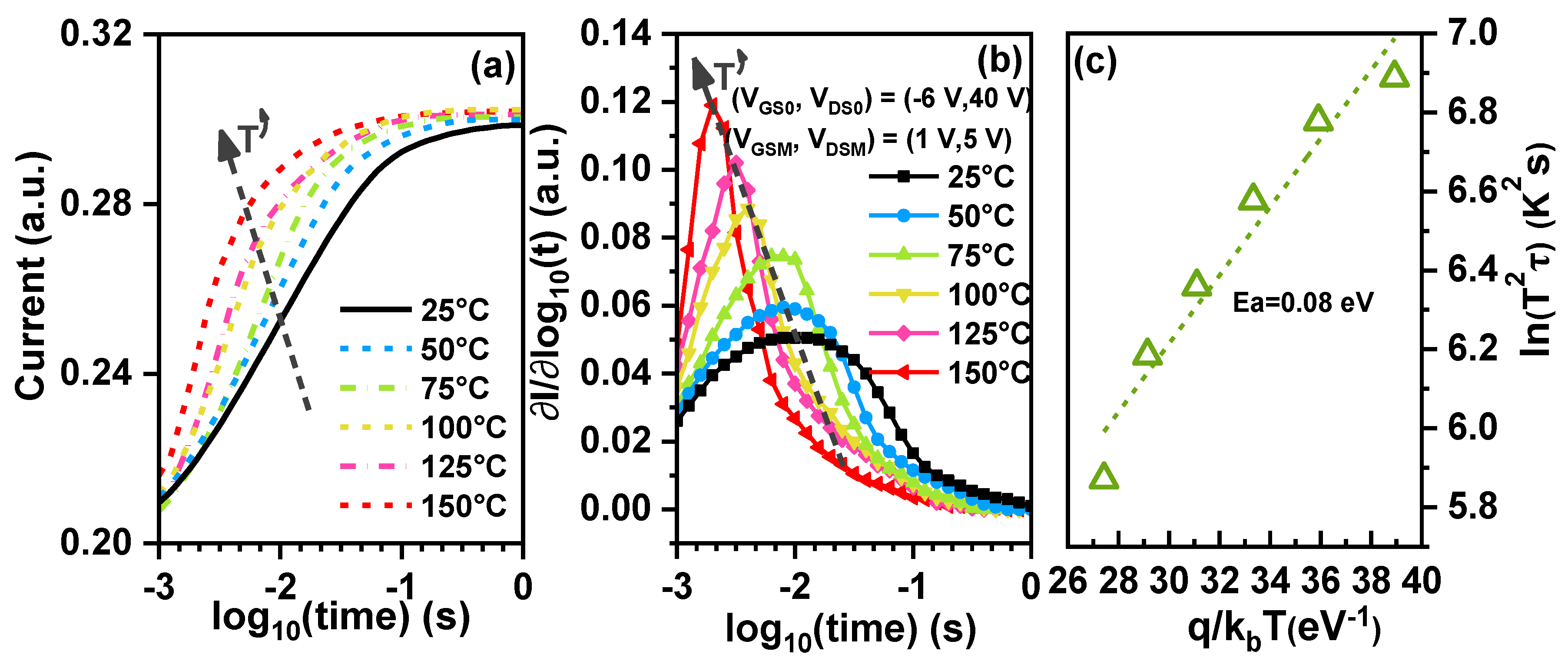

3. Current Collapse Results

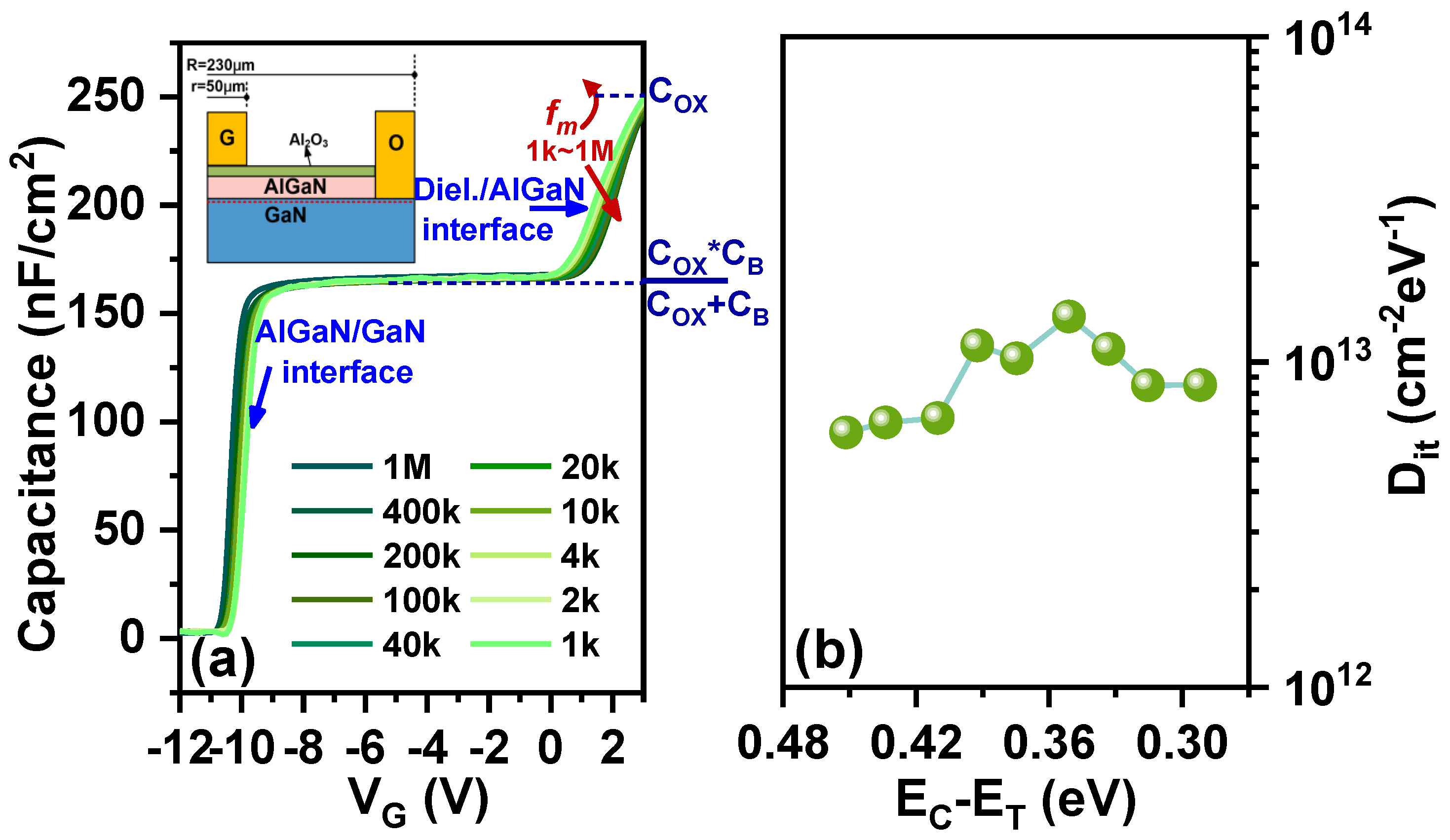

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Stradiotto, R.; Pobegen, G.; Ostermaier, C.; Waltl, M.; Grill, A.; Grasser, T. Characterization of Interface Defects With Distributed Activation Energies in GaN-Based MIS-HEMTs. IEEE Trans. Electron Devices 2017, 64, 1045–1052. [Google Scholar] [CrossRef]

- Hashizume, T.; Ootomo, S.; Hasegawa, H. Suppression of Current Collapse in Insulated Gate AlGaN/GaN Heterostructure Field-Effect Transistors Using Ultrathin Al2O3 Dielectric. Appl. Phys. Lett. 2003, 83, 2952–2954. [Google Scholar] [CrossRef]

- Wang, H.C.; Hsieh, T.E.; Lin, Y.C.; Luc, Q.H.; Liu, S.C.; Wu, C.H.; Dee, C.F.; Majlis, B.Y.; Chang, E.Y. AlGaN/GaN MIS-HEMTs With High Quality ALD-Al2O3 Gate Dielectric Using Water and Remote Oxygen Plasma As Oxidants. IEEE J. Electron Devices Soc. 2018, 6, 110–115. [Google Scholar] [CrossRef]

- Anand, M.J.; Ng, G.I.; Vicknesh, S.; Arulkumaran, S.; Ranjan, K. Reduction of Current Collapse in AlGaN/GaN MIS-HEMT with Bilayer SiN/Al2O3 Dielectric Gate Stack. Phys. Status Solidi C 2013, 10, 1421–1425. [Google Scholar] [CrossRef]

- Shen, L.; Zhang, D.; Cheng, X.; Zheng, L.; Xu, D.; Wang, Q.; Li, J.; Cao, D.; Yu, Y. Performance Improvement and Current Collapse Suppression of Al2O3/AlGaN/GaN HEMTs Achieved by Fluorinated Graphene Passivation. IEEE Electron Device Lett. 2017, 38, 596–599. [Google Scholar] [CrossRef]

- Filatova, E.O.; Konashuk, A.S. Interpretation of the Changing the Band Gap of Al2O3 Depending on Its Crystalline Form: Connection with Different Local Symmetries. J. Phys. Chem. C 2015, 119, 20755–20761. [Google Scholar] [CrossRef]

- Hashizume, T.; Nishiguchi, K.; Kaneki, S.; Kuzmik, J.; Yatabe, Z. State of the Art on Gate Insulation and Surface Passivation for GaN-Based Power HEMTs. Mater. Sci. Semicond. Process. 2018, 78, 85–95. [Google Scholar] [CrossRef]

- Lossy, R.; Gargouri, H.; Arens, M.; Würfl, J. Gallium Nitride MIS-HEMT Using Atomic Layer Deposited Al2O3 as Gate Dielectric. J. Vac. Sci. Technol. A 2013, 31, 01A140. [Google Scholar] [CrossRef]

- Low, R.S.; Chen, C.-Y.; Su, M.-H.; Lin, H.-T.; Chang, C.-Y. GaN-Based MIS-HEMTs with Al2O3 Dielectric Deposited by Low-Cost and Environmental-Friendly Mist-CVD Technique. Appl. Phys. Express 2021, 14, 031004. [Google Scholar] [CrossRef]

- Asubar, J.T.; Kawabata, S.; Tokuda, H.; Yamamoto, A.; Kuzuhara, M. Enhancement-Mode AlGaN/GaN MIS-HEMTs With High VTH and High IDmax Using Recessed-Structure With Regrown AlGaN Barrier. IEEE Electron Device Lett. 2020, 41, 693–696. [Google Scholar] [CrossRef]

- Hatano, M.; Taniguchi, Y.; Kodama, S.; Tokuda, H.; Kuzuhara, M. Reduced Gate Leakage and High Thermal Stability of AlGaN/GaN MIS-HEMTs Using ZrO2/Al2O3 Gate Dielectric Stack. Appl. Phys. Express 2014, 7, 044101. [Google Scholar] [CrossRef]

- Yao, Y.; Huang, S.; Jiang, Q.; Wang, X.; Bi, L.; Shi, W.; Guo, F.; Luan, T.; Fan, J.; Yin, H.; et al. Identification of Semi-ON-State Current Collapse in AlGaN/GaN HEMTs by Drain Current Deep Level Transient Spectroscopy. IEEE Electron Device Lett. 2022, 43, 200–203. [Google Scholar] [CrossRef]

- Modolo, N.; De Santi, C.; Minetto, A.; Sayadi, L.; Sicre, S.; Prechtl, G.; Meneghesso, G.; Zanoni, E.; Meneghini, M. A Physics-Based Approach to Model Hot-Electron Trapping Kinetics in p-GaN HEMTs. IEEE Electron Device Lett. 2021, 42, 673–676. [Google Scholar] [CrossRef]

- Dutta Gupta, S.; Joshi, V.; Chaudhuri, R.R.; Shrivastava, M. Unique Role of Hot-Electron Induced Self-Heating in Determining Gate-Stack Dependent Dynamic RON of AlGaN/GaN HEMTs Under Semi-On State. IEEE Trans. Electron Devices 2022, 69, 6934–6939. [Google Scholar] [CrossRef]

- Fabris, E.; Meneghini, M.; De Santi, C.; Borga, M.; Kinoshita, Y.; Tanaka, K.; Ishida, H.; Ueda, T.; Meneghesso, G.; Zanoni, E. Hot-Electron Trapping and Hole-Induced Detrapping in GaN-Based GITs and HD-GITs. IEEE Trans. Electron Devices 2019, 66, 337–342. [Google Scholar] [CrossRef]

- Chaudhuri, R.R.; Joshi, V.; Gupta, S.D.; Shrivastava, M. On the Channel Hot-Electron’s Interaction With C-Doped GaN Buffer and Resultant Gate Degradation in AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2021, 68, 4869–4876. [Google Scholar] [CrossRef]

- Meneghini, M.; Ronchi, N.; Stocco, A.; Meneghesso, G.; Mishra, U.K.; Pei, Y.; Zanoni, E. Investigation of Trapping and Hot-Electron Effects in GaN HEMTs by Means of a Combined Electrooptical Method. IEEE Trans. Electron Devices 2011, 58, 2996–3003. [Google Scholar] [CrossRef]

- Pan, S.; Feng, S.; Zheng, X.; He, X.; Li, X.; Bai, K. Effects of Temperature and Bias Voltage on Electron Transport Properties in GaN High-Electron-Mobility Transistors. IEEE Trans. Device Mater. Reliab. 2021, 21, 494–499. [Google Scholar] [CrossRef]

- Zhang, Y.; Sun, Z.; Wang, W.; Liang, Y.; Cui, M.; Zhao, Y.; Wen, H.; Liu, W. Low-Resistance Ni/Ag Contacts on GaN-Based p-Channel Heterojunction Field-Effect Transistor. IEEE Trans. Electron Devices 2023, 70, 31–35. [Google Scholar] [CrossRef]

- Bisi, D.; Meneghini, M.; Marino, F.A.; Marcon, D.; Stoffels, S.; Van Hove, M.; Decoutere, S.; Meneghesso, G.; Zanoni, E. Kinetics of Buffer-Related RON Increase in GaN-on-Silicon MIS-HEMTs. IEEE Electron Device Lett. 2014, 35, 1004–1006. [Google Scholar] [CrossRef]

- Zhou, X.; Tan, X.; Lv, Y.; Wang, Y.; Song, X.; Gu, G.; Xu, P.; Guo, H.; Feng, Z.; Cai, S. Dynamic Characteristics of AlGaN/GaN Fin-MISHEMTs With Al2O3 Dielectric. IEEE Trans. Electron Devices 2018, 65, 928–935. [Google Scholar] [CrossRef]

- Hariz, A.J.; Rathmell, J.G.; Varadan, V.K.; Parker, A.E. Circuit Implementation of a Theoretical Model of Trap Centres in GaAs and GaN Devices. In Proceedings of the Microelectronics: Design, Technology, and Packaging III, Canberra, ACT, Australia, 4–7 December 2007. [Google Scholar] [CrossRef]

- Wang, M.; Yan, D.; Zhang, C.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Shen, B. Investigation of Surface- and Buffer-Induced Current Collapse in GaN High-Electron Mobility Transistors Using a Soft Switched Pulsed I-V Measurement. IEEE Electron Device Lett. 2014, 35, 1094–1096. [Google Scholar] [CrossRef]

- Zhang, C.; Wang, M.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Chen, K.J.; Shen, B. Temperature Dependence of the Surface- and Buffer-Induced Current Collapse in GaN High-Electron Mobility Transistors on Si Substrate. IEEE Trans. Electron Devices 2015, 62, 2475–2480. [Google Scholar] [CrossRef]

- Zheng, X.; Feng, S.; Zhang, Y.; He, X.; Wang, Y. A New Differential Amplitude Spectrum for Analyzing the Trapping Effect in GaN HEMTs Based on the Drain Current Transient. IEEE Trans. Electron Devices 2017, 64, 1498–1504. [Google Scholar] [CrossRef]

- Wu, J. Nitride Based Metal Insulator Semiconductor Heterostructure Material and Device Design and Characterization. Ph.D. Dissertation, University of California, Los Angeles, CA, USA, 2014. Available online: https://escholarship.org/uc/item/3zr5s480 (accessed on 18 September 2024).

- Shu, Y.; Shenghou, L.; Yunyou, L.; Cheng, L.; Chen, K.J. AC Capacitance Techniques for Interface Trap Analysis in GaN-Based Buried-Channel MIS-HEMTs. IEEE Trans. Electron Devices 2015, 62, 1870–1878. [Google Scholar] [CrossRef]

- Cai, Y.; Liu, W.; Cui, M.; Sun, R.; Liang, Y.C.; Wen, H.; Yang, L.; Supardan, S.N.; Mitrovic, I.Z.; Taylor, S.; et al. Effect of surface treatment on electrical properties of GaN metal–insulator–semiconductor devices with Al2O3 gate dielectric. Jpn. J. Appl. Phys. 2020, 59, 041001. [Google Scholar] [CrossRef]

- Matys, M.; Stoklas, R.; Kuzmik, J.; Adamowicz, B.; Yatabe, Z.; Hashizume, T. Characterization of capture cross sections of interface states in dielectric/III-nitride heterojunction structures. J. Appl. Phys. 2016, 119, 205304. [Google Scholar] [CrossRef]

- Rocha, P.F.P.P. Optimization of Dielectric/GaN Interface for MIS Gate Power Devices. Ph.D. Thesis, Université Grenoble Alpes, Grenoble, France, 2024. Available online: https://theses.hal.science/tel-04496081 (accessed on 18 September 2024).

- Liu, S.; Yang, S.; Tang, Z.; Jiang, Q.; Liu, C.; Wang, M.; Shen, B.; Chen, K.J. Interface/border trap characterization of Al2O3/AlN/GaN metal-oxide-semiconductor structures with an AlN interfacial layer. Appl. Phys. Lett. 2015, 106, 051605. [Google Scholar] [CrossRef]

- Huang, S.; Jiang, Q.; Yang, S.; Tang, Z.; Chen, K.J. Mechanism of PEALD-Grown AlN Passivation for AlGaN/GaN HEMTs: Compensation of Interface Traps by Polarization Charges. IEEE Electron Device Lett. 2013, 34, 193–195. [Google Scholar] [CrossRef]

- Yang, S.; Liu, S.; Liu, C.; Lu, Y.; Chen, K.J. Nitridation interfacial-layer technology for enhanced stability in GaN-based power devices. In Proceedings of the 2015 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Sendai, Japan, 26–28 August 2015. [Google Scholar] [CrossRef]

- Cai, Y.; Wang, Y.; Liang, Y.; Zhang, Y.; Liu, W.; Wen, H.; Mitrovic, I.Z.; Zhao, C. Effect of High-k Passivation Layer on High Voltage Properties of GaN Metal-Insulator-Semiconductor Devices. IEEE Access 2020, 8, 95642–95649. [Google Scholar] [CrossRef]

- Zhu, J.J.; Ma, X.H.; Xie, Y.; Hou, B.; Chen, W.W.; Zhang, J.C.; Hao, Y. Improved Interface and Transport Properties of AlGaN/GaN MIS-HEMTs with PEALD-Grown AlN Gate Dielectric. IEEE Trans. Electron Devices 2015, 62, 512–518. [Google Scholar] [CrossRef]

- Mehari, S.; Gavrilov, A.; Eizenberg, M.; Ritter, D. Density of Traps at the Insulator/III-N Interface of GaN Heterostructure Field-Effect Transistors Obtained by Gated Hall Measurements. IEEE Electron Device Lett. 2015, 36, 893–895. [Google Scholar] [CrossRef]

- Sun, H.; Wang, M.; Yin, R.; Chen, J.; Xue, S.; Luo, J.; Hao, Y.; Chen, D. Investigation of the Trap States and VTH Instability in LPCVD Si3N4/AlGaN/GaN MIS-HEMTs with an In-Situ Si3N4 Interfacial Layer. IEEE Trans. Electron Devices 2019, 66, 3290–3295. [Google Scholar] [CrossRef]

- Lin, Y.C.; Huang, Y.X.; Huang, G.N.; Wu, C.H.; Yao, J.N.; Chu, C.M.; Chang, S.; Hsu, C.C.; Lee, J.H.; Kakushima, K.; et al. Enhancement-Mode GaN MIS-HEMTs with LaHfOx Gate Insulator for Power Application. IEEE Electron Device Lett. 2017, 38, 1101–1104. [Google Scholar] [CrossRef]

- Ranjan, K.; Arulkumaran, S.; Ng, G.I.; Sandupatla, A. Low interface trap density in AlGaN/GaN Metal-Insulator-Semiconductor High-Electron-Mobility Transistors on CVD-Diamond. In Proceedings of the 2020 4th IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Penang, Malaysia, 6–21 April 2020. [Google Scholar] [CrossRef]

- Meneghini, M.; Rossetto, I.; Bisi, D.; Stocco, A.; Chini, A.; Pantellini, A.; Lanzieri, C.; Nanni, A.; Meneghesso, G.; Zanoni, E. Buffer Traps in Fe-Doped AlGaN/GaN HEMTs: Investigation of the Physical Properties Based on Pulsed and Transient Measurements. IEEE Trans. Electron Devices 2014, 61, 4070–4077. [Google Scholar] [CrossRef]

- Liang, Y.; Zhang, Y.; He, X.; Zhao, Y.; Cui, M.; Wen, H.; Liu, W. Study of Drain-current Collapse in AlGaN/GaN MIS-HEMTs with Different Gate Lengths. In Proceedings of the 2022 IEEE 16th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Nanjing, China, 25–28 October 2022. [Google Scholar] [CrossRef]

| Insulator | Surface Treatment | Test Method | Interface Density (eV−1cm−2) | Energy Level (eV) |

|---|---|---|---|---|

| Al2O3 [28] | O2 plasma | Multi-frequency capacitance–voltage | 9.1 × ~4.8 × | 0.28 to 0.47 |

| Al2O3 [28] | Octadecanethiol | Multi-frequency capacitance–voltage | 6.1 × ~3 × | 0.28 to 0.47 |

| Al2O3 [33] | N2 plasma | Multi-frequency capacitance–voltage | 6 × ~6 × | 0.24 to 0.78 |

| Al2O3 (This work) | HCl solution | Multi-frequency capacitance–voltage | 1.37 × ~6.07 × | 0.29 to 0.45 |

| ZrO2 [34] | HCl solution | Multi-frequency capacitance–voltage | 4.7 × ~9.4 × | 0.28 to 0.47 |

| AlN [35] | In situ low-damage plasma | C-V hysteresis | 2.0 × | No mention |

| SiNx [36] | HF: H2O solution | Gated Hall method | 2.3 × ~4 × | 1.2 to 2.3 |

| S3N4 [37] | HCl solution | High-frequency capacitance–voltage | 1.4 × ~2.8 × | 0.53 to 0.71 |

| LaHfOx [38] | Rapid thermal annealing at the gate recess region | C-V hysteresis | 7.5 × | No mention |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liang, Y.; Duan, J.; Zhang, P.; Low, K.L.; Zhang, J.; Liu, W. Characterization of Trap States in AlGaN/GaN MIS-High-Electron-Mobility Transistors under Semi-on-State Stress. Nanomaterials 2024, 14, 1529. https://doi.org/10.3390/nano14181529

Liang Y, Duan J, Zhang P, Low KL, Zhang J, Liu W. Characterization of Trap States in AlGaN/GaN MIS-High-Electron-Mobility Transistors under Semi-on-State Stress. Nanomaterials. 2024; 14(18):1529. https://doi.org/10.3390/nano14181529

Chicago/Turabian StyleLiang, Ye, Jiachen Duan, Ping Zhang, Kain Lu Low, Jie Zhang, and Wen Liu. 2024. "Characterization of Trap States in AlGaN/GaN MIS-High-Electron-Mobility Transistors under Semi-on-State Stress" Nanomaterials 14, no. 18: 1529. https://doi.org/10.3390/nano14181529

APA StyleLiang, Y., Duan, J., Zhang, P., Low, K. L., Zhang, J., & Liu, W. (2024). Characterization of Trap States in AlGaN/GaN MIS-High-Electron-Mobility Transistors under Semi-on-State Stress. Nanomaterials, 14(18), 1529. https://doi.org/10.3390/nano14181529