A Compact 0.73~3.1 GHz CMOS VCO Based on Active-Inductor and Active-Resistor Topology

Abstract

:1. Introduction

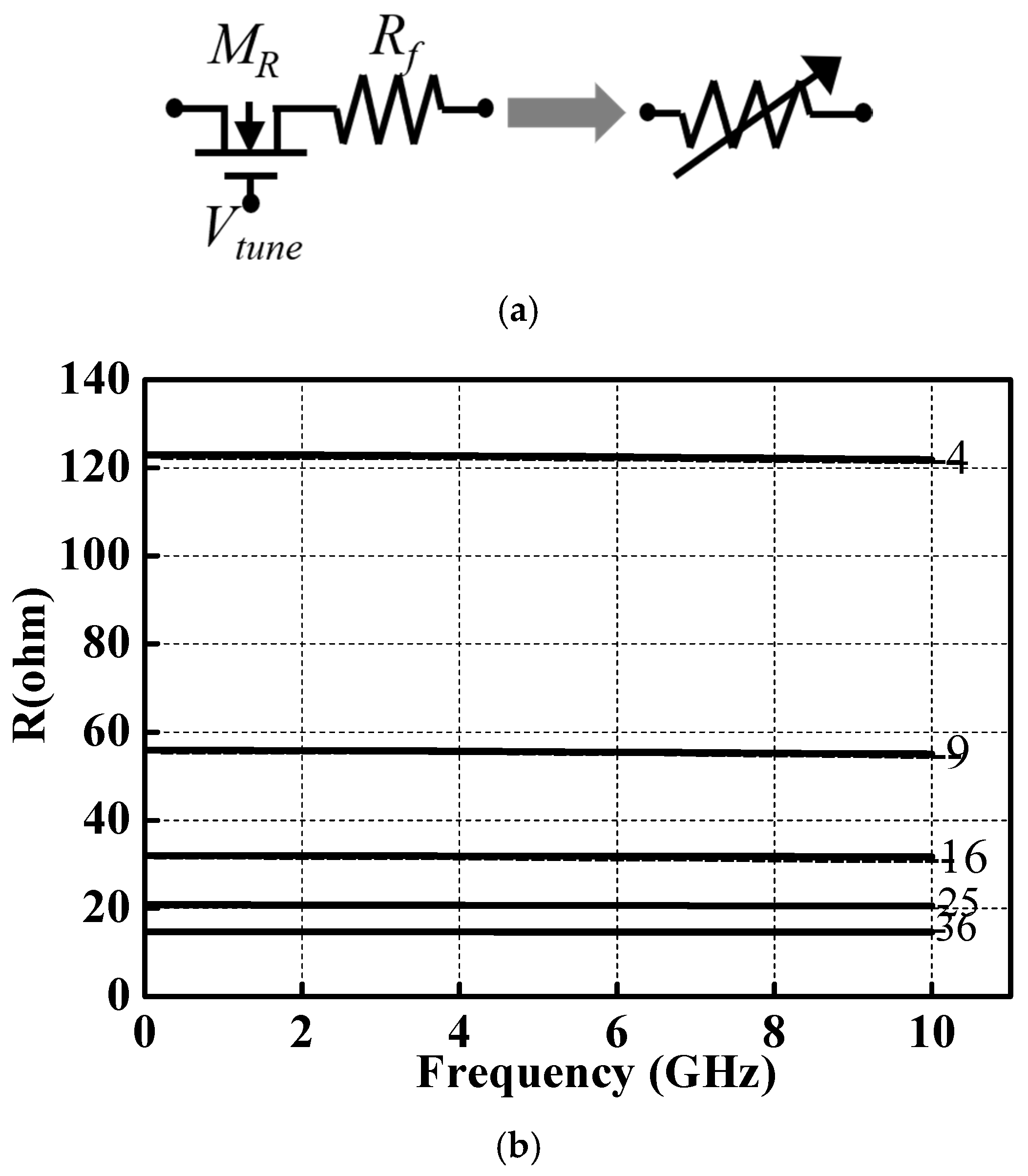

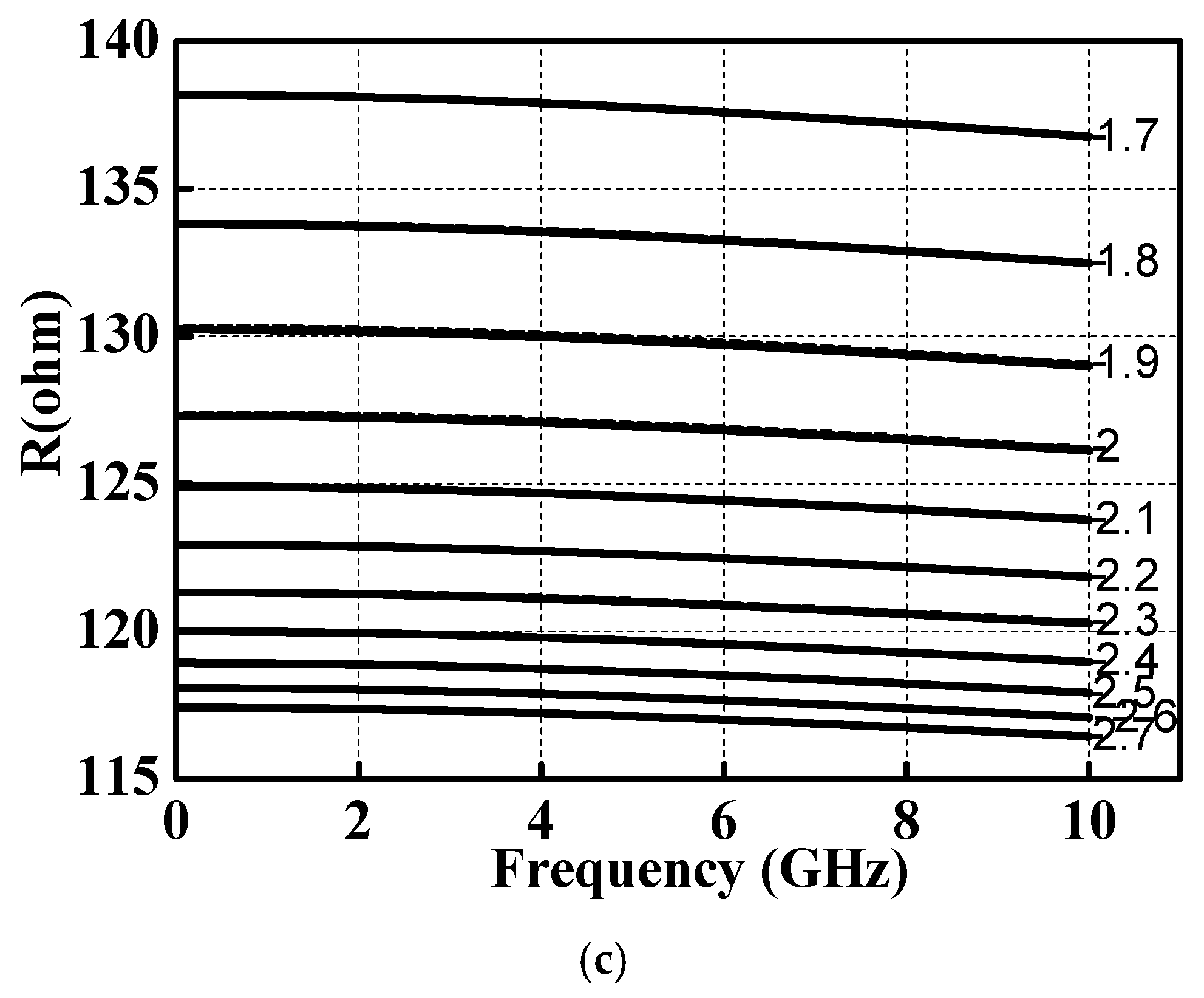

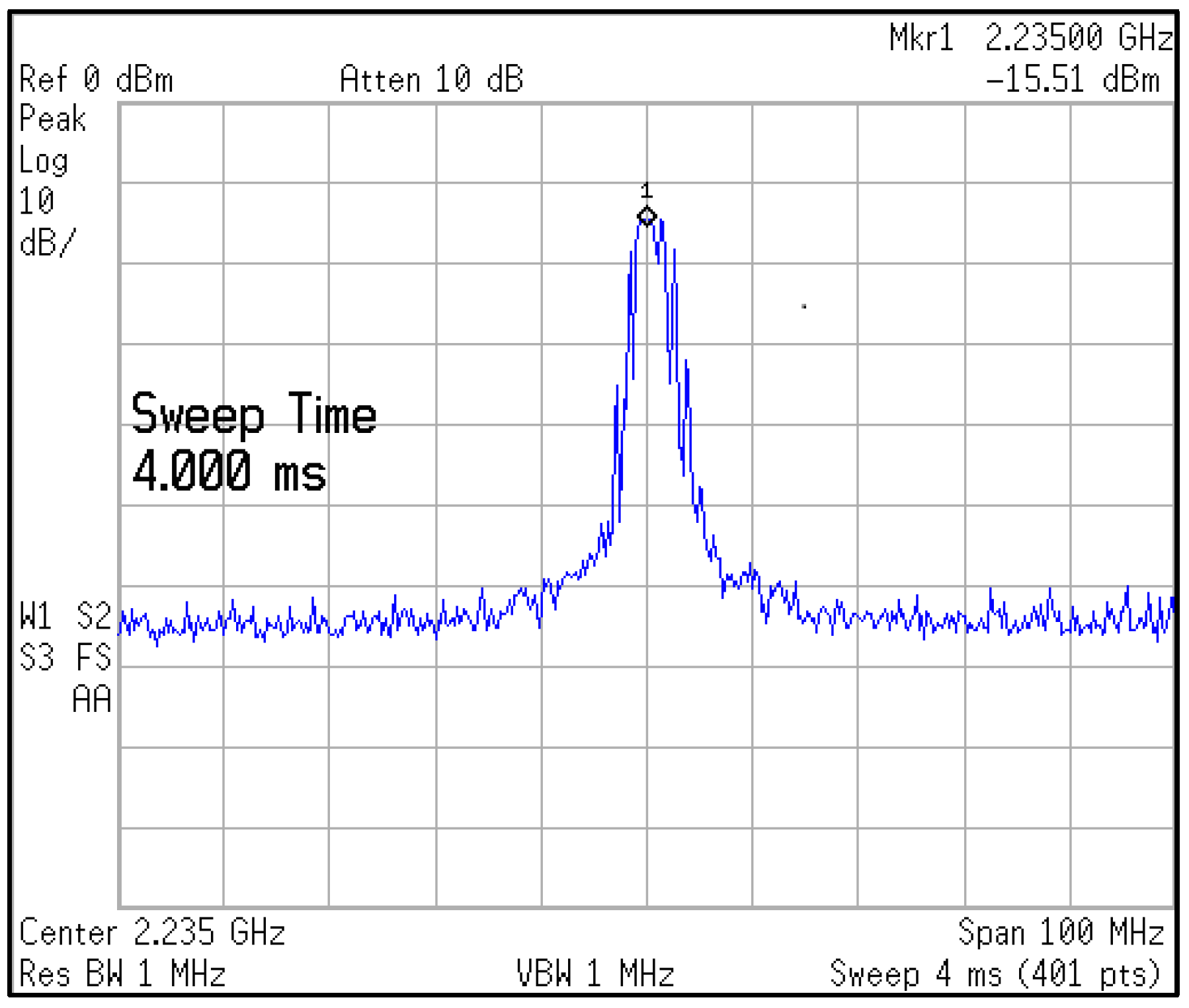

2. Circuit Design and Simulation

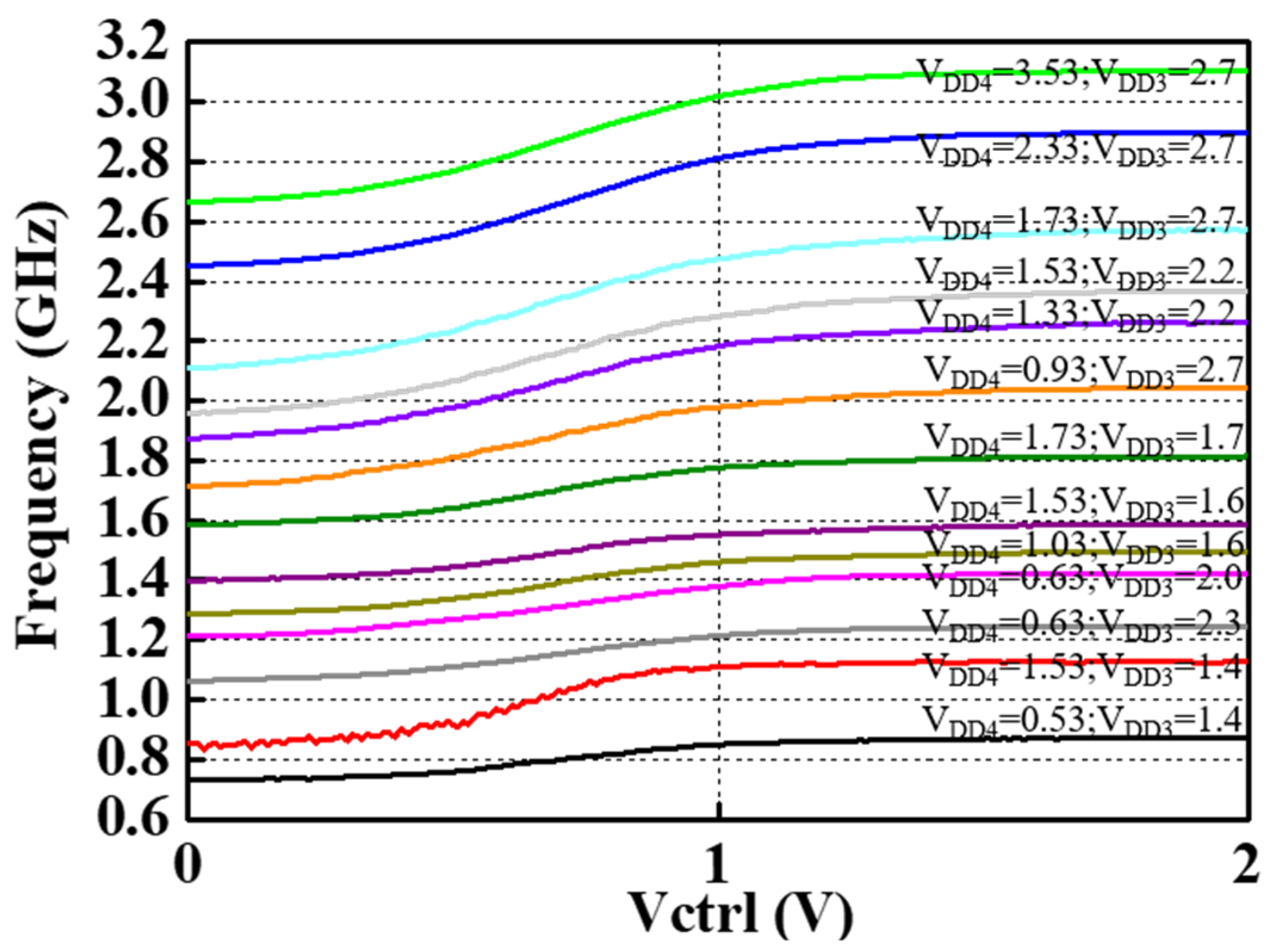

3. Implementation and Measurement

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Mukhopadhyay, R.; Park, Y.; Sen, P.; Srirattana, N.; Lee, J.; Lee, C.-H.; Nuttinck, S.; Joseph, A.; Cressler, J.D.; Laskar, J. Reconfigurable RFICs in Si-based technologies for a compact intelligent RF frontend. IEEE Trans. Microw. Theory Tech. 2005, 53, 81–93. [Google Scholar] [CrossRef]

- Dhamani, N.; Sepidband, P.; Entesari, K. A low phase noise wide-tuning range Class-F VCO based on a dual-mode resonator in 65nm CMOS. In Proceedings of the 2018 IEEE Radio and Wireless Symposium (RWS), Anaheim, CA, USA, 15–18 January 2018; pp. 277–280. [Google Scholar]

- Xu, S.; Zhang, W.; Shen, P.; Xie, H.; Jin, D.; Zhang, Y.; Yang, X.; Zhang, Z. A wide tuning range low Kvco and low phase noise VCO. In Proceedings of the 3rd International Conference on Integrated Circuits and Microsystems, Shanghai, China, 24–26 November 2018; pp. 47–50. [Google Scholar]

- Shu, R.; Subramanian, V.; Boeck, G.; Wu, J.; Lu, S. A wideband CMOS voltage-controlled oscillator with switched-capacitor array. In Proceedings of the German Microwave Conference Digest of Papers, Berlin, Germany, 15–17 March 2010; pp. 43–46. [Google Scholar]

- Yang, X.; Uchida, Y.; Xu, K.; Wang, W.; Yoshimasu, T. 2.4 GHz-band ultra-low-voltage Class-C LC-VCO IC in 65 nm CMOS Technology. In Proceedings of the 2013 Asia-Pacific Microwave Conference Proceedings (APMC), Seoul, Republic of Korea, 5–8 November 2013; pp. 325–327. [Google Scholar]

- Jeong, Y.J.; Kim, Y.M.; Chang, H.J. Low-power CMOS VCO with a low-current, high-Q active inductor. IET Microw. Antennas Propag. 2012, 6, 788–792. [Google Scholar] [CrossRef]

- Haddad, F.; Ghorbel, I.; Rahajandraibe, W. Multi-band inductor-less VCO for IoT applications. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Xu, J.; Saavedra, C.E.; Chen, G. An active inductor-based VCO with wide tuning range and high dc-to-RF power efficiency. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 462–466. [Google Scholar] [CrossRef]

- Hammadi, A.B.; Mhiri, M.; Haddad, F.; Saad, S.; Besbes, K. An enhanced design of RF integrated differential active inductor. BioNanoScience 2016, 6, 185–192. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, W.; Shen, P.; Xie, H.; Jin, D.; Xu, S.; Yang, X.; Zhang, Z. A novel LC VCO with high output power and low phase noise using differential active inductor. In Proceedings of the IEEE International Conference on Integrated Circuits and Microsystems (ICICM), Shanghai, China, 24–26 November 2018; pp. 90–93. [Google Scholar]

- Mehrabian, M.; Nabavi, A.; Rashidi, N. A 4-7GHz ultra wideband VCO with tunable active inductor. In Proceedings of the IEEE International Conference on Ultra-Wideband, Hannover, Germany, 10–12 September 2008; pp. 21–24. [Google Scholar]

- Wang, S.; Xiao, C.-Y. A 7/24-GHz CMOS VCO with High Band Ratio Using a Current-Source Switching Topology. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2016, 63, 790–795. [Google Scholar] [CrossRef] [PubMed]

| VDD1 = 1.6 V VDD2 = 0.53 V | VDD3 = 1.4~2.7 V | VDD4 = 0.53~3.53 V | Cvar = 373.9~493.7 fF |

| R1,2 = 900 Ω | R3,4 = 1.5 kΩ | C1,2 = 20.28 fF | C1,2 = 951.6 fF |

| M1,2 W/L (μm) = 16/0.18 | M3,6 W/L (μm) = 64/0.18 | M4,5 W/L (μm) = 4/0.18 | M7,10 W/L (μm) = 2/0.18 |

| M8,9 W/L (μm) = 60/0.18 | M11,12 W/L (μm) = 96/0.18 | M13,14 W/L (μm) = 400/0.18 | M15,16,17,18 W/L (μm) = 14/0.18 |

| Reference | Process (nm) | Topology | fo (GHz) | Tuning Range (%) | PDC (mW) | Pout (dBm) | Phase Noise (dBc/Hz)@1MHz | FOM * (dBc/Hz) | FOMT * (dBc/Hz) | Area (mm2) |

|---|---|---|---|---|---|---|---|---|---|---|

| [6] IET MAP’12 | 180 | Active L | 1.13~2.67 | 81 | 2.2~13 | −14.3 | −82.8~−92.2 | −144.2 | −162.4 | 0.03 |

| [7] ISCAS’17 | 130 | Active L | 1.28~2.6 | 68 | 3.8~4 | N.A. | −81~−87 | −143.8 | −160.5 | 0.0031 |

| [8] TCAS-II’11 | 130 | Active L | 0.83~3.72 | 127 | 8~13 | −0.9 | −104~−109 | −163.4 | −185.5 | 0.108 |

| [10] ** ICICM’18 | 180 | Active and Differential L | 1.13~2.71 | 82.3 | 13.6 | −4.2 | −101~−105 | −157.3 | −175.6 | N.A |

| [11] ** ICUWB’08 | 180 | Active L + Parallel R | 3.8~7.4 | 64.2 | 29.1 | N.A | −75~−92 | −143.8 | −159.9 | N.A |

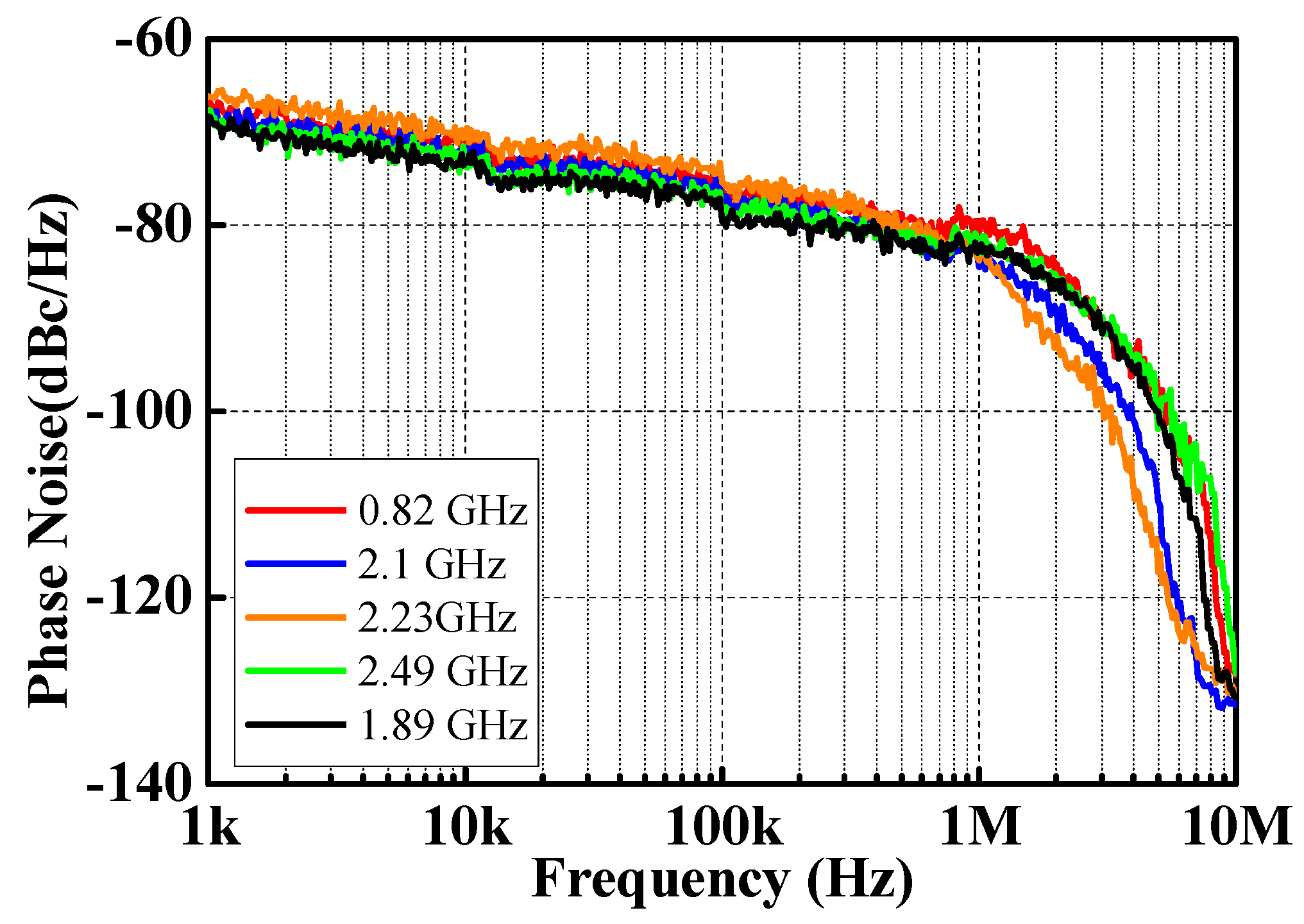

| This work | 180 | Active L + Series R | 0.73~3.1 | 123.8 | 6.8~10.1 | −15.5 | −80.7~−84.5 | −139 | −160.8 | 0.046 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pakasiri, C.; Hsu, K.-C.; Wang, S. A Compact 0.73~3.1 GHz CMOS VCO Based on Active-Inductor and Active-Resistor Topology. J. Low Power Electron. Appl. 2024, 14, 18. https://doi.org/10.3390/jlpea14020018

Pakasiri C, Hsu K-C, Wang S. A Compact 0.73~3.1 GHz CMOS VCO Based on Active-Inductor and Active-Resistor Topology. Journal of Low Power Electronics and Applications. 2024; 14(2):18. https://doi.org/10.3390/jlpea14020018

Chicago/Turabian StylePakasiri, Chatrpol, Ke-Chung Hsu, and Sen Wang. 2024. "A Compact 0.73~3.1 GHz CMOS VCO Based on Active-Inductor and Active-Resistor Topology" Journal of Low Power Electronics and Applications 14, no. 2: 18. https://doi.org/10.3390/jlpea14020018

APA StylePakasiri, C., Hsu, K.-C., & Wang, S. (2024). A Compact 0.73~3.1 GHz CMOS VCO Based on Active-Inductor and Active-Resistor Topology. Journal of Low Power Electronics and Applications, 14(2), 18. https://doi.org/10.3390/jlpea14020018