Predicting the Performance of a 26 GHz Transconductance Modulated Downconversion Mixer as a Function of LO Drive and DC Bias

Abstract

:1. Introduction

1.1. Paper Motivation

1.2. Background

1.3. Paper Contribution & Structure

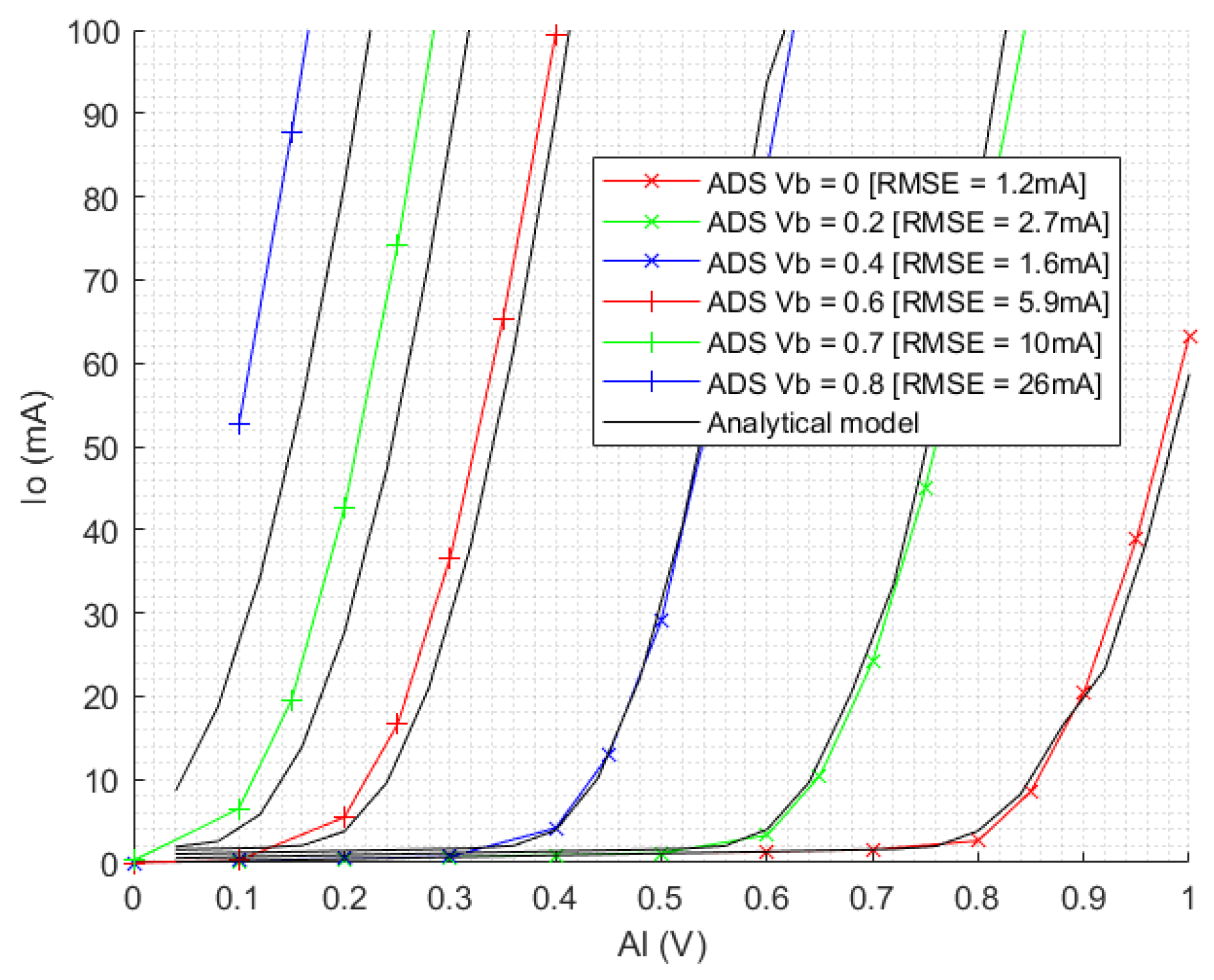

2. Transistor Collector Current Mathematical Models

3. IF Current Mathematical Models

3.1. LO Currents

3.2. Relating AL to Required Port LO Power

- Select a target AL and Vb and let the mathematical model Equation (13) produce the resulting equivalent DC current draw C0k.

- Use C0k and the BJT small-signal S parameters to estimate the base input reflection coefficient Equation (17), with set to −1, representing a collector short circuit to ground at the LO, as required for good mixer operation.

- Use AL as applied to Rp to calculate the RF LO power LOP_b, as would be seen at the base.

- Translate the power LOP_b back to the connector port, accounting for any expected intermediate RF stage insertion losses, due to combiners, etc.

3.3. Extracting the Transconductance Mixing Current

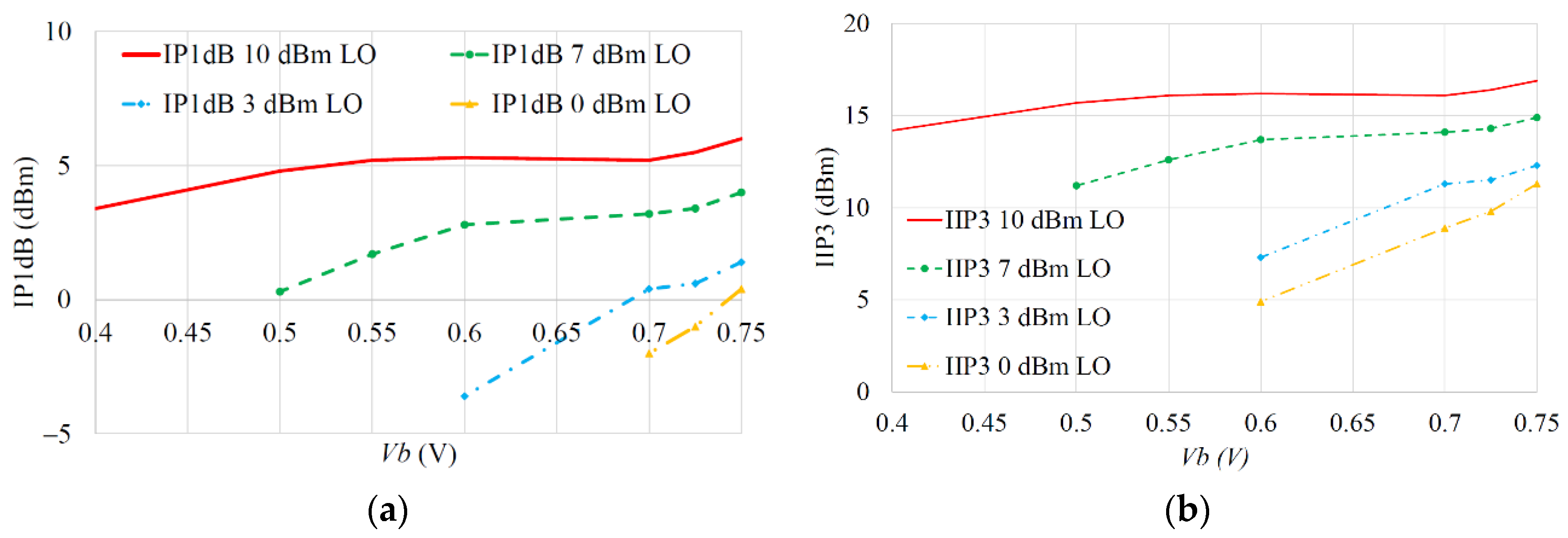

3.4. IP1dB & IIP3 Prediction Models

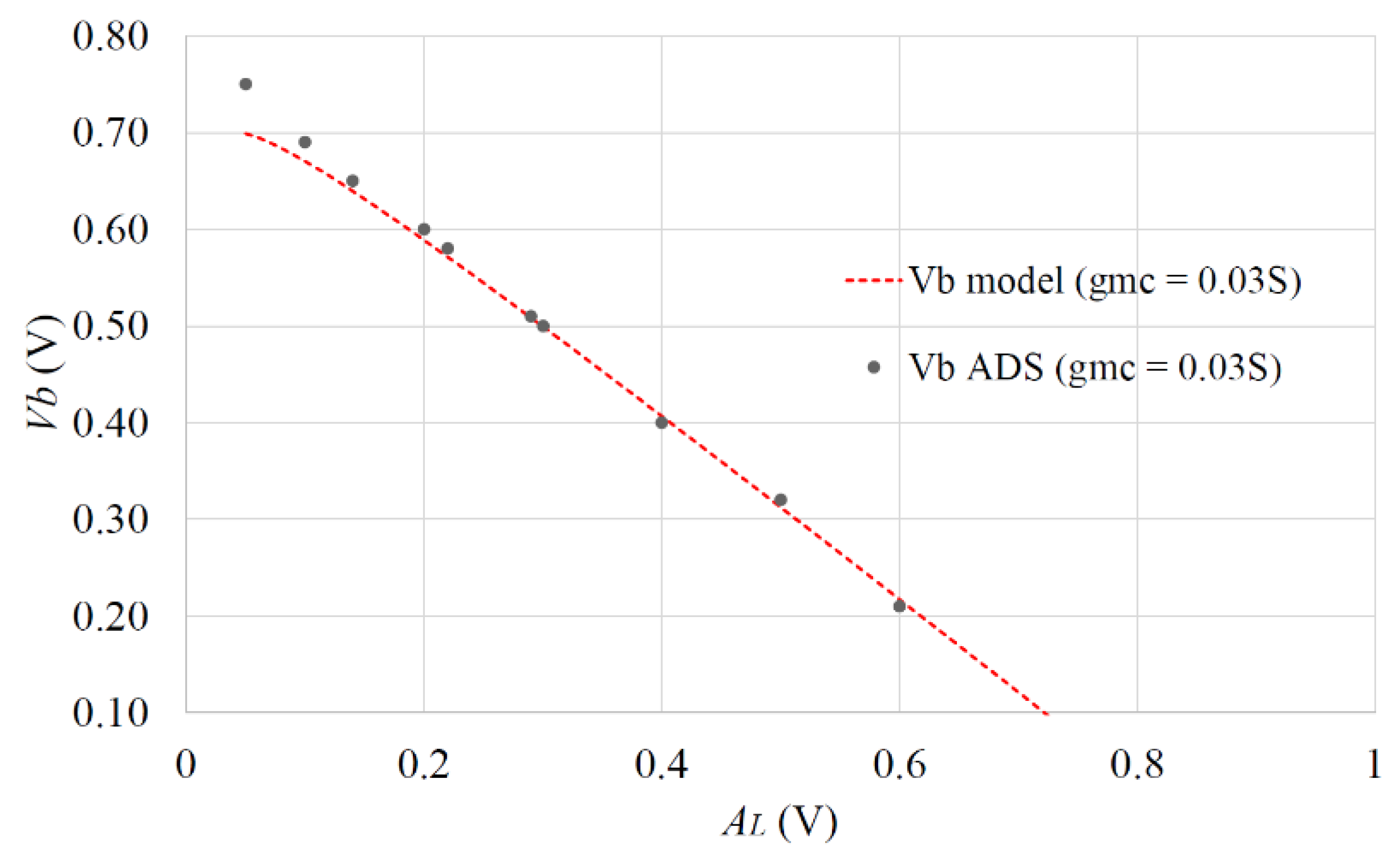

3.5. Selecting Vb for a Fixed AL and Conversion Transconductance

4. Trial Mixer Hardware for Model Validation

5. Comparison between Mathematical Models, Circuit Simulations and Measured PCB

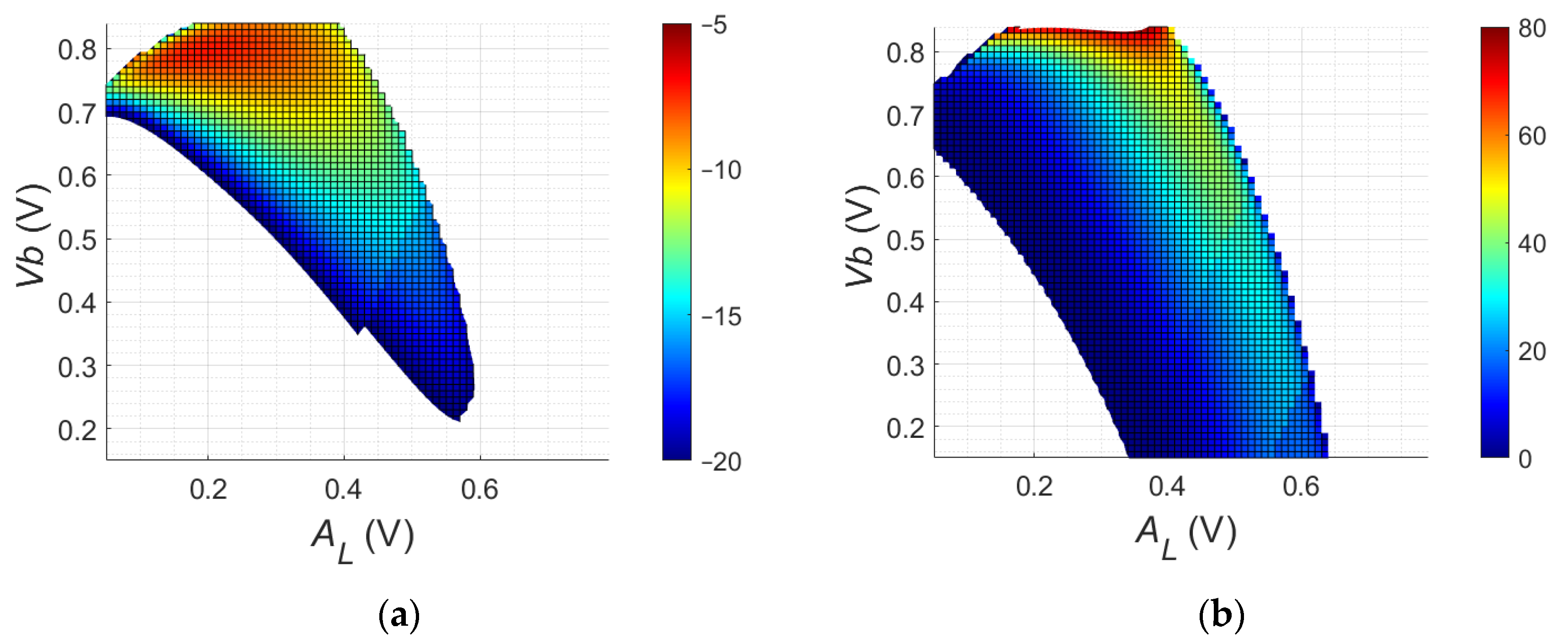

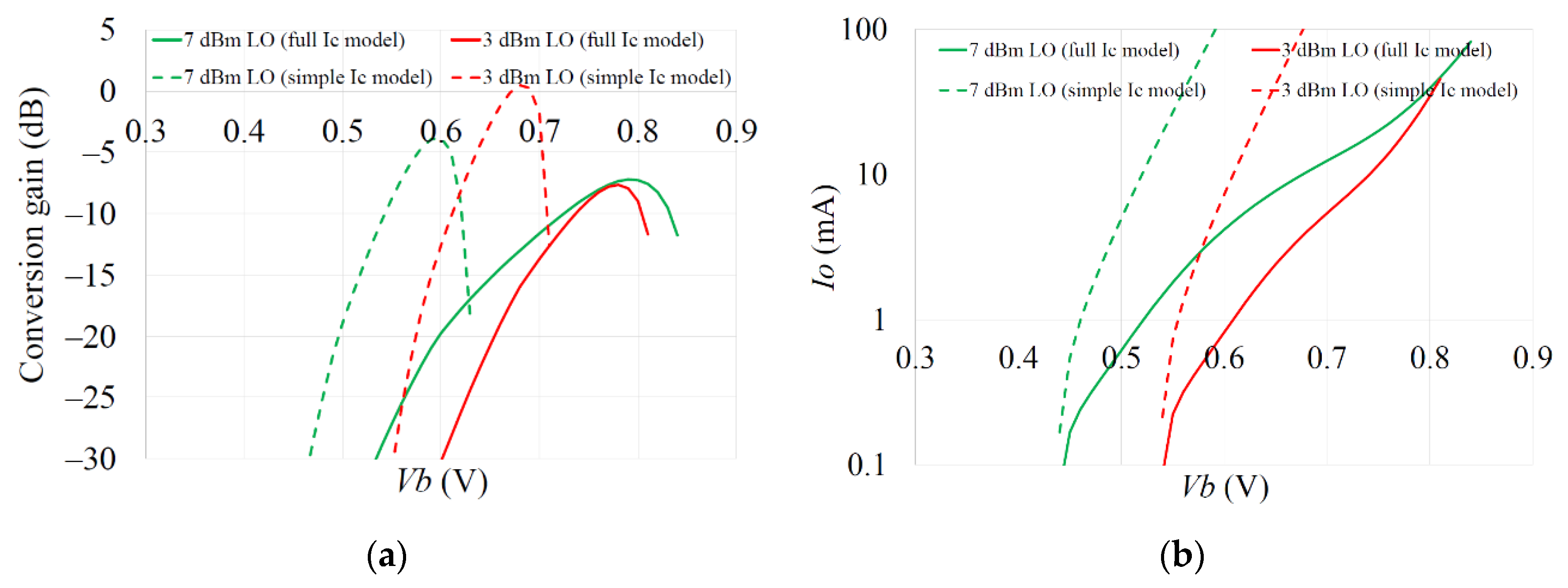

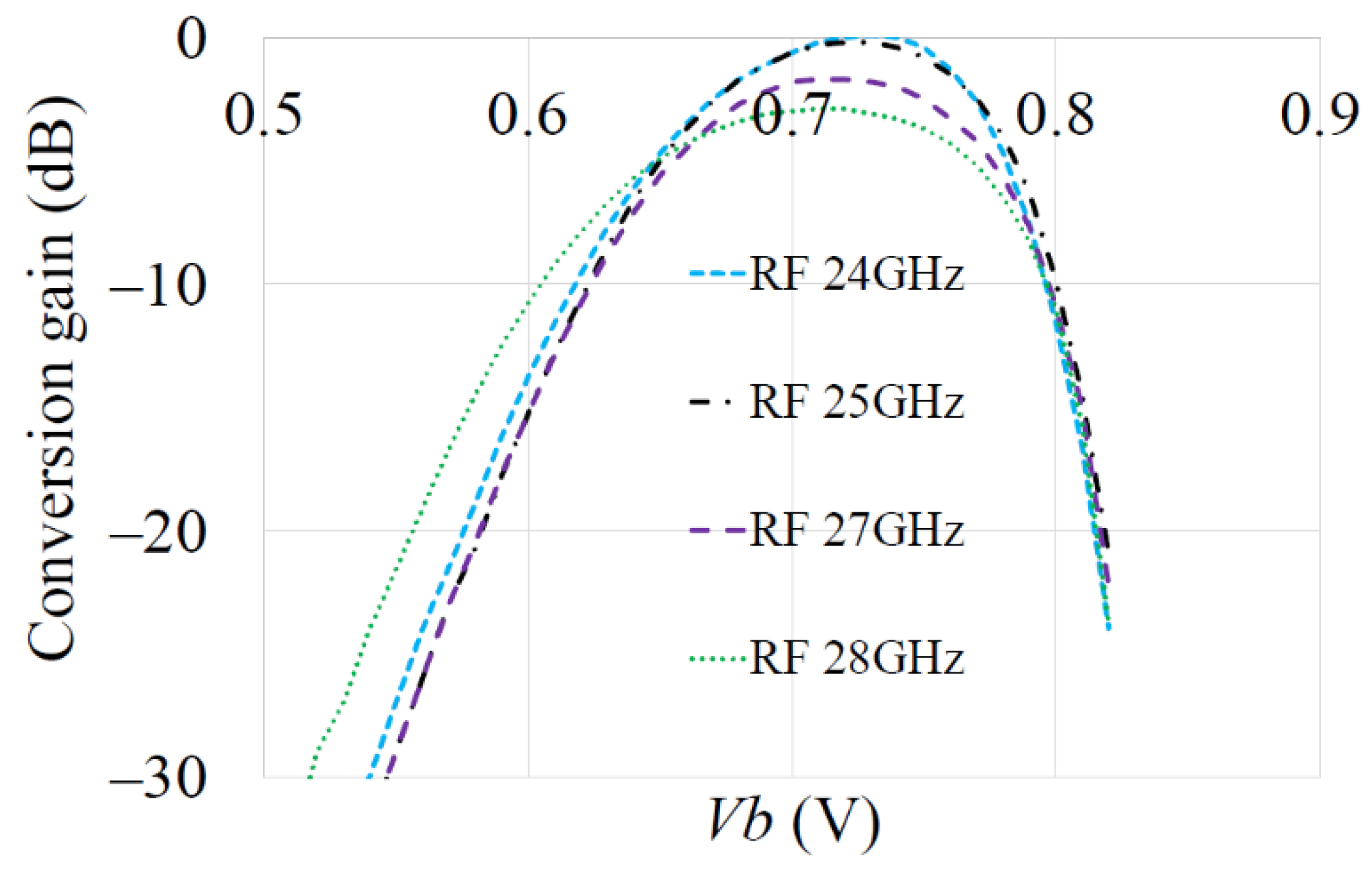

5.1. Initial Insights from Mathematical Model

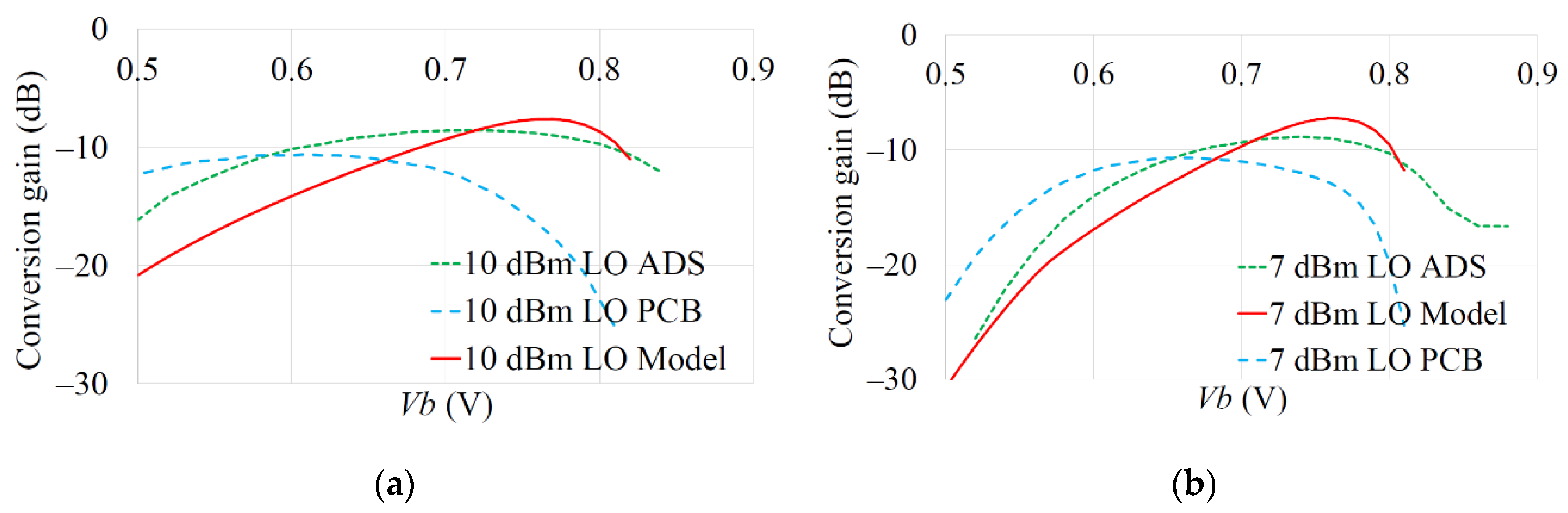

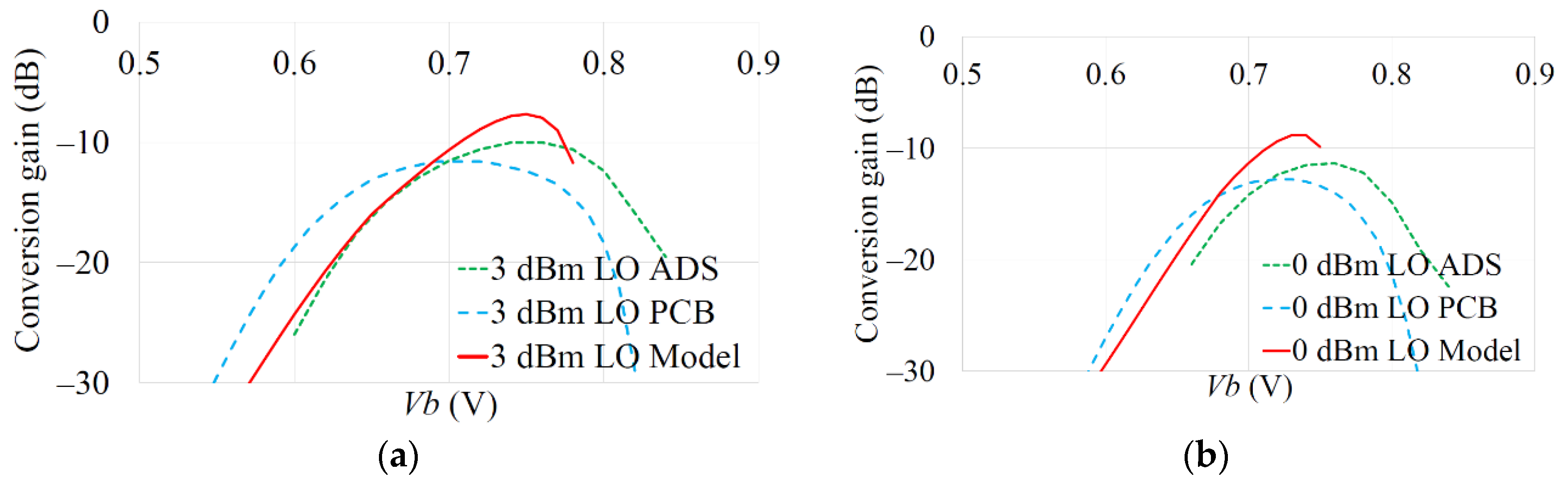

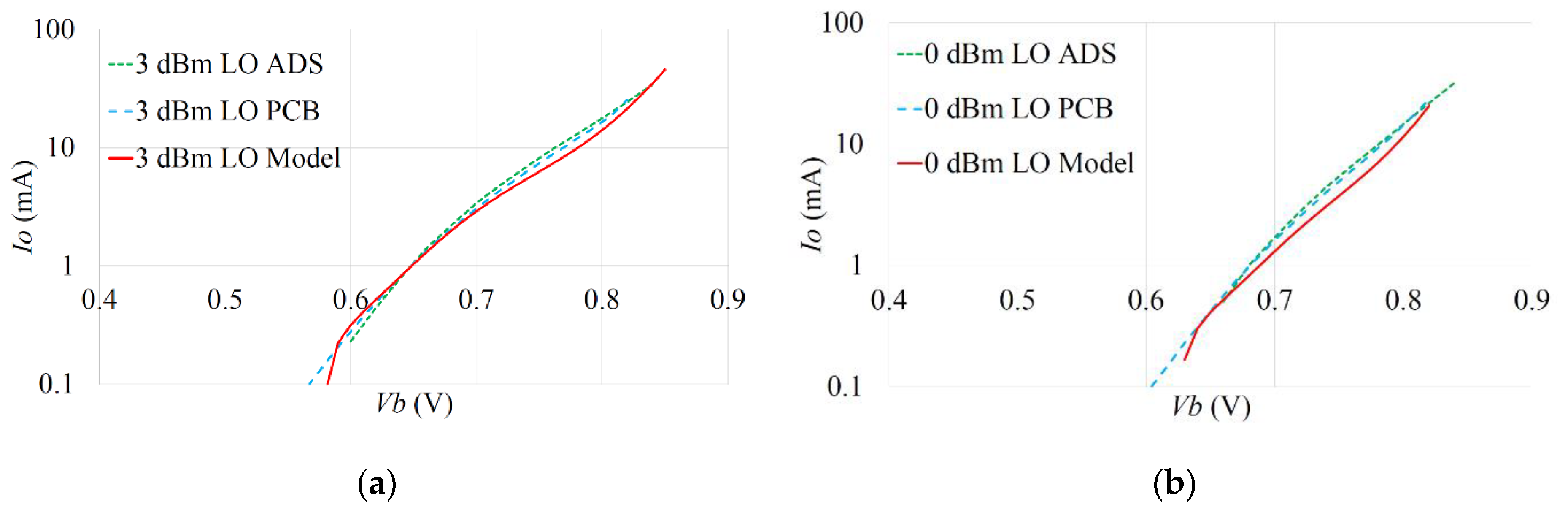

5.2. Lab Comparison Measurements of Hardware Mixer Prototype

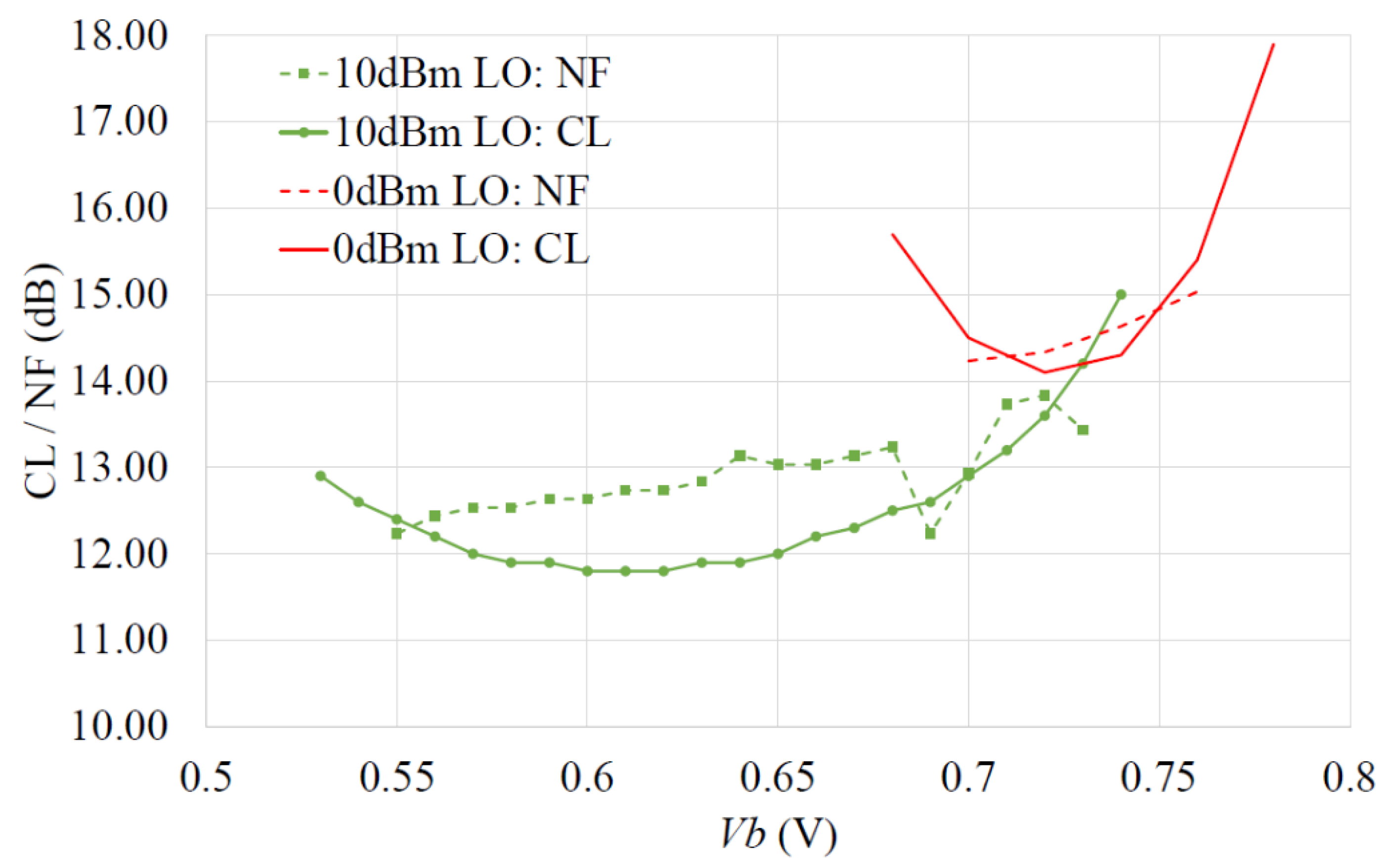

5.3. Noise Figure Measurements

6. Conclusions

- NF/Gc: best settings for AL, Vb can be found and resulting IIP3/P1dBI predicted;

- IIP3/P1dBI: best settings for AL, Vb can be found and resulting NF/Gc predicted;

- Fixed LO power: Achievable NF, Gc, IIP3, P1dBi and DC power as function of Vb can be predicted;

- Fixed DC power: Achievable NF, Gc, IIP3, P1dBi as function of LO power can be predicted.

Funding

Conflicts of Interest

References

- Hong, W.; Jiang, Z.H.; Yu, C.; Hou, D.; Wang, H.; Guo, C.; Hu, Y.; Kuai, L.; Yu, Y.; Jiang, Z.; et al. The Role of Millimeter-Wave Technologies in 5G/6G Wireless Communications. IEEE J. Microw. 2021, 1, 101–122. [Google Scholar] [CrossRef]

- Chataut, R.; Akl, R. Massive MIMO Systems for 5G and beyond Networks—Overview, Recent Trends, Challenges, and Future Research Direction. Sensors 2020, 20, 2753. [Google Scholar] [CrossRef] [PubMed]

- Yang, T.Y.; Chiou, H.K. A 28 GHz Sub-Harmonic Mixer Using LO Doubler in 0.18-Μm CMOS Technology. In Proceedings of the Digest of Papers—IEEE Radio Frequency Integrated Circuits Symposium, San Francisco, CA, USA, 10–13 June 2006; Volume 2006, pp. 209–212. [Google Scholar]

- Chang, Y.T.; Lin, K.Y. A 28-GHz Bidirectional Active Gilbert-Cell Mixer in 90-Nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 473–476. [Google Scholar] [CrossRef]

- Kumar, S.; Saraiyan, S.; Dubey, S.K.; Pal, S.; Islam, A. A 2.4 GHz Double Balanced Downconversion Mixer with Improved Conversion Gain in 180-Nm Technology. Microsyst. Technol. 2020, 26, 1721–1731. [Google Scholar] [CrossRef]

- Varonen, M.; Kärkkäinen, M.; Kantanen, M.; Halonen, K.A.I. Millimeter-Wave Integrated Circuits in 65-Nm CMOS. IEEE J. Solid-State Circuits 2008, 43, 1991–2002. [Google Scholar] [CrossRef]

- Ball, E.A. Investigation into the Relationship Between Conversion Gain, Local Oscillator Drive Level and DC bias in a SiGe Transistor Transconductance Modulated Mixer at 24–28 GHz. In Proceedings of the IEEE Texas Symposium on Wireless & Microwave Circuits and Systems, Waco, TX, USA, 18 May 2021. [Google Scholar] [CrossRef]

- Yan, Y.; Bao, M.; Gunnarsson, S.E.; Zirath, H. A 110-170-GHz Multi-Mode Transconductance Mixer in 250-nm InP DHBT Technology. IEEE Trans. Microw. Theory Tech. 2015, 63, 2897–2904. [Google Scholar] [CrossRef]

- Ning, X.; Yao, H.; Wang, X.; Jin, Z. A W-Band Single-Ended Downconversion/Upconversion Gate Mixer in InP HEMT Technology. In Proceedings of the 2013 IEEE International Conference on Microwave Technology and Computational Electromagnetics, Qingdao, China, 25 August 2013. [Google Scholar] [CrossRef]

- Pucel, R.A.; Masse, D.; Bera, R. Performance of GaAs MESFET Mixers at X Band. IEEE Trans. Microw. Theory Tech. 1976, 24, 351–360. [Google Scholar] [CrossRef]

- Del Rio, D.; Gurutzeaga, I.; Rezola, A.; Sevillano, J.F.; Velez, I.; Gunnarsson, S.E.; Tamir, N.; Saavedra, C.E.; Gonzalez-Jimenez, J.L.; Siligaris, A.; et al. A Wideband and High-Linearity E-Band Transmitter Integrated in a 55-nm SiGe Technology for Backhaul Point-to-Point 10-Gb/s Links. IEEE Trans. Microw. Theory Tech. 2017, 65, 2990–3001. [Google Scholar] [CrossRef]

- Chen, J.D.; Wang, W.J. A K-Band Low-Noise and High-Gain Down-Conversion Active Mixer Using 0.18-Μm CMOS Technology. Wirel. Pers. Commun. 2019, 104, 407–421. [Google Scholar] [CrossRef]

- Beigizadeh, M.; Nabavi, A. Design of a High Gain and Highly Linear Common-Gate UWB Mixer in K-Band. Analog. Integr. Circuits Signal Process. 2014, 78, 501–509. [Google Scholar] [CrossRef]

- Solati, P.; Yavari, M. A Wideband High Linearity and Low-Noise CMOS Active Mixer Using the Derivative Superposition and Noise Cancellation Techniques. Circuits Syst. Signal Process. 2019, 38, 2910–2930. [Google Scholar] [CrossRef]

- Heidari, T.; Nabavi, A. Design and Analysis of a Wideband Compact LNA-Mixer in Millimeter Wave Frequency. Analog. Integr. Circuits Signal Process. 2020, 105, 371–383. [Google Scholar] [CrossRef]

- Gladson, S.C.; Bhaskar, M. A Low-Power RF Mixer with Harmonic Cancellation for IEEE 802.15.4 Portable, Wearable Wireless Applications. AEU-Int. J. Electron. Commun. 2020, 124, 153335. [Google Scholar] [CrossRef]

- Sivonen, P.; Vilander, A.; Pärssinen, A. Cancellation of Second-Order Intermodulation Distortion and Enhancement of IIP2 in Common-Source and Common-Emitter RF Transconductors. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 305–317. [Google Scholar] [CrossRef]

- Nguyen, T.T.; Fujii, K.; Pham, A.-V. Highly Linear Distributed Mixer in 0.25-μm Enhancement-Mode GaAs pHEMT Technology. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 1116–1118. [Google Scholar] [CrossRef]

- Nguyen, T.T.; Riddle, A.; Fujii, K.; Pham, A.-V. Development of Wideband and High IIP3 Millimeter-Wave Mixers. IEEE Trans. Microw. Theory Tech. 2017, 65, 3071–3079. [Google Scholar] [CrossRef]

- Kivekäs, K.; Pärssinen, A.; Halonen, K.A.I. Characterization of IIP2 and DC-Offsets in Transconductance Mixers. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 2001, 48, 1028–1038. [Google Scholar] [CrossRef]

- Surana, D.C.; Gardiner, J.G. Gain and Distortion Properties of FET Mixers and Modulators. IEEE Trans. Electromagn. Compat. 1974, EMC-16, 29–38. [Google Scholar] [CrossRef]

- Korotkov, A.S. Double-Balanced Mixer Based on MOSFETs. Russ. Microelectron. 2011, 40, 128–140. [Google Scholar] [CrossRef]

- Bae, B.; Han, J. 24-40 GHz Gain-Boosted Wideband CMOS Down-Conversion Mixer Employing Body-Effect Control for 5G NR Applications. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 1034–1038. [Google Scholar] [CrossRef]

- Amirabadizadeh, S.; Bijari, A.; Alizadeh, H.; Mehrshad, N. Performance Improvement of a Down-Conversion Active Mixer Using Negative Admittance. Circuits Syst. Signal Process. 2021, 40, 22–49. [Google Scholar] [CrossRef]

- Bidi, A.A.S.; Karimi, G. Design of High Linearity Inductor-Less Active CMOS Mixer Based on Volterra Series Analysis. Circuits Syst. Signal Process. 2020, 39, 4810–4828. [Google Scholar] [CrossRef]

- García, J.A.; de La Fuente, M.L.; Zamanillo, J.M.; Mediavilla, A.; Tazón, A.; Pedro, J.C.; Carvalho, N.B. Intermodulation Distortion Analysis of FET Mixers under Multitone Excitation. In Proceedings of the 2000 30th European Microwave Conference, EuMC 2000, Paris, France, 2–5 October 2000; pp. 1–4. [Google Scholar]

- Xu, H.; Chen, J.; Wu, X.; Peng, C.; Yu, J.; Yuan, B.; Xie, Z. A 32–40 GHz 4-Channel Transceiver with 6-bit Amplitude and Phase Control. AEU Int. J. Electron. Commun. 2021, 139, 153925. [Google Scholar] [CrossRef]

- Avenier, G.; Diop, M.; Chevalier, P.; Troillard, G.; Loubet, N.; Bouvier, J.; Depoyan, L.; Derrier, N.; Buczko, M.; Leyris, C.; et al. 0.13 μ m SiGe BiCMOS Technology Fully Dedicated to Mm-Wave Applications. IEEE J. Solid-State Circuits 2009, 44, 2312–2321. [Google Scholar] [CrossRef]

- Wietstruck, M.; Marschmeyer, S.; Schulze, S.; Wipf, S.T.; Wipf, C.; Kaynak, M. Recent Developments on SiGe BiCMOS Technologies for Mm-Wave and THz Applications. In Proceedings of the 2019 IEEE MTT-S International Microwave Symposium (IMS), Boston, MA, USA, 2 June 2019; pp. 1126–1129. [Google Scholar]

- Pruvost, S.; Telliez, I.; Danneville, F.; Dambrine, G.; Rolland, N.; Pourchon, F. A 40 GHz Single-Ended Down-Conversion Mixer in 0.13 μm SiGeC BiCMOS HBT. IEEE Microw. Wirel. Compon. Lett. 2005, 15, 496–498. [Google Scholar] [CrossRef]

- Wang, X.; Guo, B.; Wu, J.; Gong, J. A 28 GHz Front-End for Phased Array Receivers Simulated in 180 Nm CMOS. In Proceedings of the 2020 IEEE International Conference on Semiconductor Electronics (ICSE), Kuala Lumpur, Malaysia, 28 July 2020; pp. 1–4. [Google Scholar]

- Kivekäs, K.; Pärssinen, A.; Ryynänen, J.; Jussila, J.; Halonen, K. Calibration Techniques of Active BiCMOS Mixers. IEEE J. Solid-State Circuits 2002, 37, 766–769. [Google Scholar] [CrossRef]

- Fonte, A.; Plutino, F.; Moquillon, L.; Razafimandimby, S.; Pruvost, S. 5G 26 GHz and 28 GHz Bands SiGe:C Receiver with Very High-Linearity and 56 DB Dynamic Range. In Proceedings of the 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, Spain, 23 September 2018; pp. 57–60. [Google Scholar]

- Kivekas, K.; Parssinen, A.; Jussila, J.; Ryynanen, J.; Halonen, K. Design of Low-Voltage Active Mixer for Direct Conversion Receivers. In Proceedings of the ISCAS 2001—2001 IEEE International Symposium on Circuits and Systems, Conference Proceedings, Sydney, NSW, Australia, 6–9 May 2001; Volume 4, pp. 382–385. [Google Scholar]

- Reynolds, S.K. A 60-GHz Superheterodyne Downconversion Mixer in Silicon-Germanium Bipolar Technology. IEEE J. Solid-State Circuits 2004, 39, 2065–2068. [Google Scholar] [CrossRef]

- Mazor, N.; Sheinman, B.; Katz, O.; Levinger, R.; Bloch, E.; Carmon, R.; Ben-Yishay, R.; Elad, D. Highly Linear 60-GHz SiGe Downconversion/Upconversion Mixers. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 401–403. [Google Scholar] [CrossRef]

- Qayyum, J.A.; Albrecht, J.D.; Ulusoy, A.C. A Compact V-Band Upconversion Mixer with -1.4-dBm OP1dB in SiGe HBT Technology. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 276–278. [Google Scholar] [CrossRef]

- Sweet, A.A. Designing Bipolar Transistor Radio Frequency Integrated Circuits, 1st ed.; Artech House: Norwood, MA, USA, 2008; pp. 200–205. [Google Scholar]

- Reynolds, S.K.; Powell, J.D. 77 and 94-GHz Downconversion Mixers in SiGe BiCMOS. In Proceedings of the 2006 IEEE Asian Solid-State Circuits Conference, ASSCC 2006, Hangzhou, China, 13–15 November 2006; pp. 191–194. [Google Scholar]

- Choi, C.; Son, J.H.; Lee, O.; Nam, I. A +12dBm OIP3 60-GHz RF Downconversion Mixer with an Output-Matching, Noise- and Distortion-Canceling Active Balun for 5G Applications. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 284–286. [Google Scholar] [CrossRef]

- Testa, P.V.; Szilagyi, L.; Xu, X.; Carta, C.; Ellinger, F. A Low-Power Low-Voltage Down-Conversion Mixer for 5G Applications at 28 GHz in 22-Nm FD-SOI CMOS Technology. In Proceedings of the Asia-Pacific Microwave Conference Proceedings, APMC, Hong Kong, 8–11 December 2020; pp. 911–913. [Google Scholar]

- Bhatt, D.; Mukherjee, J.; Redouté, J.M. Low-Power Switched Transconductance Mixer and LNA Design for Wi-Fi and WiMAX Applications in 65 Nm CMOS. IET Microw. Antennas Propag. 2018, 12, 1736–1744. [Google Scholar] [CrossRef]

- Yang, S.; Hu, K.; Fu, H.; Ma, K.; Lu, M. A 24-to-30 GHz Ultra-High-Linearity Down-Conversion Mixer for 5G Applications Using a New Linearization Method. Sensors 2022, 22, 3802. [Google Scholar] [CrossRef]

- Xu, L.; Wang, Z.; Li, Q. Design of a Broadband Millimeter-Wave Monolithic IQ Mixer. J. Infrared Millim. Terahertz Waves 2010, 31, 593–600. [Google Scholar] [CrossRef]

- Lee, D.; Lee, M.; Park, B.; Song, E.; Lee, K.; Lee, J.; Han, J.; Kwon, K. 24–40 GHz MmWave Down-Conversion Mixer with Broadband Capacitor-Tuned Coupled Resonators for 5G New Radio Cellular Applications. IEEE Access 2022, 10, 16782–16792. [Google Scholar] [CrossRef]

- Xavier, B.A.; Aitchison, C.S. Simulation and Modelling of a Heterojunction Bipolar Transistor Mixer. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Albuquerque, NM, USA, 1–5 June 1992; Volume 1, pp. 333–336. [Google Scholar]

- Antognetti, P.; Massobrio, G. Semiconductor Device Modeling with SPICE, 2nd ed.; McGraw Hill: New York, NY, USA, 1993. [Google Scholar]

- Pozar, D.M. Microwave Engineering, 4th ed.; Wiley: Hoboken, NJ, USA, 2012; pp. 637–655. [Google Scholar]

- Maas, S.A. Nonlinear Microwave and RF Circuits, 2nd ed.; Artech House: Norwood, MA, USA, 2003; pp. 497–514. [Google Scholar]

- Robertson, I.D.; Lucyszyn, S. RFIC and MMIC Design and Technology, 1st ed.; The IET: London, UK, 2001; pp. 316–321. [Google Scholar]

- Kang, S.; Choi, B.; Kim, B. Linearity Analysis of CMOS for RF Applications. IEEE Trans. Microw. Theory Tech. 2003, 51, 972–977. [Google Scholar] [CrossRef]

- Liu, Z.; Dong, J.; Chen, Z.; Jiang, Z.; Liu, P.; Wu, Y.; Zhao, C.; Kang, K. A 62–90 GHz High Linearity and Low Noise CMOS Mixer Using Transformer-Coupling Cascode Topology. IEEE Access 2018, 6, 19338–19344. [Google Scholar] [CrossRef]

- Syu, J.S.; Meng, C.; Wang, C.L. 2.4-GHz Low-Noise Direct-Conversion Receiver with Deep N-Well Vertical-NPN BJT Operating near Cutoff Frequency. IEEE Trans. Microw. Theory Tech. 2011, 59, 3195–3205. [Google Scholar] [CrossRef]

| BJT Model Parameter | Value | Unit | Description |

|---|---|---|---|

| Is | 1.249 × 10−15 | A | Transport saturation current |

| NF | 1.002 | - | Forward current emission coefficient |

| NR | 1.01 | - | Reverse current emission coefficient |

| VT | 25.9 | mV | kT/q (25.9mV at 300K) |

| VAR | 1.229 | V | Reverse Early voltage |

| VAF | 380.1 | V | Forward Early voltage |

| IKF | 0.1898 | A | Forward Beta high current roll-off |

| IKR | 0.02753 | A | Reverse Beta high current roll-off |

| CJE | 0.2531 | pF | Base-emitter zero-bias depletion cap |

| VJE | 0.9286 | V | Base-emitter built-in potential |

| MJE | 0.06125 | - | Base-emitter junction exponential factor |

| TF | 2.331 | pS | Ideal forward transit time |

| XTF | 1.159 | - | TF bias dependence coefficient |

| ITF | 0.3991 | A | TF high current parameter |

| VTF | 0.5242 | V | TF dependency on Vbc |

| CJC | 54.52 | fF | Base-collector zero-bias depletion cap |

| VJC | 0.4808 | V | Base-collector built-in potential |

| MJC | 0.5812 | - | Base-collector junction exponential factor |

| TR | 1.532 | nS | Ideal reverse transit time |

| RC | 4.1 | Ohm | Internal collector resistance |

| RE | 0.18 | Ohm | Internal emitter resistance |

| RB | 7.0 | Ohm | Zero bias internal base resistance |

| Ro | VAF/Ic | Ohm | Output resistance |

| BF | 987.1 | - | Forward max Beta |

| 10 dBm LO | 7 dBm LO | 3 dBm LO | 0 dBm LO | ||

|---|---|---|---|---|---|

| Gc: Model-PCB | 8.0 | 6.0 | 4.3 | 2.7 | dB |

| Gc: ADS-PCB | 5.2 | 5.5 | 5.3 | 5.2 | dB |

| Gc: Model-ADS | 3.0 | 1.8 | 1.3 | 2.7 | dB |

| DC Draw: Model-PCB | 2.4 | - | 1.1 | 1.2 | mA |

| DC Draw: ADS-PCB | 3.4 | - | 0.7 | 0.6 | mA |

| DC Draw: Model-ADS | 1.6 | 1.6 | 1.9 | 1.7 | mA |

| 10 dBm LO | 7 dBm LO | 3 dBm LO | 0 dBm LO | ||

|---|---|---|---|---|---|

| Gc: Model-PCB | 0.9 | 1.6 | 2.4 | 2.5 | dB |

| Gc: ADS-PCB | 3.0 | 3.5 | 3.9 | 4.0 | dB |

| Gc: Model-ADS | 2.0 | 1.8 | 1.6 | 1.4 | dB |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ball, E.A. Predicting the Performance of a 26 GHz Transconductance Modulated Downconversion Mixer as a Function of LO Drive and DC Bias. Electronics 2022, 11, 2516. https://doi.org/10.3390/electronics11162516

Ball EA. Predicting the Performance of a 26 GHz Transconductance Modulated Downconversion Mixer as a Function of LO Drive and DC Bias. Electronics. 2022; 11(16):2516. https://doi.org/10.3390/electronics11162516

Chicago/Turabian StyleBall, Edward A. 2022. "Predicting the Performance of a 26 GHz Transconductance Modulated Downconversion Mixer as a Function of LO Drive and DC Bias" Electronics 11, no. 16: 2516. https://doi.org/10.3390/electronics11162516

APA StyleBall, E. A. (2022). Predicting the Performance of a 26 GHz Transconductance Modulated Downconversion Mixer as a Function of LO Drive and DC Bias. Electronics, 11(16), 2516. https://doi.org/10.3390/electronics11162516