Evaluation of Solder Joint Reliability in 3D Packaging Memory Devices under Thermal Shock

Abstract

:1. Introduction

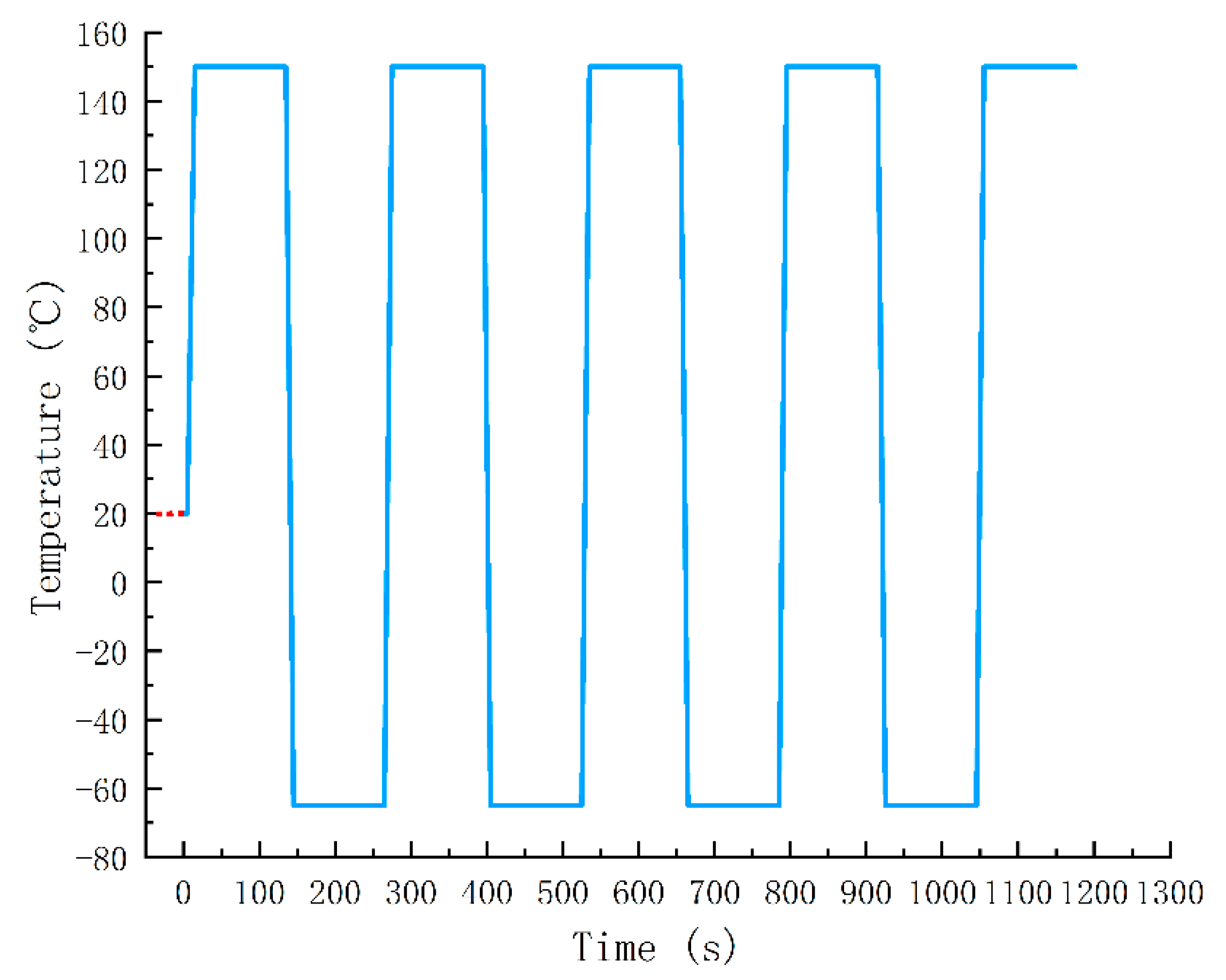

2. Experimental Procedure

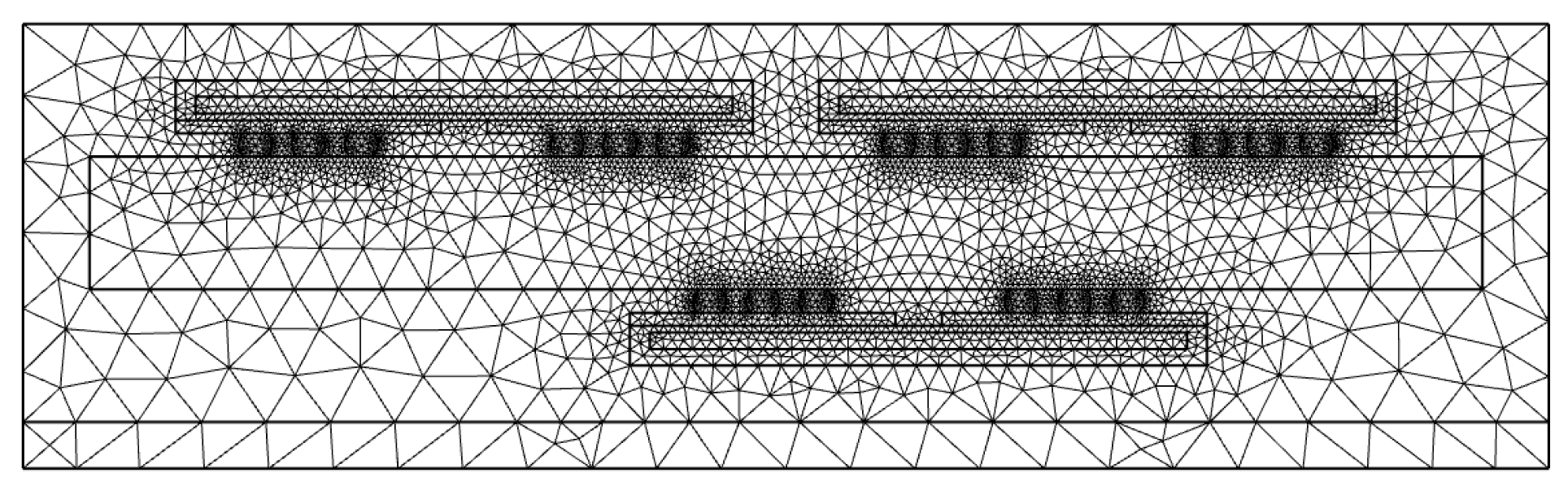

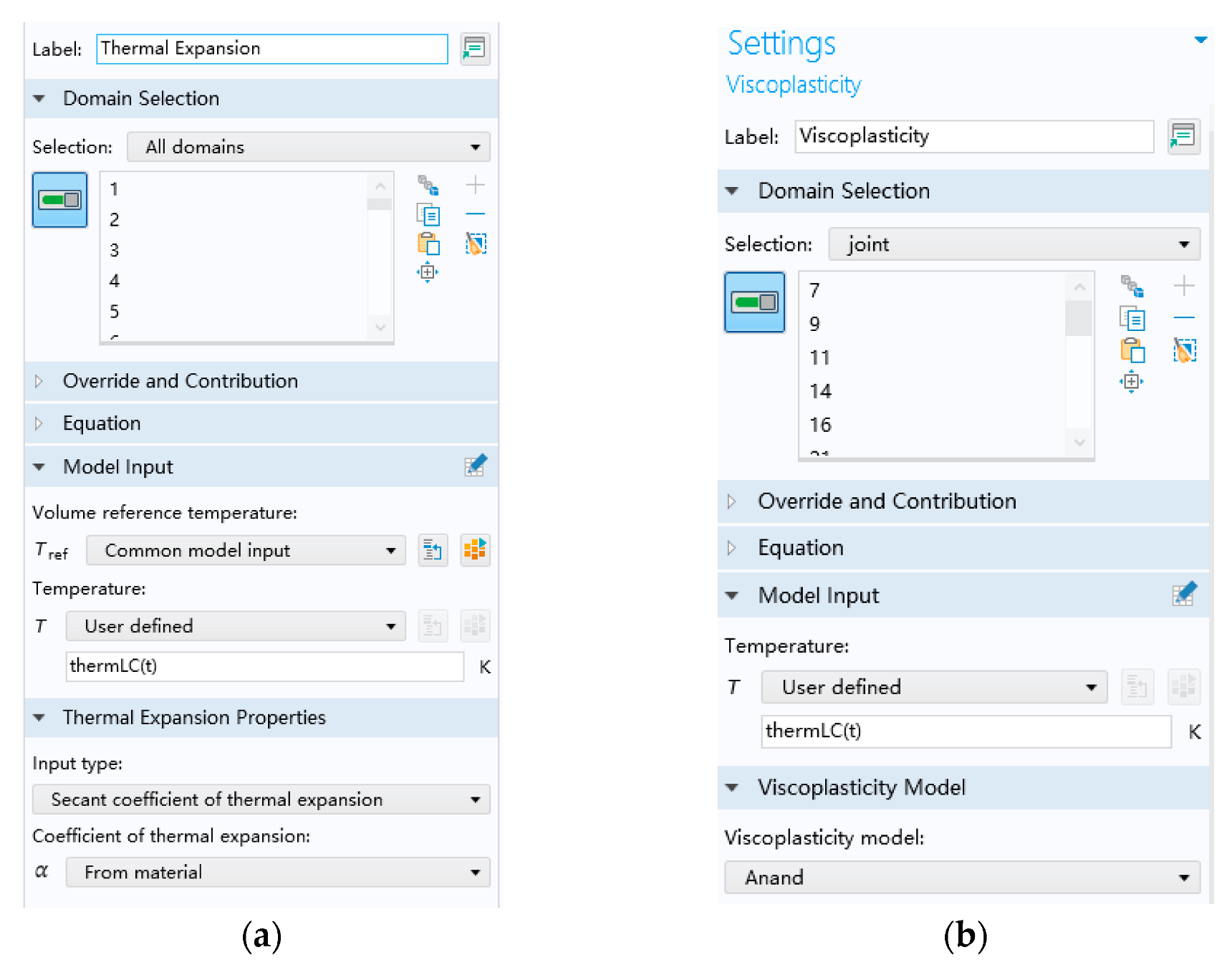

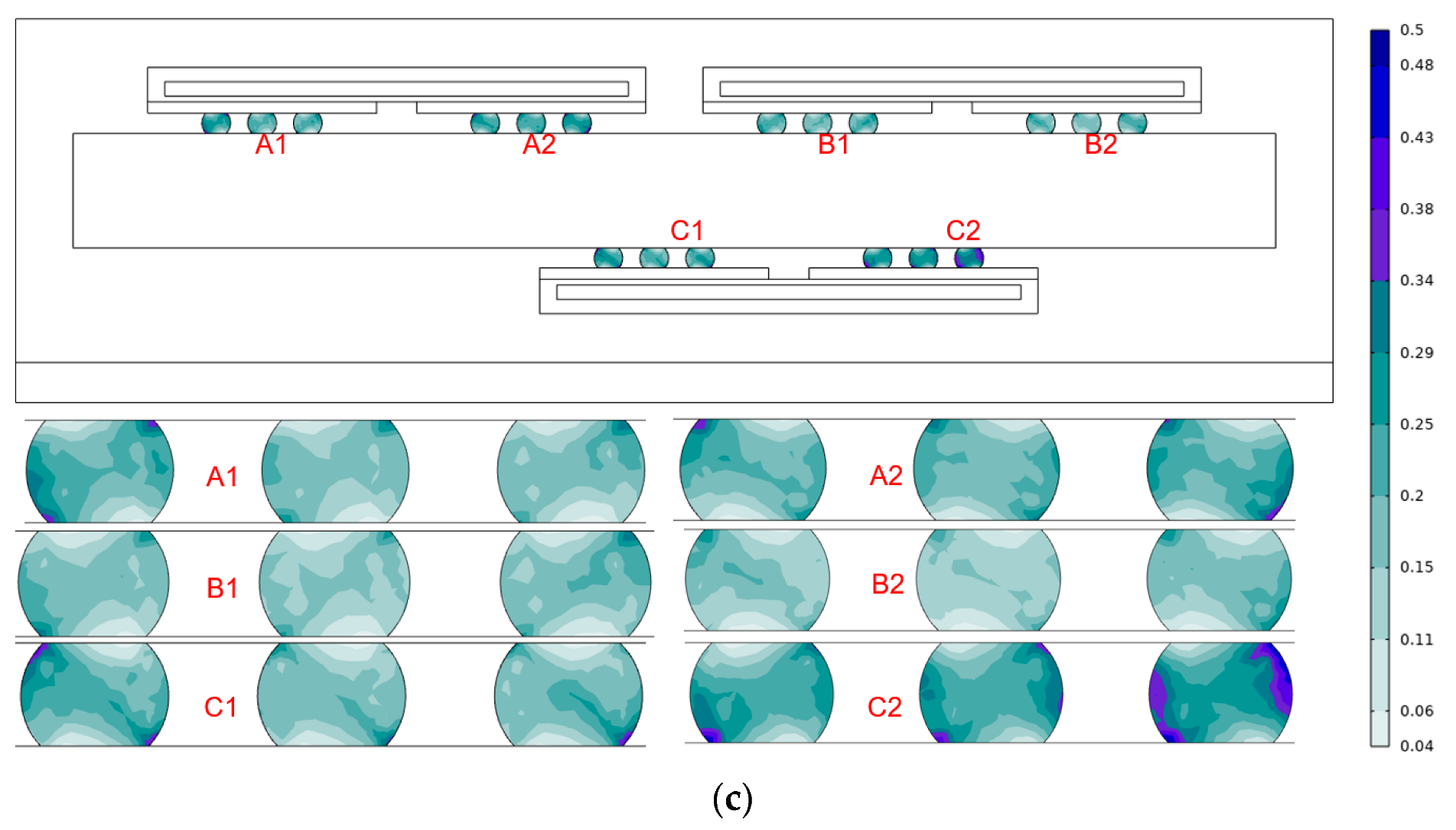

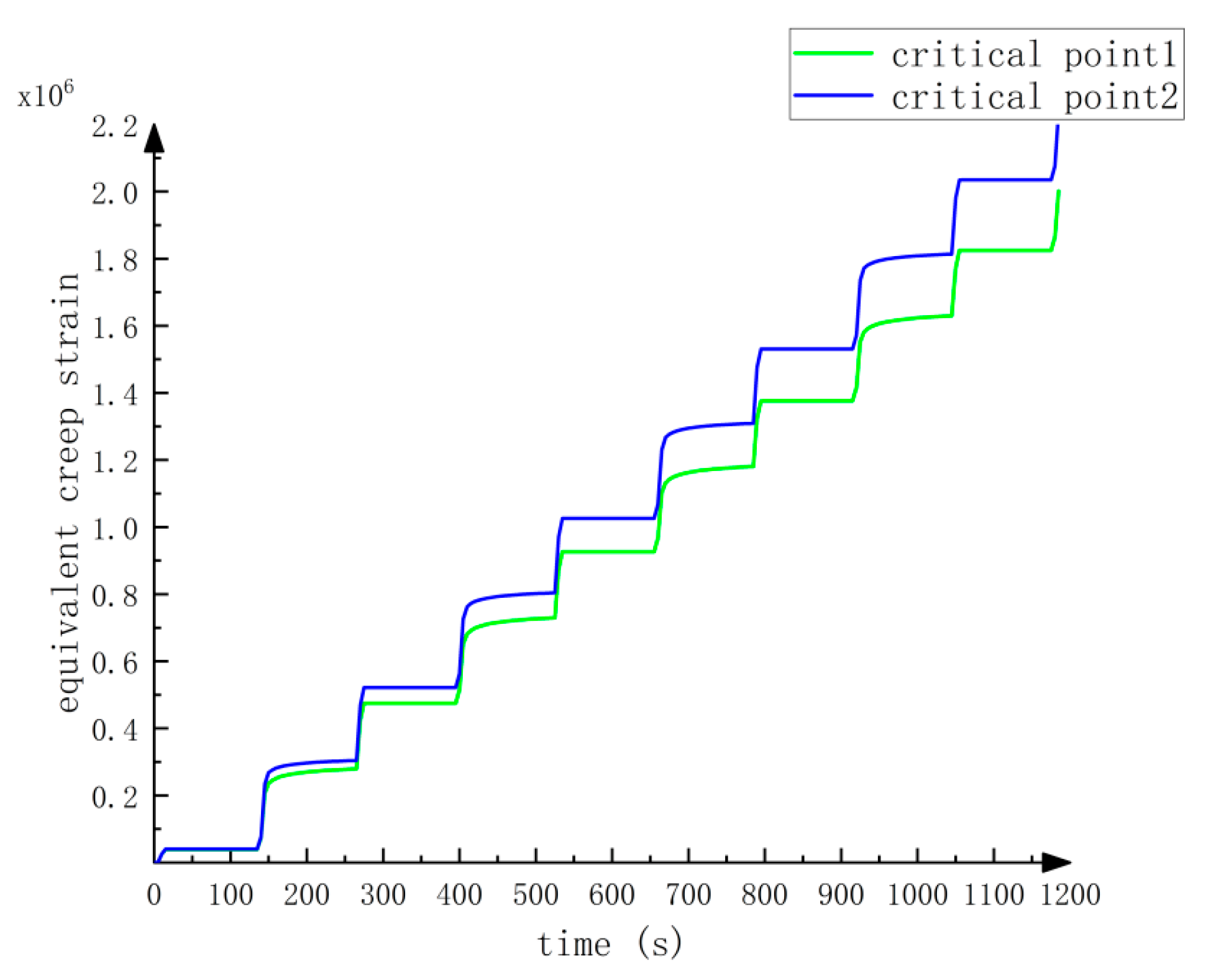

3. Finite Element Analysis

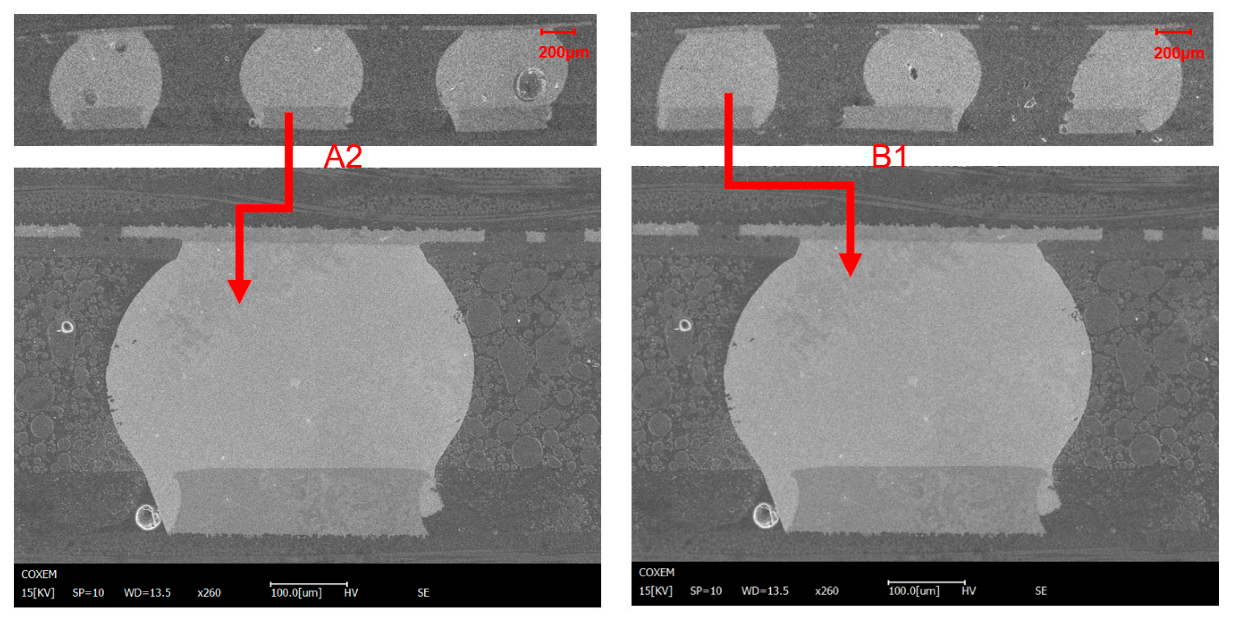

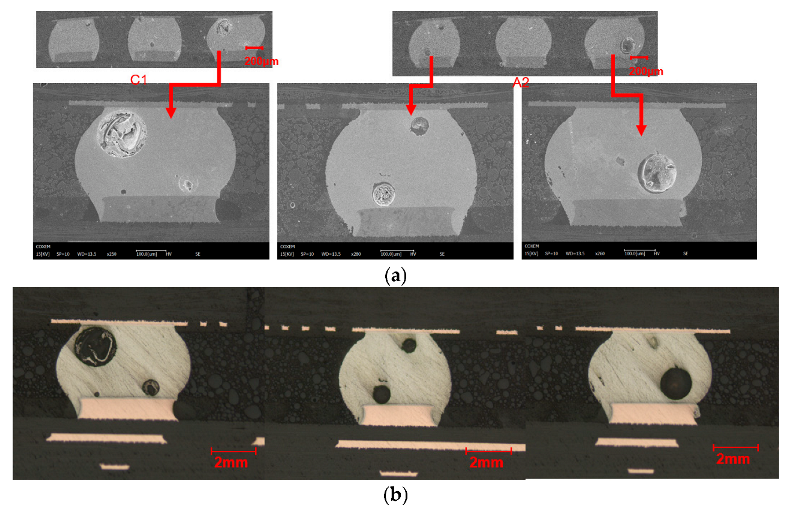

4. Results and Discussions

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tian, W.; Ma, T.; Liu, X. TSV Technology and high-energy heavy ions radiation impact review. Electronics 2018, 7, 112. [Google Scholar] [CrossRef]

- Li, T.; Hou, J.; Yan, J.; Liu, R.; Yang, H.; Sun, Z. Chiplet heterogeneous integration technology—Status and challenges. Electronics 2020, 9, 670. [Google Scholar] [CrossRef]

- Hao, Y.; Xiang, S.; Han, G.; Zhang, J.; Ma, X.; Zhu, Z.; Guo, X.; Zhang, Y.; Han, Y.; Song, Z. Recent progress of integrated circuits and optoelectronic chips. Sci. China Inf. Sci. 2021, 64, 201401. [Google Scholar] [CrossRef]

- Lau, J.H. 3D IC Integration and 3D IC Packaging. In Semiconductor Advanced Packaging; Springer: Berlin/Heidelberg, Germany, 2021; pp. 343–378. [Google Scholar]

- Hu, X.; Stow, D.; Xie, Y. Die stacking is happening. IEEE Micro 2018, 38, 22–28. [Google Scholar] [CrossRef]

- Yu, M.; Fang, Y.; Wang, Z.; Chen, G.; Pan, Y.; Yang, X.; Yin, M.; Yang, Y.; Li, M.; Cai, Y. Encapsulation layer design and scalability in encapsulated vertical 3D RRAM. Nanotechnology 2016, 27, 205202. [Google Scholar] [CrossRef]

- Chakravarthi, V.S.; Koteshwar, S.R. Introduction to Design of System on Chips and Future Trends in VLSI. In SoC Physical Design; Springer: Berlin/Heidelberg, Germany, 2022; pp. 1–20. [Google Scholar]

- Jiao, J.; De, X.; Chen, Z.; Zhao, T. Integrated circuit failure analysis and reliability prediction based on physics of failure. Eng. Fail. Anal. 2019, 104, 714–726. [Google Scholar] [CrossRef]

- Yang, B.; Li, D.; Yang, H.; Hu, Y.; Yang, P. Vibrational fatigue and reliability of package-on-package stacked chip assembly. Microelectron. J. 2019, 92, 104609. [Google Scholar] [CrossRef]

- Qiu, B.; Xiong, J.; Wang, H.; Zhou, S.; Yang, X.; Lin, Z.; Liu, M.; Cai, N. Survey on Fatigue Life Prediction of BGA Solder Joints. Electronics 2022, 11, 542. [Google Scholar] [CrossRef]

- Depiver, J.A.; Mallik, S.; Amalu, E.H. Thermal fatigue life of ball grid array (BGA) solder joints made from different alloy compositions. Eng. Fail. Anal. 2021, 125, 105447. [Google Scholar] [CrossRef]

- Clech, J.-P.M.; Coyle, R.J.; Arfaei, B. Pb-free solder joint thermo-mechanical modeling: State of the art and challenges. JOM 2019, 71, 143–157. [Google Scholar] [CrossRef]

- Zhang, S.; Li, Z.; Zhou, H.; Li, R.; Wang, S.; Paik, K.-W.; He, P. Recent Prospectives and Challenges of 3D Heterogeneous Integration. e-Prime-Adv. Electr. Eng. Electron. Energy 2022, 2, 100052. [Google Scholar]

- Wang, C.; Huang, X.-J.; Vafai, K. Analysis of hotspots and cooling strategy for multilayer three-dimensional integrated circuits. Appl. Therm. Eng. 2021, 186, 116336. [Google Scholar] [CrossRef]

- Wen, Y.; Chen, C.; Ye, Y.; Xue, Z.; Liu, H.; Zhou, X.; Zhang, Y.; Li, D.; Xie, X.; Mai, Y.W. Advances on thermal conductive epoxy-based composites as electronic packaging underfill materials—A review. Adv. Mater. 2022, 2201023. [Google Scholar] [CrossRef] [PubMed]

- Jeong, H.; Jung, K.-H.; Lee, C.-J.; Min, K.D.; Myung, W.-R.; Jung, S.-B. Effect of epoxy mold compound and package dimensions on the thermomechanical properties of a fan-out package. J. Mater. Sci. Mater. Electron. 2020, 31, 6835–6842. [Google Scholar] [CrossRef]

- Deshpande, A.; Jiang, Q.; Dasgupta, A.; Becker, U. Impact of Interfacial Roughness on Tensile vs. Shear Creep Rupture of Solder Joints. In Proceedings of the 2021 20th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (iTherm), San Diego, CA, USA, 1–4 June 2021; pp. 968–971. [Google Scholar]

- Schwerz, R.; Roellig, M.; Wolter, K.-J. Reliability analysis of encapsulated components in 3D-circuit board integration. In Proceedings of the 2018 19th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), Toulouse, France, 15–18 April 2018; pp. 1–12. [Google Scholar]

- Chen, Y.; Jing, B.; Li, J.; Jiao, X.; Hu, J.; Wang, Y. Failure analysis and modeling of solder joints in BGA packaged electronic chips. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 11, 43–50. [Google Scholar] [CrossRef]

- Fan, J.; Wu, J.; Jiang, C.; Zhang, H.; Ibrahim, M.; Deng, L. Random voids generation and effect of thermal shock load on mechanical reliability of light-emitting diode flip chip solder joints. Materials 2019, 13, 94. [Google Scholar] [CrossRef]

- Han, Z.; Huang, X. GA-BP in thermal fatigue failure prediction of microelectronic chips. Electronics 2019, 8, 542. [Google Scholar] [CrossRef]

- Ghaffarian, R. Assembly Reliability of 3D Stacks under Thermal Cycles. In Proceedings of the 2020 19th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 26–29 May 2020; pp. 1152–1159. [Google Scholar]

- Xu, Y.; Zeng, Q.; Wang, Y.; Wu, M.; Chen, X.; Chen, G. The Discussion About the Identification of the Anand Model Parameters and Two Alternative Identification Methods. J. Electron. Packag. 2022, 145, 011205. [Google Scholar] [CrossRef]

- Yeo, S.M.; Yow, H.K.; Yeoh, K.H. Solder void size reduction in semiconductor package by vacuum reflow and pressure cure processes. Solder. Surf. Mt. Technol. 2022, 34, 239–254. [Google Scholar] [CrossRef]

- Pin, S.; Gracia, A.; Delétage, J.-Y.; Fouquet, J.; Fremont, H. Robustness of BGAs: Parametric study of voids’ distribution in SAC solder joints. Microelectron. Reliab. 2019, 102, 113484. [Google Scholar] [CrossRef]

- Belyakov, S.; Coyle, R.; Arfaei, B.; Xian, J.; Gourlay, C. Microstructure and damage evolution during thermal cycling of Sn-Ag-Cu solders containing antimony. J. Electron. Mater. 2021, 50, 825–841. [Google Scholar] [CrossRef]

- Gu, J.; Lin, J.; Lei, Y.; Fu, H. Experimental analysis of Sn-3.0 Ag-0.5 Cu solder joint board-level drop/vibration impact failure models after thermal/isothermal cycling. Microelectron. Reliab. 2018, 80, 29–36. [Google Scholar] [CrossRef]

- Gain, A.K.; Zhang, L. Thermal aging effects on microstructure, elastic property and damping characteristic of a eutectic Sn–3.5 Ag solder. J. Mater. Sci. Mater. Electron. 2018, 29, 14519–14527. [Google Scholar] [CrossRef]

- Wu, P.; Wang, P.; Chiang, K. Empirical solutions and reliability assessment of thermal induced creep failure for wafer level packaging. IEEE Trans. Device Mater. Reliab. 2018, 19, 126–132. [Google Scholar] [CrossRef]

- Li, Q.-H.; Li, C.-F.; Zhang, W.; Chen, W.-W.; Liu, Z.-Q. Microstructural evolution and failure mechanism of 62Sn36Pb2Ag/Cu solder joint during thermal cycling. Microelectron. Reliab. 2019, 99, 12–18. [Google Scholar] [CrossRef]

- Chen, Y.; Wang, C.; Gao, Y.; Gao, Z.; Liu, Z.-Q. Microstructural evolution and failure analysis of Sn–Bi57–Ag0. 7 solder joints during thermal cycling. J. Mater. Sci. Mater. Electron. 2022, 33, 1942–1952. [Google Scholar] [CrossRef]

- Depiver, J.A.; Mallik, S.; Harmanto, D. Solder joint failures under thermo-mechanical loading conditions—A review. Adv. Mater. Process. Technol. 2021, 7, 1–26. [Google Scholar] [CrossRef]

- Liu, D.; Pons, D.J. Crack propagation mechanisms for creep fatigue: A consolidated explanation of fundamental behaviours from initiation to failure. Metals 2018, 8, 623. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, S.; Lin, Z.; Qiu, B.; Wang, H.; Xiong, J.; He, C.; Zhou, B.; Pan, Y.; Huang, R.; Bao, Y.; et al. Evaluation of Solder Joint Reliability in 3D Packaging Memory Devices under Thermal Shock. Electronics 2022, 11, 2556. https://doi.org/10.3390/electronics11162556

Zhou S, Lin Z, Qiu B, Wang H, Xiong J, He C, Zhou B, Pan Y, Huang R, Bao Y, et al. Evaluation of Solder Joint Reliability in 3D Packaging Memory Devices under Thermal Shock. Electronics. 2022; 11(16):2556. https://doi.org/10.3390/electronics11162556

Chicago/Turabian StyleZhou, Shuai, Zhenpei Lin, Baojun Qiu, Han Wang, Jingang Xiong, Chang He, Bei Zhou, Yiliang Pan, Renbin Huang, Yiliang Bao, and et al. 2022. "Evaluation of Solder Joint Reliability in 3D Packaging Memory Devices under Thermal Shock" Electronics 11, no. 16: 2556. https://doi.org/10.3390/electronics11162556