A H-Bridge-Multiplexing-Based Novel Power Electronic Transformer

Abstract

:1. Introduction

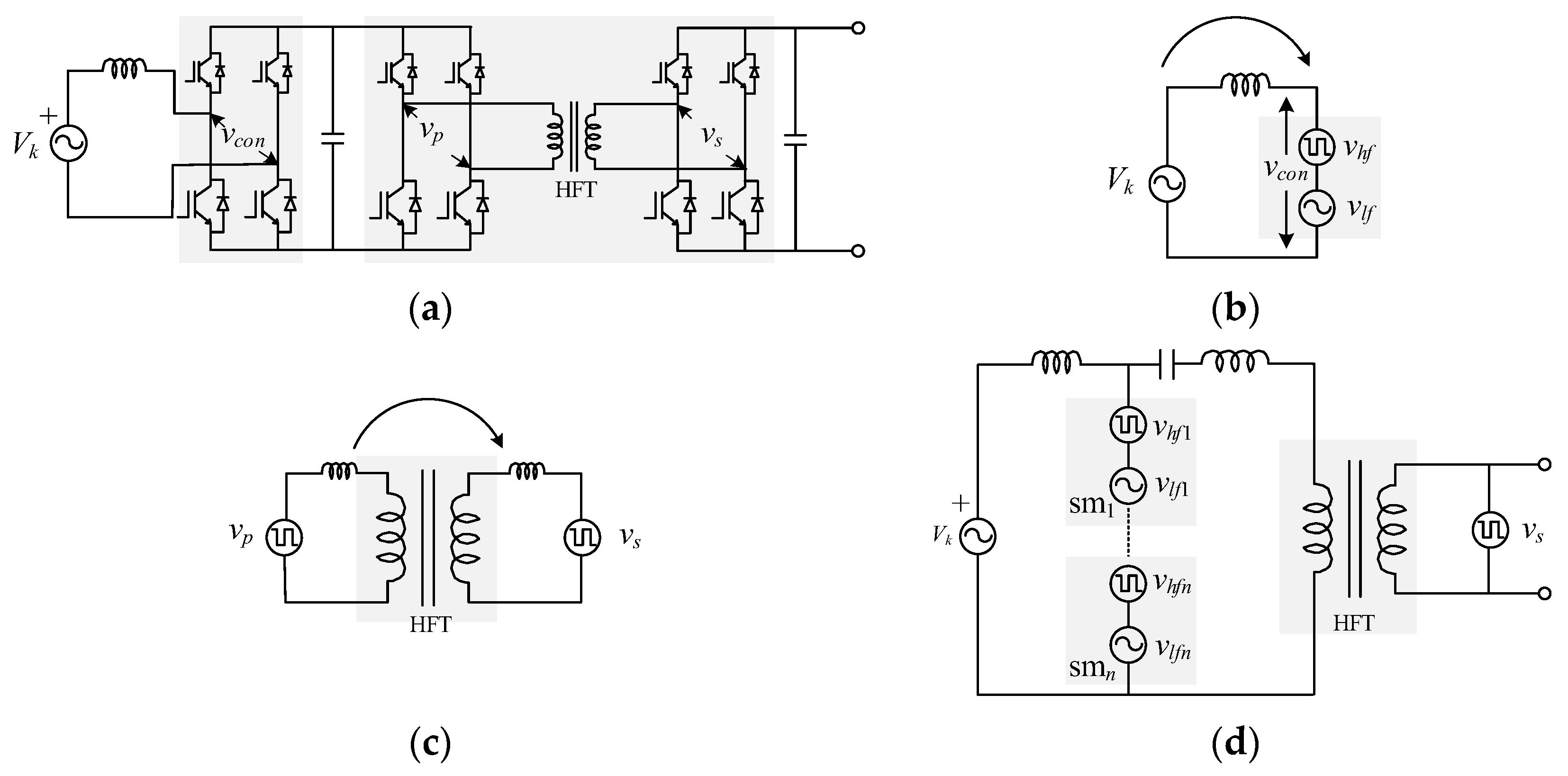

2. Proposing a Novel Topology

2.1. Description of Topology

2.2. Topology Evolution and Working Principle

2.3. Mathematical Models and Switching Signals

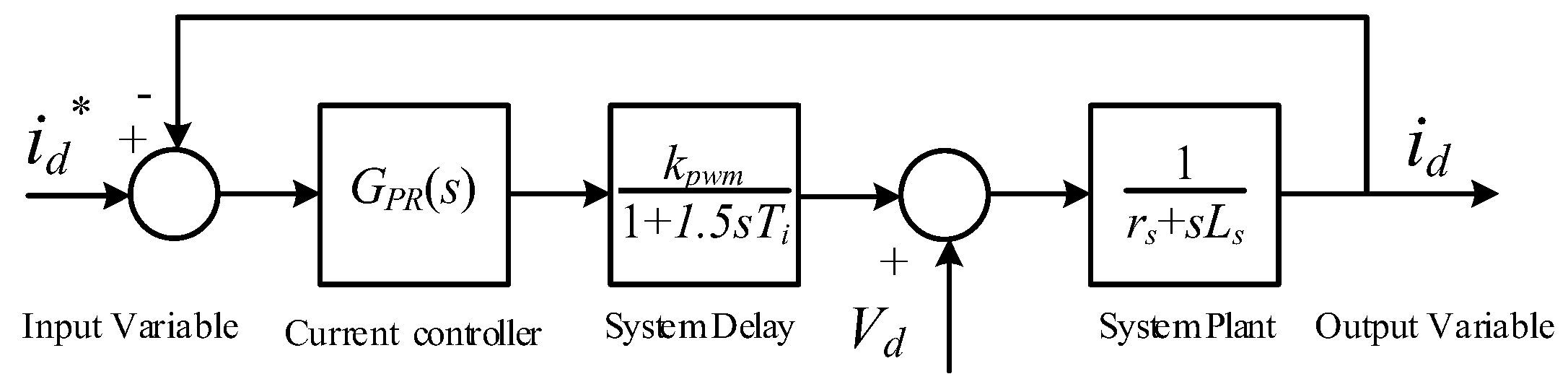

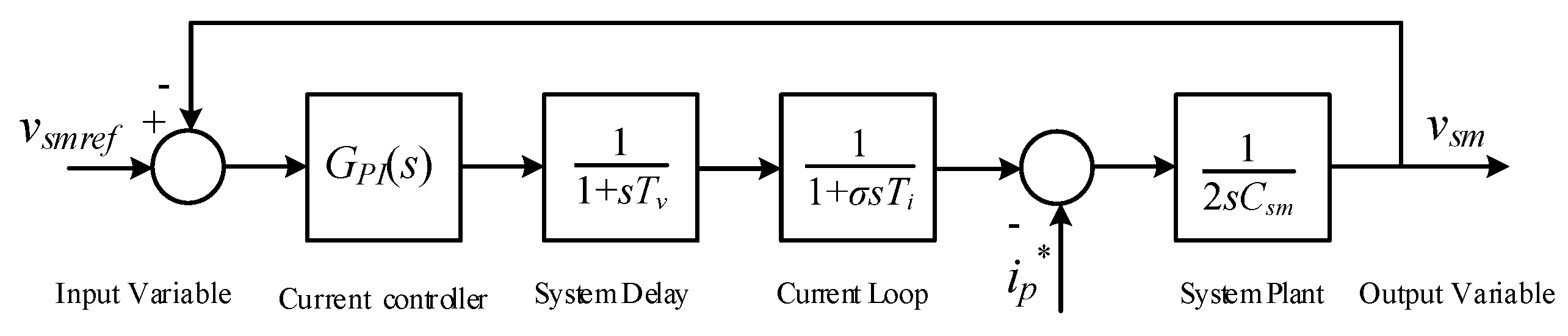

3. Control Structure

3.1. Current Loop Design on the Input Side

3.2. Submodule Voltage Loop Design on the Input Side

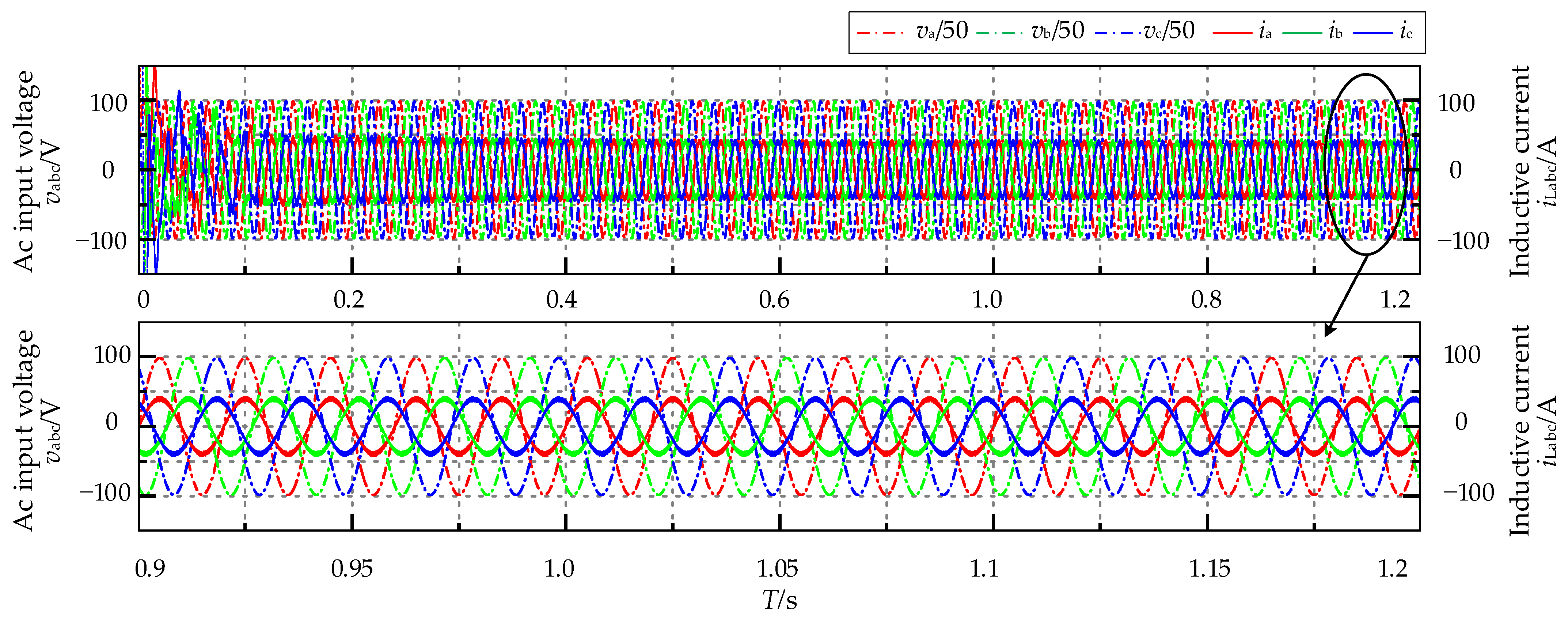

4. Design and Simulation

4.1. Input-Side Inductance Value Selection

4.2. Current Loop Design on the Input Side

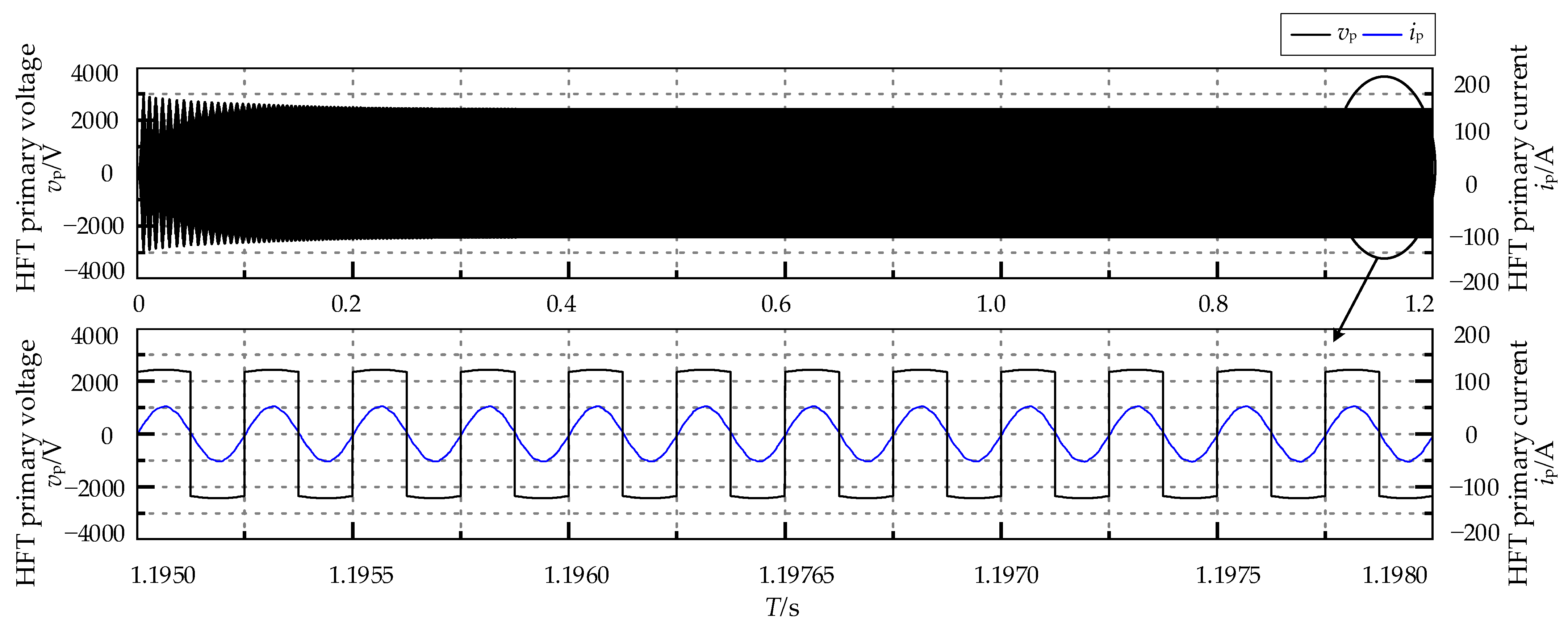

4.3. Simulation Analysis

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, X.; Liu, Y.; Zhang, Y. Pathway toward carbon-neutral power systems in China. iEnergy 2022, 1, 9–10. [Google Scholar] [CrossRef]

- Khazaei, J.; Nguyen, D.H. Multi-Agent Consensus Design for Heterogeneous Energy Storage Devices With Droop Control in Smart Grids. IEEE Trans. Smart Grid 2019, 10, 1395–1404. [Google Scholar] [CrossRef]

- Huang, A.; Crow, M.; Heydt, G.; Zheng, J.; Dale, S. The Future Renewable Electric Energy Delivery and Management (FREEDM) System: The Energy Internet. Proc. IEEE 2011, 99, 133–148. [Google Scholar] [CrossRef]

- Huang, A.Q. Medium-voltage solid-state transformer: Technology for a smarter and resilient grid. IEEE Ind. Electron. Mag. 2016, 10, 29–42. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Burgos, R. Review of Solid-State Transformer Technologies and Their Application in Power Distribution Systems. Emerg. Sel. Top. Circuits Syst. 2013, 1, 186–198. [Google Scholar]

- Huang, A.Q.; Zhu, Q.; Wang, L.; Zhang, L. 15 kV SiC MOSFET: An enabling technology for medium voltage solid state transformers. CPSS Trans. Power Electron. Appl. 2017, 2, 118–130. [Google Scholar] [CrossRef]

- Briz, F.; Lopez, M.; Rodriguze, A.; Arias, M. Modular power electronic transformers: Modular multilevel converter versus cascaded H-bridge solutions. IEEE Ind. Electron. Mag. 2016, 10, 6–19. [Google Scholar] [CrossRef]

- Vasiladiotis, M.; Rufer, A. A Modular Multiport Power Electronic Transformer With Integrated Split Battery Energy Storage for Versatile Ultrafast EV Charging Stations. IEEE Trans. Ind. Electron. 2014, 62, 3213–3222. [Google Scholar] [CrossRef]

- Deswal, D.; De León, F. Distributed Dual Model for High-Frequency Transformer Windings: Electromagnetic Transients and Solid State Transformers. IEEE Open Access J. Power Energy 2022, 9, 549–559. [Google Scholar] [CrossRef]

- Dujic, D.; Zhao, C.; Mester, A.; Steinke, J.; Weiss, M.; Lewdeni, S.; Chaudhuri, T.; Stefanutti, P. Power Electronic Traction Transformer-Low Voltage Prototype. IEEE Trans. Power Electron. 2013, 28, 5522–5534. [Google Scholar] [CrossRef]

- Madhusoodhanan, S.; Tripathi, A.; Patel, D.; Mainali, K.; Kadavelugu, A.; Hazra, S.; Bhattacharya, S.; Hatua, K. Solid State Transformer and MV grid tie applications enabled by 15 kV SiC IGBTs and 10 kV SiC MOSFETs based multilevel converters. IEEE Trans. Ind. Appl. 2015, 51, 3343–3360. [Google Scholar] [CrossRef]

- Wang, J.; Luo, F.; Duan, Q.; Ji, Z.; Gu, B.; You, J.; Gu, W.; Zhao, J. Power electronic transformer with adaptive PLL technique for voltage-disturbance ride through. J. Mod. Power Syst. Clean Energy 2018, 6, 1090–1102. [Google Scholar] [CrossRef]

- Wang, D.; Tian, J.; Mao, C.; Lu, J.; Duan, Y.; Qiu, J.; Cai, H. A 10-kV/400-V 500-kVA Electronic Power Transformer. IEEE Trans. Ind. Electron. 2016, 63, 6653–6663. [Google Scholar] [CrossRef]

- Zheng, G.; Chen, Y.; Kang, Y. Modeling and control of the modular multilevel converter (MMC) based solid state transformer (SST) with magnetic integration. CES Trans. Electr. Mach. Syst. 2020, 4, 309–318. [Google Scholar] [CrossRef]

- Wang, L.; Zhang, D.; Wang, Y.; Wu, B.; Athab, H.S. Power and Voltage Balance Control of a Novel Three-Phase Solid-State Transformer Using Multilevel Cascaded H-Bridge Inverters for Microgrid Applications. IEEE Trans. Power Electron. 2016, 31, 3289–3301. [Google Scholar] [CrossRef]

- Zhang, X.; Xu, Y.; Xiao, X. A High Power Density Resonance Cascaded H-Bridge Solid-State Transformer for Medium and High Voltage Distribution Network. Trans. China Electrotech. Soc. 2018, 33, 310–321. [Google Scholar] [CrossRef]

- Zhang, G.; Chen, J.; Zhang, B.; Zhang, Y. A critical topology review of power electronic transformers: In view of efficiency. Chin. J. Electr. Eng. 2018, 4, 90–95. [Google Scholar]

- Shu, L.; Chen, W.; Zhang, C. Power Electronic Transformer Based on Mixed-Frequency Modulation Strategy. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia, Busan, Republic of Korea, 27–30 May 2019; pp. 1559–1564. [Google Scholar]

- Ma, D.; Chen, W.; Shu, L. A Multiport Three-stage Power Electronic Transformer. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition, New Orleans, LA, USA, 15–19 March 2020; pp. 2285–2290. [Google Scholar]

- Zhang, J.; Liu, J.; Zhong, S.; Yang, J.; Zhao, N.; Zheng, T.Q. A Power Electronic Traction Transformer Configuration With Low-Voltage IGBTs for Onboard Traction Application. IEEE Trans. Power Electron. 2019, 34, 8453–8467. [Google Scholar] [CrossRef]

- Zhao, C.; Zhang, C.; Jiang, Q. An H-Bridge Time-Sharing Multiplexing-Based Power Electronic Transformer. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 4831–4840. [Google Scholar] [CrossRef]

- Mou, D.; Dai, Y.; Yuan, L.; Luo, Q.; Wang, H.; Wei, S.; Zhao, Z. Reactive Power Minimization for Modular Multi-Active-Bridge Converter With Whole Operating Range. IEEE Trans. Power Electron. 2023, 38, 8011–8015. [Google Scholar] [CrossRef]

- Velazquez-Ibañez, A.; Rodríguez-Rodríguez, J.R.; Santoyo-Anaya, M.A.; Arrieta-Paternina, M.R.; Torres-García, V.; Moreno-Goytia, E.L. Advanced PET Control for Voltage Sags Unbalanced Conditions Using Phase-Independent VSC-Rectification. IEEE Trans. Power Electron. 2021, 36, 11934–11943. [Google Scholar] [CrossRef]

- Feng, M.; Gao, C.; Ding, J.; Ding, H.; Xu, J.; Zhao, C. Hierarchical Modeling Scheme for High-Speed Electromagnetic Transient Simulations of Power Electronic Transformers. IEEE Trans. Power Electron. 2021, 36, 9994–10004. [Google Scholar] [CrossRef]

- Liu, H.; Ma, L.; Song, W.; Peng, L. An Internal Model Direct Power Control With Improved Voltage Balancing Strategy for Single-Phase Cascaded H-Bridge Rectifiers. IEEE Trans. Power Electron. 2022, 37, 9241–9253. [Google Scholar] [CrossRef]

- Pan, Y.; Teng, J.; Yang, C.; Bu, Z.; Wang, B.; Lin, X.; Sun, X. Capacitance Minimization and Constraint of CHB Power Electronic Transformer Based on Switching Synchronization Hybrid Phase-Shift Modulation Method of High Frequency Link. IEEE Trans. Power Electron. 2023, 38, 6224–6242. [Google Scholar] [CrossRef]

- Li, X.; Cheng, L.; He, L.; Wang, C.; Zhu, Z. Decoupling Control of an LLC-Quad-Active-Bridge Cascaded Power Electronic Transformer Based on Accurate Small-Signal Modeling. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 4115–4127. [Google Scholar] [CrossRef]

- Sun, Y.; Zhu, J.; Fu, C.; Chen, Z. Decoupling Control of Cascaded Power Electronic Transformer Based on Feedback Exact Linearization. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 3662–3676. [Google Scholar] [CrossRef]

- Zheng, L.; Marellapudi, A.; Chowdhury, V.; Kandula, R.; Saeedifard, M.; Grijalva, S.; Divan, D. Solid-State Transformer and Hybrid Transformer With Integrated Energy Storage in Active Distribution Grids: Technical and Economic Comparison, Dispatch, and Control. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 3771–3787. [Google Scholar] [CrossRef]

- Atkar, D.; Chaturvedi, P.; Suryawanshi, H.; Nachankar, P.; Yadeo, D.; Saketi, S. Three-Phase Integrated-Optimized Power Electronic Transformer for Electric Vehicle Charging Infrastructure. IEEE Trans. Ind. Appl. 2022, 58, 5198–5213. [Google Scholar] [CrossRef]

| Type | Parameter | Values (Units) | Parameter | Values (Units) |

|---|---|---|---|---|

| PET-I | Grid line voltage rms | 6 kV | Output-side DC voltage | 750 V |

| Input-side filter inductance | 9 mH | Output-side Capacitance | 15 mF | |

| Ratio of HFT | 3.2 | LC filter inductance | 3.166 mH | |

| Sub-module capacitance | 2 mF | LC filter capacitance | 0.5 μF | |

| Sub-module capacitance voltage | 750 V | Number of sub-modules on A phase | 12 | |

| PET-II | Grid line voltage rms | 6 kV | Output-side DC voltage | 750 V |

| Input-side filter inductance | 5 mH | Ratio of HFT | 1 | |

| Output-side capacitance | 2 mF | Number of HFT on A phase | 12 | |

| Output-side capacitance voltage | 750 V | Number of sub-modules on A phase | 12 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hou, B.; Li, Y.; Yu, Z.; Teng, Y. A H-Bridge-Multiplexing-Based Novel Power Electronic Transformer. Electronics 2024, 13, 22. https://doi.org/10.3390/electronics13010022

Hou B, Li Y, Yu Z, Teng Y. A H-Bridge-Multiplexing-Based Novel Power Electronic Transformer. Electronics. 2024; 13(1):22. https://doi.org/10.3390/electronics13010022

Chicago/Turabian StyleHou, Bingbing, Yan Li, Zhanyang Yu, and Yun Teng. 2024. "A H-Bridge-Multiplexing-Based Novel Power Electronic Transformer" Electronics 13, no. 1: 22. https://doi.org/10.3390/electronics13010022