Modeling and Experimental Validation of Dual-Output Flyback Converters with Capacitive Coupling for Improved Cross-Regulation

Abstract

:1. Introduction

2. Dual-Output Flyback Converter

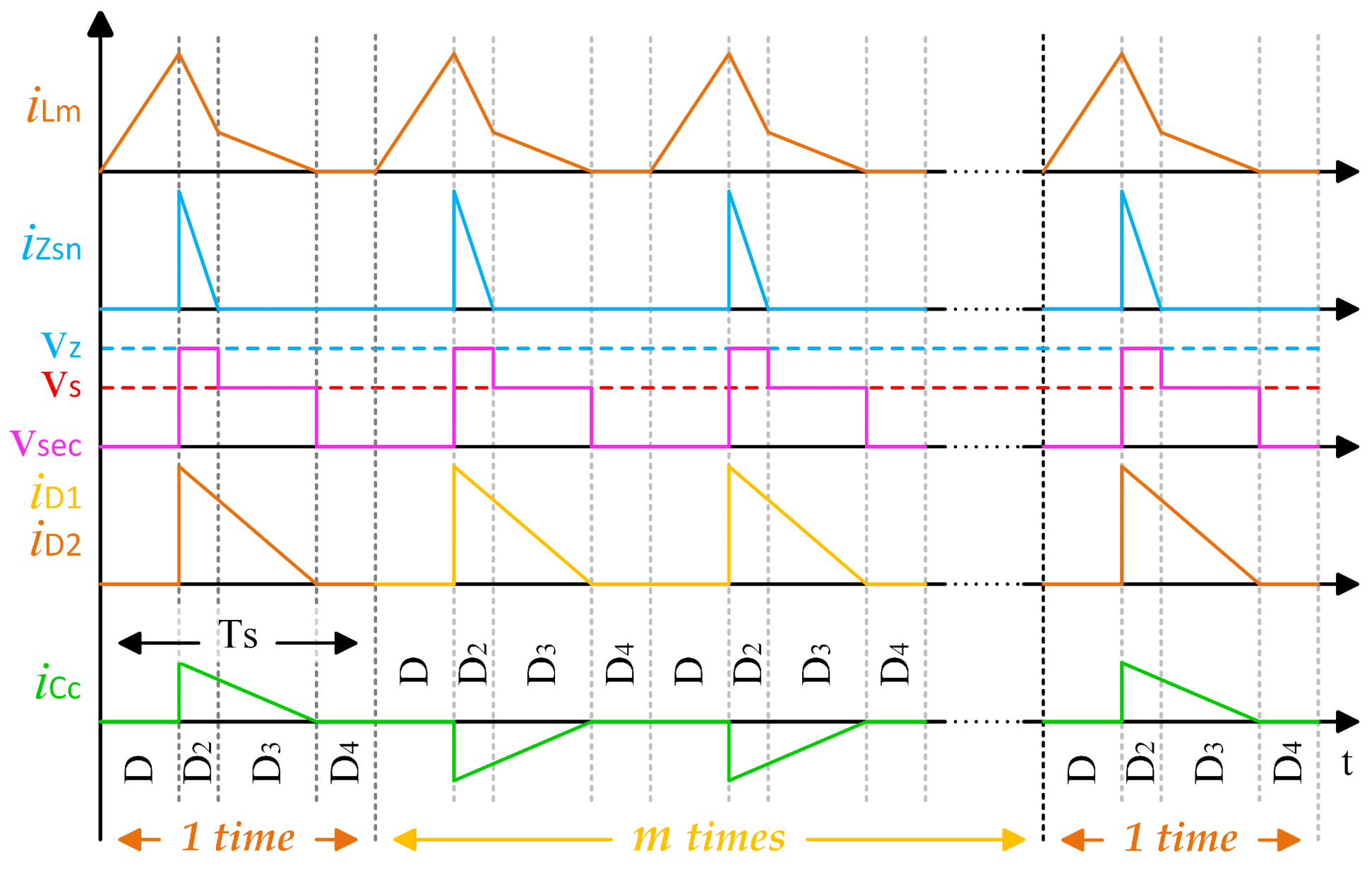

Analytical Modeling

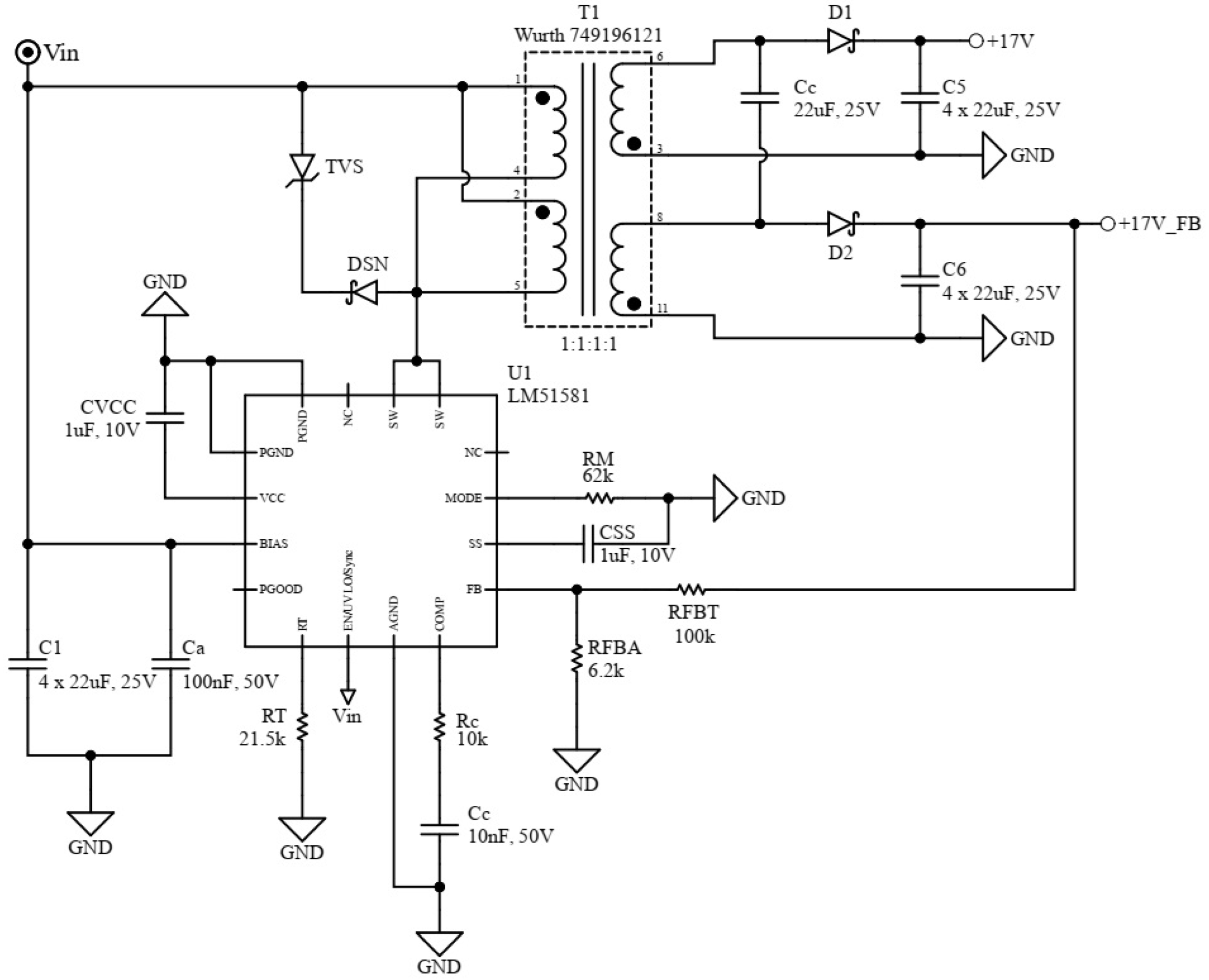

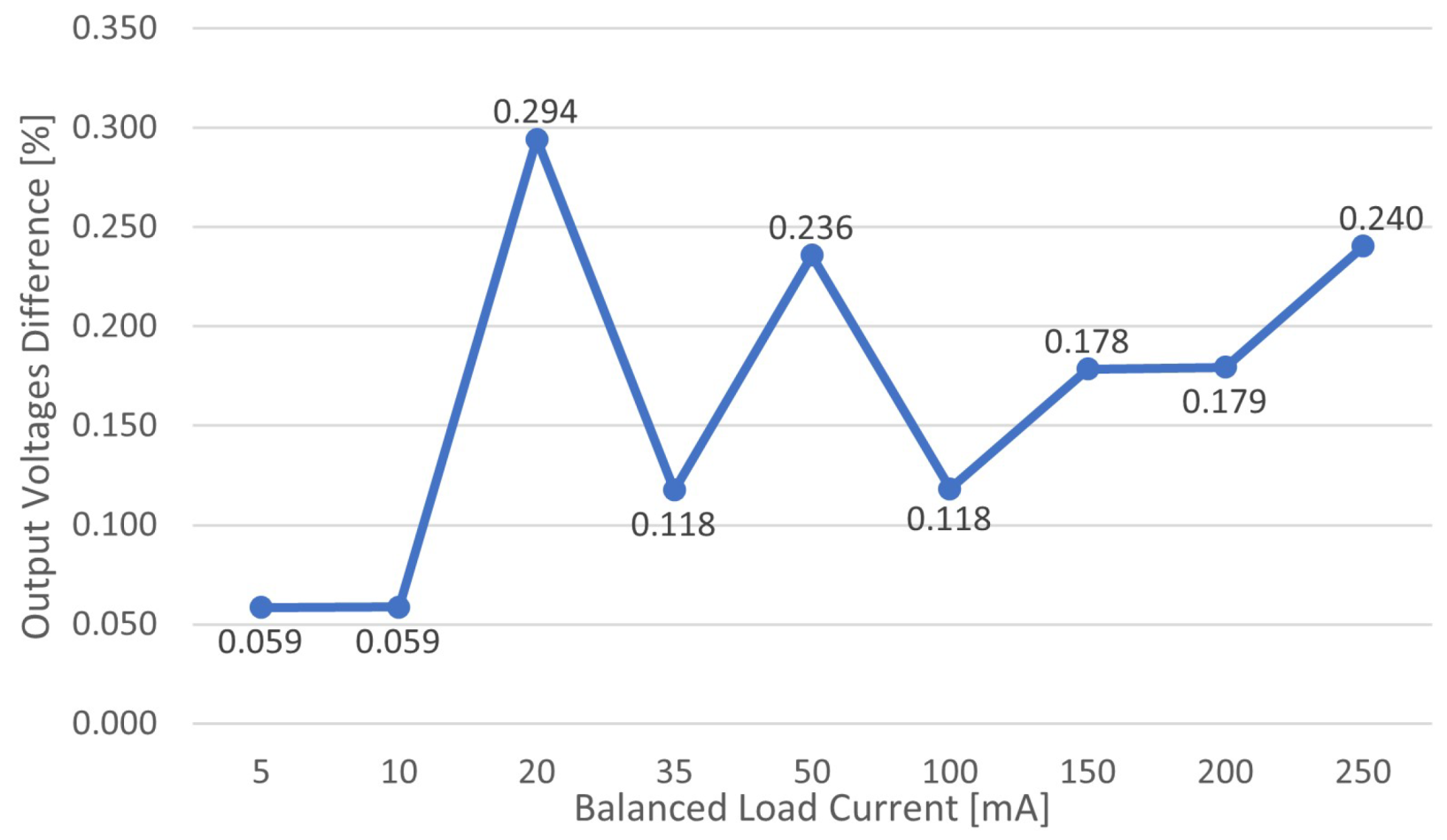

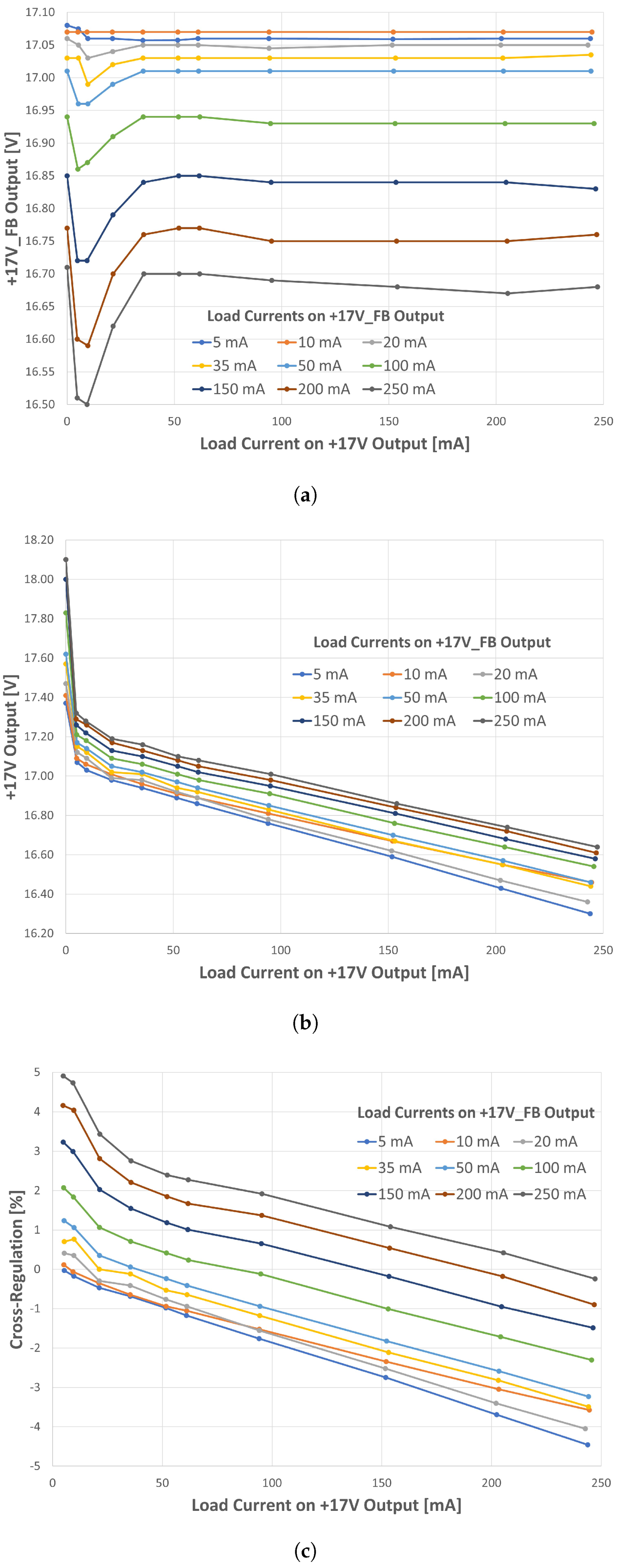

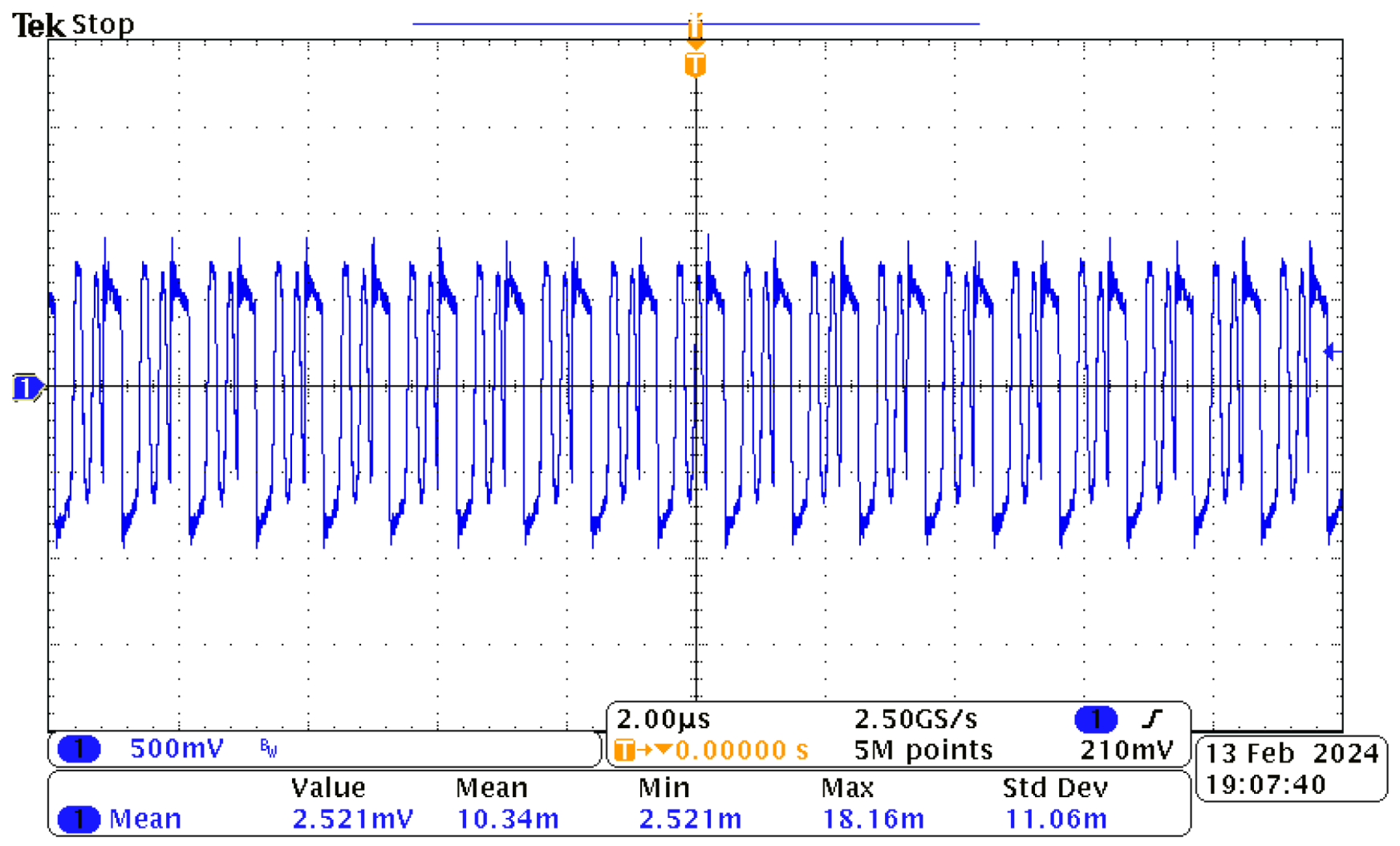

3. Experimental Section

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Schlesinger, K. Magnetic Deflection of Kinescopes. Proc. IRE 1947, 35, 813–821. [Google Scholar] [CrossRef]

- Dimitrov, B.; Krishna, M.; Cruden, A.; Sharkh, S.; Elkhateb, A. Analysis, Design, and Experimental Validation of a Primary Side Current-Sensing Flyback Converter for Use in a Battery Management System. Electronics 2018, 7, 43. [Google Scholar] [CrossRef]

- Yang, C.; Xie, F.; Chen, Y.; Xiao, W.; Zhang, B. Modeling and Analysis of the Fractional-Order Flyback Converter in Continuous Conduction Mode by Caputo Fractional Calculus. Electronics 2020, 9, 1544. [Google Scholar] [CrossRef]

- Shi, F.; Song, D. A Novel High-Efficiency Double-Input Bidirectional DC/DC Converter for Battery Cell-Voltage Equalizer with Flyback Transformer. Electronics 2019, 8, 1426. [Google Scholar] [CrossRef]

- Xue, L.; Zhang, J. Highly Efficient Secondary-Resonant Active Clamp Flyback Converter. IEEE Trans. Ind. Electron. 2018, 65, 1235–1243. [Google Scholar] [CrossRef]

- Gao, S.; Song, H.; Wang, Y.; Xu, R.; Xu, D. A Secondary-Resonance MHz Active-Clamp Flyback Converter with Partial Power Processing. IEEE Trans. Ind. Appl. 2022, 58, 7988–7997. [Google Scholar] [CrossRef]

- Granello, P.; Soeiro, T.B.; van der Blij, N.H.; Bauer, P. Revisiting the Partial Power Processing Concept: Case Study of a 5-kW 99.11% Efficient Flyback Converter-Based Battery Charger. IEEE Trans. Transp. Electrif. 2022, 8, 3934–3945. [Google Scholar] [CrossRef]

- Özen, S.H.; Doğru, U.E.; Yaşar, R.Ö.; Akboy, E. Multiple Output Application of Quasi-Resonant Flybacks on TV Applications. In Proceedings of the 2023 14th International Conference on Electrical and Electronics Engineering (ELECO), Bursa, Turkey, 30 November–2 December 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Duzgun, R.; Parlak, M.; Yilmazlar, I. Design of Multiple-Output Flyback Converter with Independently Controlled Outputs for TV Power Supply. In Proceedings of the 2023 18th Conference on Electrical Machines, Drives and Power Systems (ELMA), Varna, Bulgaria, 29 June–1 July 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Sarkar, A.; Vankayalapati, B.T.; Anand, S. GaN-Based Multiple Output Flyback Converter with Independently Controlled Outputs. IEEE Trans. Ind. Electron. 2022, 69, 2565–2576. [Google Scholar] [CrossRef]

- Kim, J.-K.; Lee, J.-B.; Moon, G.-W. Zero-Voltage Switching Multioutput Flyback Converter with Integrated Auxiliary Buck Converter. IEEE Trans. Power Electron. 2014, 29, 3001–3010. [Google Scholar] [CrossRef]

- Ji, C.; Smith, K.M.; Smedley, K.M. Cross regulation in flyback converters: Solutions. In Proceedings of the IECON’99. Conference Proceedings. 25th Annual Conference of the IEEE Industrial Electronics Society (Cat. No.99CH37029), San Jose, CA, USA, 29 November–3 December 1999; Volume 1, pp. 174–179. [Google Scholar] [CrossRef]

- Ji, C.; Smith, M.; Smedley, K.M.; King, K. Cross regulation in flyback converters: Analytic model and solution. IEEE Trans. Power Electron. 2001, 16, 231–239. [Google Scholar] [CrossRef]

- Maksimovic, D.; Erickson, R.W.; Griesbach, C. Modeling of cross-regulation in converters containing coupled inductors. IEEE Trans. Power Electron. 2000, 15, 607–615. [Google Scholar] [CrossRef]

- Hu, Y.; Zhang, J.; Chen, W.; Wen, C. Mathematical modeling of cross-regulation problem in flyback converters. In Proceedings of the 2001 IEEE 32nd Annual Power Electronics Specialists Conference (IEEE Cat. No.01CH37230), Vancouver, BC, Canada, 17–21 June 2001; Volume 4, pp. 2072–2077. [Google Scholar] [CrossRef]

- Guo, X.; Wu, S.; Zhang, Y.; Dou, C.; Chi, Y. Optimal Design of High Frequency Transformer for High Power Density Flyback Converter. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 4399–4403. [Google Scholar] [CrossRef]

- Kim, J.-W.; Ha, J.-I. Dual voltage regulations of single switch flyback converter using variable switching frequency. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1398–1402. [Google Scholar] [CrossRef]

- Jung, J.-H.; Ahmed, S. Flyback converter with novel active clamp control and secondary side post regulator for low standby power consumption under high-efficiency operation. IET Power Electron. 2011, 4, 1058–1067. [Google Scholar] [CrossRef]

- Tahan, M.; Bamgboje, D.; Hu, T. Flyback-Based Multiple Output dc-dc Converter with Independent Voltage Regulation. In Proceedings of the 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, USA, 25–28 June 2018; pp. 1–8. [Google Scholar] [CrossRef]

- Kolincio, M.; Chrzan, P.J.; Musznicki, P. Multitransformer Primary-Side Regulated Flyback Converter for Supplying Isolated IGBT and MOSFET Drivers. IEEE Trans. Ind. Electron. 2020, 67, 1005–1012. [Google Scholar] [CrossRef]

- Wen, C.-C.; Chen, C.-L. Magamp application and limitation for multiwinding flyback converter. IEE Proc. Electr. Power Appl. 2005, 152, 517–525. [Google Scholar] [CrossRef]

- Chalermyanont, K.; Sangampai, P.; Prasertsit, A.; Theinmontri, S. High Frequency Transformer Designs for Improving Cross Regulation in Multiple-Output Flyback Converters. In Proceedings of the 2007 7th International Conference on Power Electronics and Drive Systems, Bangkok, Thailand, 27–30 November 2007; pp. 53–56. [Google Scholar] [CrossRef]

- Xu, Y.; An, S.; An, S.; Wu, Y.; Wu, Q.; Zhang, Q. A High-Efficiency Multiple Output Flyback Converter Based on Variable Width Winding Planar Magnetics. In Proceedings of the 2023 IEEE 14th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Shanghai, China, 9–12 June 2023; pp. 773–779. [Google Scholar] [CrossRef]

- Guo, X.; Luan, F.; Liu, J.; Liu, M. Analysis and improvement of cross-regulation effect in the primary side-regulated multi-output flyback converter. Int. J. Circ. Theor. Appl. 2017, 45, 1299–1312. [Google Scholar] [CrossRef]

- Zhu, G.; Liu, X.; Qin, Z.; Zhang, Q.; Liu, S.; Fang, W. Research on Low Cross Regulation Multiple High Voltage Output Converter Based on Magnetic Decoupling. In Proceedings of the 2023 IEEE 2nd International Power Electronics and Application Symposium (PEAS), Guangzhou, China, 10–13 November 2023; pp. 1222–1227. [Google Scholar] [CrossRef]

- Lee, M.; Lio, J.; Chen, D.Y.; Chen, Y.; Wu, Y. Small-signal modeling of multiple-output flyback converters in continuous conduction mode with weighted feedback. IEEE Trans. Ind. Electron. 1998, 45, 236–248. [Google Scholar] [CrossRef]

- Leng, C.-M.; Chiu, H.-J. Three-Output Flyback Converter with Synchronous Rectification for Improving Cross-Regulation and Efficiency. Electronics 2021, 10, 430. [Google Scholar] [CrossRef]

- Mullett, C.; Cathell, F. Improving the Regulation of Multi-Output Flyback Converters. In Proceedings of the 2009 Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009; pp. 1923–1926. [Google Scholar] [CrossRef]

- Halder, T. An elimination technique of cross regulations in the flyback converters. In Proceedings of the 2014 IEEE 6th India International Conference on Power Electronics (IICPE), Kurukshetra, India, 8–10 December 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Wilson, T.G., Jr. Cross regulation in a two-output DC-to-DC converter with application to testing of energy-storage transformers. In Proceedings of the 1978 IEEE Power Electronics Specialists Conference, Syracuse, NY, USA, 13–15 June 1978; pp. 124–134. [Google Scholar] [CrossRef]

| Component | Manufacturer | Value |

|---|---|---|

| T1 | Würth Elektronik | 749196121 |

| U1 | Texas Instruments | LM51581 |

| D3, D4, DSN | Vishay | V2PM10LHM3/H |

| TVS | Vishay | TPSMP24AHM3_A/H |

| , C1, C5, C6 | Samsung | CL21A226MAYNNNE |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| 1 MHz | 14.7 H | ||

| 15 V | 210 nH | ||

| 17 V | 210 nH |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Granello, P.; Schirone, L. Modeling and Experimental Validation of Dual-Output Flyback Converters with Capacitive Coupling for Improved Cross-Regulation. Electronics 2024, 13, 3503. https://doi.org/10.3390/electronics13173503

Granello P, Schirone L. Modeling and Experimental Validation of Dual-Output Flyback Converters with Capacitive Coupling for Improved Cross-Regulation. Electronics. 2024; 13(17):3503. https://doi.org/10.3390/electronics13173503

Chicago/Turabian StyleGranello, Pierpaolo, and Luigi Schirone. 2024. "Modeling and Experimental Validation of Dual-Output Flyback Converters with Capacitive Coupling for Improved Cross-Regulation" Electronics 13, no. 17: 3503. https://doi.org/10.3390/electronics13173503