Circuit Implementation of Variable-Order Scaling Fractal-Ladder Fractor with High Resolution

Abstract

:1. Introduction

- A programmable resistor–capacitor series circuit and programmable universal electronic component emulators are designed based on the high-resolution multiplying digital-to-analog converter (HMDAC). These emulators can also be applied to other variable-order fractor circuits, memristor emulators, and memcapacitor emulators [35,36,37].

- This paper also proposes a method for variable-order fractional calculus based on circuit theory.

2. VSFF Design

2.1. VSFF Circuit Configuration

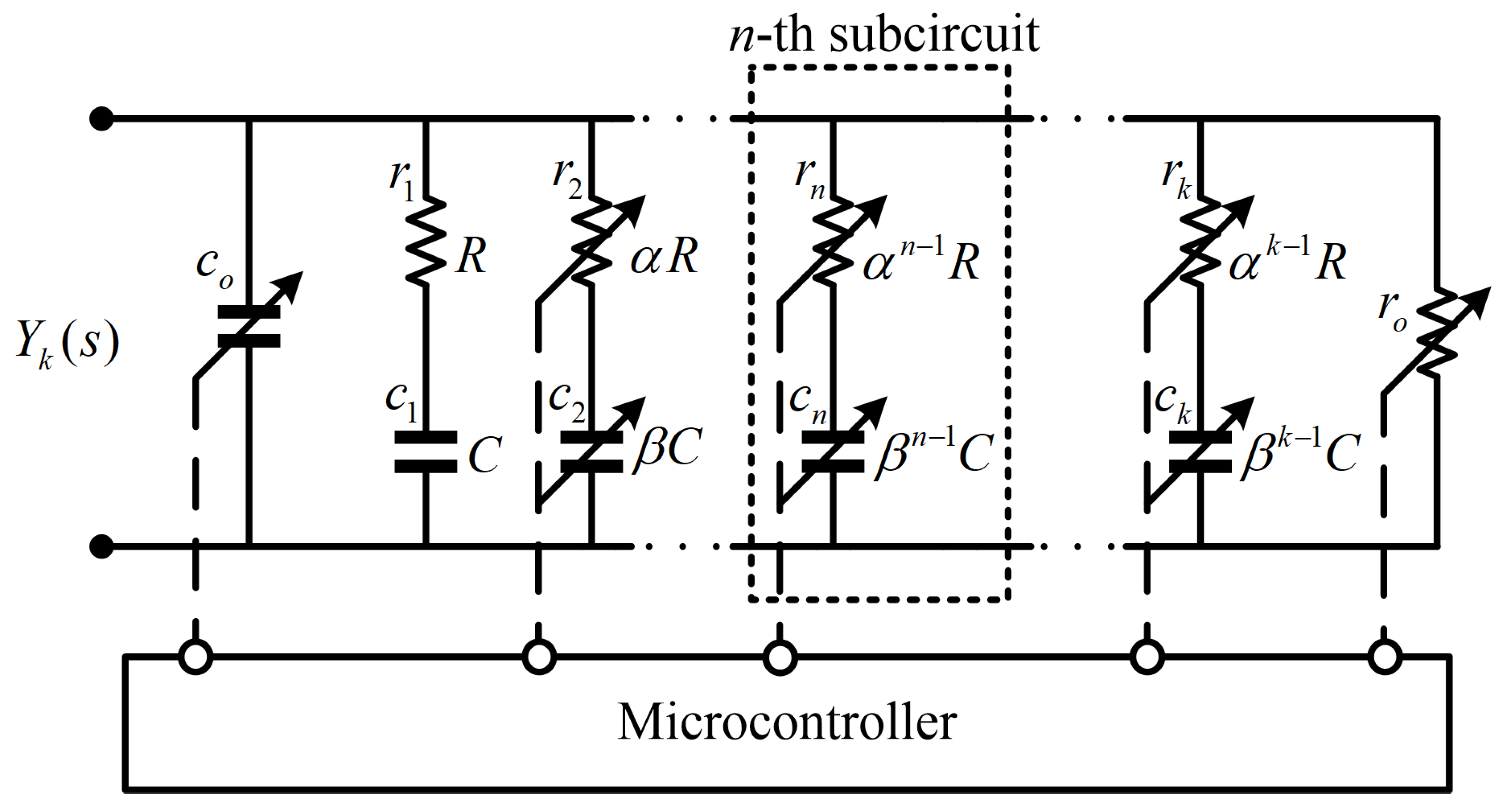

2.1.1. Circuit Configuration and Admittance

2.1.2. Characteristic Frequency and Operational Order

2.1.3. VSFF Optimization

2.1.4. Component Parameter Calculation

2.2. Programmable Resistor–Capacitor Series Circuit Emulator

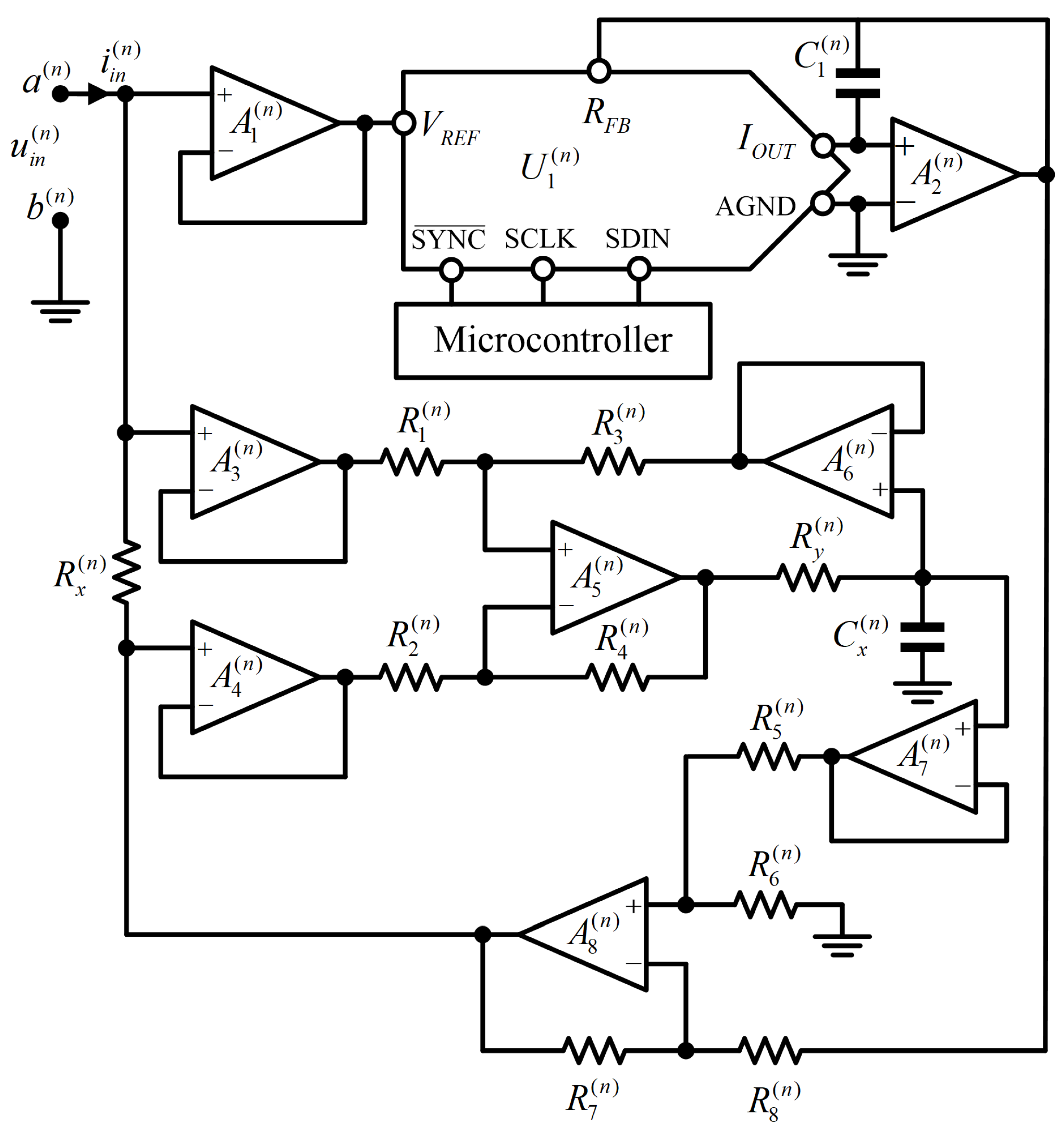

2.2.1. Circuit Schematic

2.2.2. Calculating the Control Variable of

2.2.3. Calculating the Relative Errors of and

2.3. Programmable Universal Electronic Component Emulator–Programmable Resistor and Capacitor for Circuit Optimization

2.3.1. Circuit Schematic

2.3.2. Calculating the Control Variables of and

2.3.3. Calculating the Relative Errors of and

3. Experimental Results

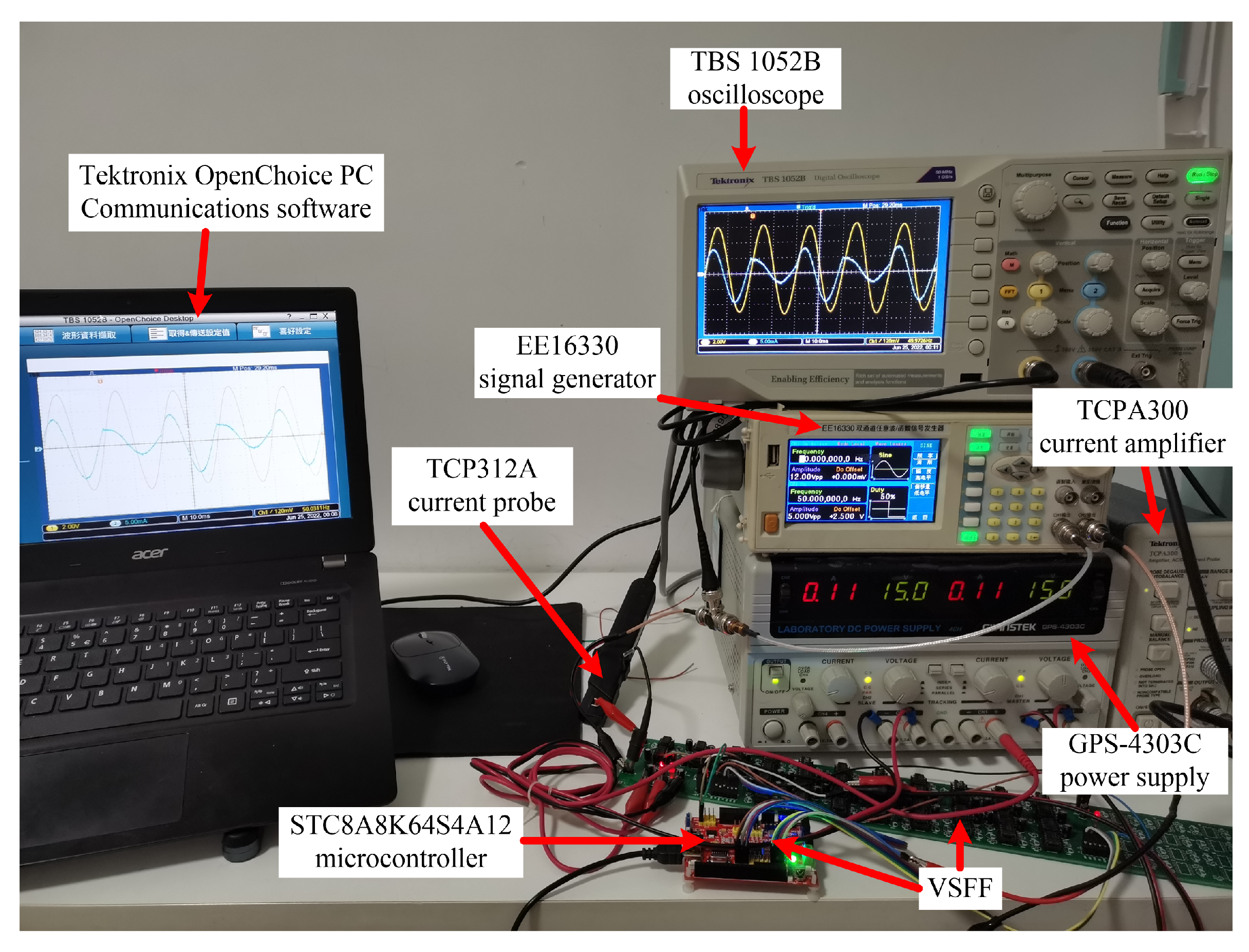

3.1. Circuit Implementation

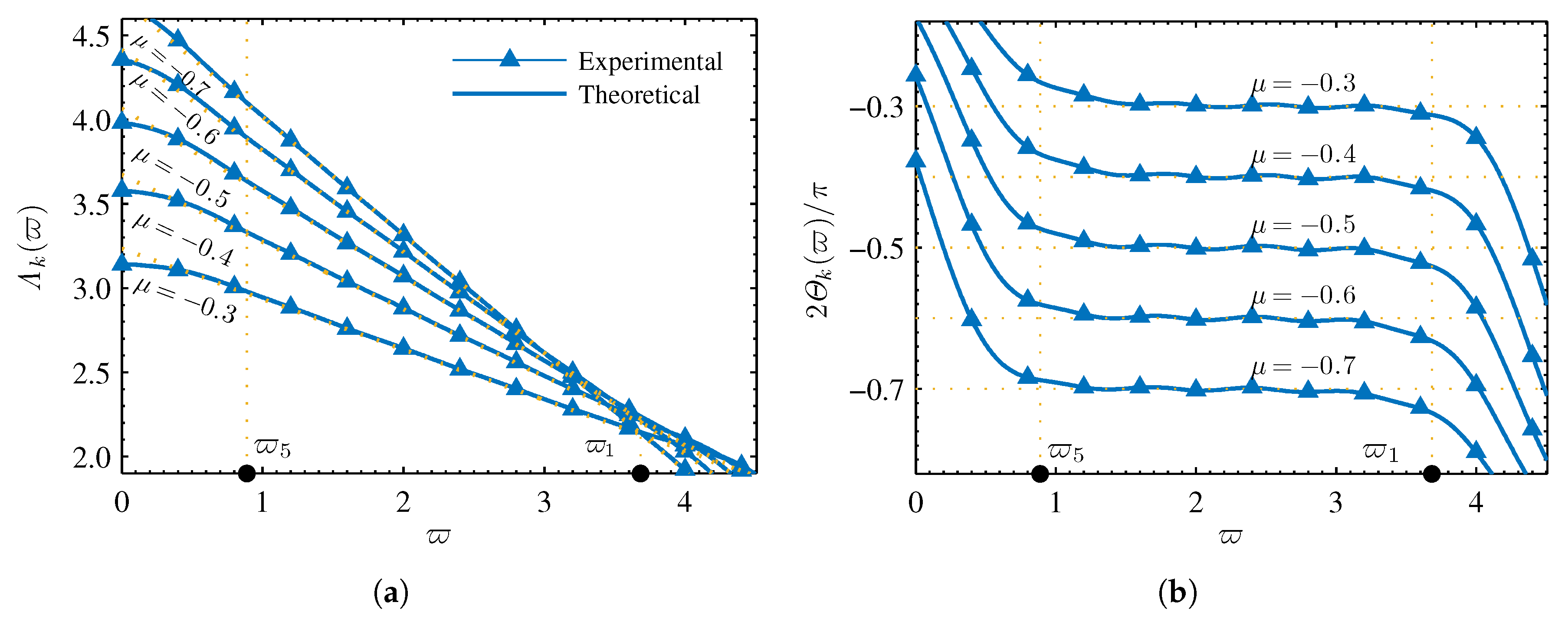

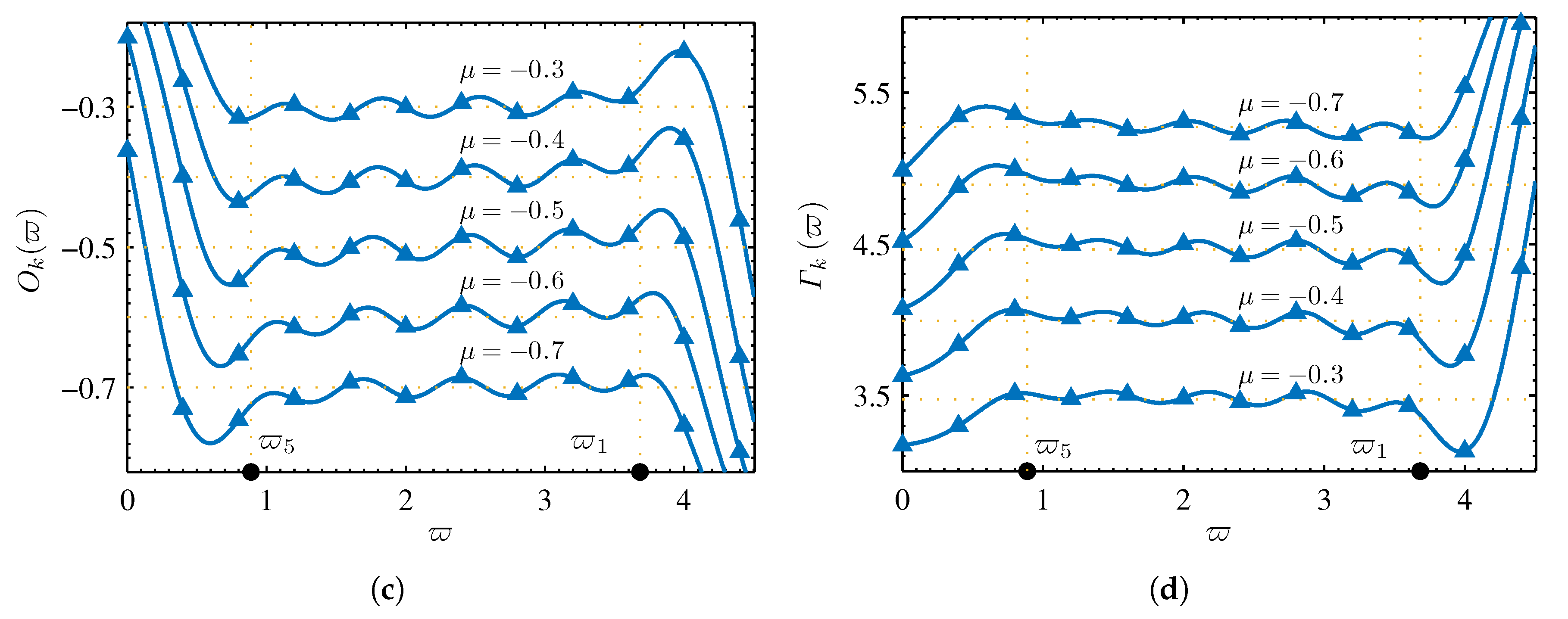

3.2. Frequency Characteristic Analysis

3.3. Two Equivalent Methods for Calculating Variable-Order Electrical Characteristics

3.3.1. Variable-Order Electrical Characteristics Obtained through Circuit Theory

3.3.2. Variable-Order Electrical Characteristics Obtained through the Grünwald–Letnikov Definition

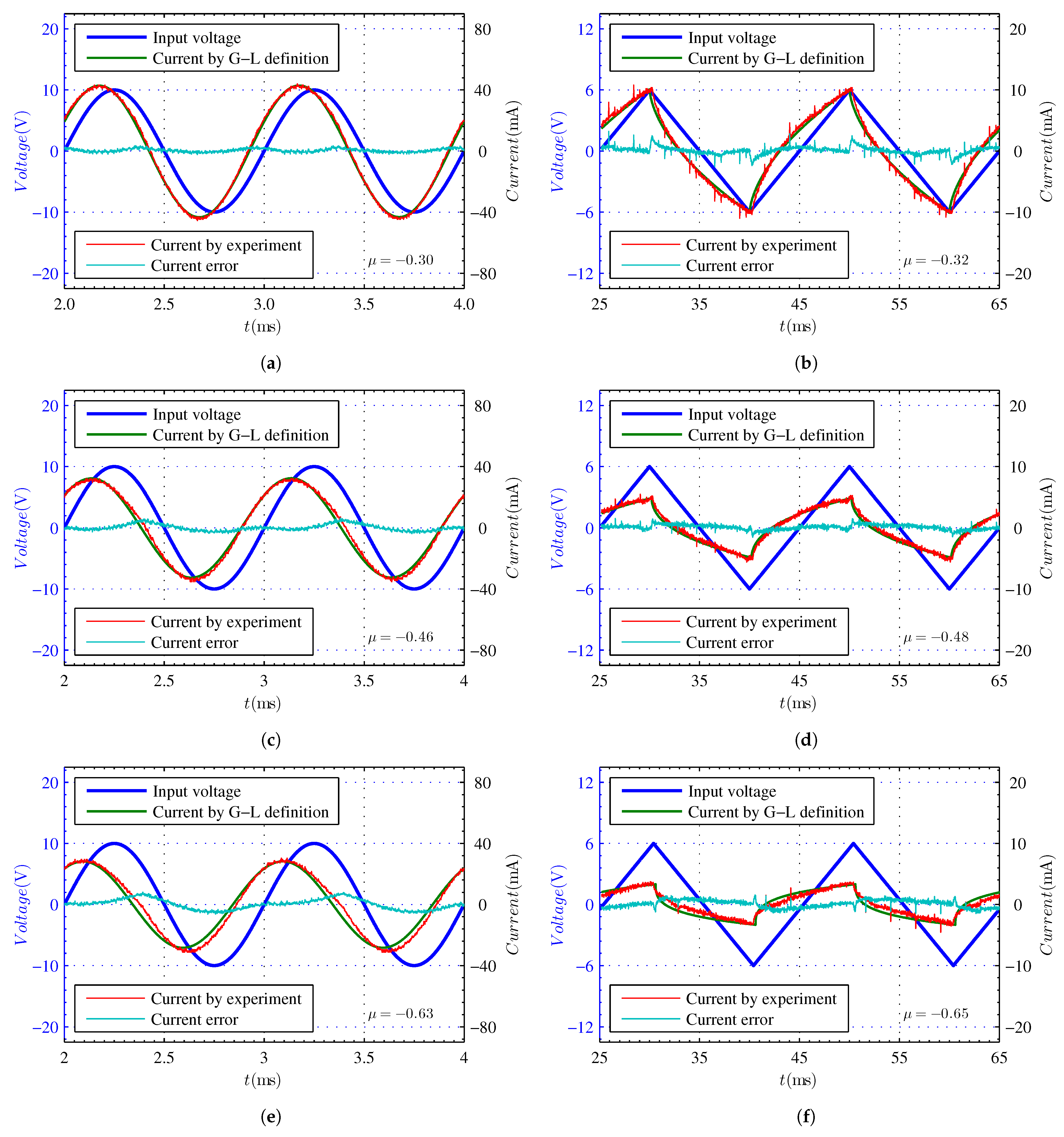

3.4. Experimental Verification

3.4.1. Steady-State Variable-Order Experiment

3.4.2. Dynamic Variable-Order Experiment

3.4.3. Continuous Variable-Order Experiment

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| VSFF | Variable-Order Scaling Fractal-Ladder Fractor |

| HMDAC | High-Resolution Multiplying Digital-to-Analog Converter |

References

- Sun, H.G.; Yong, Z.; Baleanu, D.; Wen, C.; Chen, Y.Q. A new collection of real world applications of fractional calculus in science and engineering. Commun. Nonlinear. Sci. Numer. Simul. 2018, 64, 213–231. [Google Scholar] [CrossRef]

- Baleanu, D.; Agarwal, R.P. Fractional calculus in the sky. Adv. Differ. Equ. 2021, 2021, 117. [Google Scholar] [CrossRef]

- Yu, B.; Pu, Y.F.; He, Q.Y. Fractional-Order Dual-Slope Integral Fast Analog-to-Digital Converter with High Sensitivity. J. Circuit. Syst. Comp. 2020, 29, 2050082. [Google Scholar] [CrossRef]

- Sun, H.G.; Chang, A.; Zhang, Y.; Chen, W. A review on variable-order fractional differential equations: Mathematical foundations, physical models, and its applications. Fract. Calc. Appl. Anal. 2018, 22, 27–59. [Google Scholar] [CrossRef] [Green Version]

- Wu, G.C.; Deng, Z.G.; Baleanu, D.; Zeng, D.Q. New variable-order fractional chaotic systems for fast image encryption. Chaos Interdiscip. J. Nonlinear Sci. 2019, 29, 083103. [Google Scholar] [CrossRef]

- Patnaik, S.; Hollkamp, J.P.; Semperlotti, F. Applications of variable-order fractional operators: A review. Proc. Roy. Soc. A-Math. Phy. 2020, 476, 20190498. [Google Scholar] [CrossRef] [Green Version]

- Samko, S.G.; Ross, B. Integration and differentiation to a variable fractional order. Integral Transform. Spec. Funct. 1993, 1, 277–300. [Google Scholar] [CrossRef]

- Huang, L.L.; Ju, H.P.; Wu, G.C.; Mo, Z.W. Variable–order fractional discrete–time recurrent neural networks. J. Comput. Appl. Math. 2019, 370, 112633. [Google Scholar] [CrossRef]

- Wu, F.; Gao, R.B.; Liu, J.; Li, C.B. New fractional variable-order creep model with short memory. Appl. Math. Comput. 2020, 380, 125278. [Google Scholar] [CrossRef]

- Gu, X.M.; Sun, H.W.; Zhao, Y.L.; Zheng, X. An implicit difference scheme for time-fractional diffusion equations with a time-invariant type variable order. Appl. Math. Lett. 2021, 120, 107270. [Google Scholar] [CrossRef]

- Zheng, X.C.; Wang, H.; Guo, X. Analysis of a Time-Fractional Substantial Diffusion Equation of Variable Order. Fractal Fract. 2022, 6, 114. [Google Scholar] [CrossRef]

- Zheng, X.C.; Wang, H. Discretization and Analysis of an Optimal Control of a Variable-Order Time-Fractional Diffusion Equation with Pointwise Constraints. J. Sci. Comput. 2022, 91, 56. [Google Scholar] [CrossRef]

- Sheng, H.; Sun, H.G.; Coopmans, C.; Chen, Y.Q.; Bohannan, G.W. A Physical experimental study of variable-order fractional integrator and differentiator. Eur. Phys. J. Spec. Top. 2011, 193, 93–104. [Google Scholar] [CrossRef]

- Buscarino, A.; Caponetto, R.; Di Pasquale, G.; Fortuna, L.; Graziani, S.; Pollicino, A. Carbon Black based capacitive Fractional Order Element towards a new electronic device. Int. J. Electron. Commun. 2018, 84, 307–312. [Google Scholar] [CrossRef]

- Sierociuk, D.; Malesza, W.; Macias, M. On the Recursive Fractional Variable-Order Derivative: Equivalent Switching Strategy, Duality, and Analog Modeling. Circuits Syst. Signal Process. 2015, 34, 1077–1113. [Google Scholar] [CrossRef] [Green Version]

- Sierociuk, D.; Macias, M.; Malesza, W. Analog realization of fractional variable-type and -order iterative operator. Appl. Math. Comput. 2018, 336, 138–147. [Google Scholar] [CrossRef]

- Sierociuk, D.; Macias, M.; Malesza, W. Fractional Recursive Variable-Type and Order Operator for a Particular Switching Strategy. Electronics 2020, 9, 855. [Google Scholar] [CrossRef]

- Zhou, C.Y.; Li, Z.J.; Xie, F. Coexisting attractors, crisis route to chaos in a novel 4D fractional-order system and variable-order circuit implementation. Eur. Phys. J. Plus. 2019, 134, 73. [Google Scholar] [CrossRef]

- Tsirimokou, G.; Psychalinos, C.; Freeborn, T.J.; Elwakil, A.S. Emulation of current excited fractional-order capacitors and inductors using OTA topologies. Microelectron. J. 2016, 55, 70–81. [Google Scholar] [CrossRef]

- Yuan, X. Mathematical Principles of Fractance Approximation Circuits; Science Press: Beijing, China, 2015. (In Chinese) [Google Scholar]

- Kaplan, T.; Gray, L.J. Effect of disorder on a fractal model for the ac response of a rough interface. Phys. Rev. B 1985, 32, 7360–7366. [Google Scholar] [CrossRef]

- Charef, A. Analogue realisation of fractional-order integrator, differentiator and fractional PID controller. IEE Proc.-Control. Theory Appl. 2006, 153, 714–720. [Google Scholar] [CrossRef]

- Valsa, J.; Vlach, J. RC models of a constant phase element. Int. J. Circ. Theor. App. 2013, 41, 59–67. [Google Scholar] [CrossRef]

- Adhikary, A.; Sen, P.; Sen, S.; Biswas, K. Design and Performance Study of Dynamic Fractors in Any of the Four Quadrants. Circuits Syst. Signal Process. 2016, 35, 1909–1932. [Google Scholar] [CrossRef]

- Oustaloup, A.; Levron, F.; Mathieu, B.; Nanot, F.M. Frequency-band complex noninteger differentiator: Characterization and synthesis. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 2002, 47, 25–39. [Google Scholar] [CrossRef]

- Morales-Delgado, V.F.; Gómez-Aguilar, J.; Taneco-Hernandez, M.A. Analytical solutions of electrical circuits described by fractional conformable derivatives in Liouville-Caputo sense. Int. J. Electron. Commun. 2017, 134, 108–117. [Google Scholar] [CrossRef]

- Roy, D.S. Constant argument immittance realization by a distributed RC network. IEEE Trans. Circuits Syst. 1974, 21, 655–658. [Google Scholar] [CrossRef]

- Carlson, G.E.; Halijak, C. Approximation of Fractional Capacitors by a Regular Newton Process. IEEE Trans. Circuit Theory 1964, 11, 210–213. [Google Scholar] [CrossRef]

- He, Q.Y.; Yu, B.; Yuan, X. Carlson iterating rational approximation and performance analysis of fractional operator with arbitrary order. Chin. Phys. B 2017, 26, 66–74. [Google Scholar] [CrossRef]

- Pu, Y.F.; Yuan, X.; Yu, B. Analog Circuit Implementation of Fractional-Order Memristor: Arbitrary-Order Lattice Scaling Fracmemristor. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2903–2916. [Google Scholar] [CrossRef]

- Yu, B.; He, Q.; Yuan, X. Scaling fractal-lattice franctance approximation circuits of arbitrary order and irregular lattice type scaling equation. Acta Phys. Sin. 2018, 67, 070202. [Google Scholar]

- He, Q.Y.; Pu, Y.F.; Yu, B.; Yuan, X. Scaling Fractal-Chuan Fractance Approximation Circuits of Arbitrary Order. Circuits Syst. Signal Process. 2019, 38, 4933–4958. [Google Scholar] [CrossRef]

- He, Q.Y.; Pu, Y.F.; Yu, B.; Yuan, X. A class of fractal-chain fractance approximation circuit. Int. J. Electron. 2020, 107, 1588–1608. [Google Scholar] [CrossRef]

- Pu, Y.F.; Yu, B.; Yuan, X. Ladder Scaling Fracmemristor: A Second Emerging Circuit Structureof Fractional-Order Memristor. IEEE Des. Test 2021, 38, 104–111. [Google Scholar] [CrossRef]

- Yu, D.S.; Zhao, X.Q.; Sun, T.T.; Iu, H.H.C.; Fernando, T. A Simple Floating Mutator for Emulating Memristor, Memcapacitor, and Meminductor. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1334–1338. [Google Scholar] [CrossRef]

- Liang, Y.; Wang, G.; Xia, C.; Lu, Z. Simple modelling of S-type NbOx locally active memristor. Electron. Lett. 2021, 57, 630–632. [Google Scholar] [CrossRef]

- Bao, B.C.; Zhu, Y.X.; Ma, J.; Bao, H.; Chen, M. Memristive neuron model with an adapting synapse and its hardware experiments. Sci. China Technol. Sci. 2021, 64, 1107–1117. [Google Scholar] [CrossRef]

- Shen, J.; Cong, J.; Chai, Y.; Shang, D.; Shen, S.; Zhai, K.; Tian, Y.; Sun, Y. A non-volatile memory based on nonlinear magnetoelectric effects. Phys. Rev. Appl. 2016, 6, 021001. [Google Scholar] [CrossRef] [Green Version]

- ADI. AD5544/AD5554 Data Sheet. [EB/OL]. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD5544_5554.pdf (accessed on 6 July 2022).

- Yu, B.; He, Q.; Yuan, X.; Yang, L. Approximation performance analyses and applications of f characteristics in fractance approximation circuit. J. Sichuan Univ. 2018, 55, 301–306. [Google Scholar]

| , , | ||

| , | , | , |

| 1-st subcircuit | ||

| 2-nd subcircuit | , | , |

| , | ||

| 3-rd subcircuit | , | , |

| , | ||

| 4-th subcircuit | , | , |

| , | ||

| 5-th subcircuit | , | , |

| , | ||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, B.; Pu, Y.; He, Q.; Yuan, X. Circuit Implementation of Variable-Order Scaling Fractal-Ladder Fractor with High Resolution. Fractal Fract. 2022, 6, 388. https://doi.org/10.3390/fractalfract6070388

Yu B, Pu Y, He Q, Yuan X. Circuit Implementation of Variable-Order Scaling Fractal-Ladder Fractor with High Resolution. Fractal and Fractional. 2022; 6(7):388. https://doi.org/10.3390/fractalfract6070388

Chicago/Turabian StyleYu, Bo, Yifei Pu, Qiuyan He, and Xiao Yuan. 2022. "Circuit Implementation of Variable-Order Scaling Fractal-Ladder Fractor with High Resolution" Fractal and Fractional 6, no. 7: 388. https://doi.org/10.3390/fractalfract6070388

APA StyleYu, B., Pu, Y., He, Q., & Yuan, X. (2022). Circuit Implementation of Variable-Order Scaling Fractal-Ladder Fractor with High Resolution. Fractal and Fractional, 6(7), 388. https://doi.org/10.3390/fractalfract6070388