A Generic Control-Oriented Model Order Reduction Approach for High Step-Up DC/DC Converters Based on Voltage Multiplier

Abstract

:1. Introduction

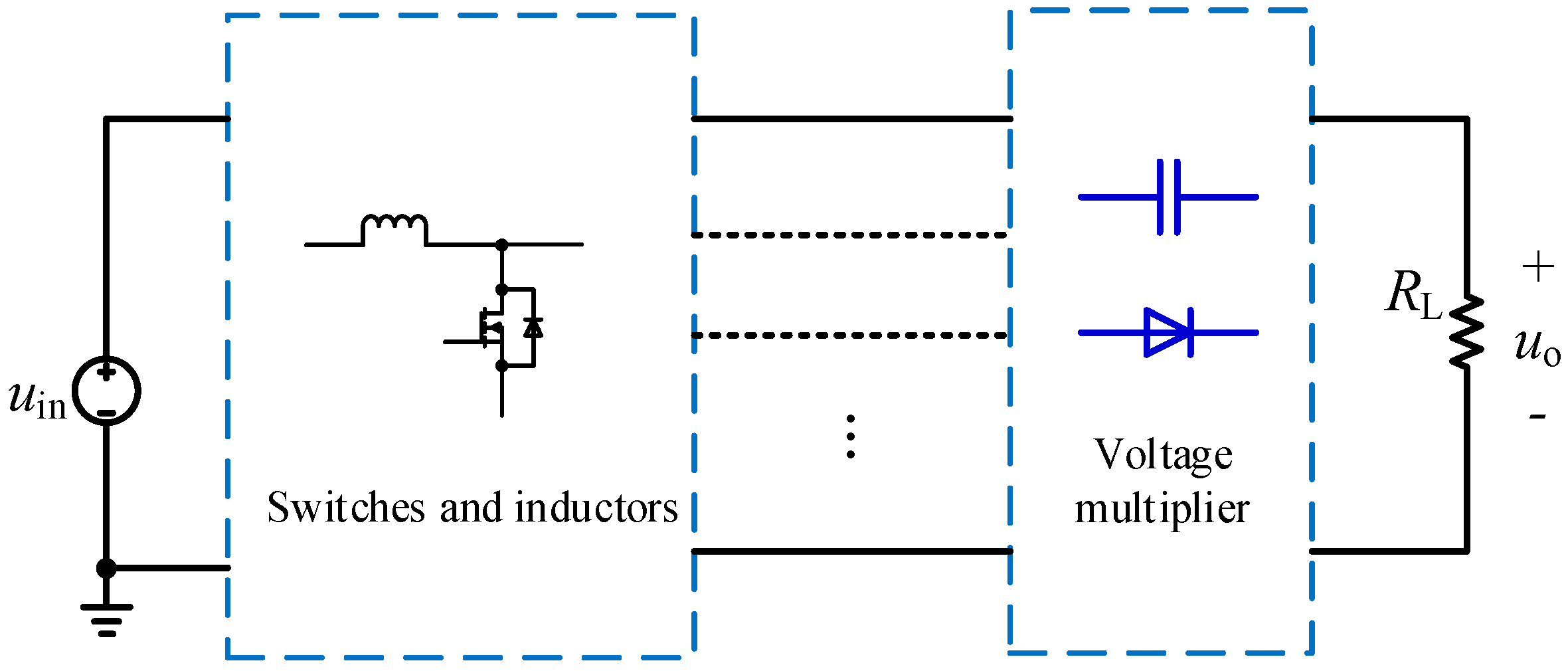

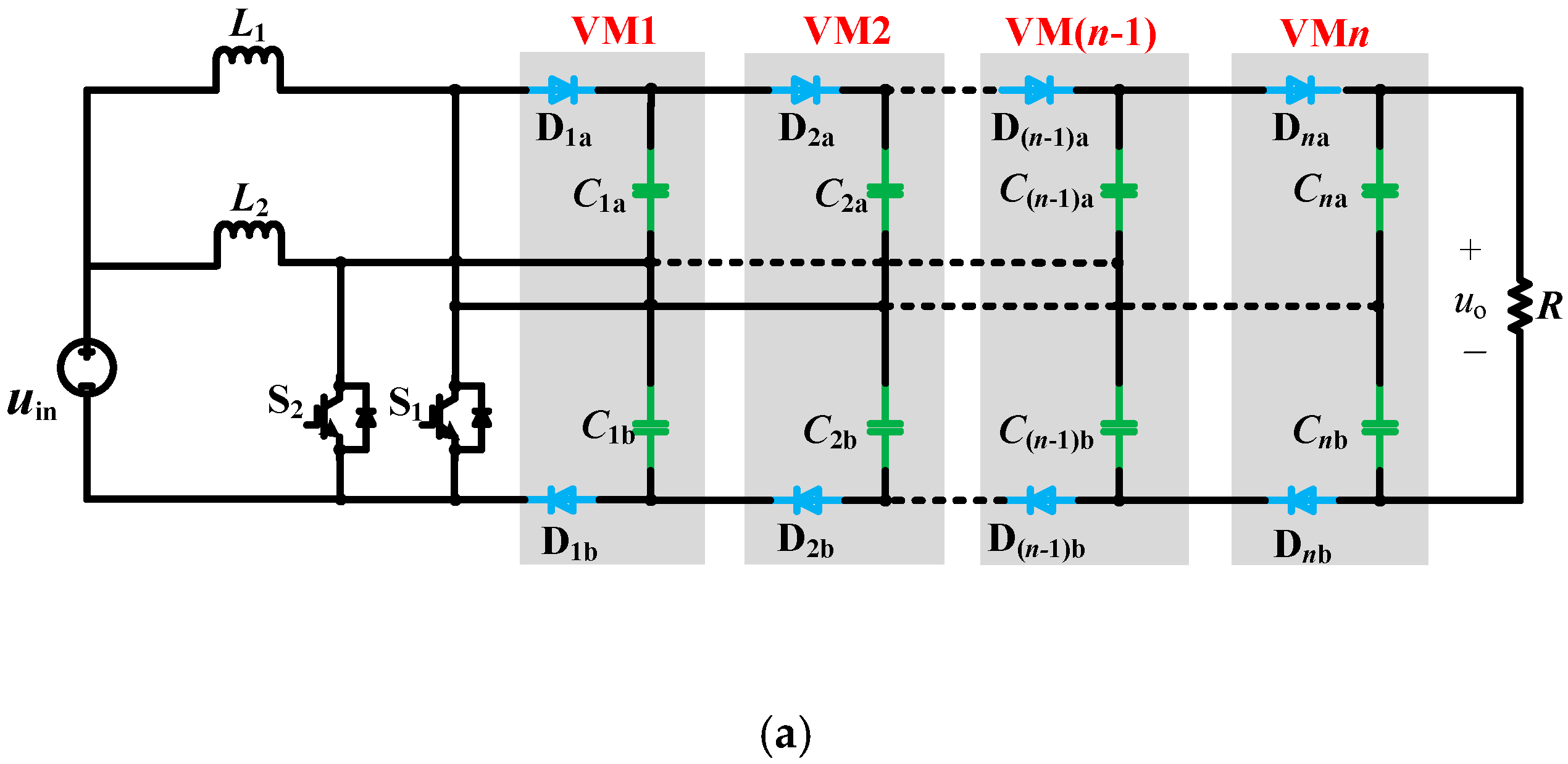

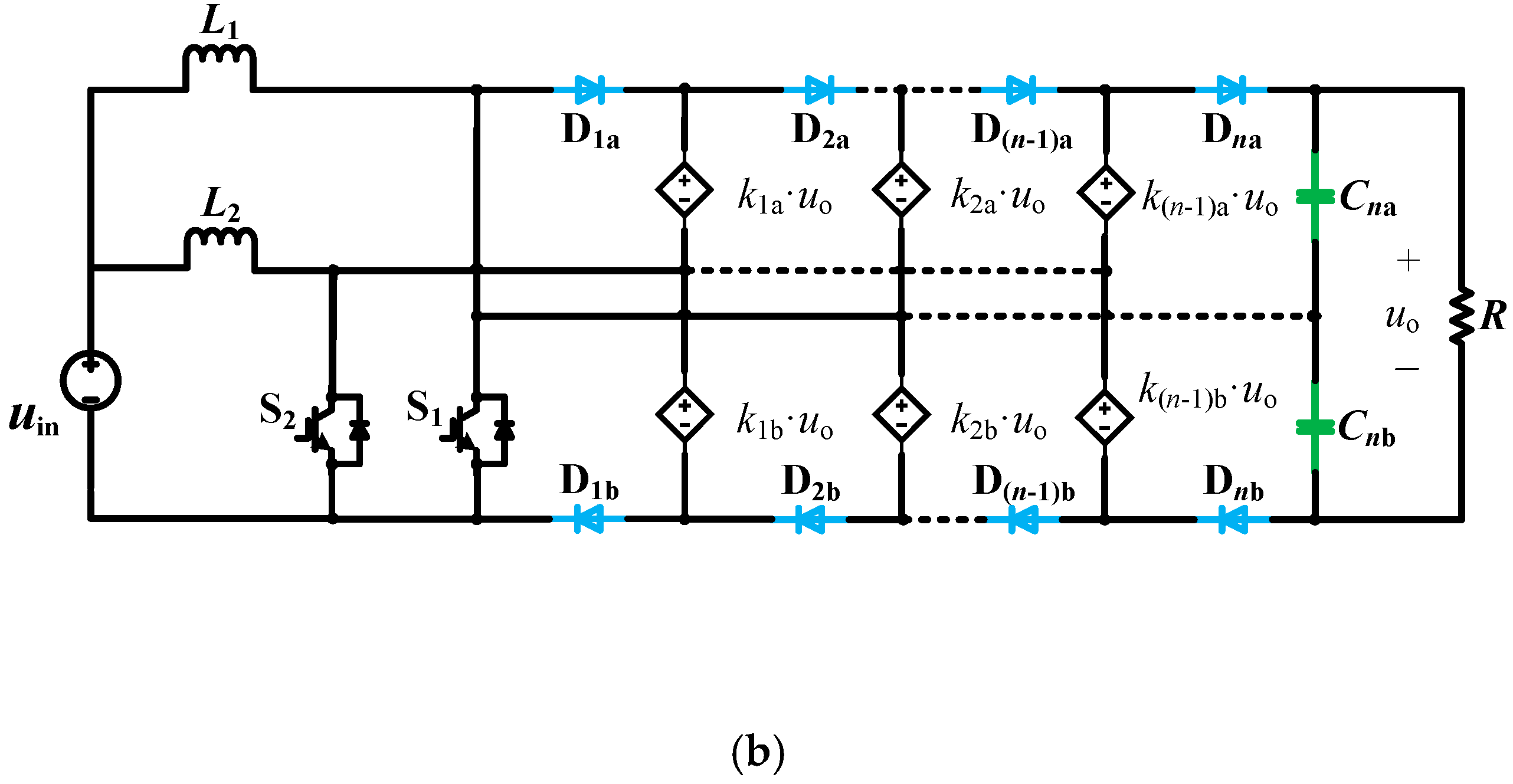

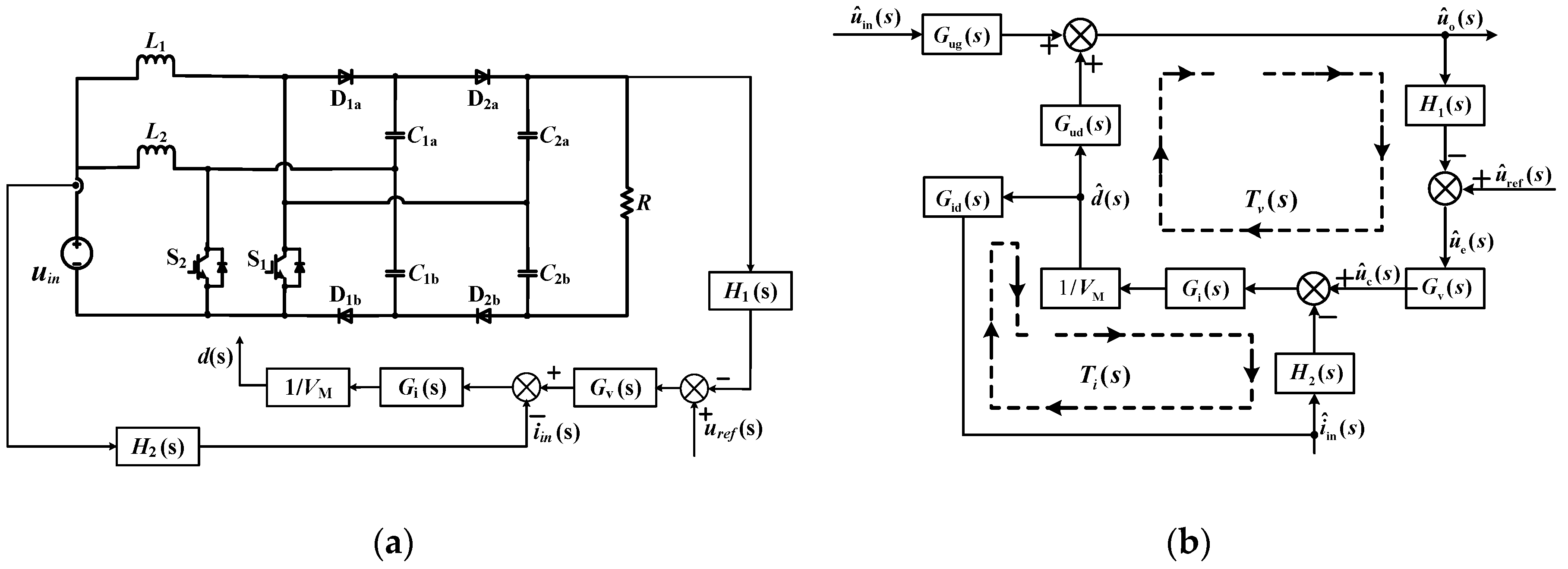

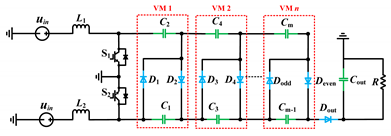

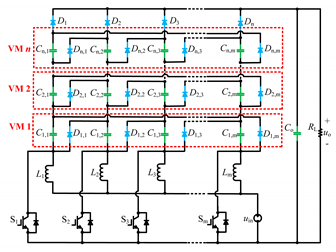

2. Proposed Modeling Method and Reduced-Order Models

2.1. Proposed Model Order Reduction Method

- Step 1:

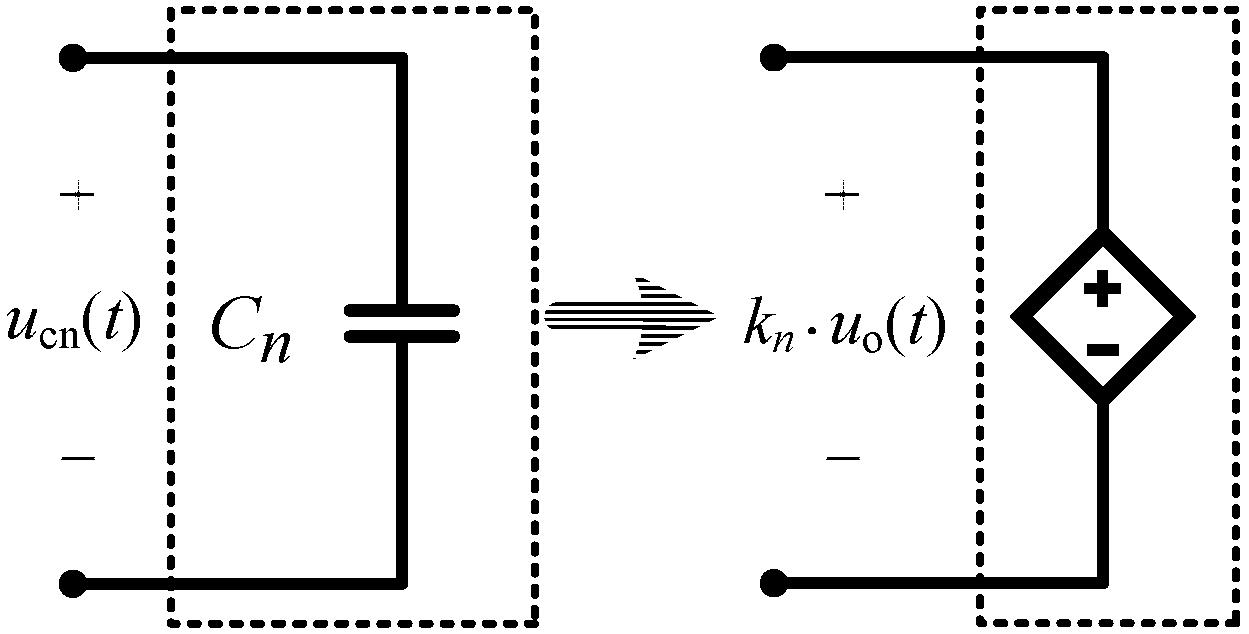

- Obtain the steady-state relationship between all VM capacitor voltages and the output voltage uo(t) according to the results from circuit analysis. The general relationship can be expressed aswhere ucn(t) is the voltage of n-th VM capacitor and kn is corresponding proportional gain.

- Step 2:

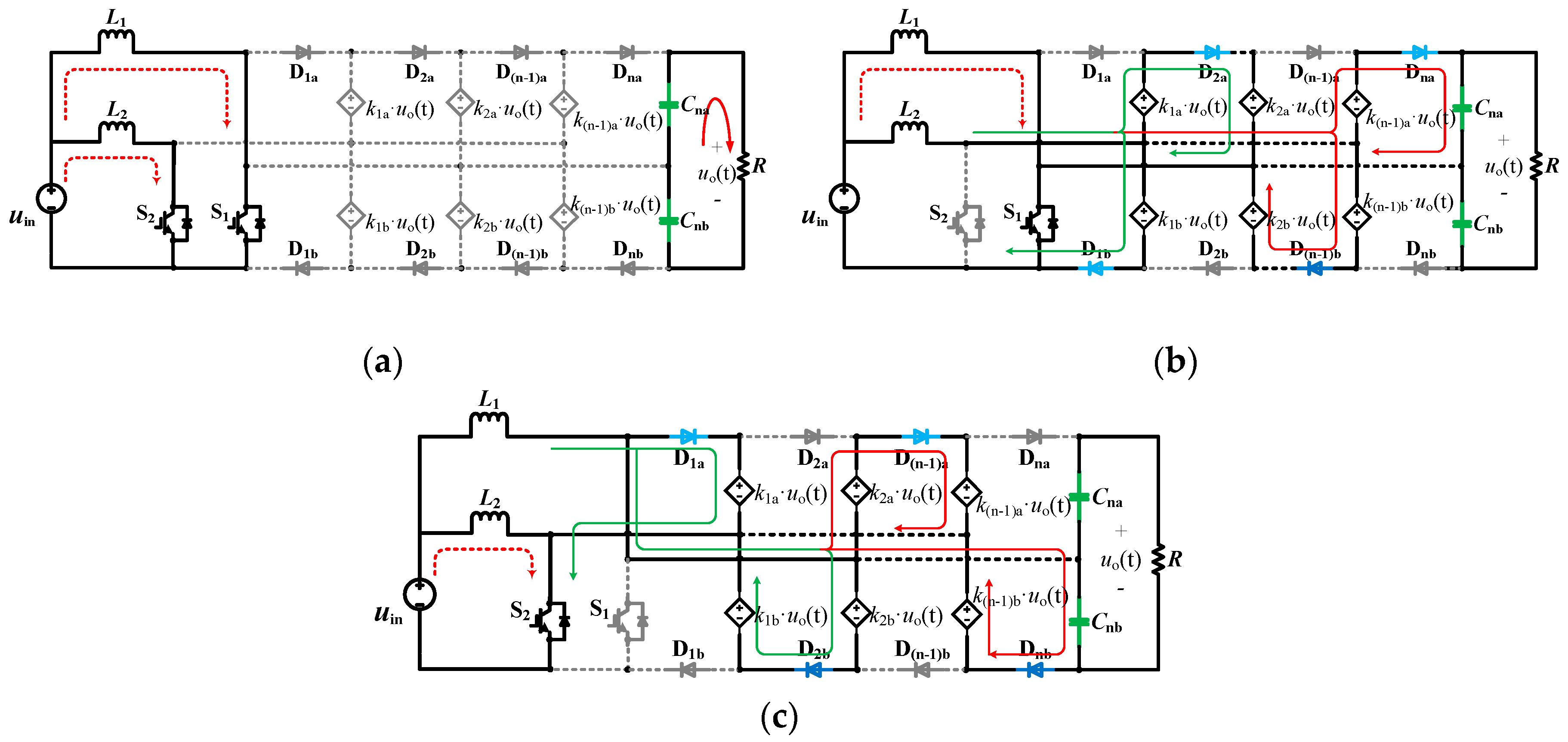

- Replace all VM capacitors, except the ones at the output, with controlled voltage sources according to (1). This step is shown graphically in Figure 2.

- Step 3:

- Reformulate and simplify the resulting model to construct an equivalent reduced-order circuit based on the state-space averaging method [28].

2.2. A General Reduced-Order Model of the Converters Based on VM

3. Small Signal AC Models and Transfer Functions

3.1. Small-Signal AC Models

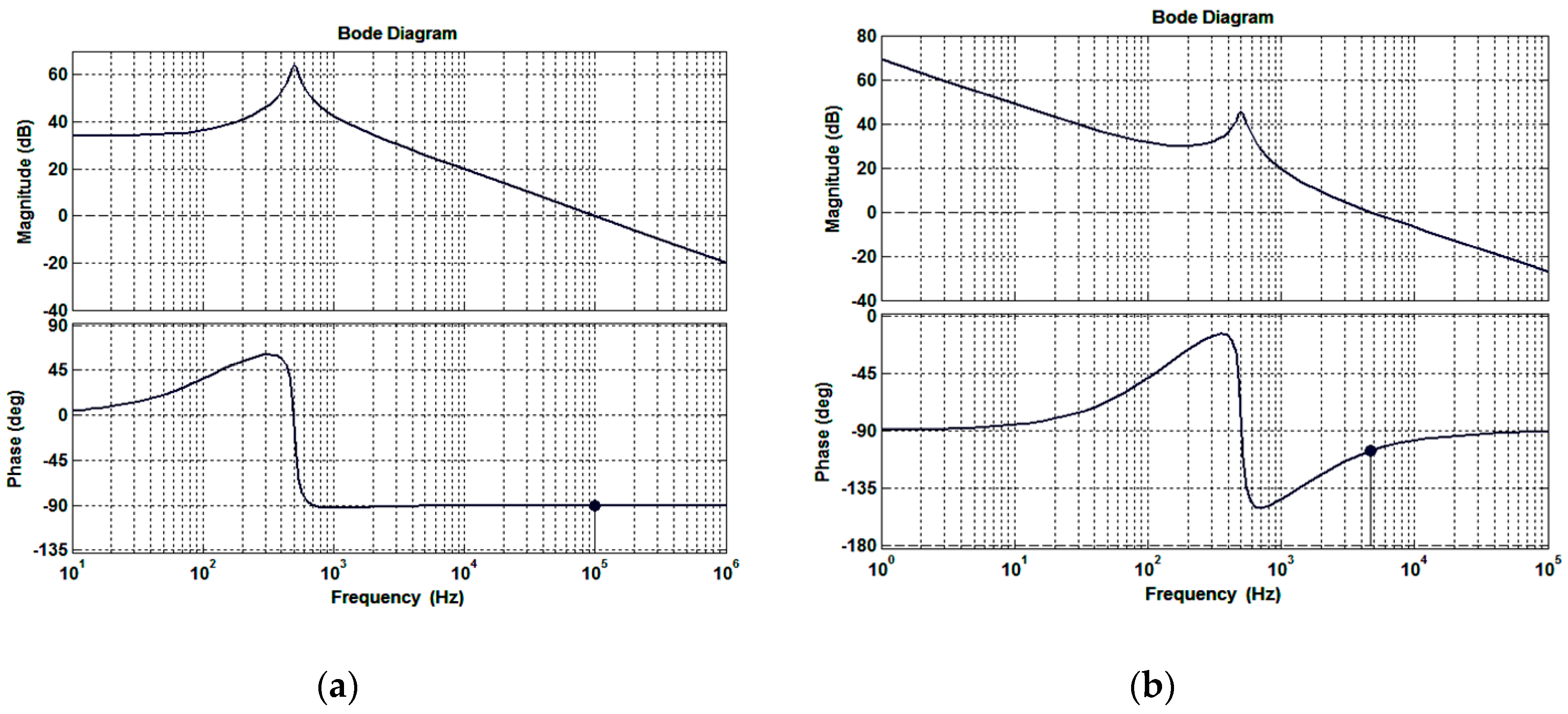

3.2. Transfer Functions

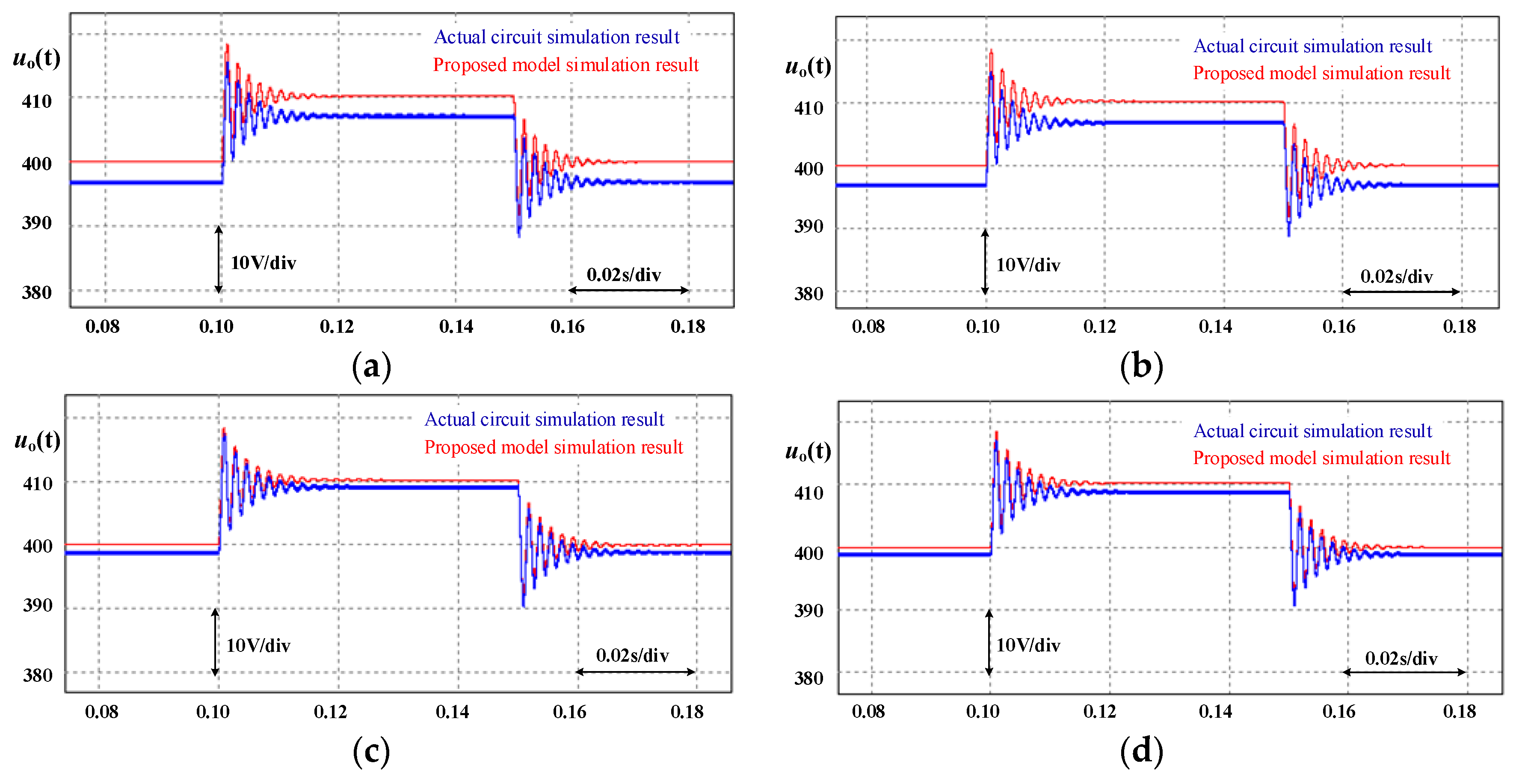

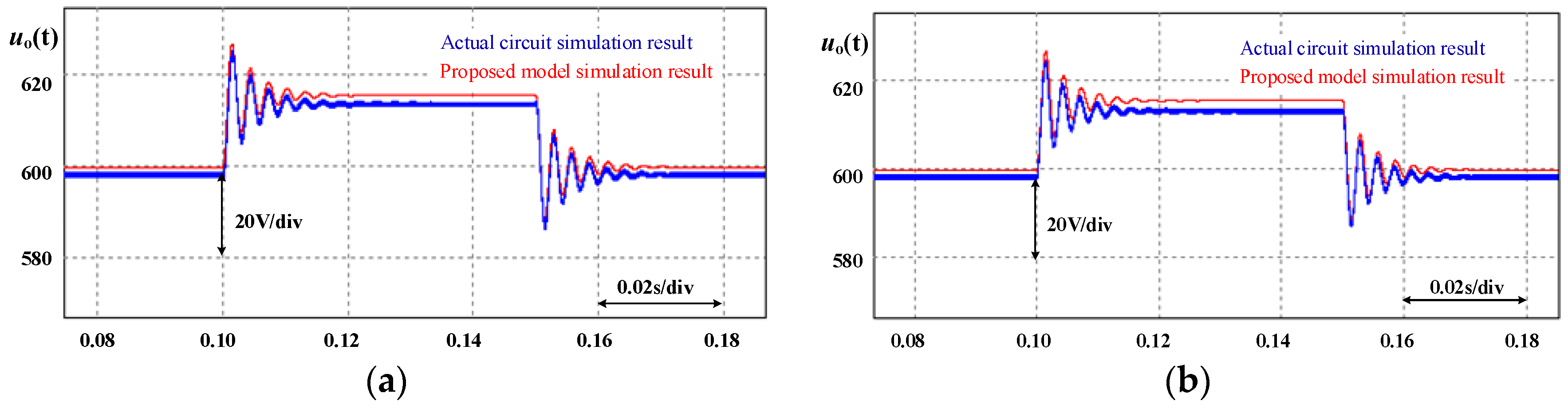

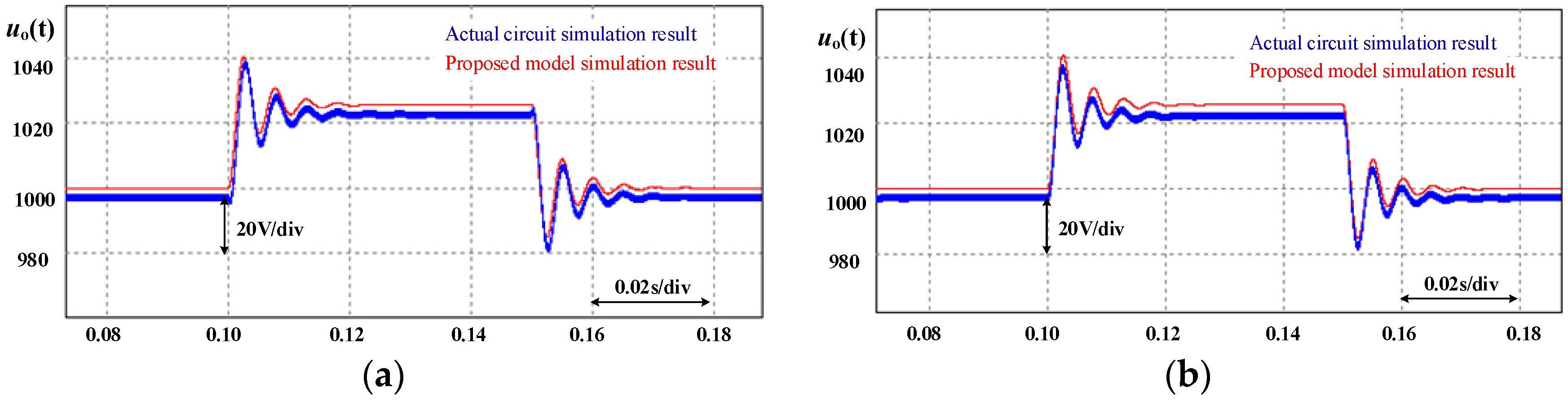

3.3. Accuracy of the Small Signal AC Model

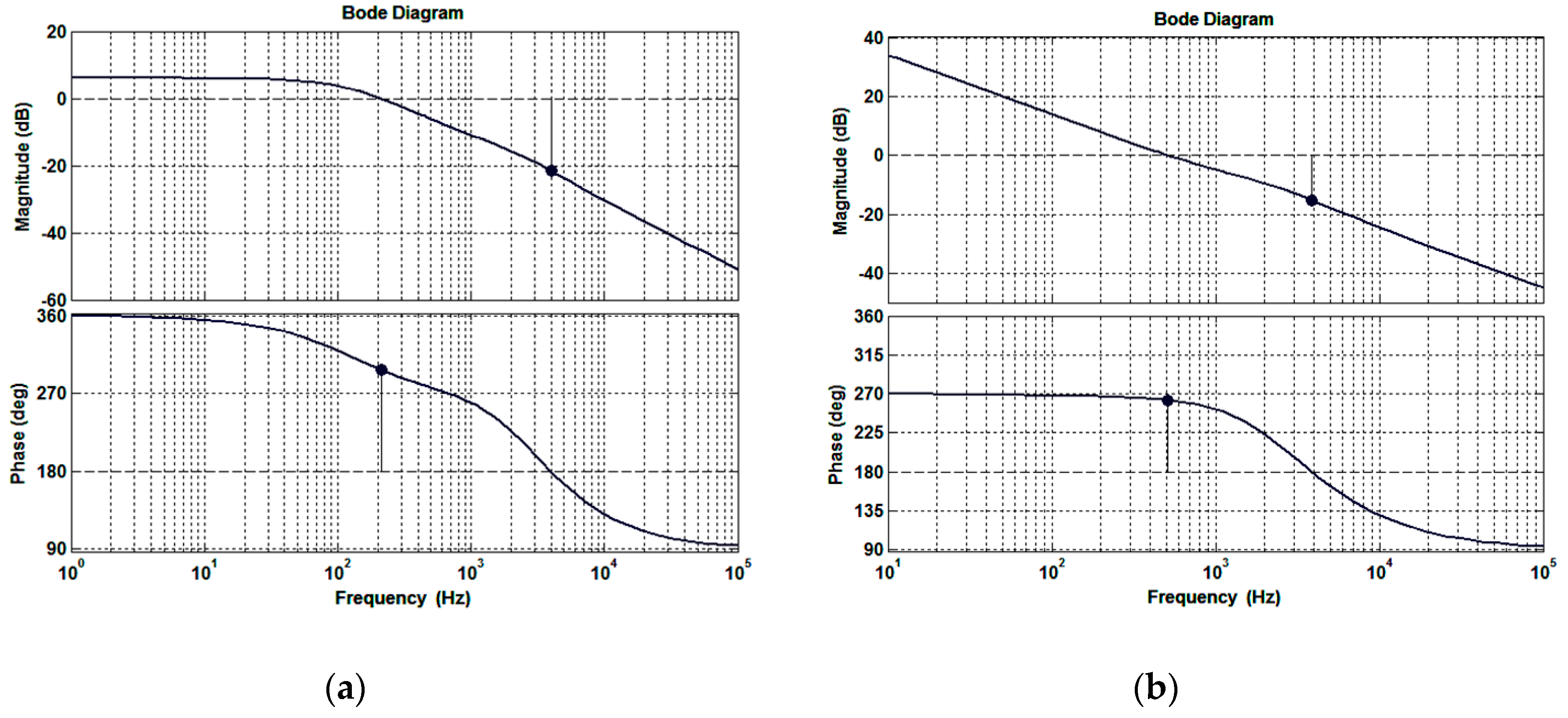

4. Controller Design

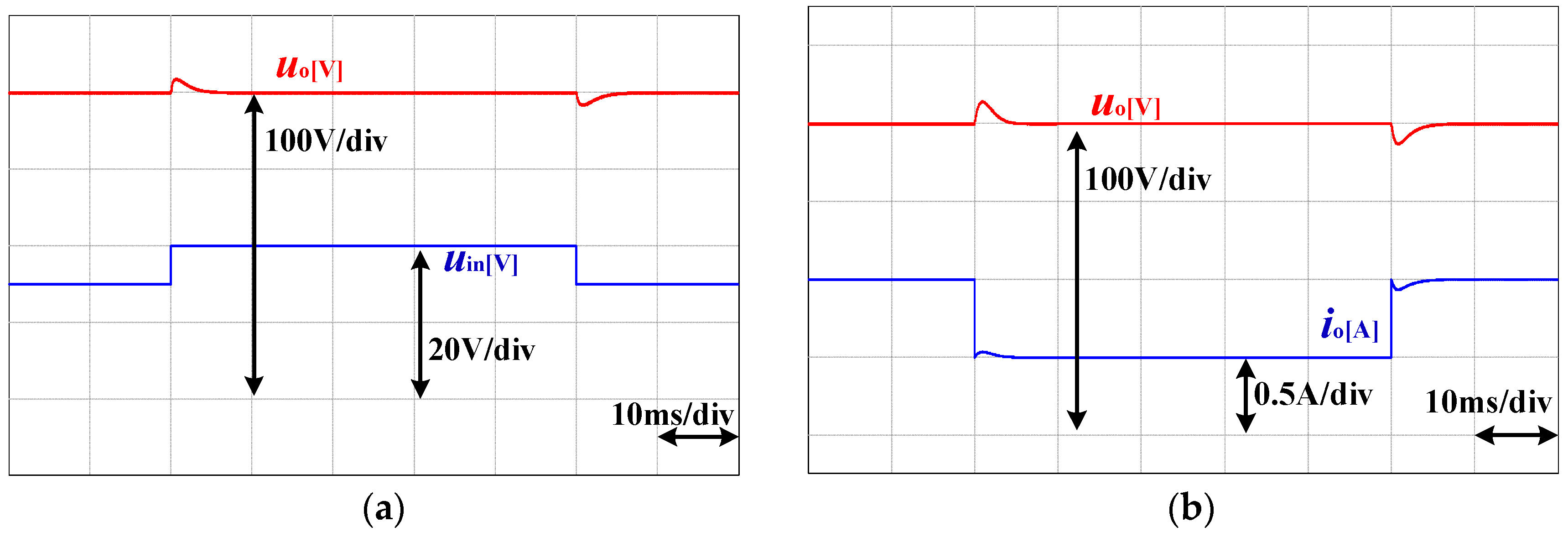

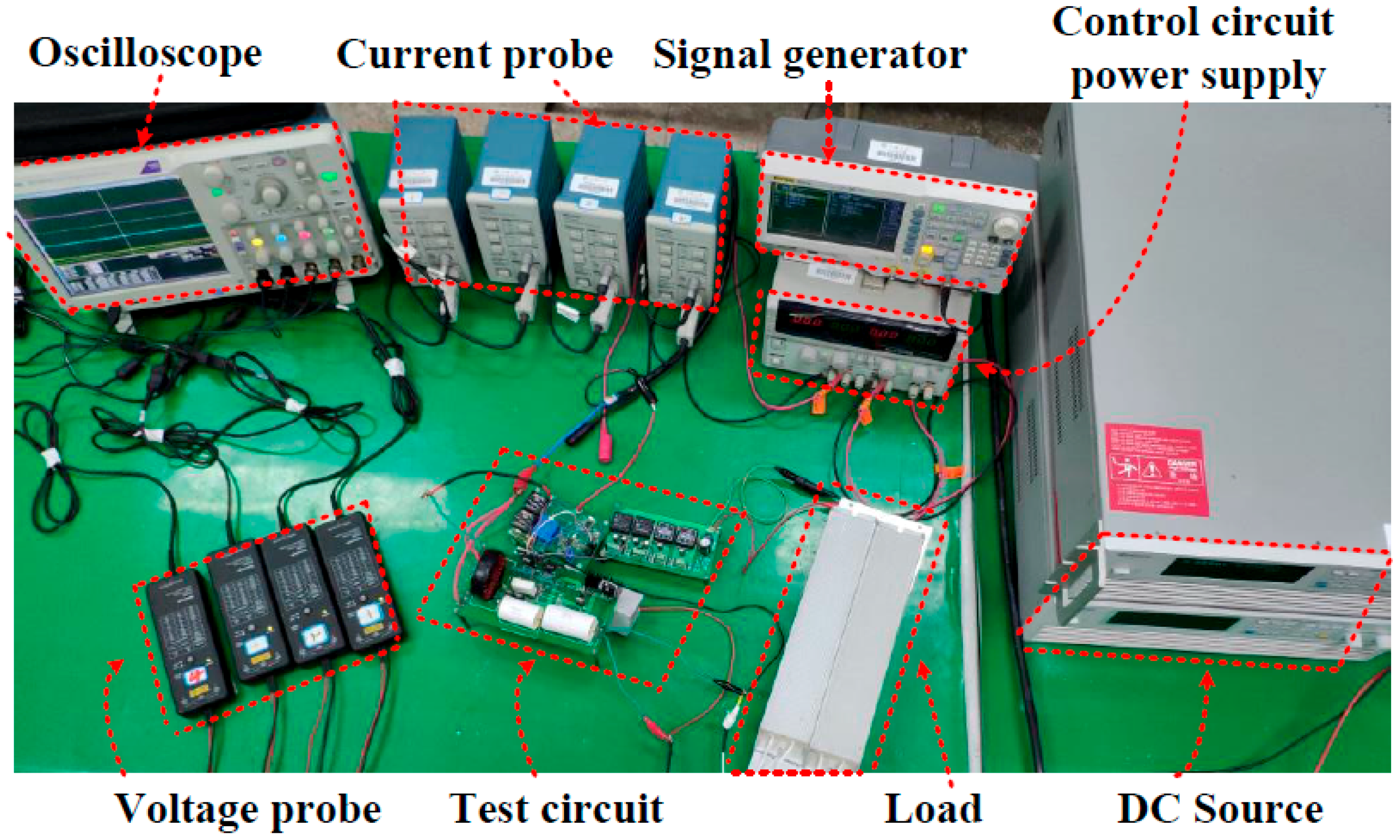

5. Simulation and Experimental Verification

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Baddipadiga, B.P.R.; Prabhala, V.A.K.; Ferdowsi, M. A Family of High-Voltage-Gain DC–DC Converters Based on a Generalized Structure. IEEE Trans. Power Electron. 2018, 33, 8399–8411. [Google Scholar] [CrossRef]

- Wu, Y.; Lin, J.; Lin, H. Standards and Guidelines for Grid-Connected Photovoltaic Generation Systems: A Review and Comparison. IEEE Trans. Ind. Appl. 2017, 53, 3205–3216. [Google Scholar] [CrossRef]

- Li, W.; He, X. Review of Nonisolated High-Step-Up DC/DC Converters in Photovoltaic Grid-Connected Applications. IEEE Trans. Ind. Electron. 2011, 58, 1239–1250. [Google Scholar] [CrossRef]

- Zhu, B.; Liu, S.; Vilathgamuwa, D.M.; Li, Y. High step-up scalable voltage multiple cell based dc/dc converter for offshore wind farms. IET Power Electron. 2019, in press. [Google Scholar] [CrossRef]

- Fuzato, G.H.F.; Aguiar, C.R.; Ottoboni, K.D.A.; Bastos, R.F.; Machado, R.Q. Voltage gain analysis of the interleaved boost with voltage multiplier converter used as electronic interface for fuel cells systems. IET Power Electron. 2016, 9, 1842–1851. [Google Scholar] [CrossRef]

- Li, W.; Fan, L.; Zhao, Y.; He, X.; Xu, D.; Wu, B. High-Step-Up and High-Efficiency Fuel-Cell Power-Generation System With Active-Clamp Flyback–Forward Converter. IEEE Trans. Ind. Electron. 2012, 59, 599–610. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M. Interleaved Boost Converter With Intrinsic Voltage-Doubler Characteristic for Universal-Line PFC Front End. IEEE Trans. Power Electron. 2007, 22, 1394–1401. [Google Scholar] [CrossRef]

- Pan, C.; Chuang, C.; Chu, C. A Novel Transformer-less Adaptable Voltage Quadrupler DC Converter with Low Switch Voltage Stress. IEEE Trans. Power Electron. 2014, 29, 4787–4796. [Google Scholar] [CrossRef]

- Prabhala, V.A.K.; Fajri, P.; Gouribhatla, V.S.P.; Baddipadiga, B.P.; Ferdowsi, M. A DC–DC Converter With High Voltage Gain and Two Input Boost Stages. IEEE Trans. Power Electron. 2016, 31, 4206–4215. [Google Scholar] [CrossRef]

- Müller, L.; Kimball, J.W. High Gain DC–DC Converter Based on the Cockcroft–Walton Multiplier. IEEE Trans. Power Electron. 2016, 31, 6405–6415. [Google Scholar] [CrossRef]

- Zhou, L.; Zhu, B.; Luo, Q.; Chen, S. Interleaved non-isolated high step-up DC/DC converter based on the diode-capacitor multiplier. IET Power Electron. 2014, 7, 390–397. [Google Scholar] [CrossRef]

- Zhu, B.; Ren, L.; Wu, X. Kind of high step-up dc/dc converter using a novel voltage multiplier cell. IET Power Electron. 2017, 10, 129–133. [Google Scholar] [CrossRef]

- Baddipadiga, B.P.; Ferdowsi, M. A high-voltage-gain dc-dc converter based on modified dickson charge pump voltage multiplier. IEEE Trans. Power Electron. 2017, 32, 7707–7715. [Google Scholar] [CrossRef]

- Prudente, M.; Pfitscher, L.L.; Emmendoerfer, G.; Romaneli, E.F.; Gules, R. Voltage Multiplier Cells Applied to Non-Isolated DC–DC Converters. IEEE Trans. Power Electron. 2008, 23, 871–887. [Google Scholar] [CrossRef]

- Gules, R.; Pfitscher, L.L.; Franco, L.C. An interleaved boost DC-DC converter with large conversion ratio. In Proceedings of the 2003 IEEE International Symposium on Industrial Electronics (Cat. No.03TH8692), Rio de Janeiro, Brazil, 9–11 June 2003; Volume 1, pp. 411–416. [Google Scholar]

- Zhu, B.; Liu, S.; Huang, Y.; Tan, C. Non-isolated high step-up DC/DC converter based on a high degrees of freedom voltage gain cell. IET Power Electron. 2017, 10, 2023–2033. [Google Scholar] [CrossRef]

- Axelrod, B.; Berkovich, Y.; Shenkman, A.; Golan, G. Diode-capacitor voltage multipliers combined with boost-converters: Topologies and characteristics. IET Power Electron. 2012, 5, 873–884. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Ramirez, J.M.; Peng, F.Z.; Valderrabano, A. A DC-DC multilevel boost converter. IET Power Electron. 2010, 3, 129–137. [Google Scholar] [CrossRef]

- Babaei, E.; Abbasi, O. Structure for multi-input multi-output dc–dc boost converter. IET Power Electron. 2016, 9, 9–19. [Google Scholar] [CrossRef]

- Liu, J.; Xu, M.; Zeng, J.; Wu, J.; Eric, C.K.W. Modified voltage equaliser based on Cockcroft–Walton voltage multipliers for series-connected supercapacitors. IET Electr. Syst. Transp. 2018, 8, 44–51. [Google Scholar] [CrossRef]

- Zhu, B.; Zeng, Q.; Vilathgamuwa, D.M.; Li, Y.; She, X. Non-isolated high voltage gain dual-input dc/dc converter with ZVT auxiliary circuit. IET Power Electron. 2019, 12, 861–868. [Google Scholar] [CrossRef]

- Zhu, B.; Zeng, Q.; Chen, Y.; Zhao, Y.; Liu, S. A Dual-Input High Step-Up DC/DC Converter With ZVT Auxiliary Circuit. IEEE Trans. Energy Convers. 2019, 34, 161–169. [Google Scholar] [CrossRef]

- Zhao, Y.; Li, W.; Deng, Y.; He, X. Analysis, Design, and Experimentation of an Isolated ZVT Boost Converter With Coupled Inductors. IEEE Trans. Power Electron. 2011, 26, 541–550. [Google Scholar] [CrossRef]

- Xie, R.; Li, W.; Zhao, Y.; Zhao, J.; He, X.; Cao, F. Performance analysis of isolated ZVT interleaved converter with winding-cross-coupled inductors and switched-capacitors. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 2025–2029. [Google Scholar]

- Alcazar, Y.J.A.; Cabero, W.G.C.; Bascopé, R.P.T.; Daher, S.; Oliveira, D.S.; de Sousa, G.J.M. Modeling and control of the high voltage gain boost converter based on three-state switching cell and voltage multipliers (mc). In Proceedings of the 2009 Brazilian Power Electronics Conference, Bonito-Mato Grosso do Sul, Brazil, 27 September–1 October 2009; pp. 655–664. [Google Scholar]

- Dupont, F.H.; Rech, C.; Gules, R.; Pinheiro, J.R. Reduced-Order Model and Control Approach for the Boost Converter With a Voltage Multiplier Cell. IEEE Trans. Power Electron. 2013, 28, 3395–3404. [Google Scholar] [CrossRef]

- Liao, Y.-H.; Lai, C.-M.; Ke, Y.-L. Modeling and design of an improved current-fed converter with new voltage multiplier circuit combination. In Proceedings of the 2011 IEEE Industry Applications Society Annual Meeting, Orlando, FL, USA, 9–13 October 2011; pp. 1–8. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics; Springer US: New York, NY, USA, 2001. [Google Scholar]

| Ref. | Topology | Expressions of Equivalent Parameters |

|---|---|---|

| [9] |  | |

| [10] |  | |

| [11] |  | |

| [14] |  | |

| [16] |  |

| Reference | A | B | C |

|---|---|---|---|

| [12] | |||

| [9,11,14] | |||

| [10] | |||

| [16] |

| Component | Rated Parameters | Extended Parameters |

|---|---|---|

| Switches | GP4055 | GP4055 |

| Diodes | STTH15L06D | STTH15L06D |

| VM number | 2 | 3/5 |

| Capacitors in VM (μF) | 10 | 10 |

| Output filter capacitor (μF) | 10 | 10 |

| L1, L2 (μH) | 320 | 320 |

| Load resistance (Ω) | 400 | 400 |

| Switch frequency (kHz) | 50 | 50 |

| Duty cycle | 0.6 | 0.6 |

| Input voltage (V) | 40 | 40 |

| Output voltage (kV) | 0.4 | 0.6/1 |

| Output power (kW) | 0.4 | 0.9/2.5 |

| VM Numbers | Capacitor Values (μF) | Voltage Ripple |

|---|---|---|

| 2 | C1a, C1b: 10 | 2% |

| C1a, C1b: 2 | 10% | |

| C1a, C1b: 0.67 | 30% | |

| 3 | C1a, C1b: 3 | 10% |

| C2a, C2b: 1.5 | ||

| 5 | C1a, C1b: 5 | 10% |

| C2a, C2b: 2.5 | ||

| C3a, C3b: 1.7 | ||

| C4a, C4b: 1.25 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, B.; Zeng, Q.; Vilathgamuwa, M.; Li, Y.; Chen, Y. A Generic Control-Oriented Model Order Reduction Approach for High Step-Up DC/DC Converters Based on Voltage Multiplier. Energies 2019, 12, 1971. https://doi.org/10.3390/en12101971

Zhu B, Zeng Q, Vilathgamuwa M, Li Y, Chen Y. A Generic Control-Oriented Model Order Reduction Approach for High Step-Up DC/DC Converters Based on Voltage Multiplier. Energies. 2019; 12(10):1971. https://doi.org/10.3390/en12101971

Chicago/Turabian StyleZhu, Binxin, Qingdian Zeng, Mahinda Vilathgamuwa, Yang Li, and Yao Chen. 2019. "A Generic Control-Oriented Model Order Reduction Approach for High Step-Up DC/DC Converters Based on Voltage Multiplier" Energies 12, no. 10: 1971. https://doi.org/10.3390/en12101971