Radiation Assessment of a 15.6ps Single-Shot Time-to-Digital Converter in Terms of TID

Abstract

:1. Introduction

2. Proposed TDC Architecture

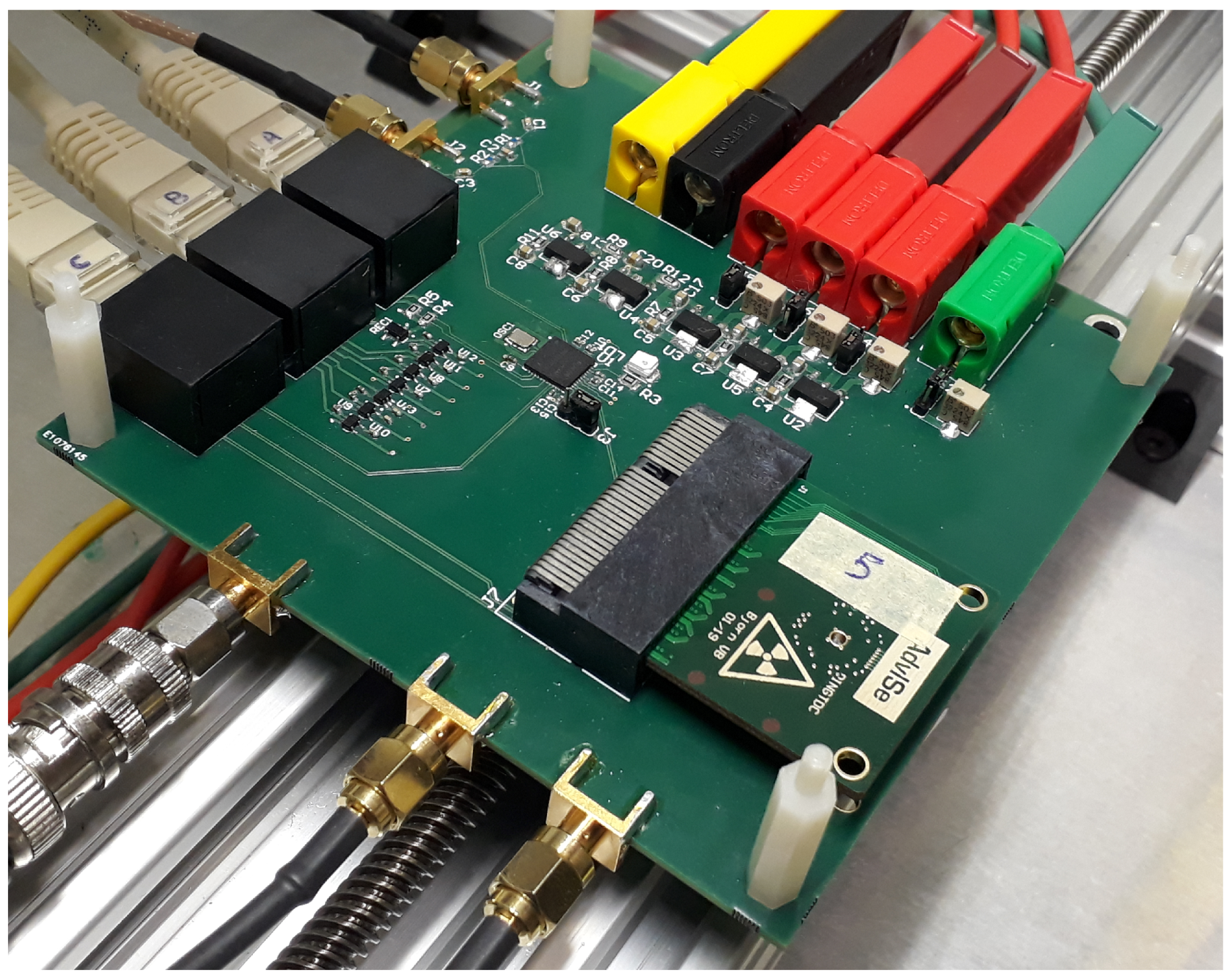

3. Circuit Implementation

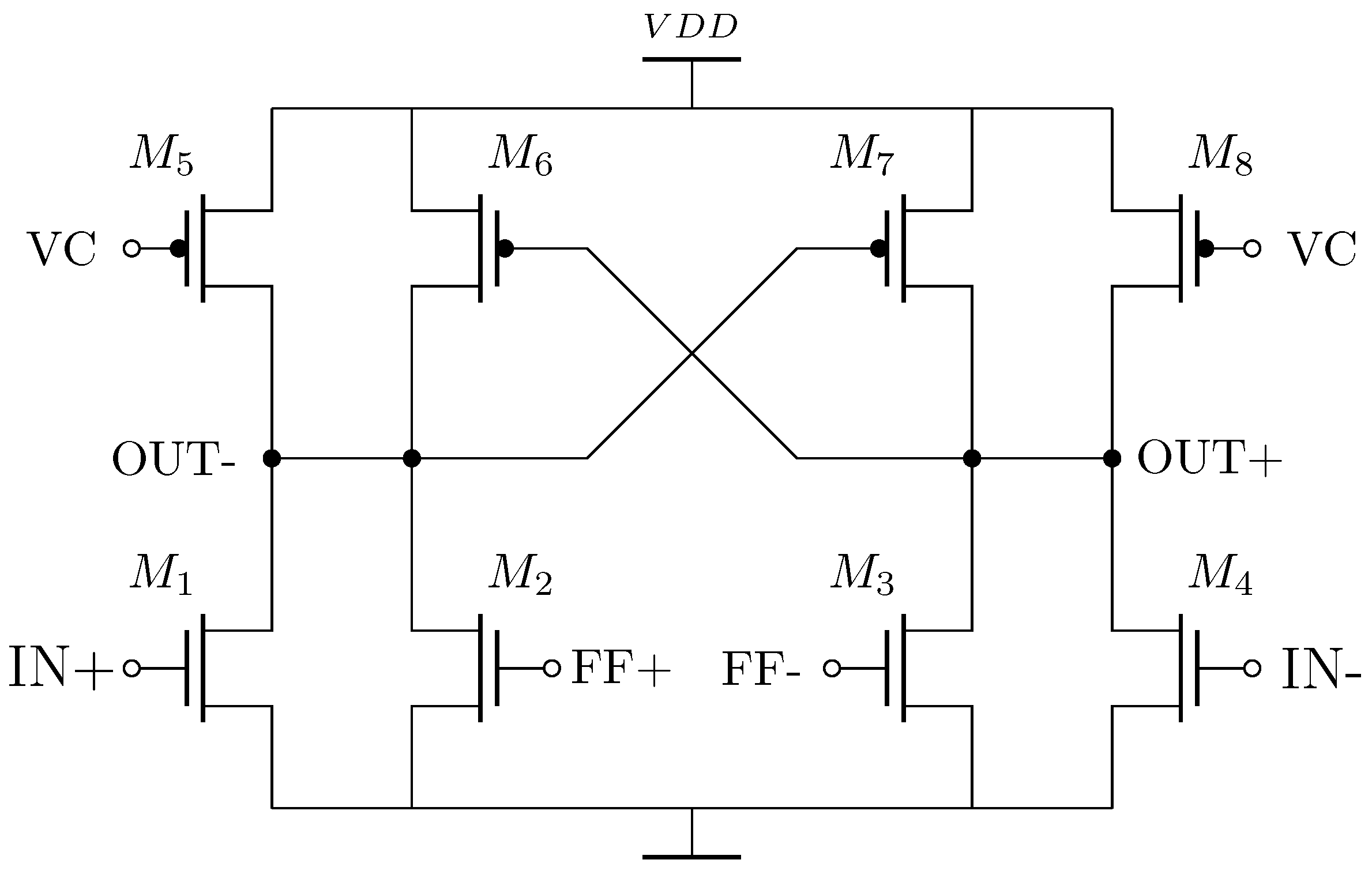

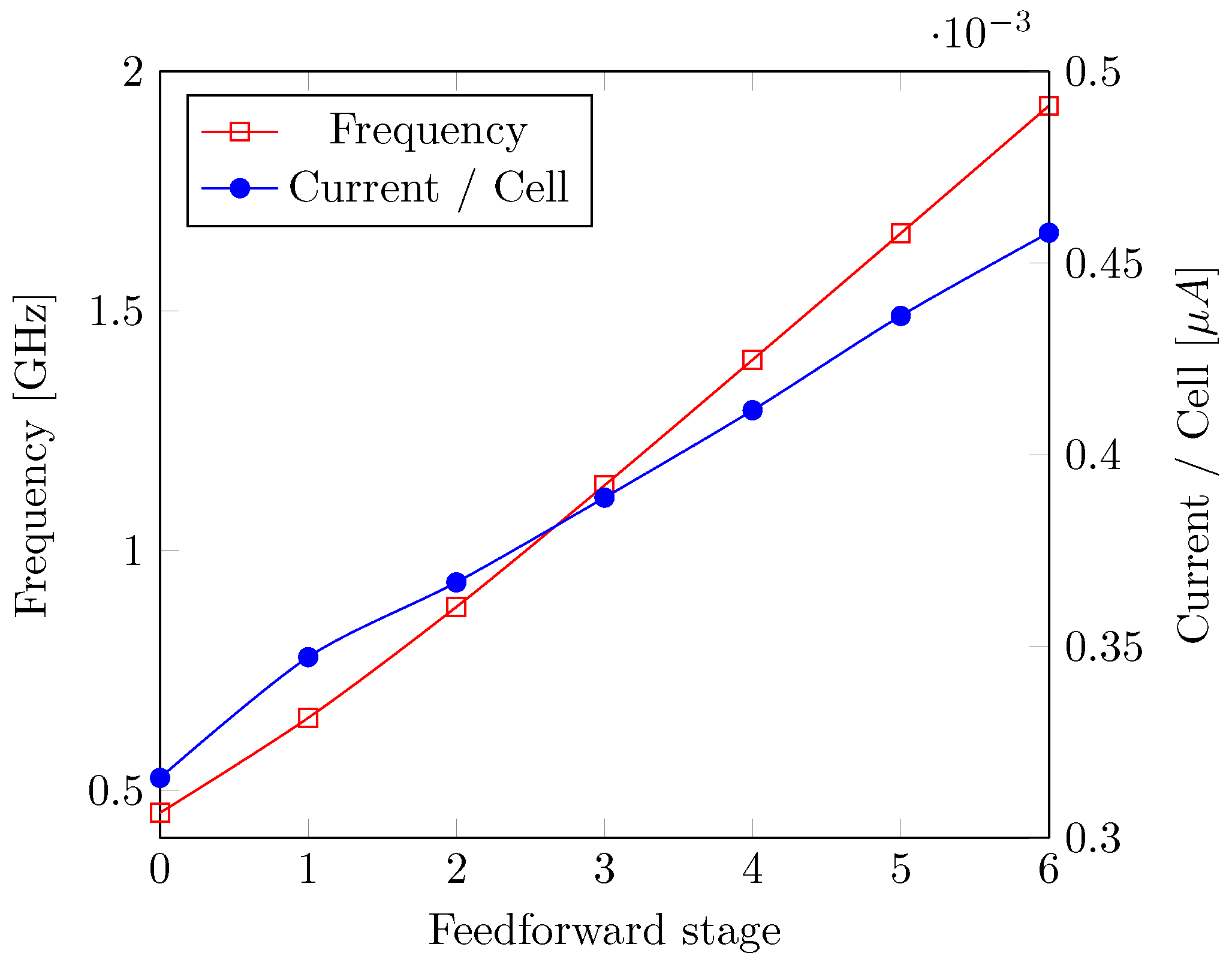

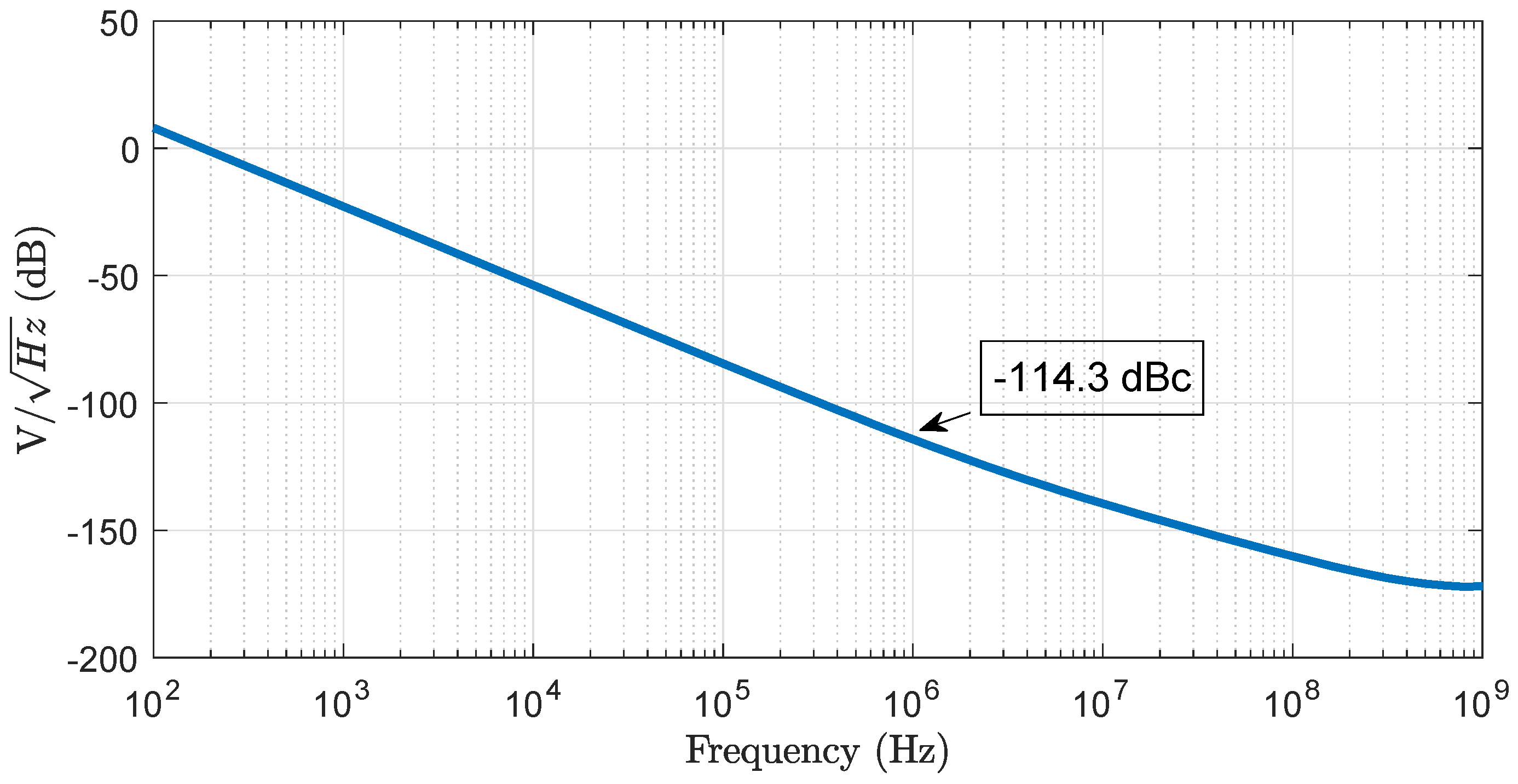

3.1. VCO

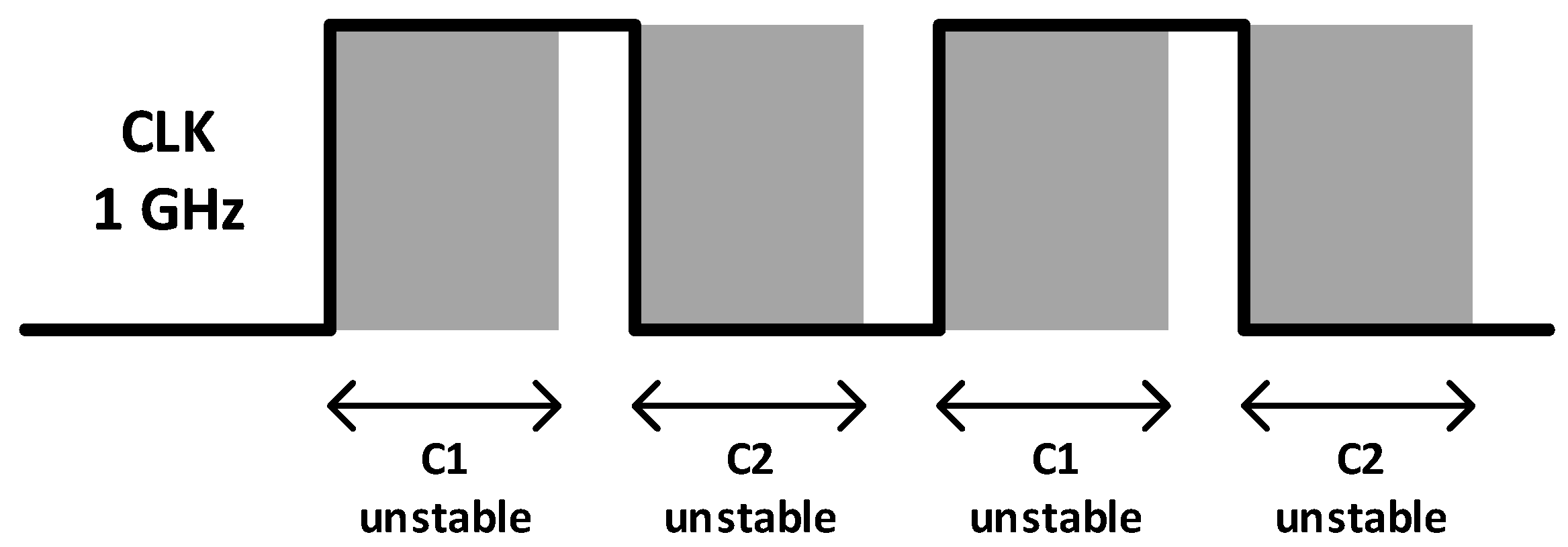

3.2. Sampling Circuit

3.3. Digital Control Block

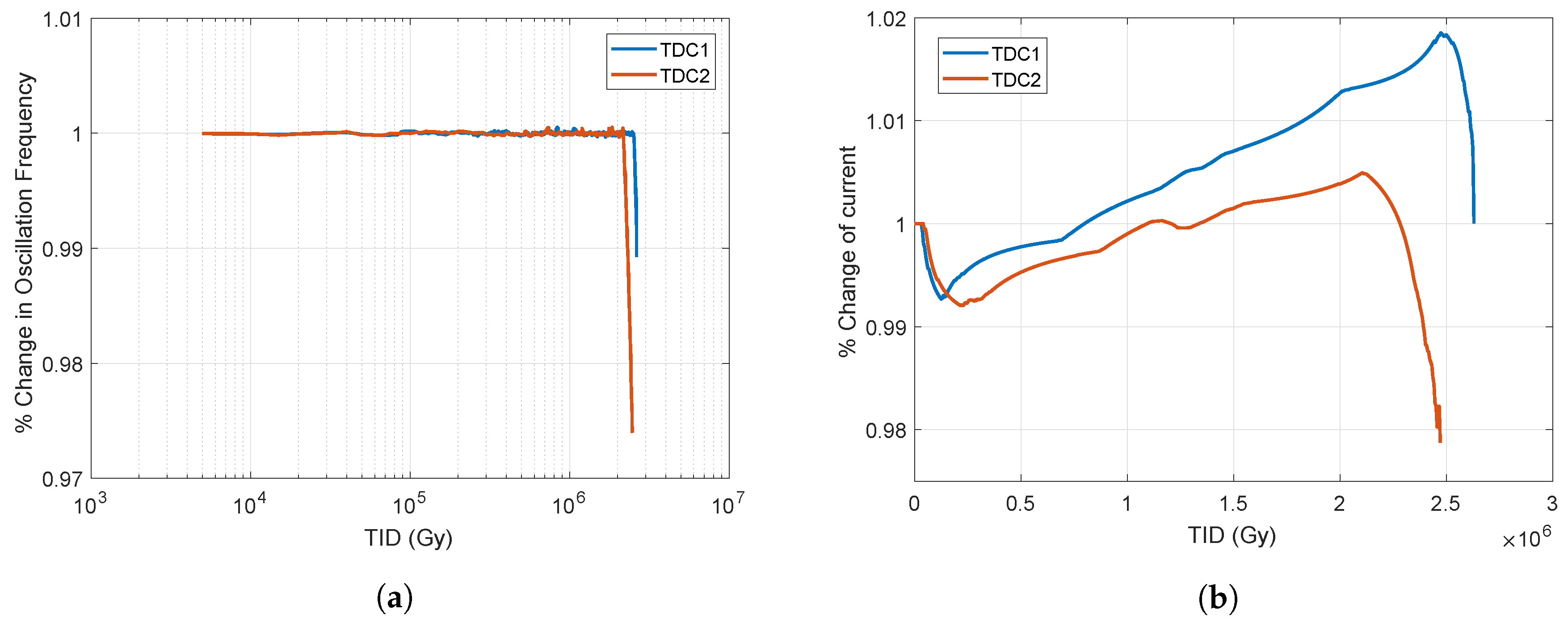

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hu, C. Future CMOS Scaling and reliability. Proc. IEEE 1993, 81, 682–689. [Google Scholar] [CrossRef]

- Jurgo, M.; Navickas, R. Comparison of TDC parameters in 65 nm and 0.13 μm CMOS. In Proceedings of the 2017 5th IEEE Workshop on Advances in Information, Electronic and Electrical Engineering (AIEEE), Riga, Latvia, 24–25 November 2017; pp. 1–4. [Google Scholar]

- Jee, D.W.; Seo, Y.H.; Park, H.J.; Sim, J.Y. A 2 GHz fractional-N digital PLL with 1b noise shaping Δ Σ TDC. IEEE J. Solid-State Circuits 2012, 47, 875–883. [Google Scholar] [CrossRef]

- Naraghi, S.; Courcy, M.; Flynn, M.P. A 9-bit, 14 μw and 0.06 mm2 pulse position modulation ADC in 90 nm digital CMOS. IEEE J. Solid-State Circuits 2010, 45, 1870–1880. [Google Scholar] [CrossRef]

- Nose, K.; Kajita, M.; Mizuno, M. A 1-ps resolution jitter-measurement macro using interpolated jitter oversampling. IEEE J. Solid-State Circuits 2006, 41, 2911–2920. [Google Scholar] [CrossRef]

- Dudek, P.; Szczepański, S.; Hatfield, J.V. A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE J. Solid-State Circuits 2000, 25, 240–247. [Google Scholar] [CrossRef]

- Henzler, S.; Koeppe, S.; Kamp, W.; Mulatz, H.; Schmitt-Landsiedel, D. 90 nm 4.7 ps-Resolution 0.7-LSB single-shot precision and 19 pJ-per-shot local passive interpolation time-to-digital converter with on-chip characterization. In Proceedings of the IEEE International Solid-State Circuits Conference on Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008. [Google Scholar]

- Yao, C.; Jonsson, F.; Chen, J.; Zheng, L.R. A high-resolution Time-to-Digital Converter based on parallel delay elements. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems, Seoul, Korea, 20–23 May 2012; pp. 3158–3161. [Google Scholar]

- Prinzie, J.; Steyaert, M.; Leroux, P. A Self-Calibrated Bang-Bang Phase Detector for Low-Offset Time Signal Processing. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 453–457. [Google Scholar] [CrossRef]

- Han, Y.; Rhee, W.; Wang, Z. A PVT-insensitive self-dithered TDC design by utilizing a Δ Σ DLL. In Proceedings of the 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, USA, 5–8 August 2012. [Google Scholar]

- Cao, Y.; De Cock, W.; Steyaert, M.; Leroux, P. 1-1-1 MASH Δ Σ time-to-digital converters with 6 ps resolution and third-order noise-shaping. IEEE J. Solid-State Circuits 2012, 47, 2093–2106. [Google Scholar] [CrossRef]

- Gande, M.; Maghari, N.; Oh, T.; Moon, U.K. A 71dB dynamic range third-order Δ Σ TDC using charge-pump. In Proceedings of the IEEE Symposium on VLSI Circuits, Digest of Technical Papers, Honolulu, HI, USA, 13–15 June 2012. [Google Scholar]

- Straayer, M.Z.; Perrott, M.H. A multi-path gated ring oscillator TDC with first-order noise shaping. IEEE J. Solid-State Circuits 2009, 44, 1089–1098. [Google Scholar] [CrossRef]

- Elshazly, A.; Rao, S.; Young, B.; Hanumolu, P.K. A noise-shaping time-to-digital converter using switched-ring oscillators—Analysis, design, and measurement techniques. IEEE J. Solid-State Circuits 2014, 49, 1184–1197. [Google Scholar] [CrossRef]

- Prinzie, J.; Christiansen, J.; Moreira, P.; Steyaert, M.; Leroux, P. Comparison of a 65 nm CMOS ring- and lc-oscillator based PLL in terms of TID and SEU sensitivity. IEEE Trans. Nucl. Sci. 2017, 64, 245–252. [Google Scholar] [CrossRef]

- Moazedi, M.; Abrishamifar, A.; Sodagar, A.M. A highly-linear modified pseudo-differential current starved delay element with wide tuning range. In Proceedings of the 2011 19th Iranian Conference on Electrical Engineering, Tehran, Iran, 17–19 May 2011; p. 1. [Google Scholar]

- Lacoe, R.C. Improving integrated circuit performance through the application of hardness-by-design methodology. IEEE Trans. Nucl. Sci. 2008, 55, 1903–1925. [Google Scholar] [CrossRef]

- Prinzie, J. Radiation Hardened CMOS Integrated Circuits for Time-Based Signal Processing; Springer: Berlin/Heidelberg, Germany, 2017. [Google Scholar]

- Faccio, F.; Michelis, S.; Cornale, D.; Paccagnella, A.; Gerardin, S. Radiation-Induced Short Channel (RISCE) and Narrow Channel (RINCE) Effects in 65 and 130 nm MOSFETs. IEEE Trans. Nucl. Sci. 2015, 62, 2933–2940. [Google Scholar] [CrossRef]

- Johnston, A.H.; Swimm, R.T.; Allen, G.R.; Miyahira, T.F. Total dose effects in CMOS trench isolation regions. IEEE Trans. Nucl. Sci. 2009, 56, 1941–1949. [Google Scholar] [CrossRef]

- Nikolić, B.; Oklobdžija, V.G.; Stojanovič, V.; Jia, W.; Chiu, J.K.S.; Leung, M.M.T. Improved sense-amplifier- based flip-flop: Design and measurements. IEEE J. Solid-State Circuits 2000, 35, 876–884. [Google Scholar] [CrossRef]

- Staszewski, R.B.; Vemulapalli, S.; Vallur, P.; Wallberg, J.; Balsara, P.T. 1.3 V 20 ps Time-to-Digital Converter for Frequency Synthesis in 90-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 220–224. [Google Scholar] [CrossRef]

- Mota, M.; Christiansen, J. High-resolution time interpolator based on a delay locked loop and an RC delay line. IEEE J. Solid-State Circuits 1999, 34, 1360–1366. [Google Scholar] [CrossRef]

- Barnaby, H.J. Total-ionizing-dose effects in modern CMOS technologies. IEEE Trans. Nucl. Sci. 2006, 53, 3103–3121. [Google Scholar] [CrossRef]

- Verbeeck, J.; Leroux, P.; Steyaert, M. Radiation effects upon the mismatch of identically laid out transistor pairs. In Proceedings of the IEEE International Conference on Microelectronic Test Structures, Amsterdam, The Netherlands, 4–7 April 2011. [Google Scholar]

- Hwang, C.S.; Chen, P.; Tsao, H.W. A high-precision time-to-digital converter using a two-level conversion scheme. IEEE Trans. Nucl. Sci. 2004, 51, 1349–1352. [Google Scholar] [CrossRef]

- Yu, J.; Dai, F.F.; Jaeger, R.C. A 12-Bit vernier ring time-to-digital converter in 0.13 μ CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 830–842. [Google Scholar] [CrossRef]

- Lu, P.; Liscidini, A.; Andreani, P. A 3.6 mW, 90 nm CMOS gated-vernier time-to-digital converter with an equivalent resolution of 3.2 ps. IEEE J. Solid-State Circuits 2012, 47, 1626–1635. [Google Scholar] [CrossRef]

- Karadamoglou, K.; Paschalidis, N.P.; Sarris, E.; Stamatopoulos, N.; Kottaras, G.; Paschalidis, V. An 11-bit high-resolution and adjustable-range CMOS time-to-digital converter for space science instruments. IEEE J. Solid-State Circuits 2004, 39, 214–222. [Google Scholar] [CrossRef]

- Christiansen, J. High Performance Time to Digital Converter; CERN Microelectronics Group: Geneva, Switzerland, 2004. [Google Scholar]

| Reference | [26] | [27] | [13] | [22] | [28] | This Work |

|---|---|---|---|---|---|---|

| Technology (nm) | 350 | 130 | 130 | 90 | 90 | 65 |

| Technique | 2-level DL | Vernier Ring | GRO | Pseudo Diff | Vernier GRO | Ring |

| Time resolution (ps) | 24 | 8 | 6 | 17–21 | 6.4 | 15.6 |

| Range (bit) | 8 | 12 | 11 | 6 | - | 18 |

| Power (mW) | 50 | 7.5 | 2.2–21 | 6.9 | 4.32 | 134 |

| DNL/INL (LSBrms) | 0.55/1.5 | - | - | 0.7/0.7 | - | 0.22/0.34 |

| Sample rate (MS/s) | 160 | 15 | 50 | 26 | 250 | 200 |

| Area () | 0.6 | 0.26 | 0.04 | 0.01 | 0.027 | 0.26 |

| Radiation Tolerance | - | - | - | - | - | 2.2 MGy |

| Reference | [29] | [11] | [30] | This Work |

|---|---|---|---|---|

| Technology (nm) | 800 | 130 | 250 | 65 |

| Technique | Pulse shrinking | DLL | Ring | |

| Application | Space | LIDAR | High Energy Physics | High Energy Physics |

| RAW resolution (ps) | 50 | 10.5 | 24 | 15.6 |

| Range (bit) | 11 | 11 | 21 | 18 |

| Power (mW) | 10 | 1.7 | 450 (multi channel) | 134 |

| DNL/INL (LSBrms) | x/0.45 | - | 0.21/2.1 | 0.22/0.34 |

| Sample rate (MS/s) | 1 | 50 | 8 | 200 |

| Area () | - | 0.11 | - | 0.26 |

| Radiation Tolerance | 1 KGy | 3.4 MGy | 0.3 KGy | 2.2 MGy |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Van Bockel, B.; Prinzie, J.; Leroux, P. Radiation Assessment of a 15.6ps Single-Shot Time-to-Digital Converter in Terms of TID. Electronics 2019, 8, 558. https://doi.org/10.3390/electronics8050558

Van Bockel B, Prinzie J, Leroux P. Radiation Assessment of a 15.6ps Single-Shot Time-to-Digital Converter in Terms of TID. Electronics. 2019; 8(5):558. https://doi.org/10.3390/electronics8050558

Chicago/Turabian StyleVan Bockel, Bjorn, Jeffrey Prinzie, and Paul Leroux. 2019. "Radiation Assessment of a 15.6ps Single-Shot Time-to-Digital Converter in Terms of TID" Electronics 8, no. 5: 558. https://doi.org/10.3390/electronics8050558