1. Introduction

An instrumentation amplifier (IA) is among the most crucial components of high-precision analog front-end (AFE) circuits [

1,

2]. Particularly for sensor applications, the primary requirements of IAs are low noise, low offset, low gain error, and high input impedance characteristics [

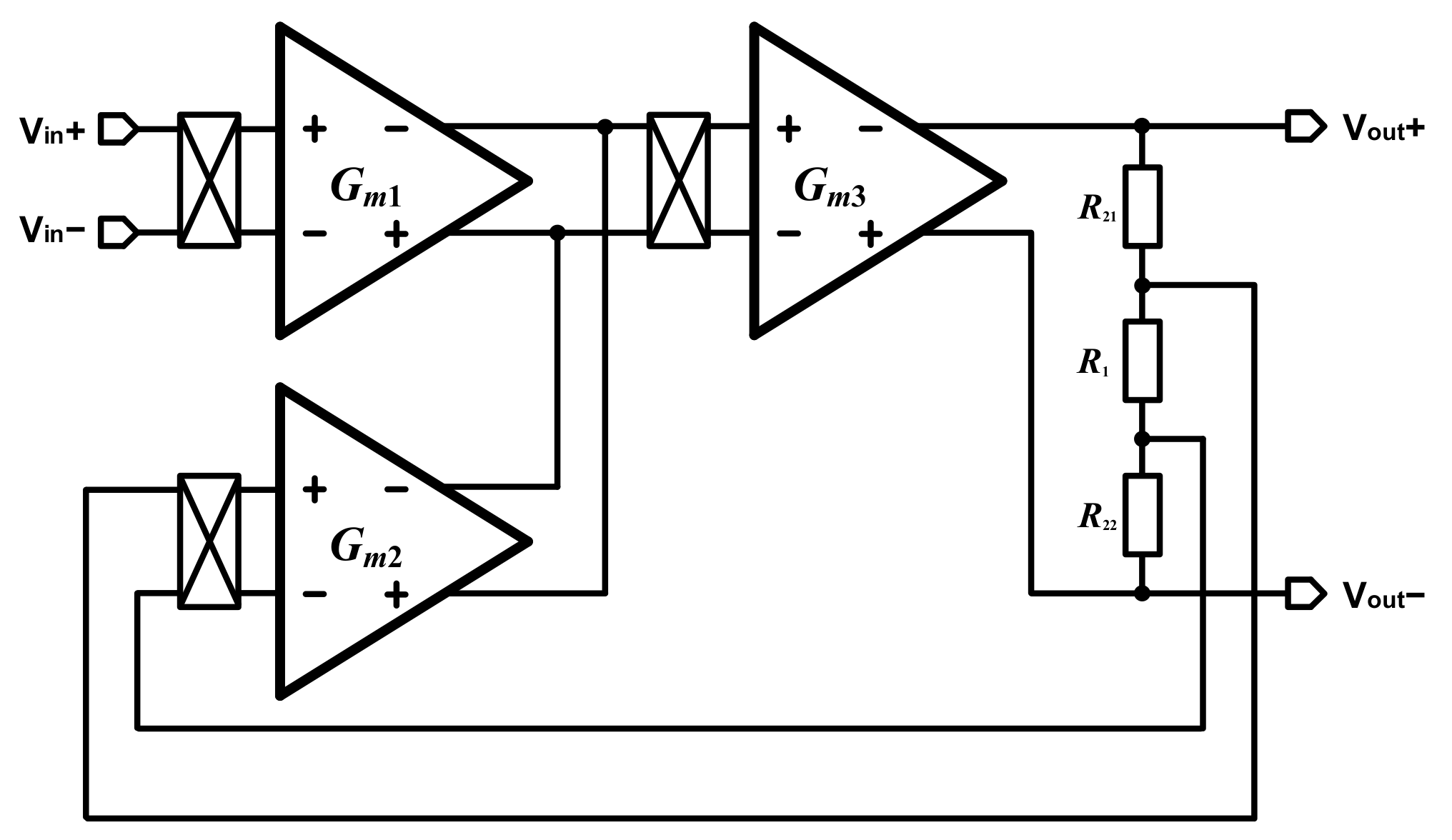

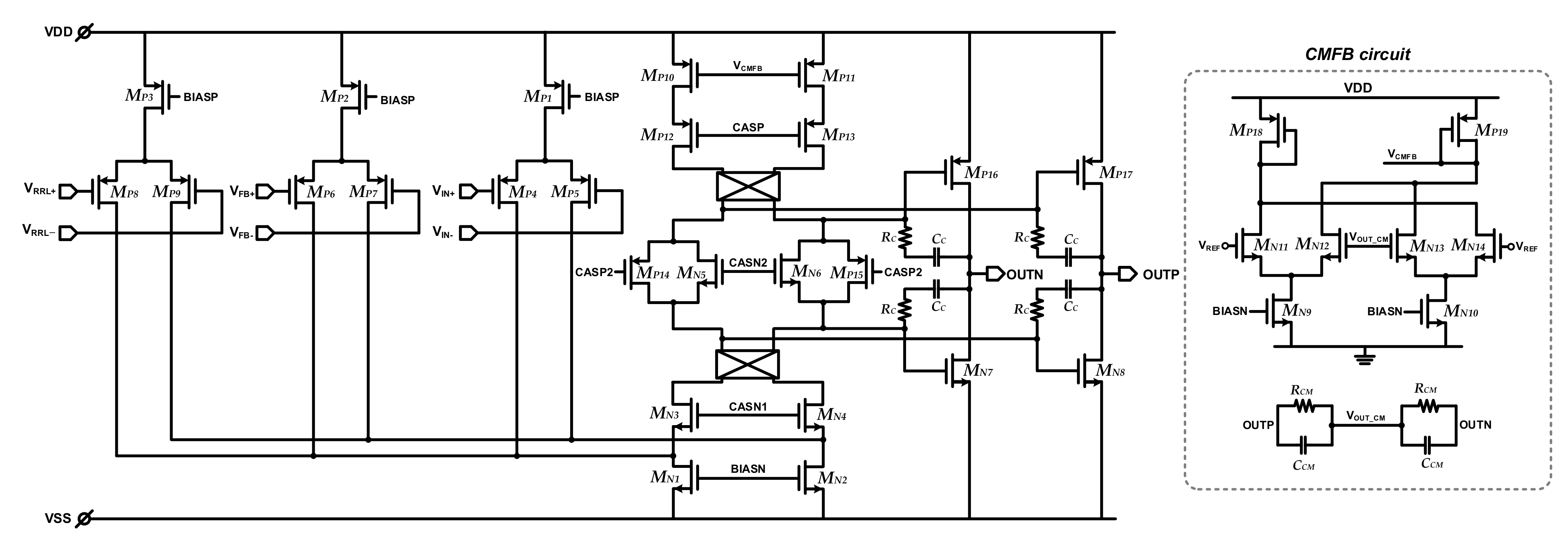

3]. Current-feedback instrumentation amplifiers (CFIAs) with a chopper structure, as depicted in

Figure 1 [

4], are among the IA structures of the sensor AFE that can satisfy these criteria.

The input signal of the CFIA is converted to current via transconductance (

Gm1), and the output feedback voltage forms negative feedback by supplying current to the output of (

Gm1) via transconductance (

Gm2). The gain (

Gm3) eliminates the difference between the output power currents of the transconductances (

Gm1 and

Gm2) and the output voltage (

Vout) shown in

Figure 1 and expressed in Equation (1).

As shown in Equation (1), the closed-loop gain of the CFIA is determined by the degree of matching between the input transconductances (Gm1 and Gm2) and resistors R1 and R2.

The chopper CFIA has a higher common-mode rejection ratio (CMRR) because the input common-mode can be isolated by converting the input differential voltage signal into the input differential current. By averaging the input mismatch using the input chopper, a higher-input CMRR can be achieved.

In addition, the power consumption can be reduced because the input signal path (from Gm1 to Gm3) and feedback signal path (from Gm2 to Gm3) share the output stage (Gm3).

When the junction capacitances of the chopper switches are disregarded, it is possible to obtain a high-input impedance in the CFIA because the gates of the input MOSFET differential pair form the input nodes. The input impedance of the CFIA can be expressed as Equation (2).

where

Cg is the gate input capacitance of the input transconductance (

Gm1), and

fCH is the chopper clock frequency.

The CFIA, with such a simple structure, has numerous advantages. However, it can still degrade the performance, owing to DC offset caused by the mismatch of MOSFETs at the input stage or flicker noise caused by dangling bonds at the interface of the gate oxide and silicon substrates in MOSFETs [

5].

Therefore, the CFIA requires a dynamic offset compensation (DOC) technique for high-precision sensors. Auto-zeroing (AZ) and chopping are prevalent DOC techniques used in amplifiers [

6].

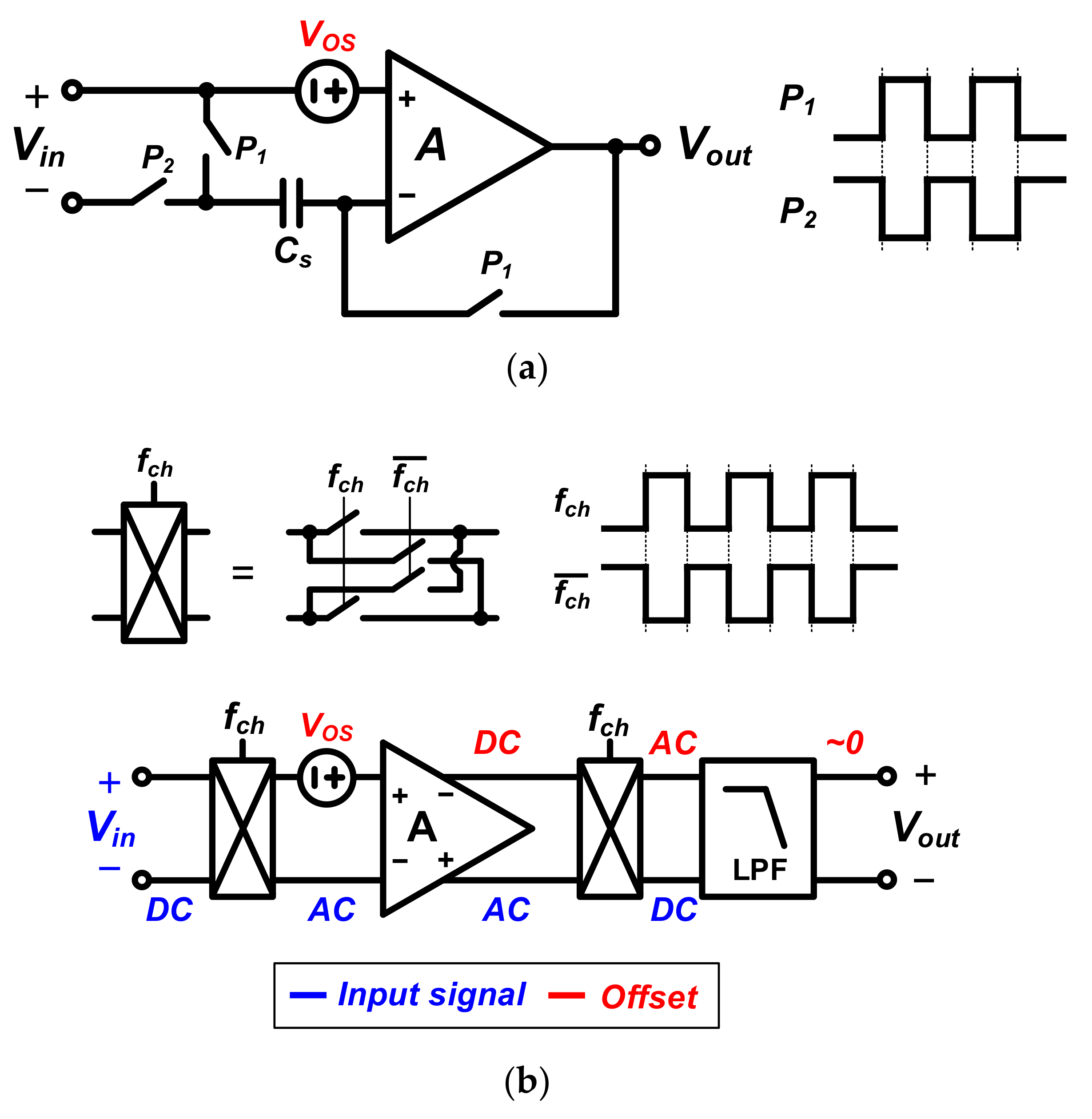

Figure 2 shows two popular DOC methods: AZ and chopping. AZ is a sampling-based method used to remove the input end offset of an op amp. As shown in

Figure 2a, the AZ is controlled by clocks

P1 and

P2, which are the offset sampling and amplifying phases, respectively. By storing the offset in the offset sampling capacitor (

Cs) during sampling phase

P1 and subtracting the offset from

Cs in amplifying phase

P2, it is possible to reduce the effect of the offset on the output. However, there is a disadvantage in that the high-frequency thermal noise is folded into the low-frequency band and integrated due to aliasing due to the use of offset sampling in the capacitor.

In the chopping technique, as shown in

Figure 2b, the frequency bands of the signal and noise are separated using amplitude modulation to implement the low noise characteristics of the circuit. To prevent the amplification of low-frequency noise, signals are modulated at high frequencies using chopper frequencies and amplified. Subsequently, low-frequency noise is sent to high frequencies through demodulation, and signals are sent back to low-frequency bands to achieve low-noise characteristics.

In contrast to the AZ technique, the chopping technique does not generate aliasing owing to sampling, allowing for the implementation of lower-noise characteristics. CFIA was therefore implemented using the chopping technique in this study.

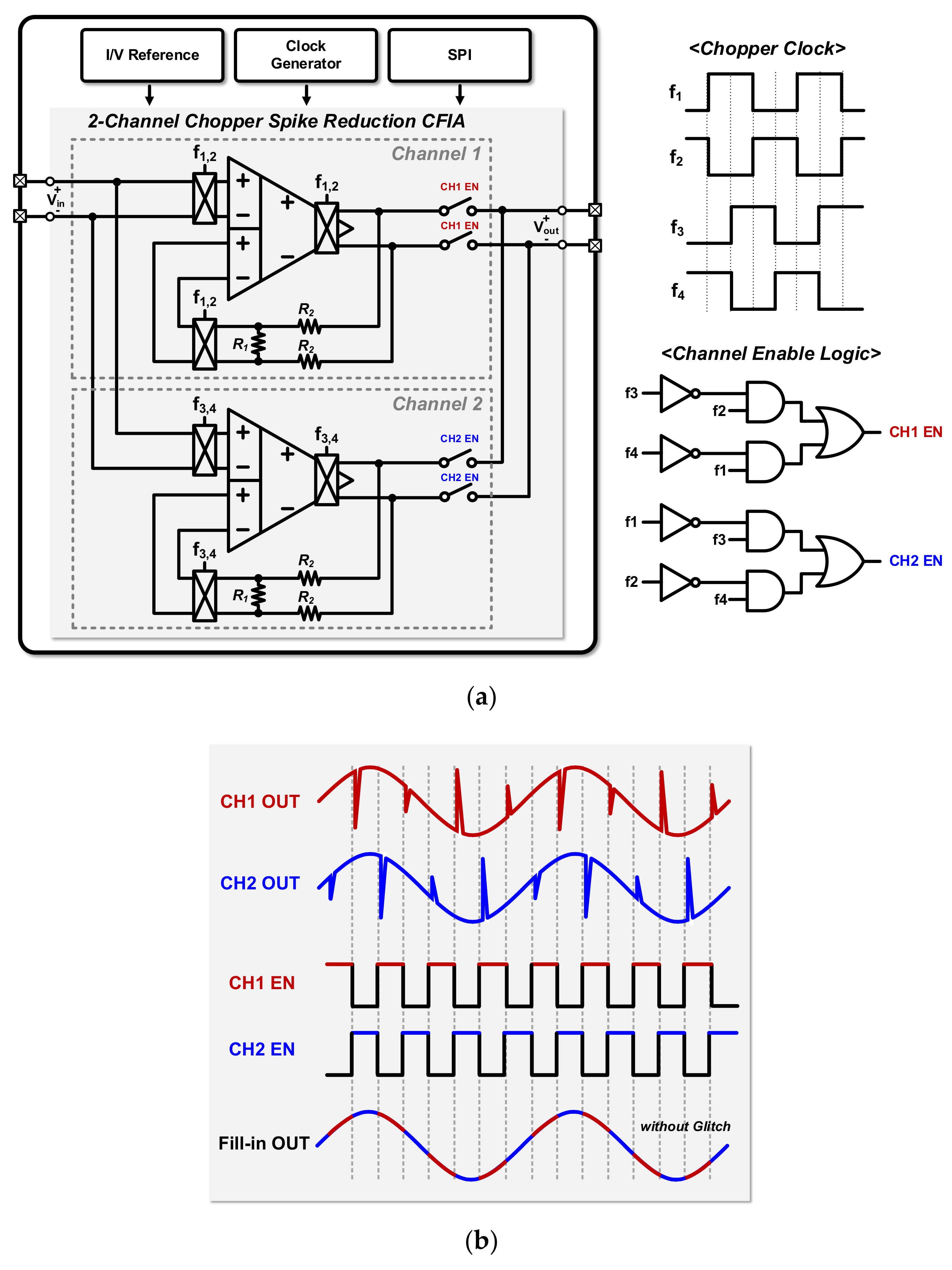

The chopper amplifier can achieve lower noise without requiring noise folding in the AZ amplifier, although it is subject to two major drawbacks: ripple and glitch. A ripple is the upmodulated offset resulting from the chopper operation. In

Figure 3a, the offset of the operational transconductance amplifier (OTA) is converted to current like a red signal, and then changed to high frequency ripple component at the same frequency as the chopper frequency (

fch), like a pink signal. When a low-frequency filter (LPF) is used to eliminate ripple, the overall bandwidth is reduced below the chopper frequency, and a large area becomes necessary, owing to the large RC constants.

Figure 3b demonstrates that a chopper glitch also occurs at the edge of the chopper clock, owing to the delay caused by the finite bandwidth of the operational OTA. The blue signal through chopper is delayed in voltage to current conversion, as is the red signal, due to the finite bandwidth of the OTA. After that, the signal that went through chopper again has a glitch in the form of a pink signal. WThis results in input signal distortion at a frequency twice the chopper clock frequency (2

fch). During the up- and downconversion operations of the chopper, chopper glitches and their harmonics produce intermodulation distortion (IMD). Recent reports indicate that fill-in techniques reduce glitches and glitch-induced IMD [

7]. In [

7], chopped AZ amplifiers were used in a ping-pong manner; however, in this study, we employed a dual chopper amplifier with a ripple rejection loop. Because the chopper amplifier does not experience noise folding owing to sampling operations, this amplifier can achieve a low-noise floor that is nearly limited by the thermal noise level. Moreover, the correlated noise components of the dual-channel chopper amplifier can be reduced [

8], resulting in a reduced noise level.

In the dual-path structure, the layout matching of the switch and amplifier causes similar offsets and charge injections for the two paths, accounting for much of the switching noise. The noise caused by non-ideal switch behavior can then be eliminated by the adder. Moreover, the adder can mitigate other sources of common mode noise in the two paths, such as supply noise.

Figure 4 depicts the noise structure, which is comprised of two paths and an adder.

The equivalent noise at the output of the adder is expressed as:

where

A is the gain of the adder, and α is the correlation efficiency between the noise source path, ranging from 0 to 1. The proposed fill-in technique uses a dual path with α greater than 0. Therefore, additional noise reduction is possible, as shown in Equation (3).

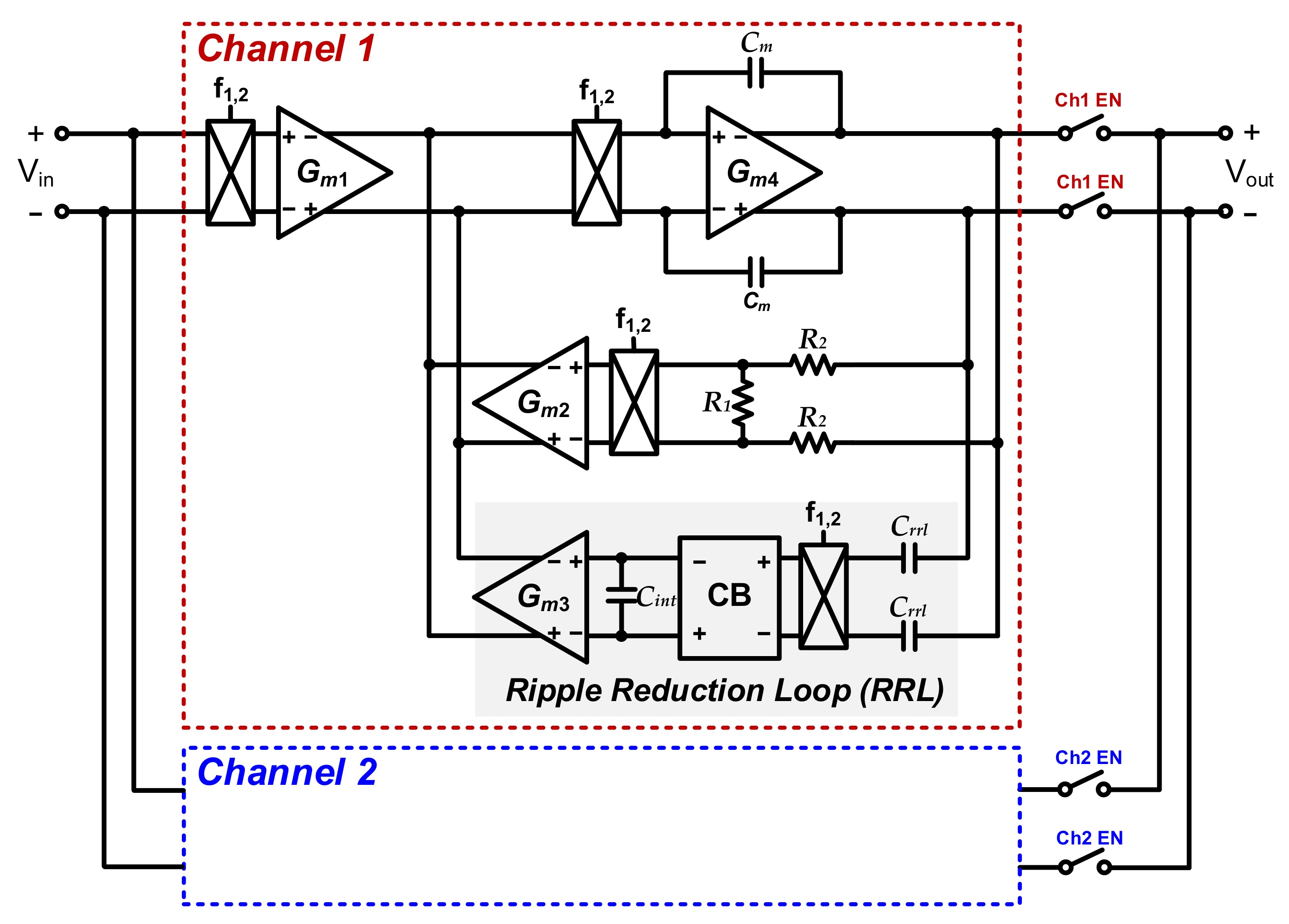

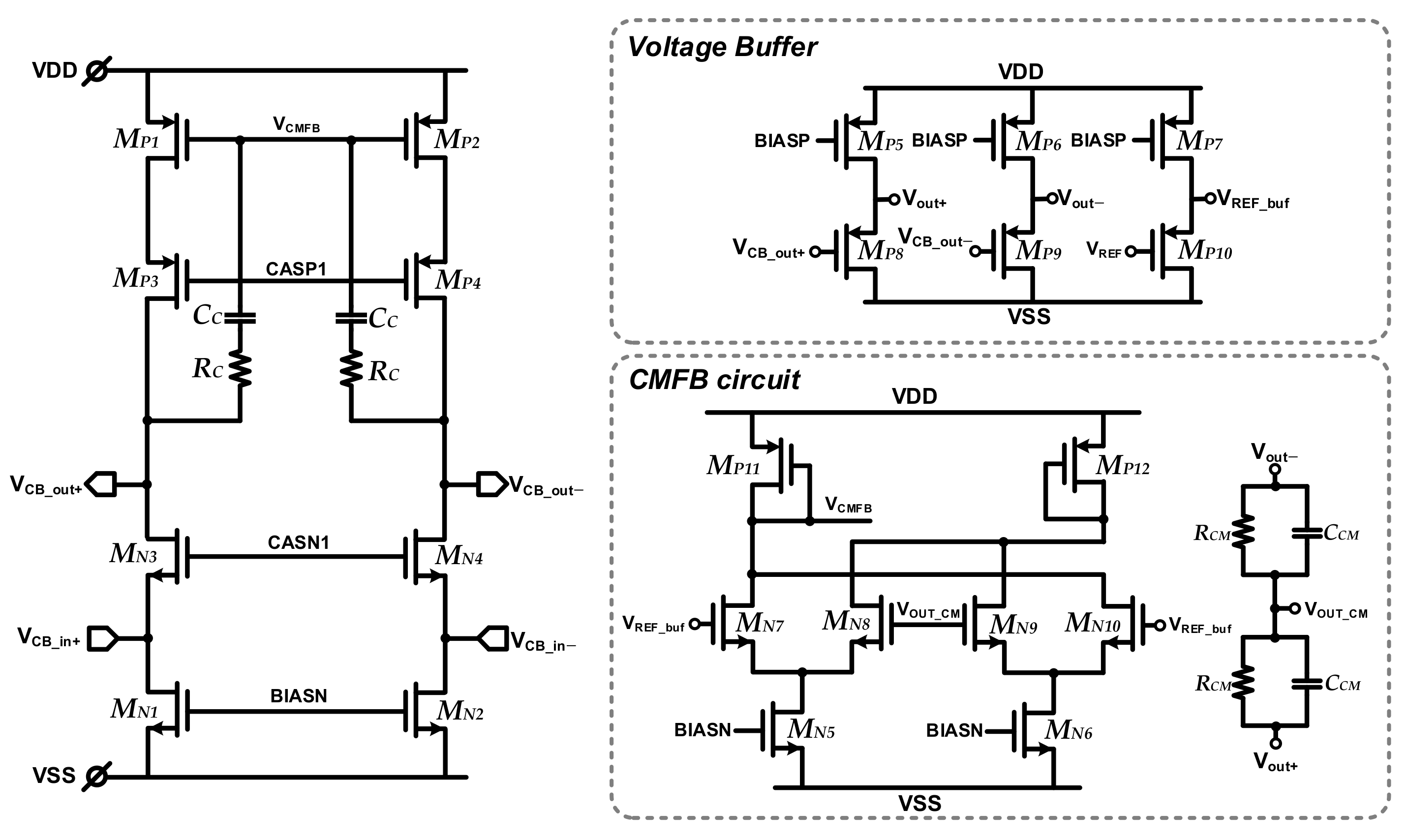

A low-noise CFIA employing a dual-chopper fill-in technique with a ripple reduction loop (RRL) is proposed in this study. Conventional chopper amplifiers suffer from glitches due to the chopper operation and the amplifier phase delay. In the proposed circuit, the glitch can be reduced by using the dual-channel fill-in technique. Glitch-induced IMD reduction was achieved using the fill-in technique. A wider bandwidth was also achieved by relaxing the LPF requirement using the RRL and glitch reduction. Using the chopping technique, noise folding was prevented, and a low-noise characteristic was implemented. An additional noise reduction was achieved through a noise correlation factor between the dual channels.

3. Measurement Results

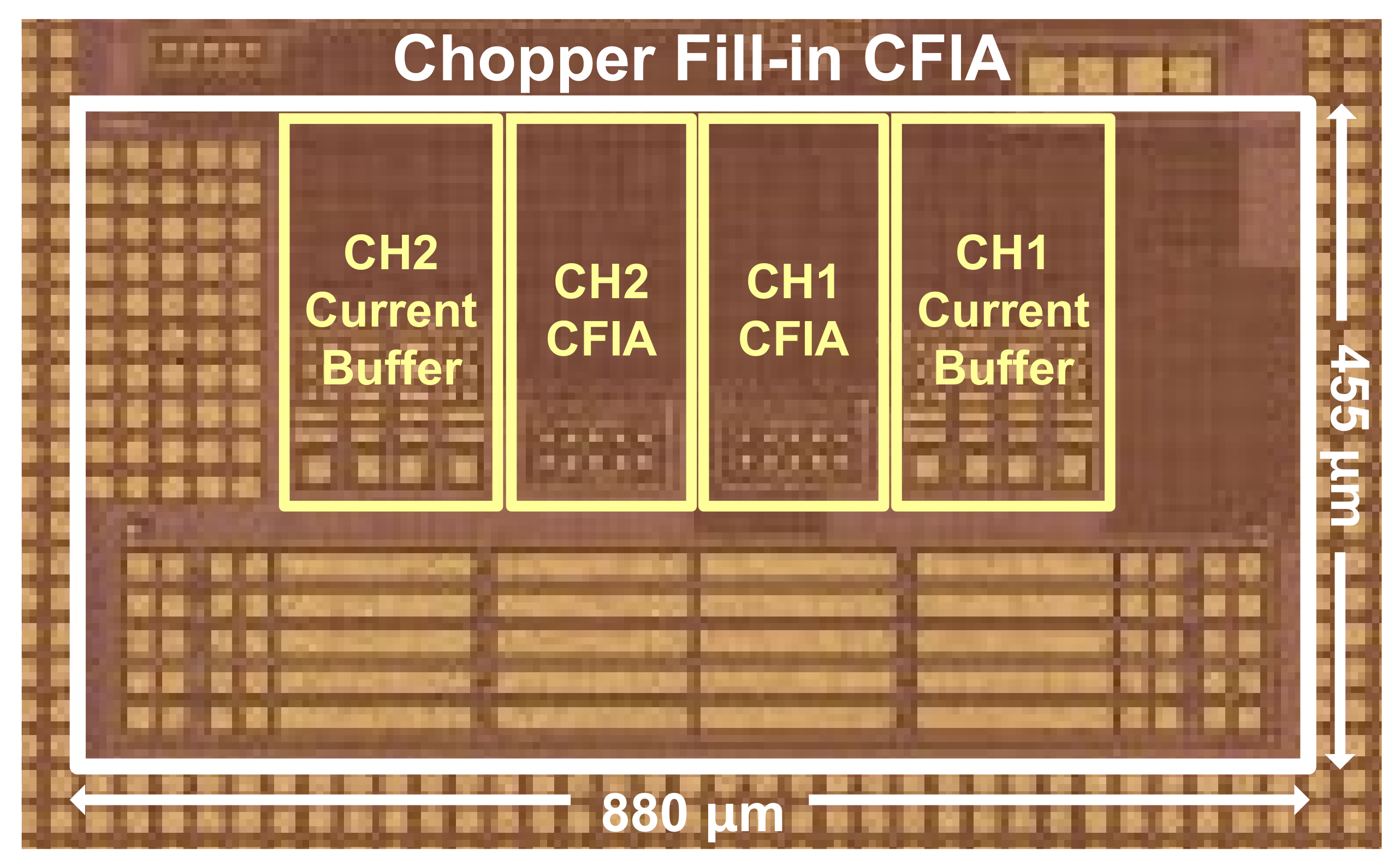

A die photograph of the proposed CFIA is shown in

Figure 13. The circuit was fabricated using a 0.18 µm CMOS process, and the area of the proposed chopper fill-in CFIA circuit is 455 × 880 µm.

Figure 14 depicts the test board and measurement environment used to evaluate the performance of the proposed CFIA using a printed circuit board.

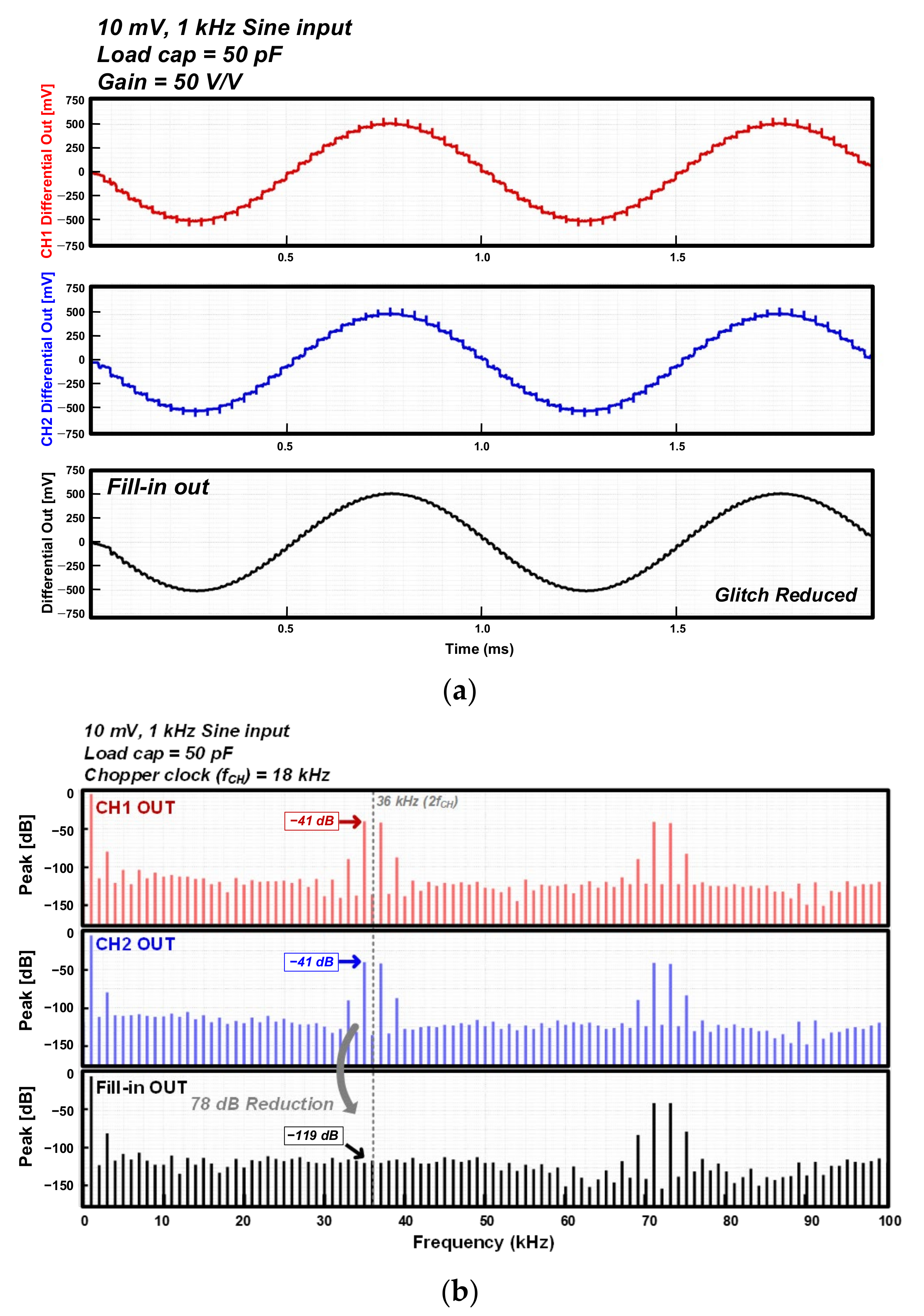

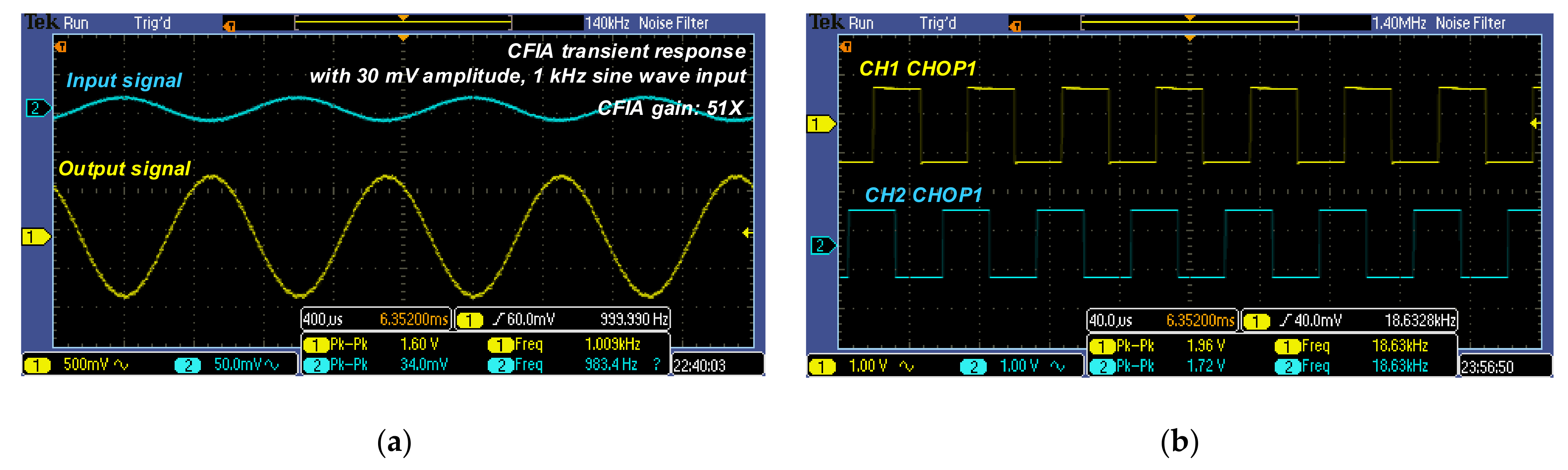

The transient result of the proposed CFIA is shown in

Figure 15. The proposed CFIA had an ideal gain of 51 V/V. As shown in

Figure 15a, an input sine signal of 30 mV

peak-to-peak and 1 kHz was amplified to a 1.6-V

peak-to-peak sine signal. The chopper clocks of channels 1 and 2 have a 1/4 phase difference, as shown in

Figure 15b, and the proposed circuit uses a chopper frequency of 18 kHz.

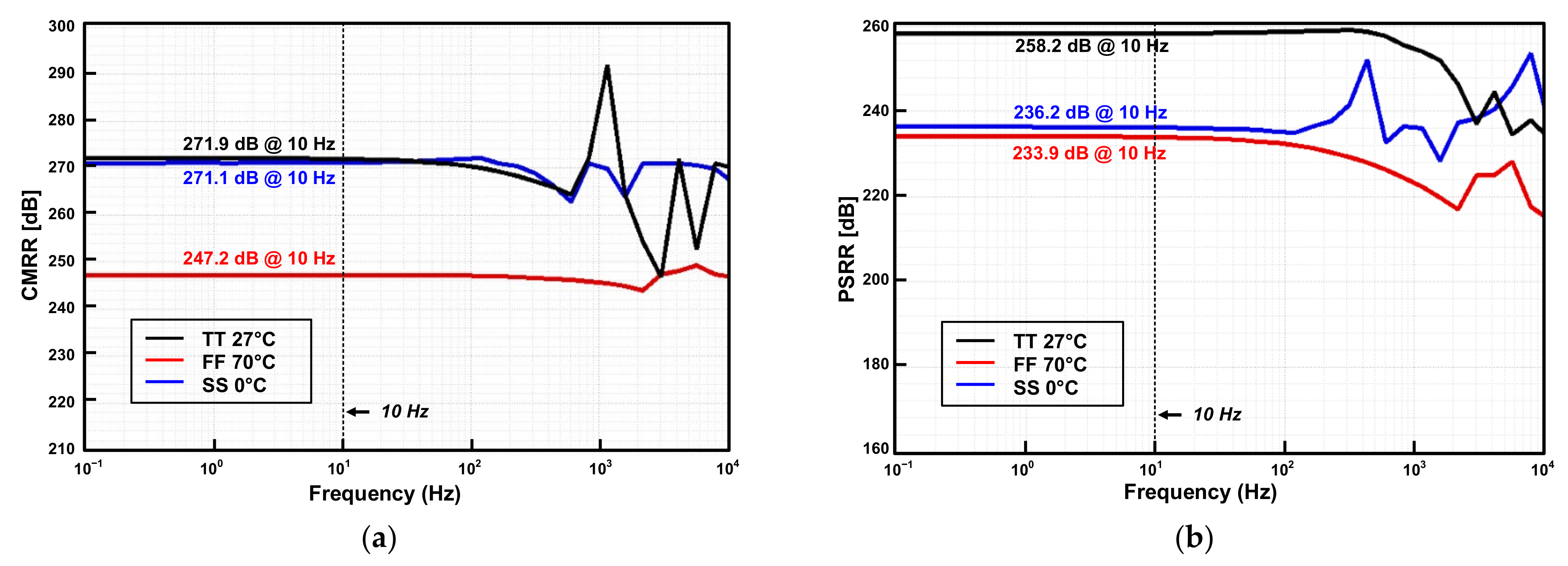

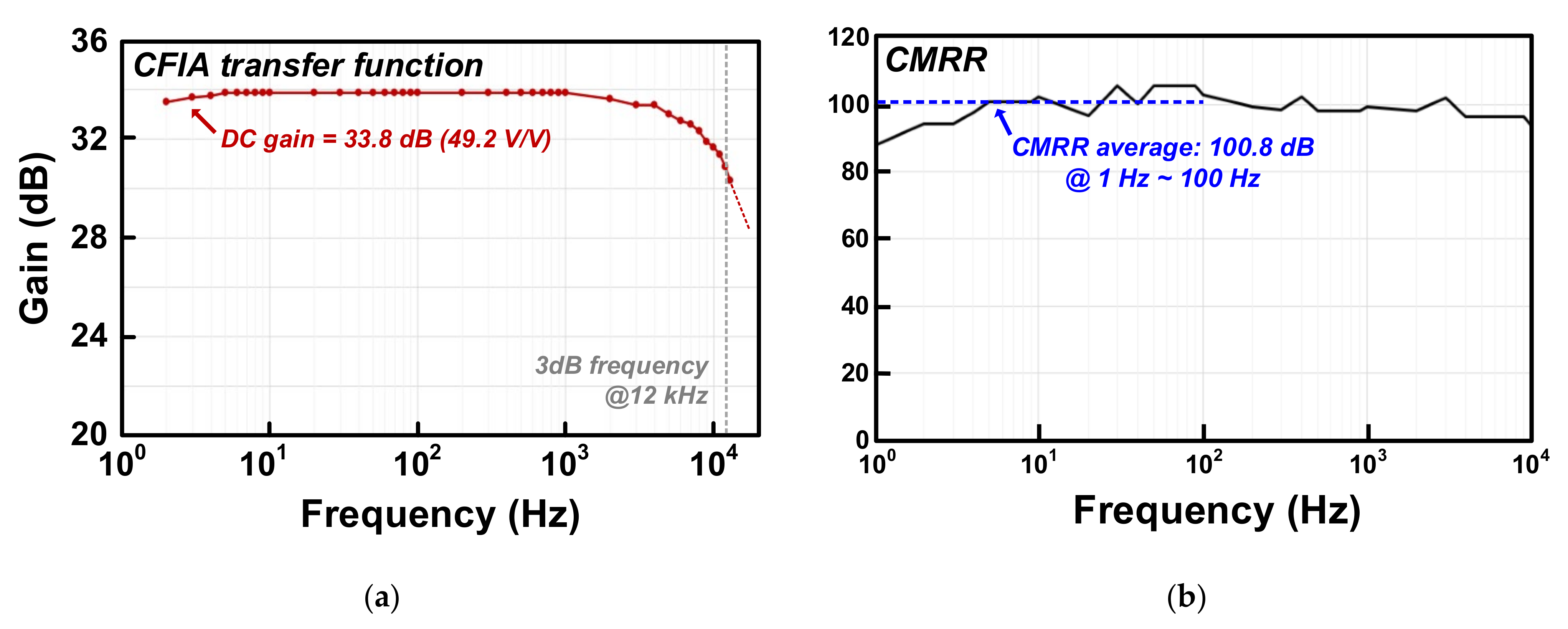

Figure 16a represents the measurement results of the proposed CFIA transfer function. The transfer function has an average DC gain of 33.8 dB (49.2 V/V) and a 3-dB frequency of 12 kHz at 30.9 dB, resulting in a gain bandwidth (GBW) of 420 kHz.

Figure 16b shows the CMRR measurement results of the proposed CFIA. The average CMRR from 1 Hz to 100 Hz is 100.8 dB.

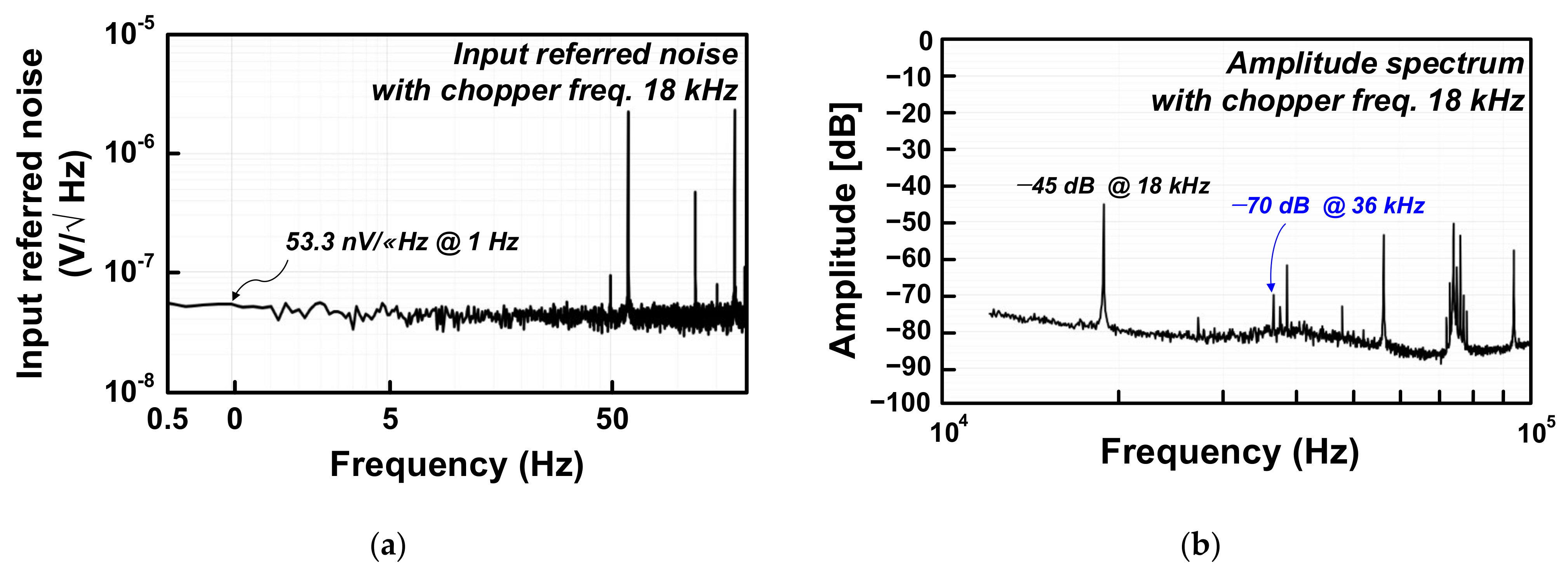

Figure 17a presents the measured input-referred noise of the proposed CFIA; at 1 Hz, its value was 53.3 nV/√Hz. For the IMD tone amplitude measurement, 1 kHz and 10 mV sine inputs were used. As shown in

Figure 17b, the measured amplitude of the IMD tone a twice the chopper frequency of 36 kHz with a chopper frequency of 18 kHz is −70 dB.

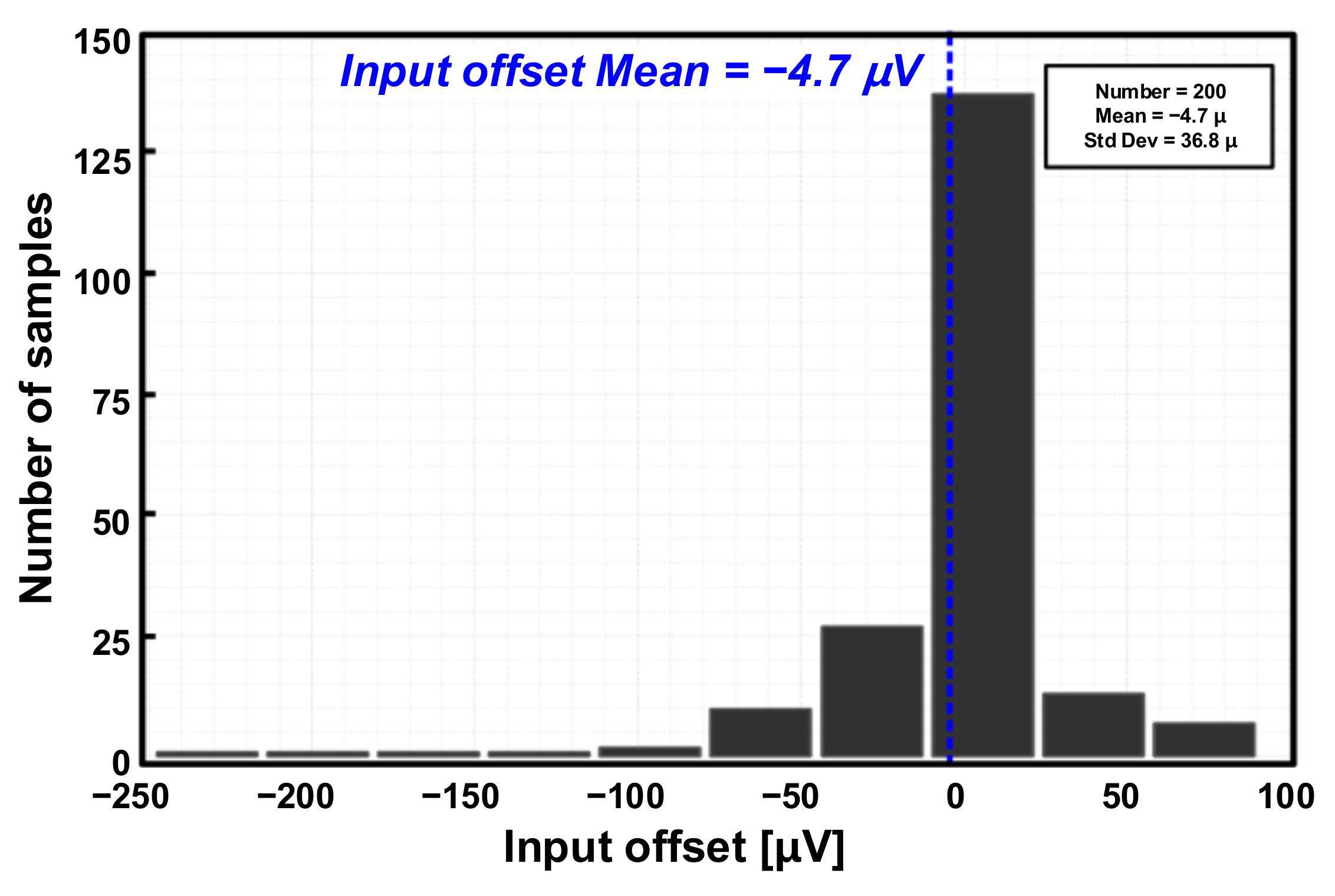

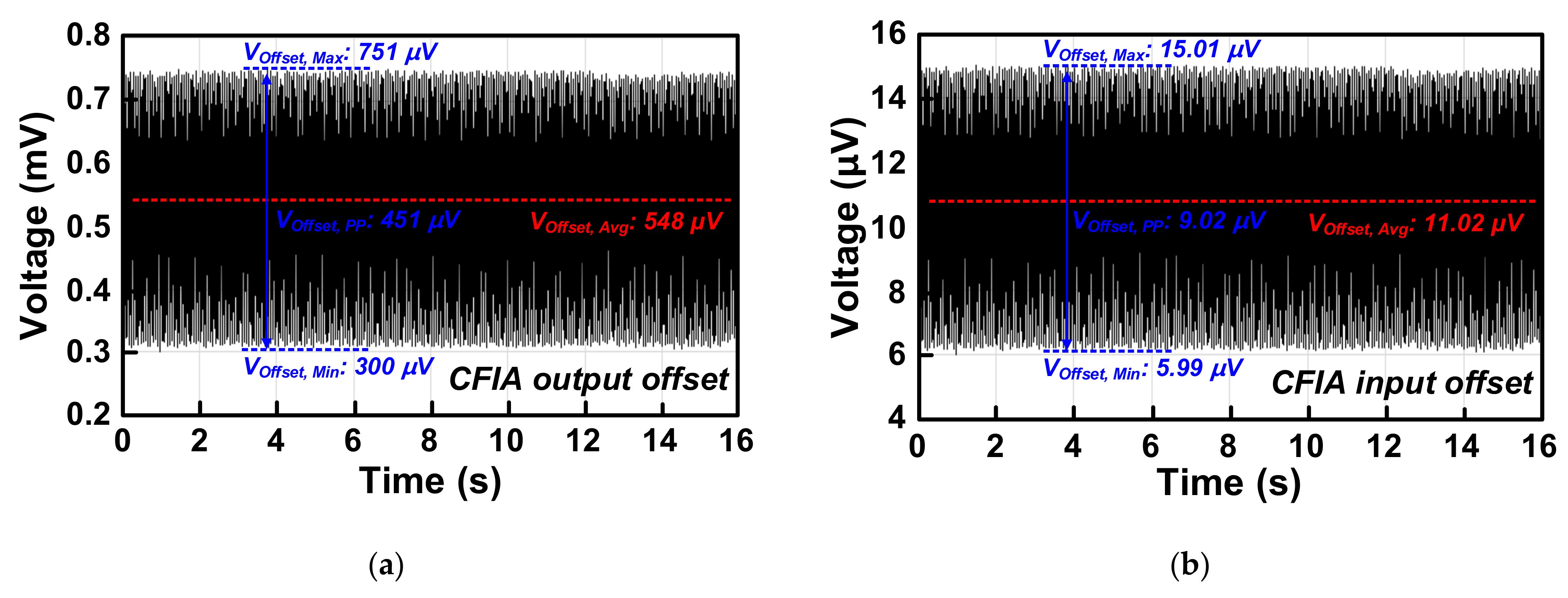

The measured output and input offset of the proposed CFIA is shown in

Figure 18. The output offset measurement result shows that an average offset of 548 µV is present in the output of the CFIA and has a peak-to-peak value of 451 µV.

Figure 18b shows the result of converting the measured output offset of the CFIA into input offset, which has an input average offset of 11.02 µV.

The calculated noise efficiency factor (NEF) for the proposed CFIA is 4.4.

Table 6 shows a performance summary and comparison of the proposed circuit with other previous works on low-noise CFIAs.

4. Conclusions and Discussion

In this study, we present a dual-chopper CFIA with an RRL for glitch reduction. The chopping technique was used to obtain noise characteristics in the amplifier. However, glitches caused by chopping occur at each edge of the chopper clock, resulting in glitch-induced IMD. Owing to the input offset, the chopping technique also produces ripples.

Glitch-induced IMD was reduced in this study using a fill-in technique, whereby only neat signals were alternately used as outputs by avoiding the glitch section with a dual-chopping channel CFIA. By using the dual channel, it was possible to obtain an effect of noise reduction according to the noise correlation factor between channels. The RRL was implemented to reduce the ripple caused by chopping so that a high-order LPF was not required.

The proposed CFIA is based on a low-noise chopper fully differential difference amplifier with a cascode stage and a Monticelli class-AB output stage, which can drive a larger load and increase power efficiency.

The proposed dual-chopper CFIA was constructed using a standard 0.18 µm CMOS process, occupying an effective area of 1.28 mm2, and its current consumption with a 1.8-V power supply is 29.5 μA. The proposed CFIA had a gain of 51 V/V and GBW of 420 kHz. The input-referred noise at 1 Hz was 53.3 nV/√Hz, and integrated noise was 24.7 nV/√Hz, with an NEF of 4.48. The CMRR and PSRR have values of 108.8 dB and 105.3 dB at 100 Hz, respectively. The input offset is 11 μV, with a 51 V/V gain. The IMD amplitude at the chopper frequency harmonic is -70 dB.