Characteristics Analysis of IGZO TFT and Logic Unit in the Temperature Range of 8–475 K

Abstract

1. Introduction

2. Devices and Methods

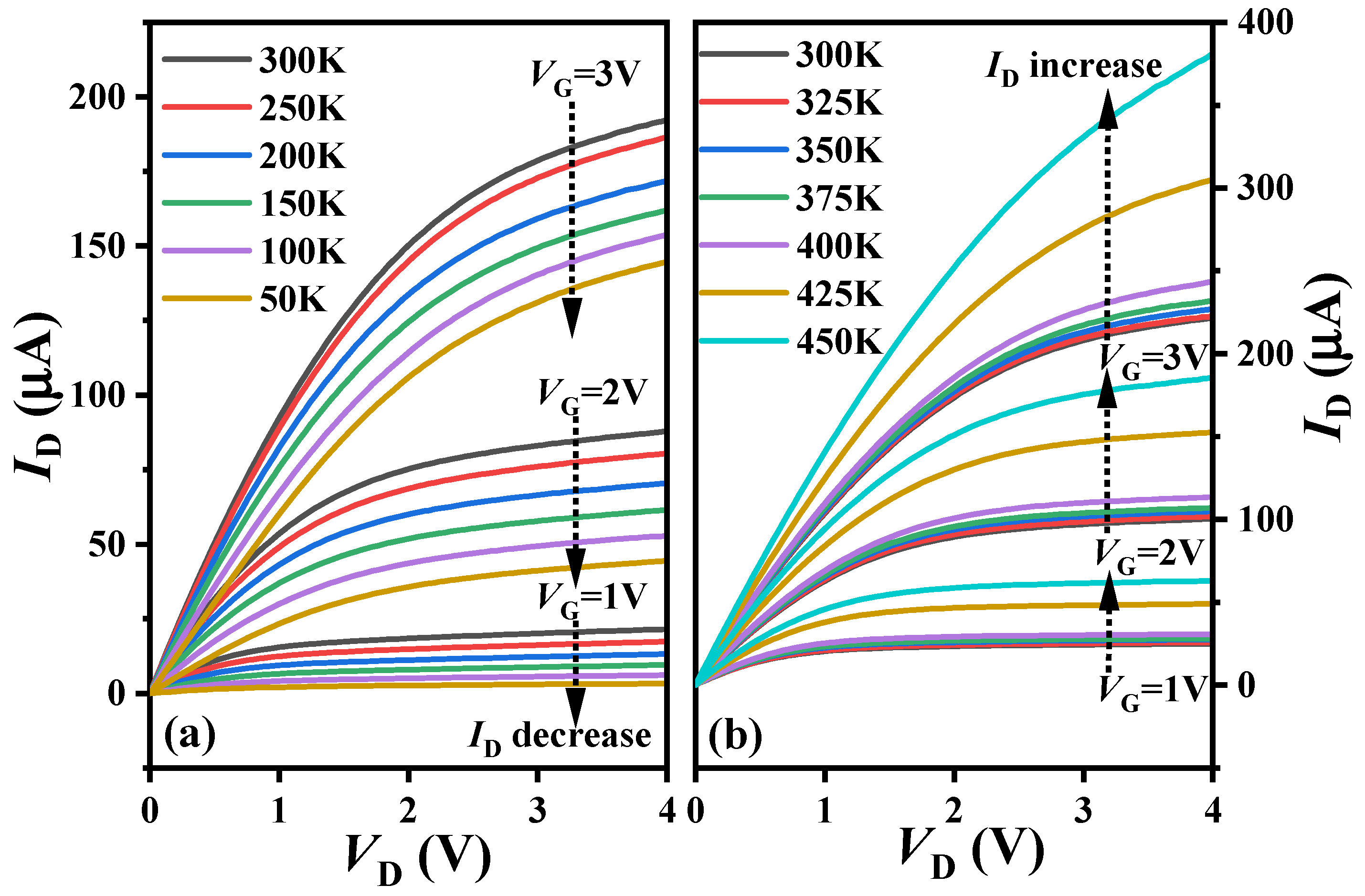

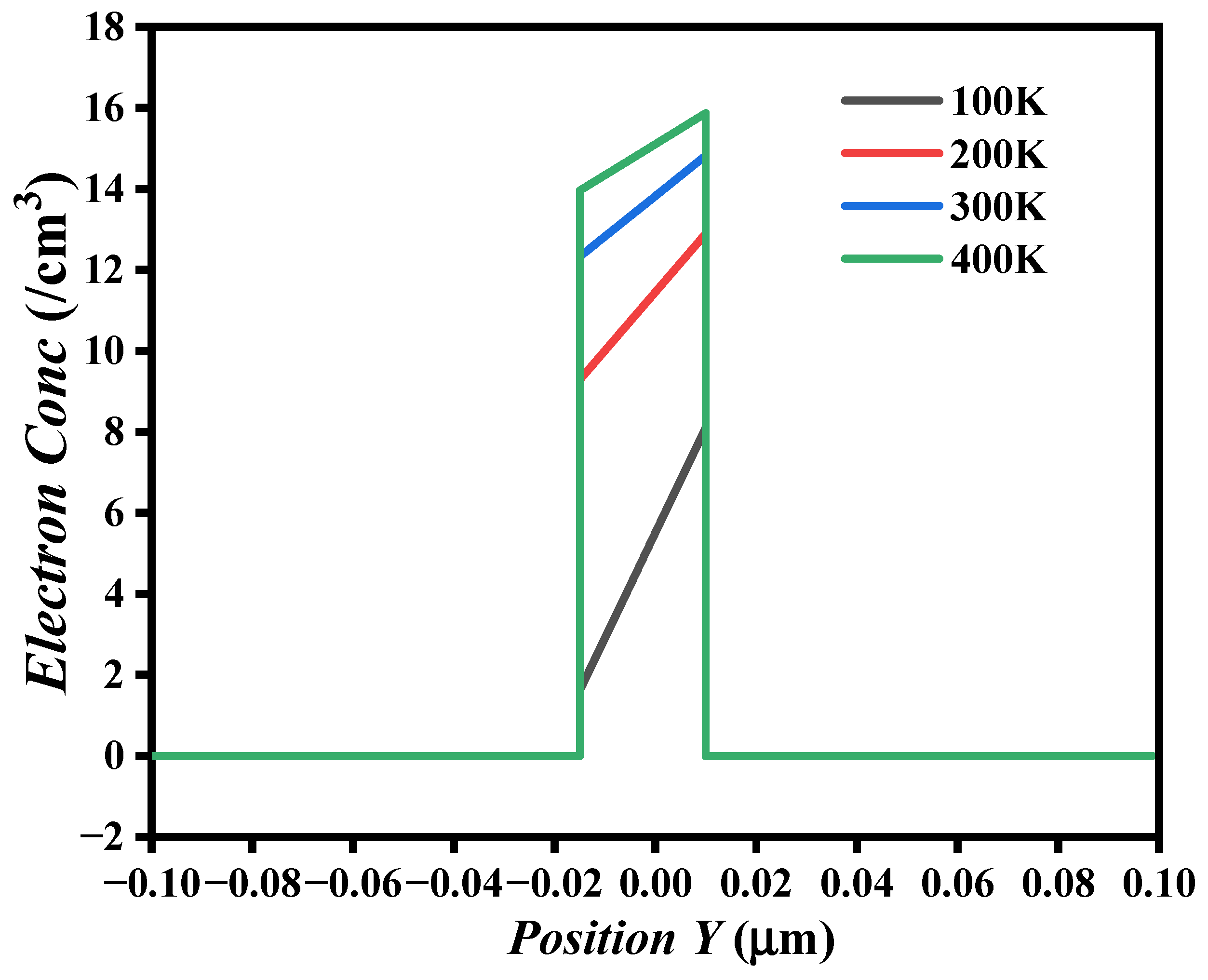

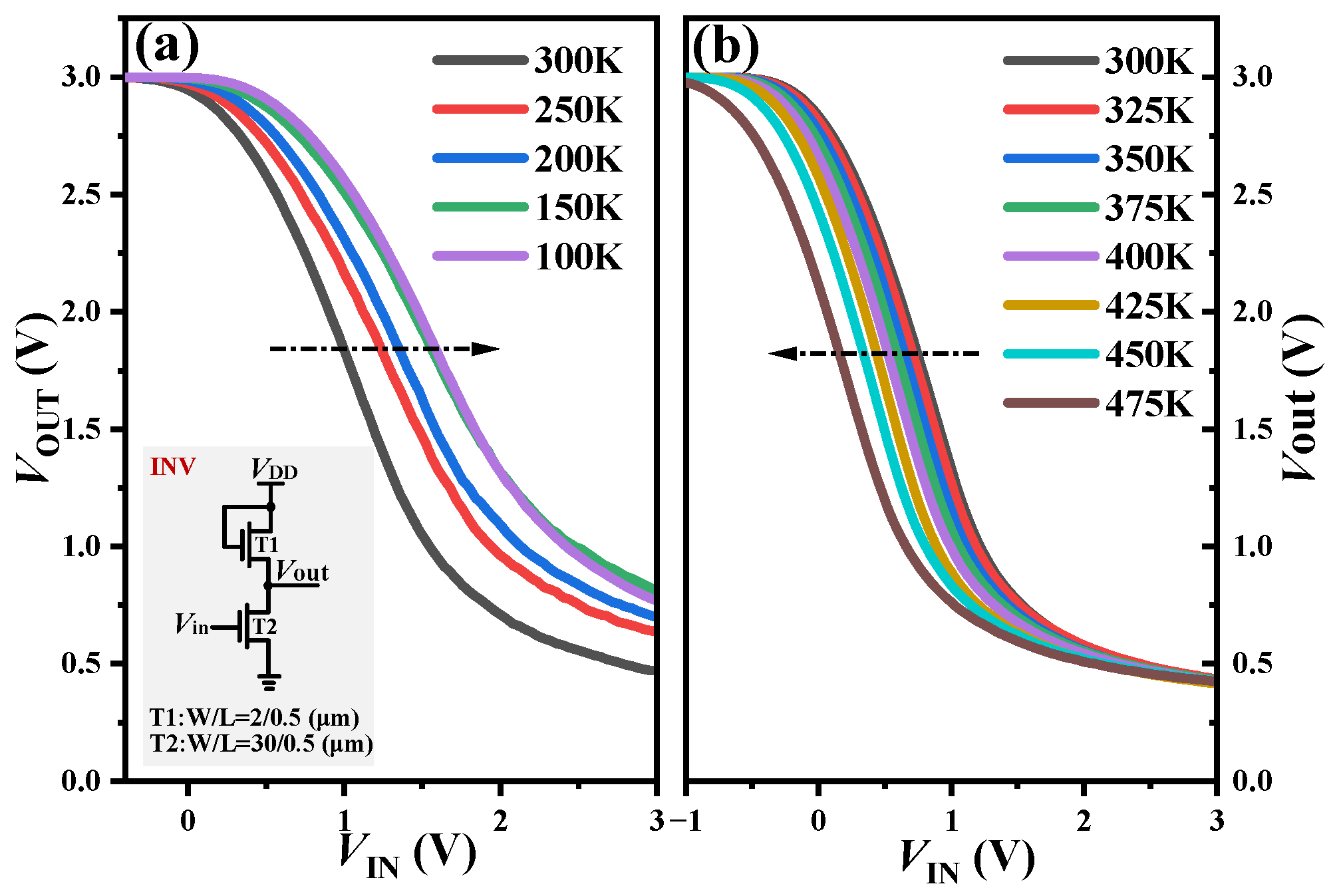

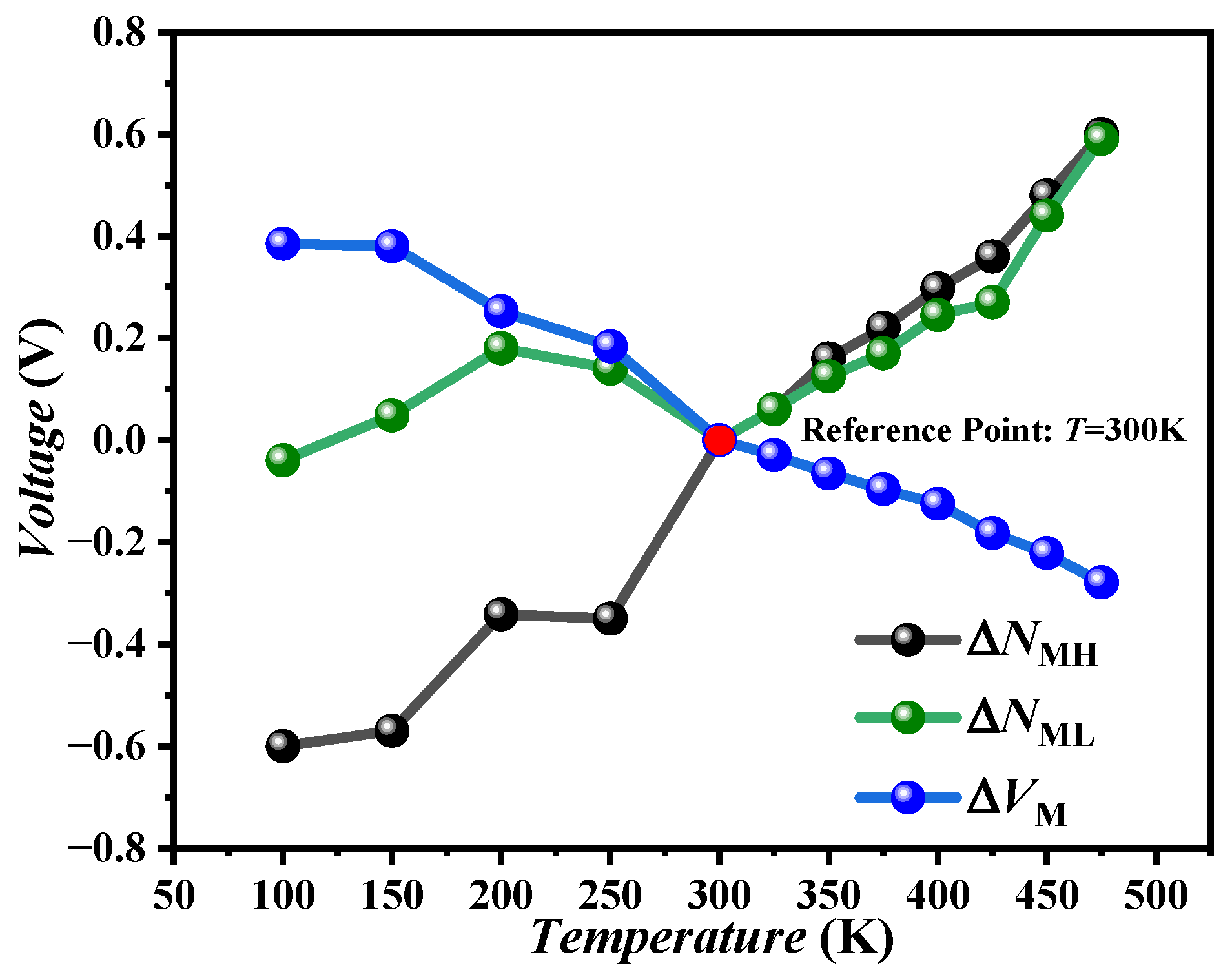

3. Experimental Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zhu, Y.; He, Y.L.; Jiang, S.S.; Chen, C.S.; Wan, Q. Indium–gallium–zinc–oxide thin-film transistors: Materials, devices and applications. J. Semicond. 2021, 42, 031101. [Google Scholar] [CrossRef]

- Choi, S.; Kim, S.; Jang, J.; Kim, J.; Kim, D.M.; Choi, S.J.; Mo, H.S.; Lee, S.M.; Kim, D.H. Oxygen content and bias influence on amorphous InGaZnO TFT-based temperature sensor performance. IEEE Electron Device Lett. 2019, 40, 1666–1669. [Google Scholar] [CrossRef]

- Tang, H.Y.; Li, Y.T.; Sokolovskij, R.; Sacco, L.; Zheng, H.; Ye, H.Y.; Yu, H.Y.; Fan, X.J.; Tian, H.; Ren, T.L.; et al. Ultra-high sensitive NO2 gas sensor based on tunable polarity transport in CVD-WS2/IGZO pn heterojunction. ACS Appl. Mater. Interfaces 2019, 11, 40850–40859. [Google Scholar] [CrossRef] [PubMed]

- Bai, Z.H.; Gong, T.Z.; Duan, X.L.; Wang, J.W.; Xiao, K.; Geng, D.; Li, L. Low frequency noise of Channel-All-Around (CAA) InGaZnO field effect transistors. IEEE Electron Device Lett. 2022, 43, 2117–2120. [Google Scholar] [CrossRef]

- Liao, C.W. Mobility impact on compensation performance of AMOLED pixel circuit using IGZO TFTs. J. Semicond. 2019, 40, 022403. [Google Scholar] [CrossRef]

- Masashi, O.; Yoshinori, A.; Kazuki, T.; Tatsuki, K.; Satoru, O.; Akio, S.; Kunihiro, F.; Shuhei, N.; Tatsuya, O.; Ryota, H.; et al. 3D-Stacked CAAC-In-Ga-Zn oxide FETs with gate length of 72nm. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 1950–1953. [Google Scholar]

- Kang, Y.Y.; Han, K.Z.; Kumar, A.; Wang, C.K.; Sun, C.; Zhou, Z.P.; Zhou, J.R.; Gong, X. Back-End-of-Line compatible fully depleted CMOS inverters employing Ge p-FETs and a-InGaZnO n-FETs. IEEE Electron Device Lett. 2021, 42, 1488–1491. [Google Scholar] [CrossRef]

- Han, K.Z.; Samanta, S.; Xu, S.Q.; Wu, Y.; Gong, X. High field temperature-independent field-effect mobility of amorphous indium-gallium-zinc oxide thin-film transistors: Understanding the importance of equivalent-oxide-thickness downscaling. IEEE Trans. Electron Devices 2021, 68, 118–124. [Google Scholar] [CrossRef]

- Kim, M.J.; Park, H.J.; Yoo, S.; Cho, M.H.; Jeong, J.K. Effect of channel thickness on performance of ultra-thin body IGZO field-effect transistors. IEEE Trans. Electron Devices 2022, 69, 2409–2416. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Electronic structure of the amorphous oxide semiconductor a-InGaZnO4–x: Tauc-Lorentz optical model and origins of subgap states. Phys. Status Solidi A 2009, 206, 860–867. [Google Scholar] [CrossRef]

- Sheng, J.; Hong, T.; Lee, H.; Kim, K.; Sasase, M.; Kim, J.; Hosono, H.; Park, J.S. Amorphous IGZO TFT with high mobility of ~70 cm2/vs via vertical dimension control using PEALD. ACS Appl. Mater. Interfaces 2019, 43, 40300–40309. [Google Scholar] [CrossRef] [PubMed]

- Chatterjee, I.; Zhang, E.X.; Bhuva, B.L. Bias dependence of total-dose effects in bulk FinFETs. IEEE Trans. Nucl. Sci. 2013, 60, 4476–4482. [Google Scholar] [CrossRef]

- Ho, D.; Choi, S.; Kang, H. In situ radiation hardness study of amorphous Zn-In-Sn-O thin-film transistors with structural plasticity and defect tolerance. ACS Appl. Mater. Interfaces 2023, 15, 33751–33762. [Google Scholar] [CrossRef] [PubMed]

- Costa, J.C.; Pouryazdan, A.; Panidi, J. Flexible IGZO TFTs and their suitability for space applications. IEEE J. Electron Devices Soc. 2019, 7, 1182–1190. [Google Scholar] [CrossRef]

- Park, S.; Song, M.K.; Sung, T. Effect of X-ray irradiation on a-IGZO and LTPS thin-film transistors for radiography applications. Appl. Surf. Sci. 2021, 550, 149237. [Google Scholar] [CrossRef]

- Kim, D.G.; Kim, J.U.; Lee, J.S. Negative threshold voltage shift in an a-IGZO thin film transistor under X-ray irradiation. RSC Adv. 2019, 9, 20865–20870. [Google Scholar] [CrossRef] [PubMed]

- Dayananda, G.K.; Rai, C.S.; Jayarama, A. Simulation model for electron irradiated IGZO thin film transistors. J. Semicond. 2018, 39, 022002. [Google Scholar] [CrossRef]

- Pan, C.C.; Yang, S.B.; Chen, L.L. Improvement in bias stability of IGZO TFT with etching stop structure by UV irradiation treatment of active layer island. IEEE J. Electron Devices Soc. 2020, 8, 524–529. [Google Scholar] [CrossRef]

- Guo, Z.; Li, K.; Li, X. Total-Ionizing-Dose Effects in IGZO Thin-Film Transistors. IEEE Trans. Nucl. Sci. 2023, 70, 2002–2007. [Google Scholar] [CrossRef]

- Dayananda, G.K.; Rai, C.S.; Jayarama, A. Study of radiation resistance property of a-IGZO thin film transistors. In Proceedings of the 2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 20–21 May 2016; pp. 1816–1819. [Google Scholar]

- Wang, H.B.; Bi, J.S.; Bu, J.H.; Liu, H.N.; Zhao, F.Z.; Cao, H.J.; Ai, C. Characteristics of 22 nm UTBB-FDSOI technology with an ultra-wide temperature range. Semicond. Sci. Technol. 2022, 37, 105004. [Google Scholar] [CrossRef]

- Estrada, M.; Rivas, M.; Garduño, I.; Avila-Herrera, F.; Cerdeira, A.; Pavanello, M.; Mejia, I.; Quevedo-Lopez, M.A. Temperature dependence of the electrical characteristics up to 370 K of amorphous In-Ga-ZnO thin film transistors. Microelectron. Reliab. 2016, 56, 29–33. [Google Scholar] [CrossRef]

- Chang, G.W.; Chang, T.C.; Jhu, J.C.; Tsai, T.M.; Chang, K.C.; Syu, Y.E.; Tai, Y.H.; Jian, F.Y.; Hung, Y.C. Temperature-dependent instability of bias stress in InGaZnO thin-film transistors. IEEE Trans. Electron Devices 2014, 61, 2119–2124. [Google Scholar] [CrossRef]

- Yan, G.P.; Yang, H.; Liu, W.B.; Zhou, N.; Hu, Y.P.; Shi, Y.F.; Gao, J.F.; Tian, G.L.; Zhang, Y.D.; Fan, L.J.; et al. Mechanism analysis of ultralow leakage and abnormal instability in InGaZnO thin-film transistor toward DRAM. IEEE Trans. Electron Devices 2022, 69, 2417–2422. [Google Scholar] [CrossRef]

- Samanta, S.; Chand, U.; Xu, S.; Han, K.Z.; Wu, Y.; Wang, C.; Kumar, A.; Velluri, H.; Li, Y.; Fong, X.Y.; et al. Low subthreshold swing and high mobility amorphous indium–gallium–zinc-oxide thin-film transistor with thin HfO2 gate dielectric and excellent uniformity. IEEE Electron Device Lett. 2020, 41, 856–859. [Google Scholar] [CrossRef]

- Charlene, C.; Katsumi, A.; Hideya, K.; Jerzy, K. Density of states of a-InGaZnO from temperature-dependent field-effect studies. IEEE Trans. Electron Devices 2009, 56, 1177–1183. [Google Scholar]

- Takechi, K.; Nakata, M.; Eguchi, T.; Yamaguchi, H.; Kaneko, S. Comparison of ultraviolet photo-field effects between hydrogenated amorphous silicon and amorphous InGaZnO4 thin-film transistors. Jpn. J. Appl. Phys. 2009, 48, 010203. [Google Scholar] [CrossRef]

- Durante, O.; Intonti, K.; Viscardi, L. Subthreshold Current Suppression in ReS2 Nanosheet-Based Field-Effect Transistors at High Temperatures. ACS Appl. Nano Mater. 2023, 6, 21663–21670. [Google Scholar] [CrossRef]

- Abe, K.; Sato, A.; Takahashi, K.; Kumomi, H.; Kamiya, T.; Hosono, H. Mobility-and temperature-dependent device model for amorphous In–Ga–Zn–O thin-film transistors. Thin Solid Films 2014, 559, 40–43. [Google Scholar] [CrossRef]

- Sarkar, A. Device simulation using Silvaco ATLAS tool. In Technology Computer Aided Design; CRC Press: Boca Raton, FL, USA, 2018; pp. 203–252. [Google Scholar]

- He, H.Y.; Liu, Y.; Yin, J.L.; Wang, X.L.; Lin, X.N.; Zhang, S.D. Introducing effective temperature into Arrhenius equation with Meyer-Neldel rule for describing both Arrhenius and non-Arrhenius dependent drain current of amorphous InGaZnO TFTs. Solid-State Electron. 2021, 181, 108011. [Google Scholar] [CrossRef]

- He, H.; Xiong, C.; Yin, J.L.; Wang, X.L.; Lin, X.N.; Zhang, S.D. Analytical drain current and capacitance model for amorphous InGaZnO TFTs considering temperature characteristics. IEEE Trans. Electron Devices 2020, 67, 3637–3644. [Google Scholar] [CrossRef]

- Chakraborty, W.; Ye, H.; Grisafe, B.; Lightcap, I.; Datta, S. Low thermal budget (<250 °C) dual-gate amorphous indium tungsten oxide (IWO) thin-film transistor for monolithic 3-D integration. IEEE Trans. Electron Devices 2020, 67, 5336–5342. [Google Scholar]

- Takechi, K.; Nakata, M.; Eguchi, T.; Yamaguchi, H.; Kaneko, S. Temperature-Dependent Transfer Characteristics of Amorphous InGaZnO4 Thin-Film Transistors. Jpn. J. Appl. Phys. 2009, 48, 011301. [Google Scholar] [CrossRef]

- Samanta, S.; Han, K.Z.; Sun, C.; Wang, C.K.; Kumar, A.; Thean, A.V.Y.; Gong, X. Amorphous InGaZnO thin-film transistors with sub-10-nm channel thickness and ultra scaled channel length. IEEE Trans. Electron Devices 2021, 68, 1050–1056. [Google Scholar] [CrossRef]

- Yang, T.J.; Kim, J.H.; Ryoo, C.I.; Myoung, S.J.; Kim, C.W.; Baeck, J.H.; Bae, J.U.; Noh, J.Y.; Lee, S.W.; Park, K.S.; et al. Analysis of Drain-Induced Barrier Lowering in InGaZnO Thin-Film Transistors. IEEE Trans. Electron Devices 2023, 70, 121–126. [Google Scholar] [CrossRef]

- Yang, C.I.; Chang, T.C.; Liao, P.Y.; Chen, L.H.; Chen, B.W.; Chou, W.C.; Chen, G.F.; Lin, S.C.; Yeh, C.Y.; Tsai, C.M.; et al. Drain-Induced-Barrier-Lowing-Like effect induced by oxygen-vacancy in scaling-down via-contact type amorphous InGaZnO thin-film transistors. IEEE J. Electron Devices Soc. 2018, 6, 685–690. [Google Scholar] [CrossRef]

- Park, J.S.; Jeong, J.K.; Mo, Y.G.; Kim, H.D. Improvements in the device characteristics of amorphous indium gallium zinc oxide thin-film transistors by Ar plasma treatment. Appl. Phys. Lett. 2007, 90, 262106. [Google Scholar] [CrossRef]

- Vodapally, S.; Jang, Y.I.; Kang, I.M.; Cho, I.K.; Lee, J.H.; Bae, Y.; Ghibaudo, G.; Cristoloveanu, S.; Im, K.S.; Lee, J.H. 1/f-Noise in AlGaN/GaN nanowire omega-finfets. IEEE Electron Device Lett. 2016, 38, 252–254. [Google Scholar]

- Sindhuri, V.; Son, D.H.; Lee, D.G.; Sakong, S.H.; Jeong, Y.H.; Cho, I.T.; Lee, J.H.; Kim, Y.T.; Cristoloveanu, S.; Bae, Y.H.; et al. 1/f noise characteristics of AlGaN/GaN FinFETs with and without TMAH surface treatment. Microelectron. Eng. 2015, 147, 134–136. [Google Scholar] [CrossRef]

- Zhang, Y.; Hu, S.J.; Zhou, Y.F.; Wu, T.W.; Peng, Y.; Deng, H.C.; Bao, X.Q.; Zeng, Q.B. A Two-Dimensional MoS2 device and CMOS inverter based on the plasma immersion doping technique. J. Electron. Mater. 2023, 52, 5218–5226. [Google Scholar] [CrossRef]

- Chen, J.B.; Liu, Z.H.; Wang, H.Y.; He, Y.; Zhu, X.X.; Ning, J.; Zhang, J.C.; Hao, Y. A GaN complementary FET inverter with excellent noise margins monolithically integrated with power gate-injection HEMTs. IEEE Trans. Electron Devices 2022, 69, 51–56. [Google Scholar] [CrossRef]

| T (K) | ΔλDIBL (mV/V) | T (K) | ΔλDIBL (mV/V) |

|---|---|---|---|

| 8 | 355.5 | 325 | 10.52 |

| 50 | 75.5 | 350 | −11.08 |

| 100 | 62.5 | 375 | −10.98 |

| 150 | 29.2 | 400 | 33.32 |

| 200 | 15.5 | 425 | 133.32 |

| 250 | 10.5 | 450 | 466.22 |

| 300 | 0 | 475 | >1166.2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, J.; Bi, J.; Xu, G.; Liu, M. Characteristics Analysis of IGZO TFT and Logic Unit in the Temperature Range of 8–475 K. Electronics 2024, 13, 1427. https://doi.org/10.3390/electronics13081427

Wang J, Bi J, Xu G, Liu M. Characteristics Analysis of IGZO TFT and Logic Unit in the Temperature Range of 8–475 K. Electronics. 2024; 13(8):1427. https://doi.org/10.3390/electronics13081427

Chicago/Turabian StyleWang, Jianjian, Jinshun Bi, Gaobo Xu, and Mengxin Liu. 2024. "Characteristics Analysis of IGZO TFT and Logic Unit in the Temperature Range of 8–475 K" Electronics 13, no. 8: 1427. https://doi.org/10.3390/electronics13081427

APA StyleWang, J., Bi, J., Xu, G., & Liu, M. (2024). Characteristics Analysis of IGZO TFT and Logic Unit in the Temperature Range of 8–475 K. Electronics, 13(8), 1427. https://doi.org/10.3390/electronics13081427