Investigation on Capacitance Collapse Induced by Secondary Capture of Acceptor Traps in AlGaN/GaN Lateral Schottky Barrier Diode

Abstract

:1. Introduction

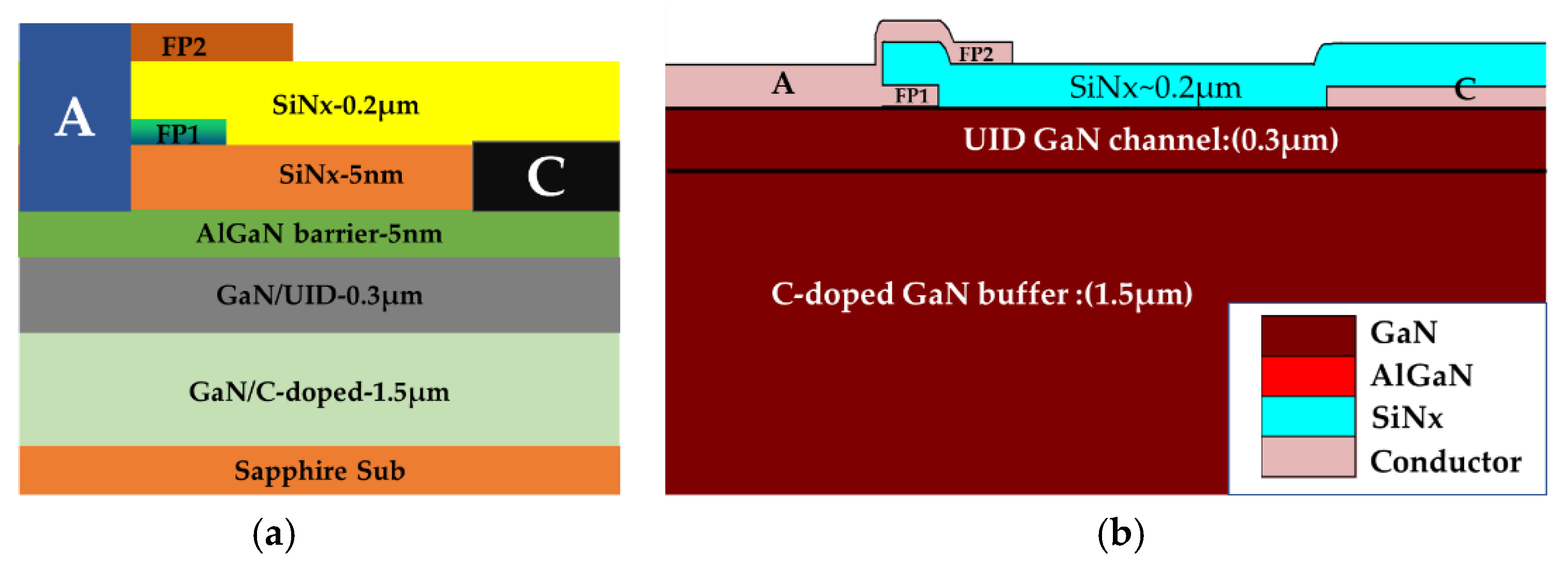

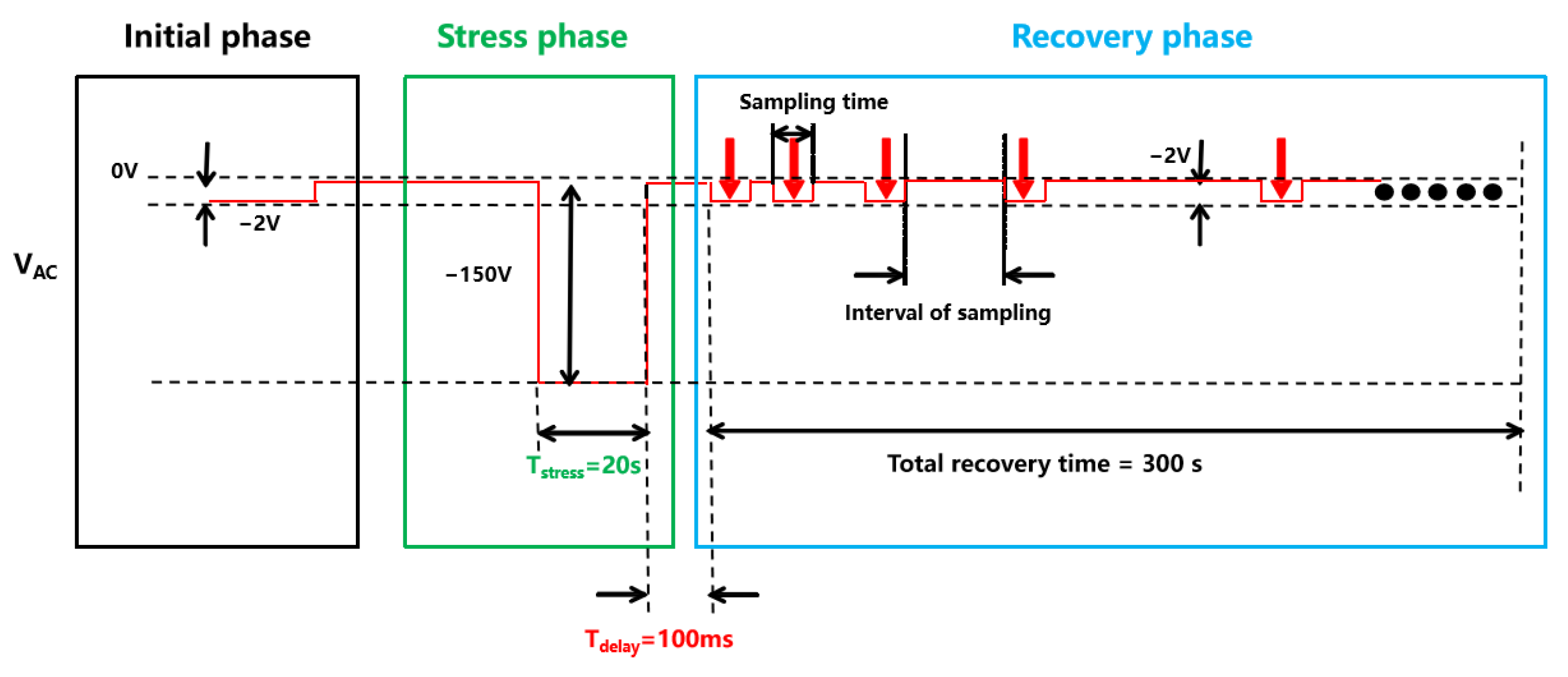

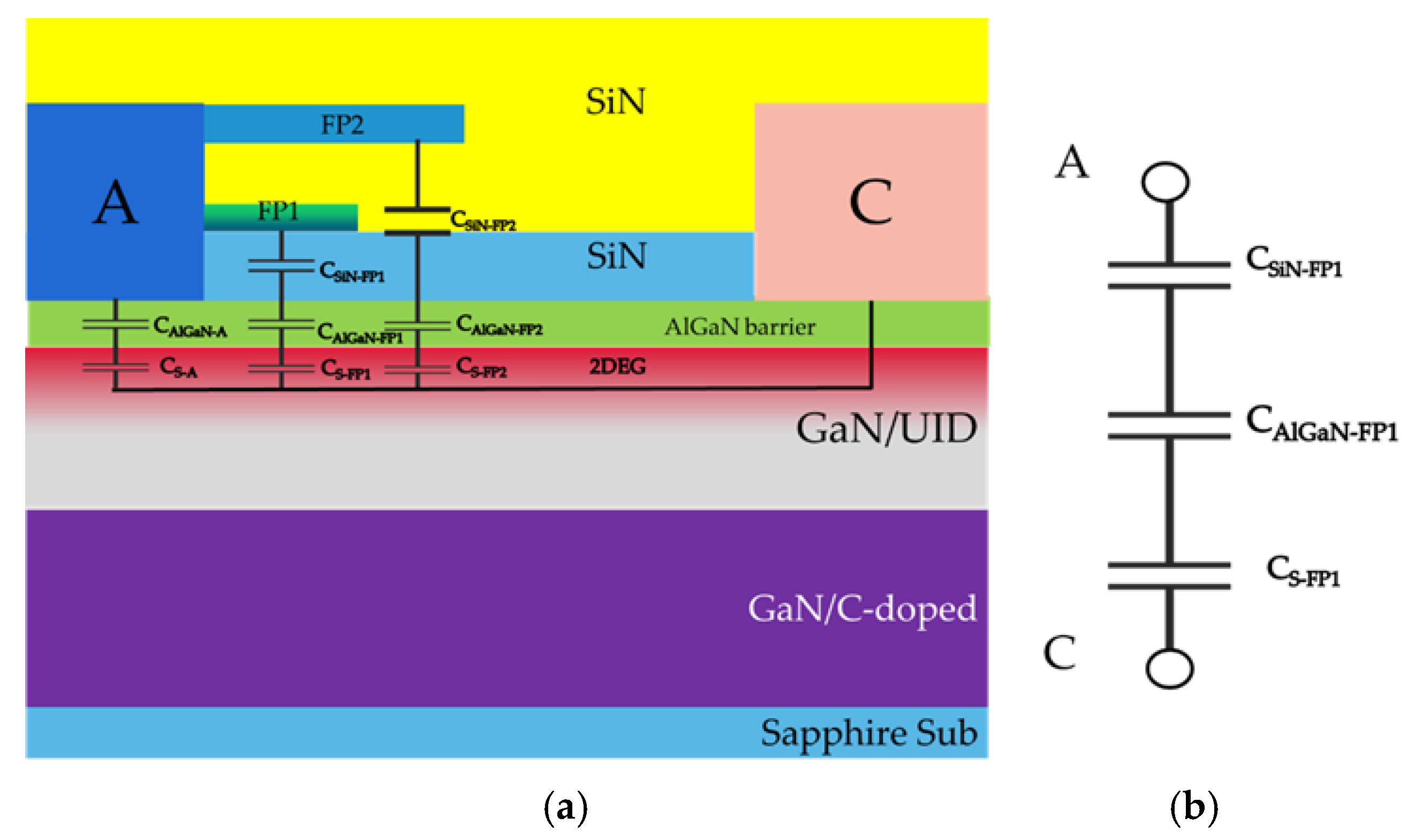

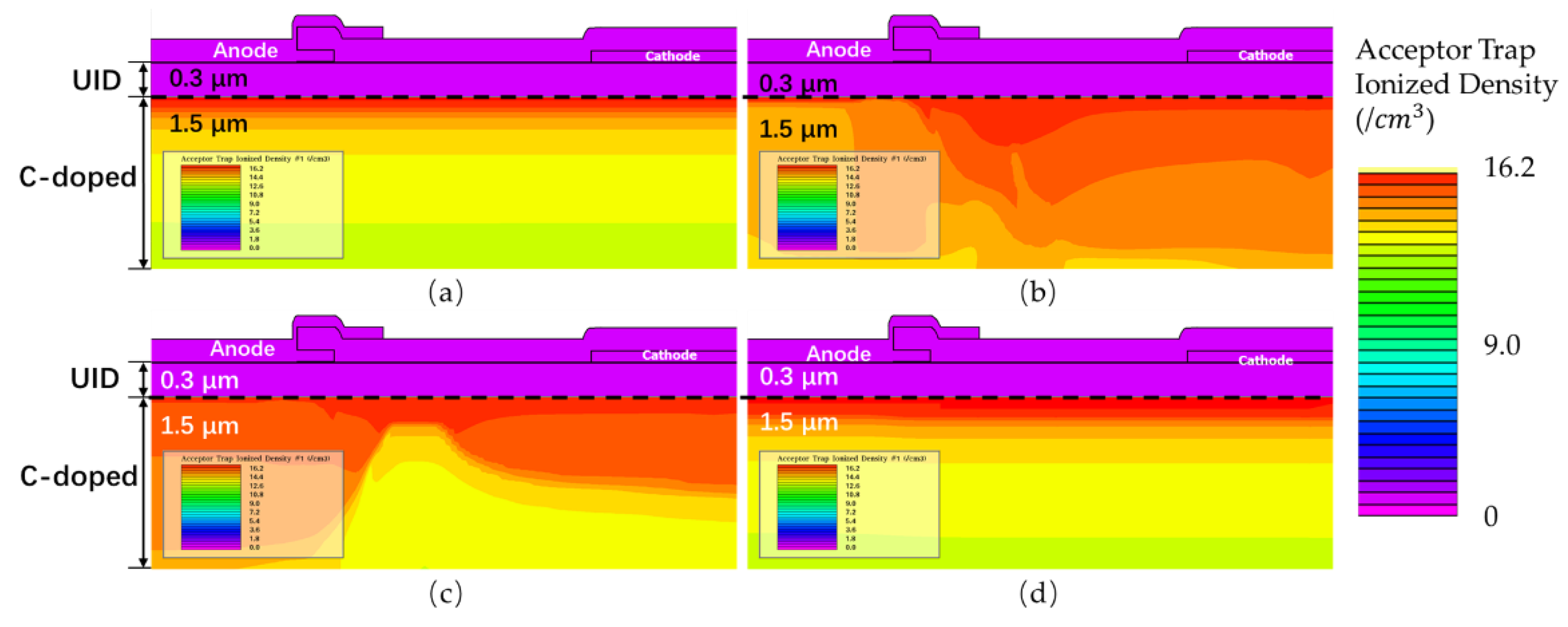

2. Device Characterization and Simulation

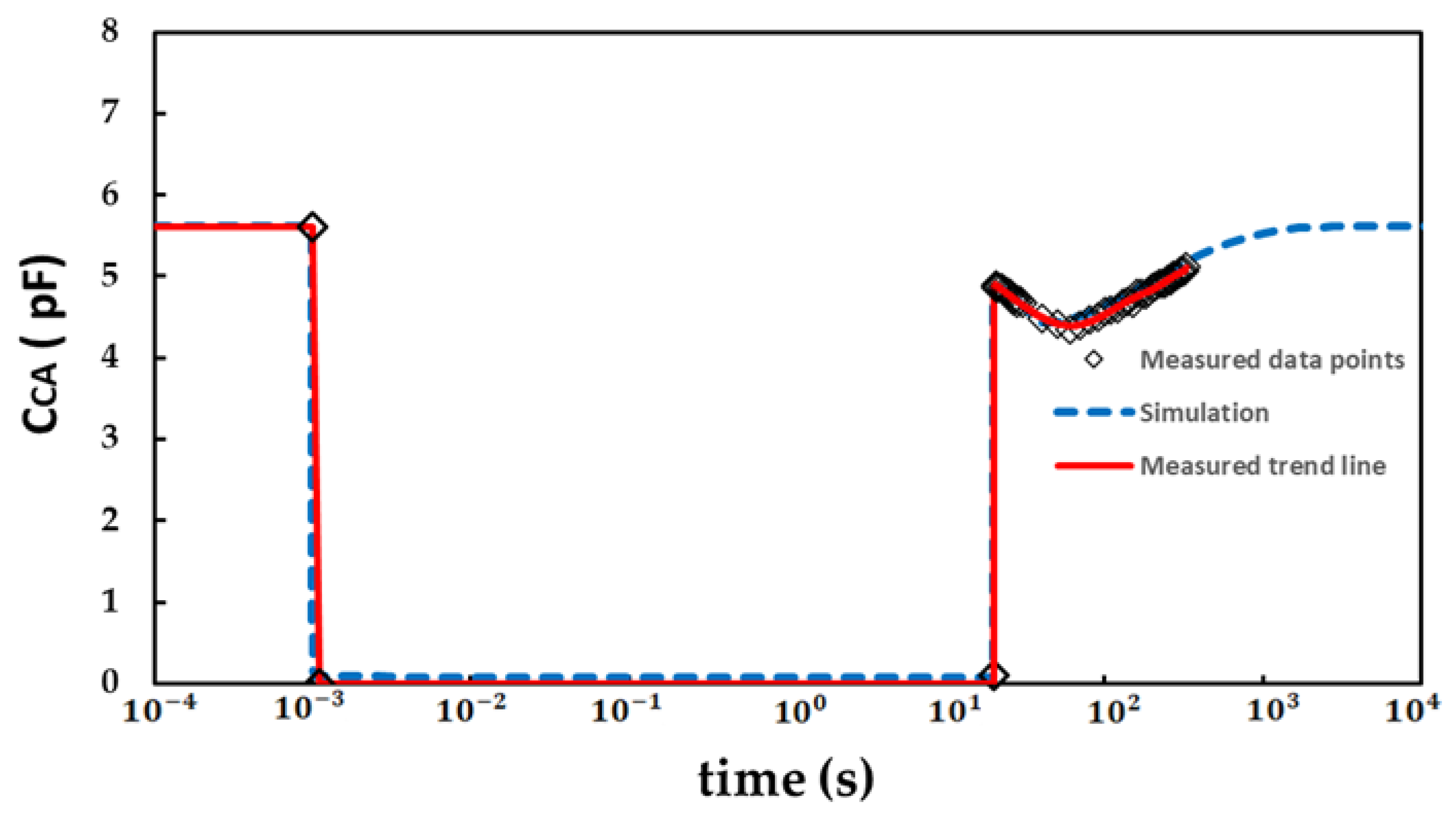

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Yong, W.; Yu, N.; Deng, D.; Ming, L.; Lau, K. Improved AlGaN/GaN HEMTs Grown on Si Substrates by MOCVD. In Proceedings of the 2010 Academic Symposium on Optoelectronics and Microelectronics Technology and 10th Chinese-Russian Symposium on Laser Physics and Laser Technology Optoelectronics Technology (ASOT), Harbin, China, 28 July–1 August 2011; IEEE: Harbin, China, 2011; pp. 68–71. [Google Scholar]

- Loo-Yau, J. Modeling Parasitic Capacitances in Gallium Nitride (GaN) FET Transistor. In Proceedings of the 2014 IEEE Central America and Panama Convention, Panama City, Panama, 12–14 November 2014. [Google Scholar]

- Ahsan, S.; Ghosh, S.; Sharma, K.; Dasgupta, A.; Khandelwal, S.; Chauhan, Y. Capacitance modeling in dual field-plate power GaN HEMT for accurate switching behavior. IEEE Trans. Electron Devices 2016, 63, 565–572. [Google Scholar] [CrossRef]

- Chiu, H.; Yang, C.; Wang, H.; Huang, H. Characteristics of AlGaN/GaN HEMTs with various field-plate and gate-to-drain extensions. IEEE Trans. Electron Devices 2013, 60, 3877–3882. [Google Scholar] [CrossRef]

- Schellenberg, J. A 2-W W-Band GaN Traveling-Wave Amplifier With 25-GHz Bandwidth. IEEE Trans. Microw. Theory Tech. 2015, 63, 2833–2840. [Google Scholar] [CrossRef]

- Yang, S.; Kim, T.; Kong, D.; Kim, S.; Yeom, K. A Novel analysis of a ku-band planar p-i-n diode limiter. IEEE Trans. Microw. Theory Tech. 2009, 57, 1447–1460. [Google Scholar] [CrossRef]

- Smith, D.; Heston, D.; Allen, D. Designing High-Power Limiter Circuits with GaAs PIN Diodes. In Proceedings of the 1999 IEEE MTT-S International Microwave Symposium Digest, Anaheim, CA, USA, 13–19 June 1999; IEEE: Anaheim, CA, USA, 1999; pp. 329–332. [Google Scholar]

- Bisi, D.; Chini, A.; Soci, F.; Stocco, A.; Meneghini, M.; Pantellini, A.; Nanni, A.; Lanzieri, C.; Gamarra, P.; Lacam, C.; et al. Hot-Electron Degradation of AlGaN/GaN High-Electron Mobility Transistors During RF Operation: Correlation with GaN Buffer Design. IEEE Electron. Device Lett. 2015, 36, 1011–1014. [Google Scholar] [CrossRef]

- Bisi, D.; Stocco, A.; Rossetto, I.; Meneghini, M.; Rampazzo, F.; Chini, A.; Soci, F.; Pantellini, A.; Lanzieri, C.; Gamarra, P.; et al. Effects of buffer compensation strategies on the electrical performance and RF reliability of AlGaN/GaN HEMTs. Microelectron. Reliab. 2015, 55, 1662–1666. [Google Scholar] [CrossRef] [Green Version]

- Sze, S.; Kwok, K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2007; pp. 197–240. [Google Scholar]

- Kang, X.; Wang, X.; Huang, S.; Zhang, J.; Fan, J.; Yang, S.; Wang, Y.; Zheng, Y.; Wei, K.; Zhi, J.; et al. Recess-Free AlGaN/GaN lateral Schottky Barrier Controlled Schottky Rectifier with Low Turn-on Voltage and High Reverse Blocking. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; IEEE: Chicago, IL, USA, 2018; pp. 280–283. [Google Scholar]

- Kang, X.; Zheng, Y.; Wu, H.; Wei, K.; Zhang, G.; Liu, X. Thin barrier gated-edge termination AlGaN/GaN Schottky-barrier-diode with low reverse leakage and high turn-on uniformity. Semicond. Sci. Technol. 2021, 36, 094001. [Google Scholar] [CrossRef]

- Zhang, H.; Kang, X.; Zheng, Y.; Wu, H.; Wei, K.; Liu, X.; Ye, T.; Jin, Z. Investigation on Dynamic Characteristics of AlGaN/GaN Lateral Schottky Barrier Diode. Micromachines 2021, 12, 1296. [Google Scholar] [CrossRef] [PubMed]

- Bisi, D.; Meneghini, M.; de Santi, C.; Chini, A.; Dammann, M.; Bruckner, P.; Mikulla, M.; Meneghesso, G.; Zanoni, E. Deep-Level Characterization in GaN HEMTs-Part I: Advantages and Limitations of Drain Current Transient Measurements. IEEE Trans. Electron. Devices 2013, 60, 3166–3175. [Google Scholar] [CrossRef]

- Yang, S.; Han, S.; Sheng, K.; Chen, K.J. Dynamic On-Resistance in GaN Power Devices: Mechanisms, Characterizations, and Modeling. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1425–1439. [Google Scholar] [CrossRef]

- Uren, M.J.; Karboyan, S.; Chatterjee, I.; Pooth, A.; Moens, P.; Banerjee, A.; Kuball, M. “Leaky Dielectric” Model for the Suppression of Dynamic RON in Carbon-Doped AlGaN/GaN HEMTs. IEEE Trans. Electron. Devices 2017, 64, 2826–2834. [Google Scholar] [CrossRef] [Green Version]

- Tanaka, K.; Umeda, H.; Ishida, H.; Ishida, M.; Ueda, T. Effects of hole traps on the temperature dependence of current collapse in a normally-OFF gate-injection transistor. Jpn. J. Appl. Phys. 2016, 55, 054101. [Google Scholar] [CrossRef]

- Gomes, J.L.; Nunes, L.C.; Sobolev, N.A.; Pedro, J.C. Memristive Properties of GaN HEMTs Containing Deep-Level Traps. Phys. Status Solidi 2018, 256, 1800387. [Google Scholar] [CrossRef]

- Chen, X.; Zhong, Y.; Zhou, Y.; Gao, H.; Zhan, X.; Su, S.; Guo, X.; Sun, Q.; Zhang, Z.; Bi, W.; et al. Determination of carbon-related trap energy level in (Al)GaN buffers for high electron mobility transistors through a room-temperature approach. Appl. Phys. Lett. 2020, 117, 263501. [Google Scholar] [CrossRef]

- Zagni, N.; Chini, A.; Puglisi, F.; Pavan, P.; Verzellesi, G. On the Modeling of the Donor/Acceptor Compensation Ratio in Carbon-Doped GaN to Univocally Reproduce Breakdown Voltage and Current Collapse in Lateral GaN Power HEMTs. Micromachines 2021, 12, 709. [Google Scholar] [CrossRef]

- Zagni, N.; Chini, A.; Puglisi, F.; Pavan, P.; Verzellesi, G. The effects of carbon on the bidirectional threshold voltage instabilities induced by negative gate bias stress in GaN MIS-HEMTs. J. Comput. Electron. 2020, 19, 1555–1563. [Google Scholar] [CrossRef]

- Koller, C.; Pobegen, G.; Ostermaier, C.; Pogany, D. Effect of Carbon Doping on Charging/Discharging Dynamics and Leakage Behavior of Carbon-Doped GaN. IEEE Trans. Electron. Devices 2018, 65, 5314–5321. [Google Scholar] [CrossRef]

- Xu, Y.; Li, Z.; Yang, X.; Shi, L.; Zhang, P.; Cao, X.; Nie, J.; Wu, S.; Zhang, J.; Feng, Y.; et al. Migration of carbon from Ga sites to N sites in GaN: A combined PAS and hybrid DFT study. Jpn. J. Appl. Phys. 2019, 58, 090901. [Google Scholar] [CrossRef]

- Chini, A.; Meneghesso, G.; Meneghini, M.; Fantini, F.; Verzellesi, G.; Patti, A.; Iucolano, F. Experimental and Numerical Analysis of Hole Emission Process from Carbon-Related Traps in GaN Buffer Layers. IEEE Trans. Electron Devices 2016, 63, 3473–3478. [Google Scholar] [CrossRef]

| Parameters | Value | Unit |

|---|---|---|

| Schottky metal work function | 4.65 | eV |

| Polarization charge density in the access region | cm−2 | |

| Polarization charge density in the electrode region | cm−2 | |

| C-doping concentration in the buffer | cm−3 | |

| ETA of the acceptor trap in the C-doped buffer | Ev + 0.95 | eV |

| ETD of the donor trap in the UID-GaN channel | Ec − 1.05 | eV |

| Electron capture cross sections | cm2 | |

| Hole capture cross sections | cm2 | |

| AC frequency | Hz | |

| Ramp time from stress to capacitance test | 10 | μs |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Kang, X.; Zheng, Y.; Wei, K.; Wu, H.; Liu, X.; Ye, T.; Jin, Z. Investigation on Capacitance Collapse Induced by Secondary Capture of Acceptor Traps in AlGaN/GaN Lateral Schottky Barrier Diode. Micromachines 2022, 13, 748. https://doi.org/10.3390/mi13050748

Zhang H, Kang X, Zheng Y, Wei K, Wu H, Liu X, Ye T, Jin Z. Investigation on Capacitance Collapse Induced by Secondary Capture of Acceptor Traps in AlGaN/GaN Lateral Schottky Barrier Diode. Micromachines. 2022; 13(5):748. https://doi.org/10.3390/mi13050748

Chicago/Turabian StyleZhang, Haitao, Xuanwu Kang, Yingkui Zheng, Ke Wei, Hao Wu, Xinyu Liu, Tianchun Ye, and Zhi Jin. 2022. "Investigation on Capacitance Collapse Induced by Secondary Capture of Acceptor Traps in AlGaN/GaN Lateral Schottky Barrier Diode" Micromachines 13, no. 5: 748. https://doi.org/10.3390/mi13050748

APA StyleZhang, H., Kang, X., Zheng, Y., Wei, K., Wu, H., Liu, X., Ye, T., & Jin, Z. (2022). Investigation on Capacitance Collapse Induced by Secondary Capture of Acceptor Traps in AlGaN/GaN Lateral Schottky Barrier Diode. Micromachines, 13(5), 748. https://doi.org/10.3390/mi13050748