Voltage-Controlled Spin-Orbit-Torque-Based Nonvolatile Flip-Flop Designs for Ultra-Low-Power Applications

Abstract

:1. Introduction

- (1)

- We proposed a symmetric complementary scheme, employing two back-to-back connected VC-SOT-MTJ devices to enable fast data configuration and a high reading threshold;

- (2)

- We proposed a simple working method for the NVFF to enable traditional FF functions and nonvolatility;

- (3)

- We proposed two high-speed, energy-efficient VC-FF designs with simpler circuit structures and lower area overhead.

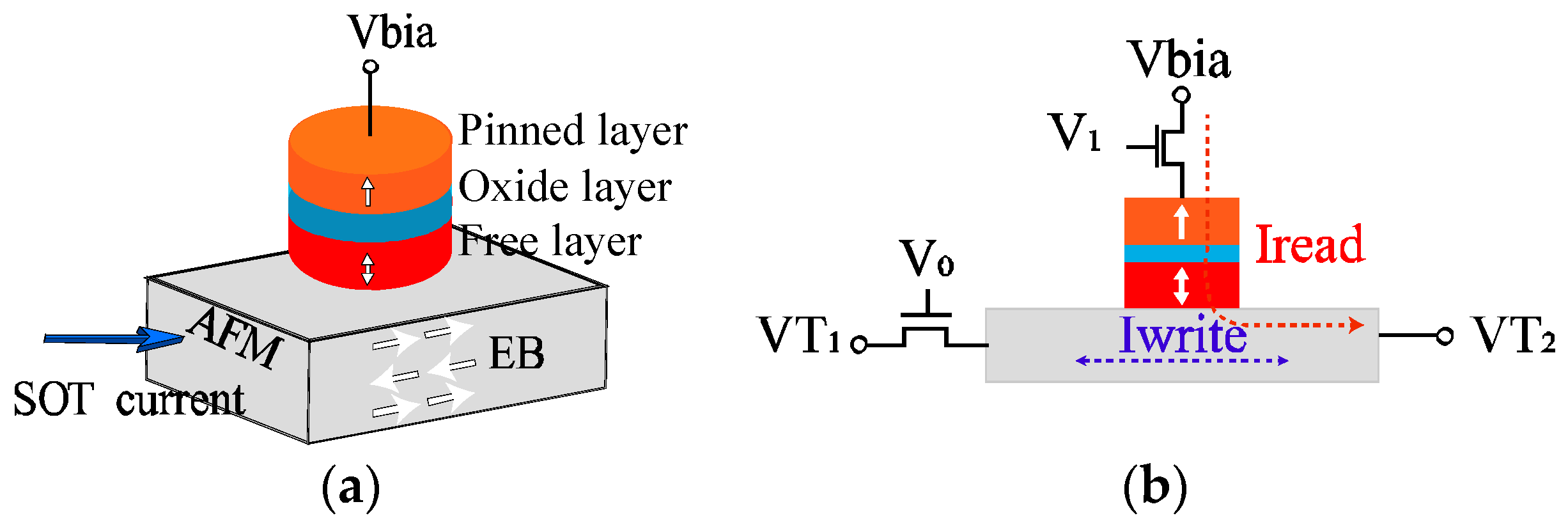

2. Basic Structure of the VC-SOT MTJ Device

3. Proposed VC-FFs

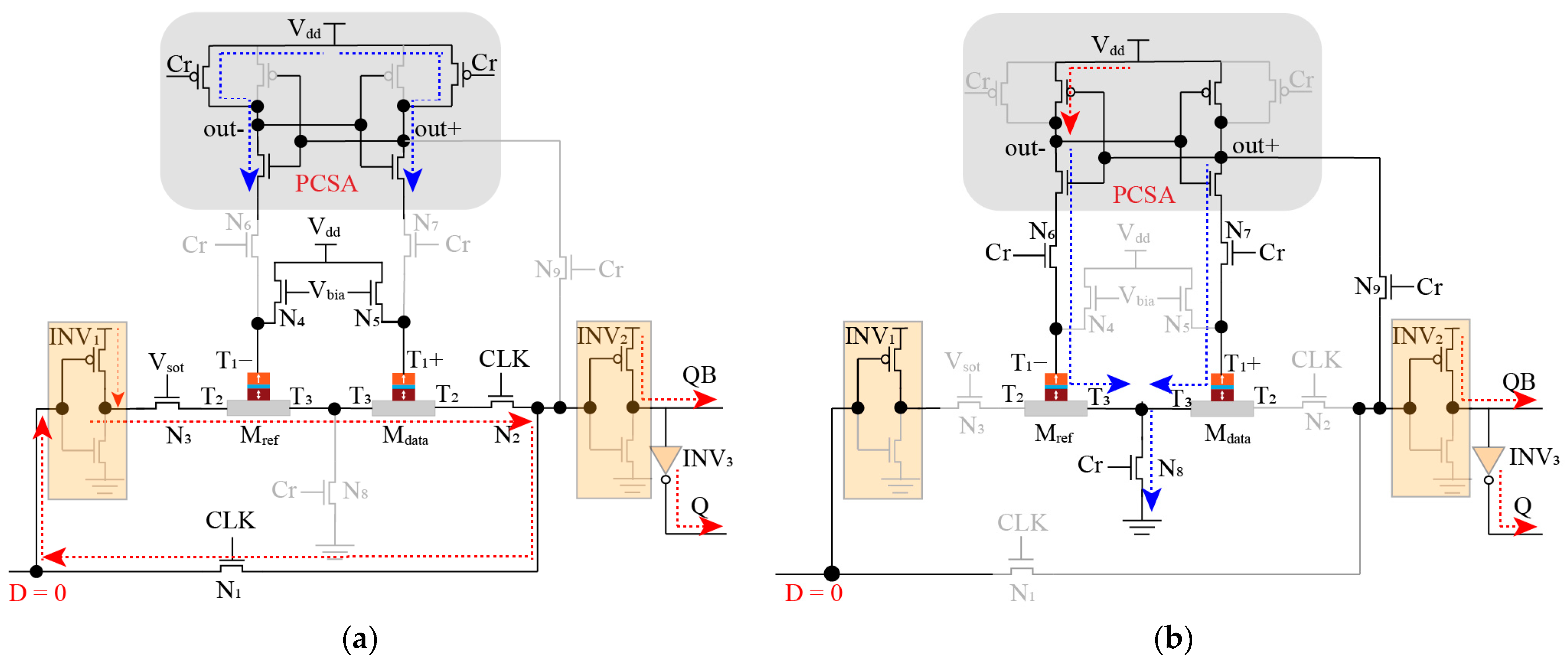

3.1. VC-DFF Circuit Architecture and Operations

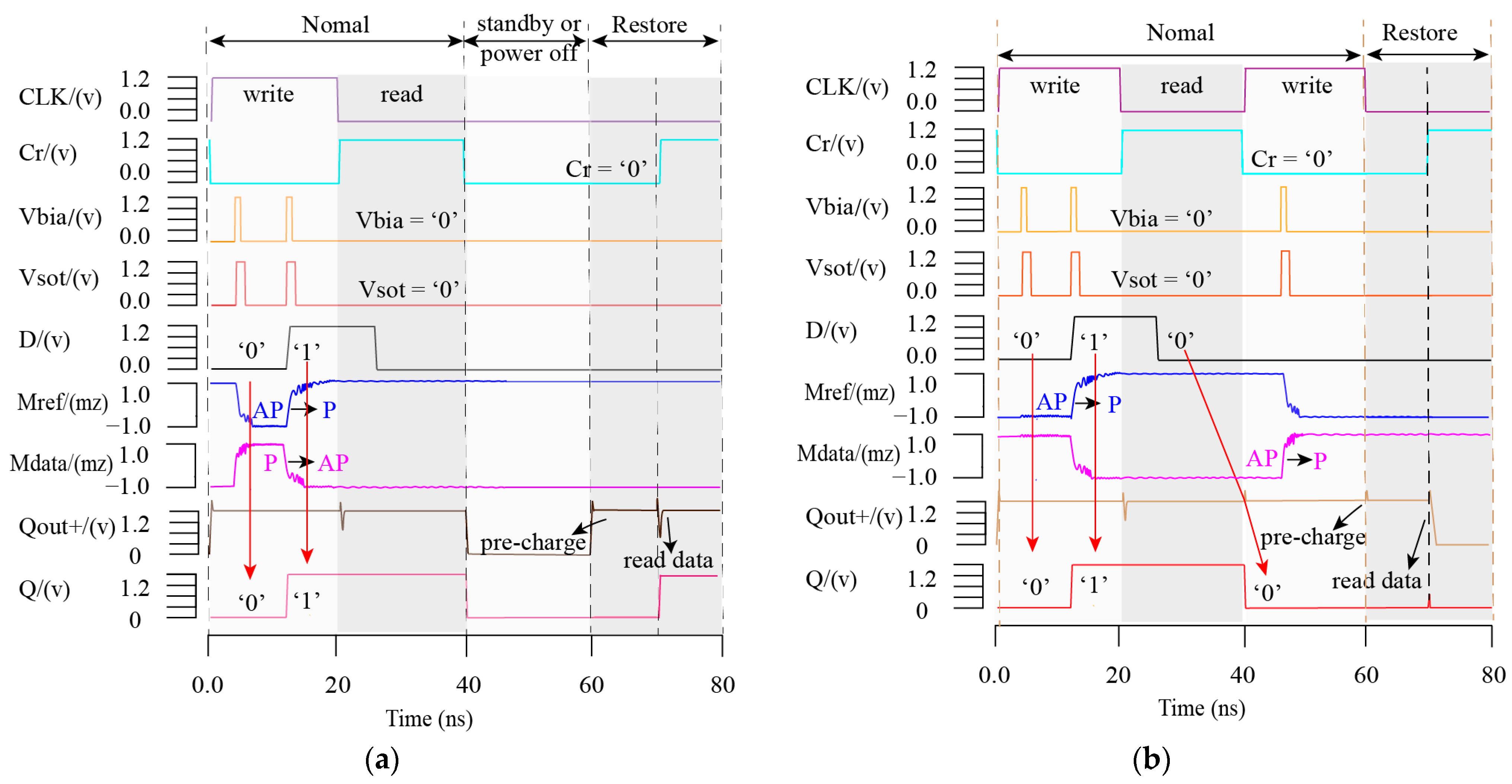

3.1.1. Normal Mode

3.1.2. Standby/Power off Mode

3.1.3. Restore Mode

3.2. VC-SRFF Circuit Architecture and Operations

4. Simulations and Discussions

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kulah, H.; Najafi, K. Energy Scavenging from Low-Frequency Vibrations by Using Frequency Up-Conversion for Wireless Sensor Applications. IEEE Sens. J. 2008, 8, 261–268. [Google Scholar] [CrossRef]

- Pan, C.; Xie, M.; Liu, Y.; Wang, Y.; Xue, C.J.; Wang, Y.; Chen, Y.; Hu, J. A lightweight progress maximization scheduler for non-volatile processor under unstable energy harvesting. In Proceedings of the LCTES ‘17: SIGPLAN/SIGBED Conference on Languages, Compilers and Tools for Embedded Systems, Barcelona, Spain, 21–22 June 2017; pp. 101–110. [Google Scholar]

- Zheng, J.; Zeng, Z.; Zhu, Y. Memristor-based nonvolatile synchronous flip-flop circuits. In Proceedings of the International Conference on Information Science and Technology (ICIST), Da Nang, Vietnam, 16–19 April 2017; pp. 504–508. [Google Scholar]

- Kazi, I.; Meinerzhagen, P.; Gaillardon, P.E.; Sacchetto, D.; Leblebici, Y.; Burg, A.; Micheli, G.D. Energy/Reliability Trade-Offs in Low-Voltage ReRAM-Based Non-Volatile Flip-Flop Design. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 3155–3164. [Google Scholar] [CrossRef]

- Cai, H.; Wang, Y.; De Barros Naviner, L.A.; Zhao, W. Robust Ultra-Low Power Non-Volatile Logic-in-Memory Circuits in FD-SOI Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 847–857. [Google Scholar] [CrossRef]

- Kang, W.; Ran, Y.; Lv, W.; Zhang, Y.; Zhao, W. High-Speed, Low-Power, Magnetic Non-Volatile Flip-Flop with Voltage-Controlled, Magnetic Anisotropy Assistance. IEEE Magn. Lett. 2017, 7, 1–5. [Google Scholar] [CrossRef]

- Portal, J.M.; Bocquet, M.; Moreau, M.; Aziza, H.; Deleruyelle, D.; Zhang, Y.; Kang, W.; Klein, J.O.; Zhang, Y.G.; Chappert, C.; et al. An Overview of Non-Volatile Flip-Flops Based on Emerging Memory Technologies. J. Electron. Sci. Technol. 2014, 12, 173–181. [Google Scholar]

- Jaiswal, A.; Andrawis, R.; Roy, K. Area-Efficient Nonvolatile Flip-Flop Based on Spin Hall Effect. IEEE Magn. Lett. 2018, 9, 1–4. [Google Scholar] [CrossRef]

- Na, T. Robust Offset-Cancellation Sensing-Circuit-Based Spin-Transfer-Torque Nonvolatile Flip-Flop. IEEE Access 2020, 8, 159806–159815. [Google Scholar] [CrossRef]

- Ali, K.; Li, F.; Lua, S.Y.H.; Heng, C. Energy- and Area-Efficient Spin-Orbit Torque Nonvolatile Flip-Flop for Power Gating Architecture. IEEE Trans. Very Large Scale Integr. Syst.(VLSI) 2018, 26, 630–638. [Google Scholar] [CrossRef]

- Kwon, K.W.; Choday, S.H.; Kim, Y.; Fong, X.; Park, S.P.; Roy, K. SHE-NVFF: Spin Hall Effect-Based Nonvolatile Flip-Flop for Power Gating Architecture. IEEE Electron Device Lett. 2014, 35, 488–490. [Google Scholar] [CrossRef]

- Huang, K.; Lian, Y. A Low-Power Low-VDD Nonvolatile Latch Using Spin Transfer Torque MRAM. IEEE Trans. Nanotechnol. 2013, 12, 1094–1103. [Google Scholar] [CrossRef]

- Lee, A.; Lo, C.P.; Lin, C.C.; Chen, W.H.; Hsu, K.H.; Wang, Z.B.; Su, F.; Yuan, Z.; Wei, Q.; King, Y.C.; et al. A ReRAM-Based Nonvolatile Flip-Flop with Self-Write-Termination Scheme for Frequent-OFF Fast-Wake-Up Nonvolatile Processors. IEEE J. Solid-State Circuits 2017, 52, 2194–2207. [Google Scholar] [CrossRef]

- Usami, K.; Akaike, J.; Akiba, S.; Kudo, M.; Yagami, K. Energy Efficient Write Verify and Retry Scheme for MTJ Based Flip-Flop and Application. In Proceedings of the Non-Volatile Memory Systems and Applications Symposium (NVMSA), Hakodate, Japan, 28–31 August 2018; pp. 91–98. [Google Scholar]

- Kim, S.K.; Oh, T.W.; Lim, S.; Ko, D.H.; Jung, S.O. High-Performance and Area-Efficient Ferroelectric FET-Based Nonvolatile Flip-Flops. IEEE Access 2021, 9, 35549–35561. [Google Scholar] [CrossRef]

- Deng, X.Y.; Xu, T. High-Speed, Energy-Efficient Magnetic Nonvolatile Flip-Flop with Self-Adaptive Write Circuit Utilizing Voltage-Controlled Magnetic Anisotropy. IEEE Trans. Magn. 2021, 57, 1–8. [Google Scholar] [CrossRef]

- Biglari, M.; Lieske, T.; Fey, D. High-Endurance Bipolar ReRAM-Based Non-Volatile Flip-Flops with Run-Time Tunable Resistive States. In Proceedings of the 14th IEEE/ACM International Symposium, Athens, Greece, 17–19 July 2018; pp. 1–6. [Google Scholar]

- Park, J. Area-efficient STT/CMOS non-volatile flip-flop. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Deng, E.; Kang, W.; Zhao, W.; Wei, S.; Wang, Y.; Zhang, D. Spin-Orbit Torque Nonvolatile Flip-Flop Designs. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems, Daegu, Korea, 22–28 May 2021; pp. 1–5. [Google Scholar]

- Kazemi, M.; Ipek, E.; Friedman, E.G. Energy-Efficient Nonvolatile Flip-Flop with Subnanosecond Data Backup Time for Fine-Grain Power Gating. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1154–1158. [Google Scholar] [CrossRef]

- Chang, Z.; Cui, A.; Wang, Z.; Qu, G. Novel Memristor-based Nonvolatile D Latch and Flip-flop Designs. In Proceedings of the 2021 22nd International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 7–9 April 2021; pp. 244–250. [Google Scholar]

- Peng, S.Z.; Lu, J.Q.; Li, W.X.; Wang, L.Z.; Zhang, H.; Li, X.; Wang, K.L.; Zhao, W.S. Field-Free Switching of Perpendicular Magnetization through Voltage-Gated Spin-Orbit Torque. In Proceedings of the 2019 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 7–11 December 2019; pp. 28.6.1–28.6.4. [Google Scholar]

- Zhao, W.; Chappert, C.; Javerliac, V.; Noziere, J. High Speed, High Stability and Low Power Sensing Amplifier for MTJ/CMOS Hybrid Logic Circuits. IEEE Trans. Magn. 2009, 45, 3784–3787. [Google Scholar] [CrossRef]

- De Rose, R.; d’Aquino, M.; Finocchio, G.; Crupi, F.; Carpentieri, M.; Lanuzza, M. Compact Modeling of Perpendicular STT-MTJs with Double Reference Layers. IEEE Trans. Nanotechnol. 2019, 18, 1063–1070. [Google Scholar] [CrossRef]

| Parameter | Description | Default Value |

|---|---|---|

| Ki | Interfacial anisotropy density | 1.005 × 10−6 KJ/m2 |

| MS | Saturation magnetization | 1.2 × 106 A/m |

| § | Voltage control coefficient | 75 fJ/V·m |

| D | Diameter of the free layer | 80 nm |

| tOX | Oxide layer height | 1.5–2.5 nm |

| tFL | Free layer thickness | 1.1 nm |

| l,w,d | Heavy metal dimension | 100 nm, 100 nm, 3 nm |

| α | Magnetic damping constant | 0.02 |

| θ | Spin Hall angle | 0.3 |

| rho | Heavy metal resistivity | 200 μΩ · cm |

| Hex | Exchange bias field | −7956 A/m |

| T | Temperature | 300 K |

| Vdd | Voltage | 1.2 V |

| Υ | Gyromagnetic ratio | 2.21276 × 105 m/(A·s) |

| μ0 | Permeability in free space | 1.2566 × 106 H/m |

| kB | Boltzmann constant | 1.38 × 10−23 J/K |

| e | Elementary charge | 1.6 × 10−19 C |

| STT-Based NVDFF [12] | STT-Based NVDFF [24] | SOT-Based NVDFF [19] | SOT-Based NVDFF [8] | Proposed VC-DFF/VC-SRFF | |

|---|---|---|---|---|---|

| Technological Node (nm) | 40 | 20 | 40 | 45 | 40 |

| Number of Devices | 21T + 2MTJ | 28T + 2MTJ | 21T + 2MTJ | 16T + 1MTJ | 20T + 2MTJ/24T + 2MTJ |

| Twrite (ns) | 35.7 | 4.1 | 1.6 | 4 | 1.7 |

| Write Power Consumption (fJ/bit) | 4780 | 54.5 | 131.4 | 218 | 6.64 |

| TRecovery (ns) | >0.1 | 0.24 | 0.2 | 0.3 | 0.16 |

| Recovery Power Consumption (fJ/bit) | 5 | 14.5 | 6.7 | 6 | 3.24 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, X.; Deng, E.; Luo, L.; Jiang, L.; Zhang, Y.; Liu, D.; Pan, B.; Kang, W. Voltage-Controlled Spin-Orbit-Torque-Based Nonvolatile Flip-Flop Designs for Ultra-Low-Power Applications. Appl. Sci. 2023, 13, 11316. https://doi.org/10.3390/app132011316

Liu X, Deng E, Luo L, Jiang L, Zhang Y, Liu D, Pan B, Kang W. Voltage-Controlled Spin-Orbit-Torque-Based Nonvolatile Flip-Flop Designs for Ultra-Low-Power Applications. Applied Sciences. 2023; 13(20):11316. https://doi.org/10.3390/app132011316

Chicago/Turabian StyleLiu, Xiao, Erya Deng, Lichuan Luo, Linjun Jiang, Youguang Zhang, Dijun Liu, Biao Pan, and Wang Kang. 2023. "Voltage-Controlled Spin-Orbit-Torque-Based Nonvolatile Flip-Flop Designs for Ultra-Low-Power Applications" Applied Sciences 13, no. 20: 11316. https://doi.org/10.3390/app132011316

APA StyleLiu, X., Deng, E., Luo, L., Jiang, L., Zhang, Y., Liu, D., Pan, B., & Kang, W. (2023). Voltage-Controlled Spin-Orbit-Torque-Based Nonvolatile Flip-Flop Designs for Ultra-Low-Power Applications. Applied Sciences, 13(20), 11316. https://doi.org/10.3390/app132011316